Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении систем цифровой обработки сигналов, основанных на выполнении быстрого преобразования Лурье.

Целью изобретения является повышение точности устройства.

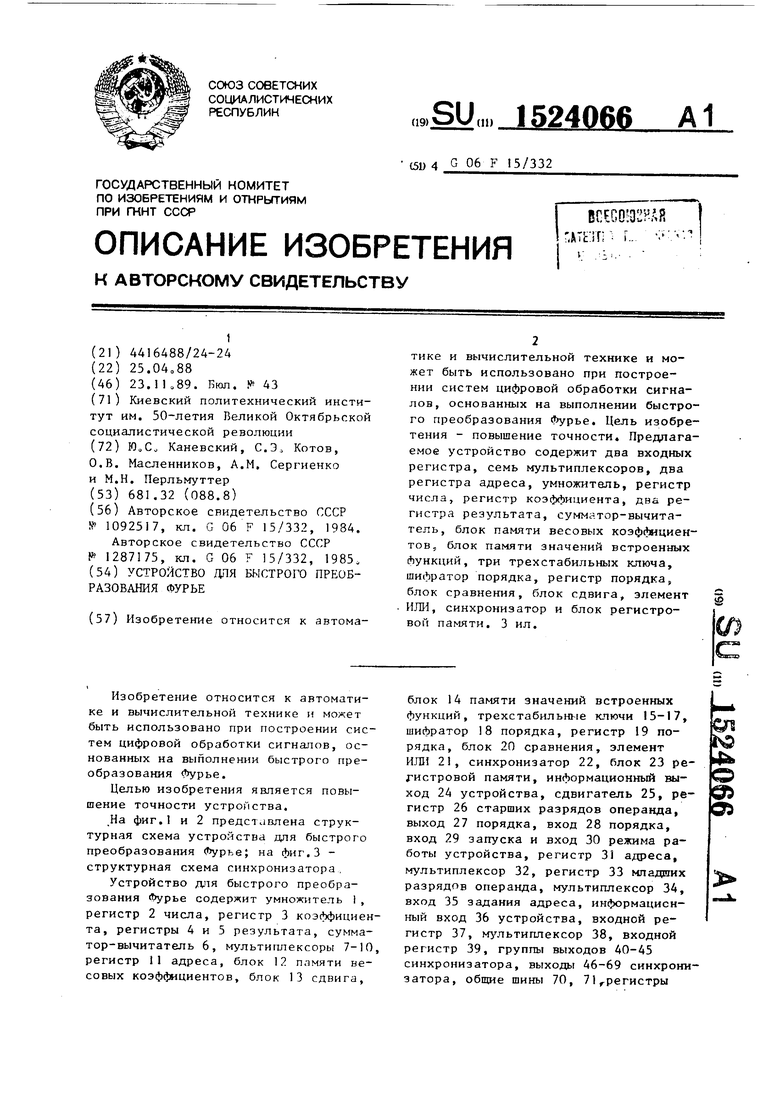

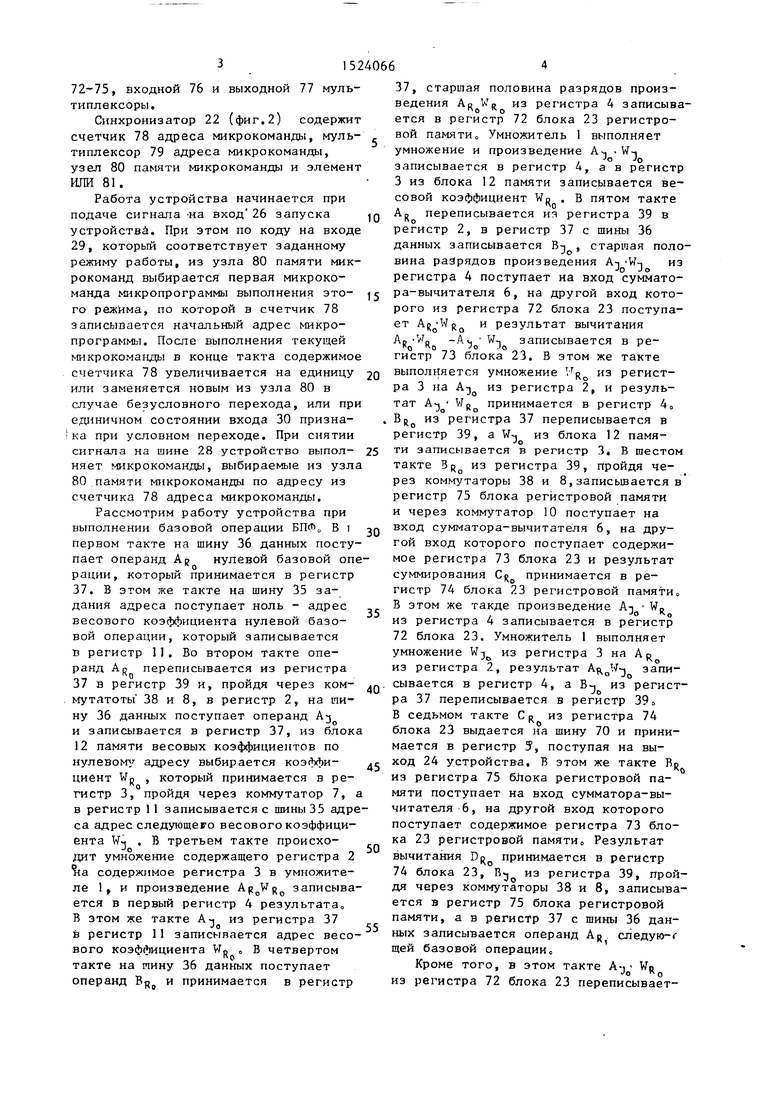

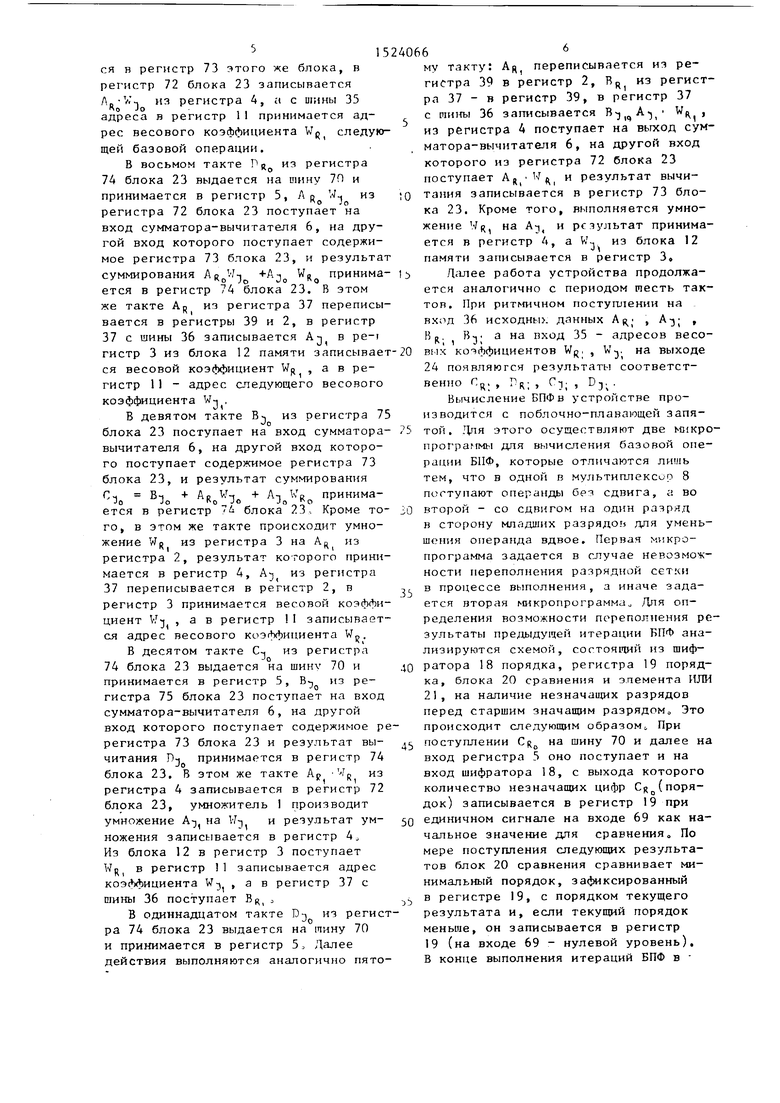

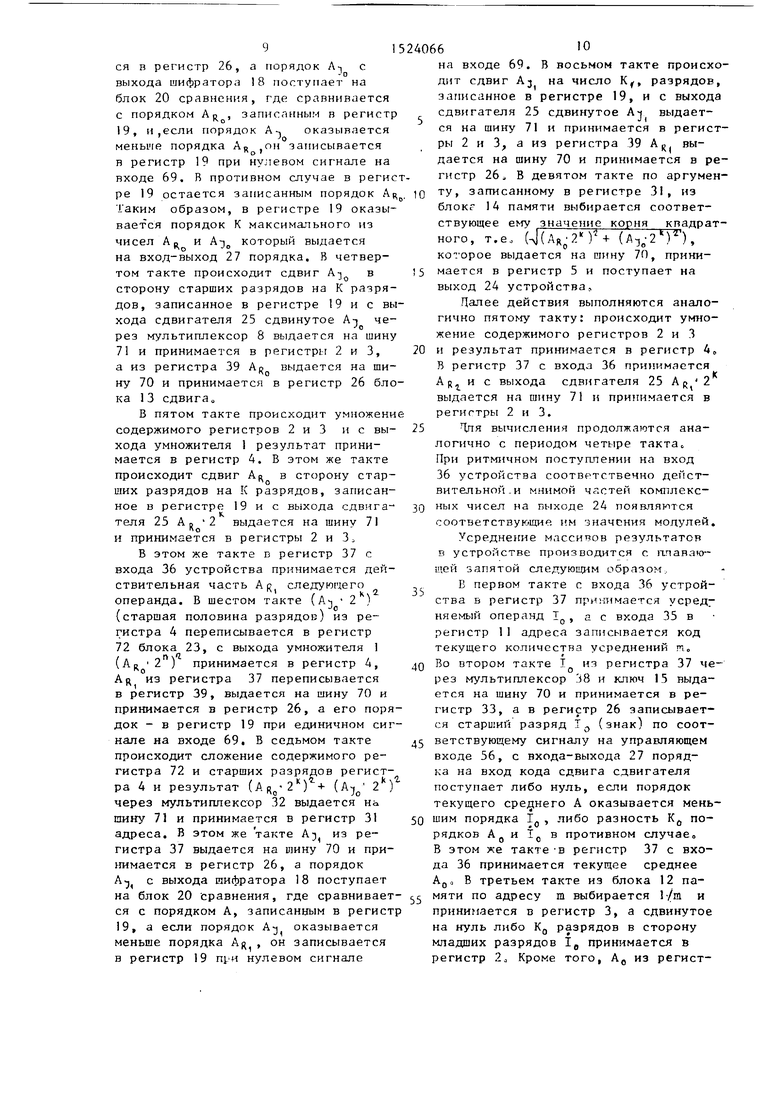

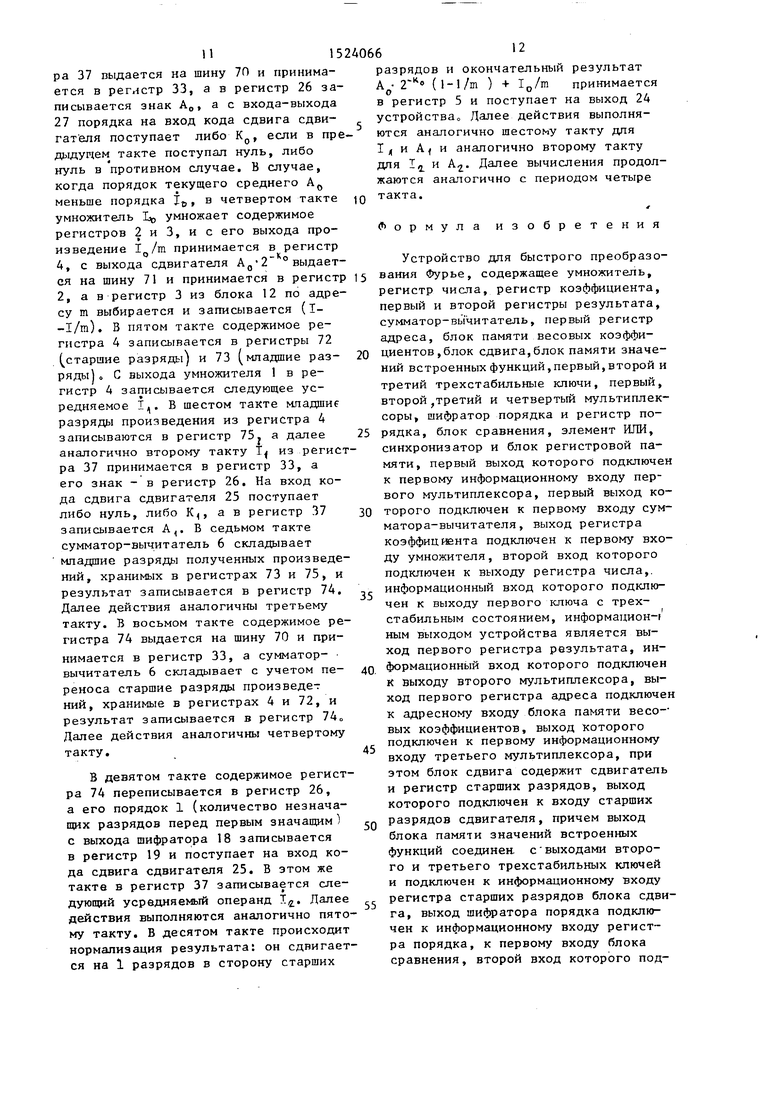

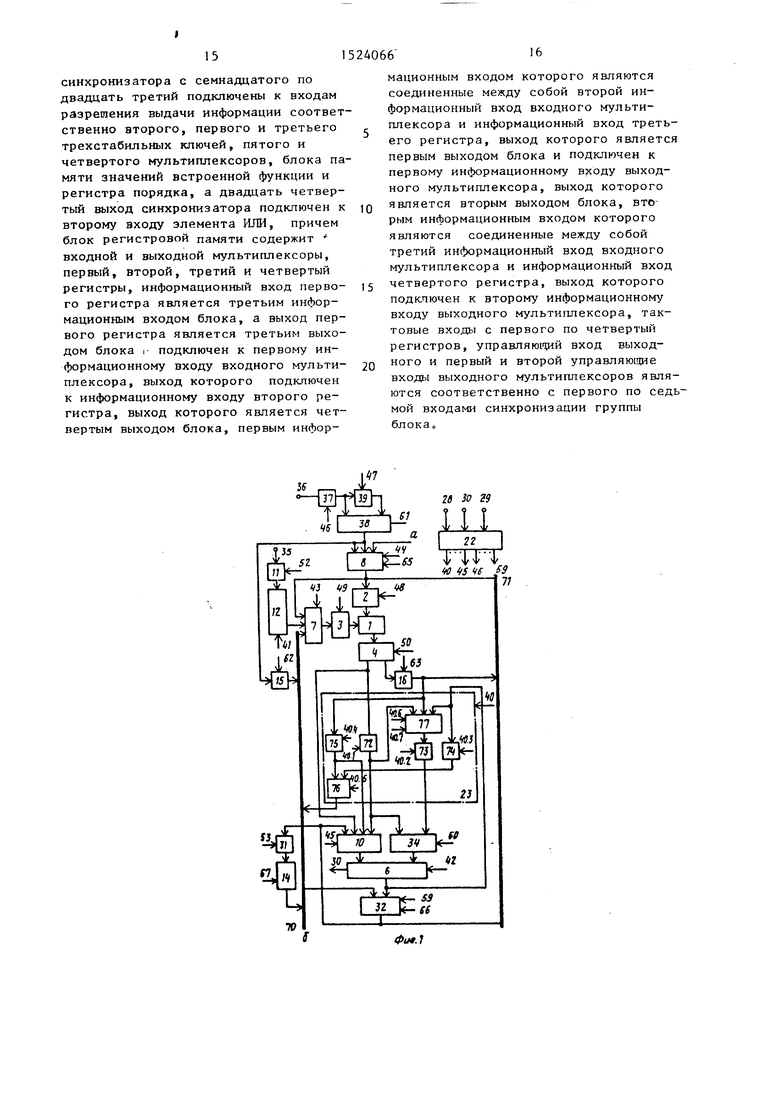

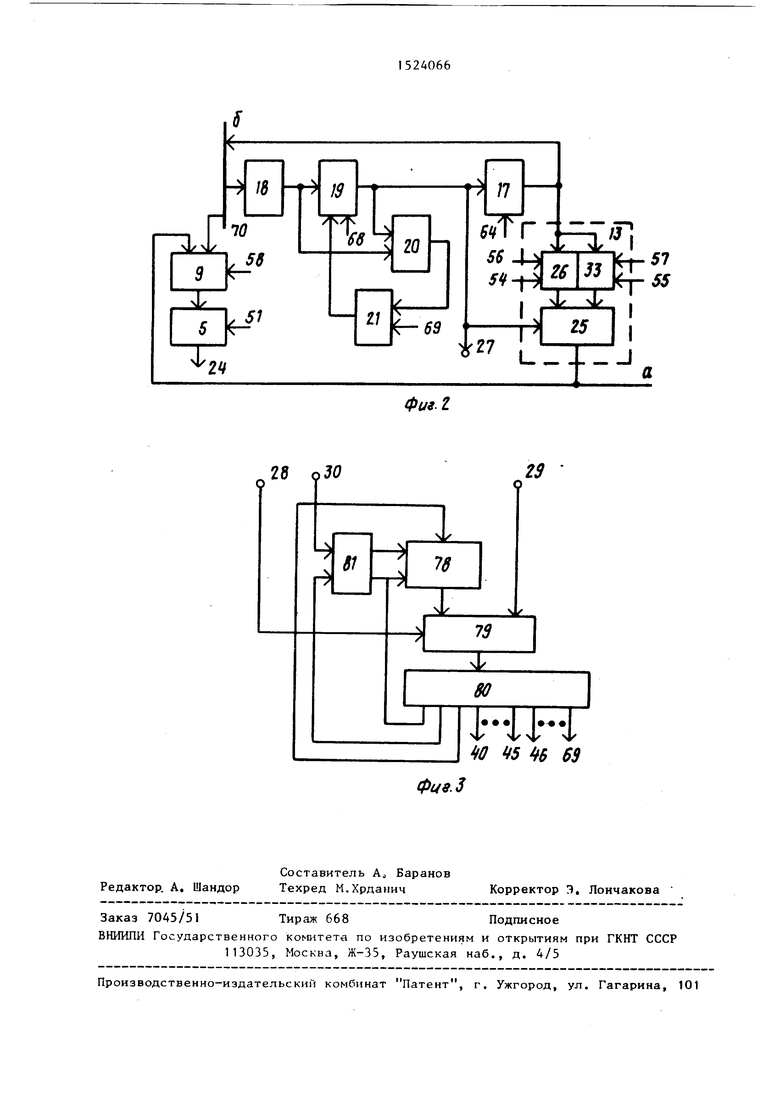

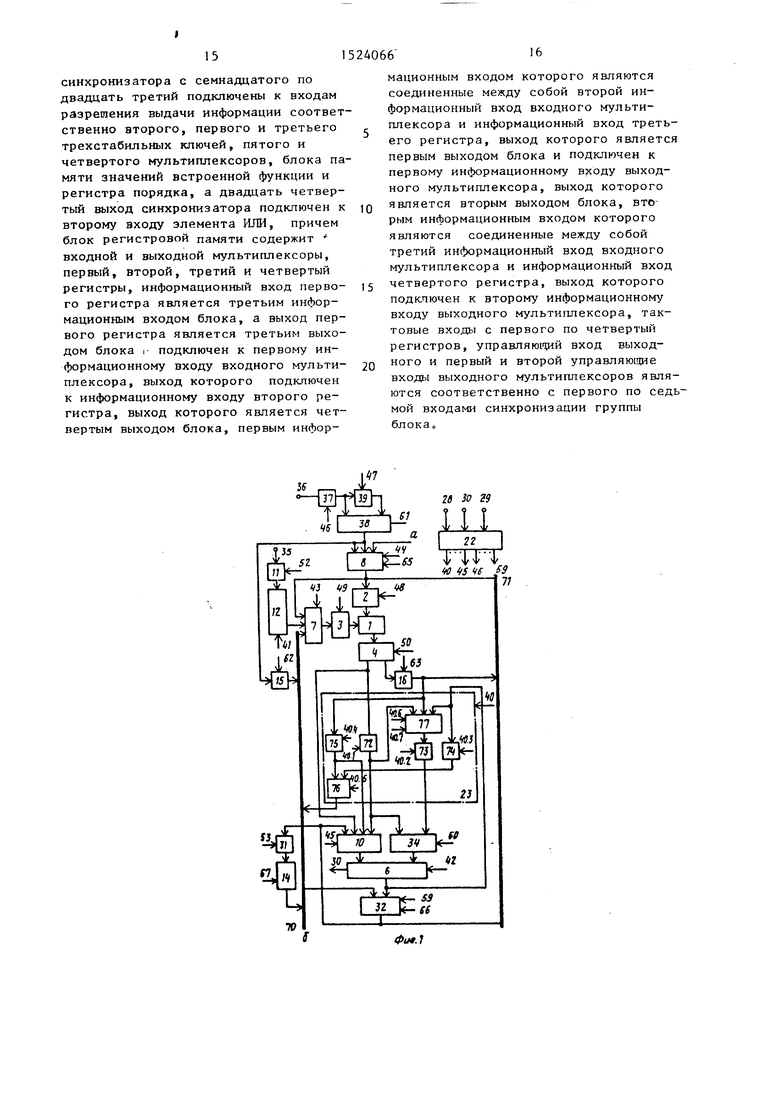

На фиг.1 и 2 представлена структурная схема устройства для быстрого преобразования «Т урье; на Лиг.З - структурная схема синхронизатора,

Устройство для быстрого преобразования Фурье содержит умножитель 1, регистр 2 числа, регистр 3 коэффициента, регистры 4 и 5 результата, сумма- тор-вычитатель 6, мультиплексоры 7-10, регистр 11 адреса, блок 12 плмяти весовых коэффициентов, блок 13 сдвига.

блок 14 памяти значений встроенных функций, трехстабильнме ключи 15-17, шифратор 18 порядка, регистр 19 порядка, блок 20 сравнения, элемент ИЛ 21, синхронизатор 22, блок 23 регистровой памяти, информационный выход 24 устройства, сдвигатель 25, регистр 26 старших разрядов операнда, выход 27 порядка, вход 28 порядка, вход 29 запуска и вход 30 режима работы устройства, регистр 31 адреса, мультиплексор 32, регистр 33 мпадшнх разрядов операнда, мультиплексор 34, вход 35 задания адреса, информационный вход 36 устройства, входной регистр 37, мультиплексор 38, входной регистр 39, группы выходов 40-45 синхронизатора, выходы 46-69 синхронизатора, общие шины 70, 71 регистры

©Г1

72-75, входной 76 и выходной 77 мультиплексоры.

Синхронизатор 22 (фиг.2) содержит счетчик 78 адреса микрокоманды, муль- типлексор 79 адреса микрокоманды, узел 80 памяти микрокоманды и элемент ИЛИ 81.

Работа устройства начинается при подаче сигнала -на вход 26 запуска устройств. При этом по коду на входе 29, который соответствует заданному режиму работы, из узла ВО памяти микрокоманд выбирается первая микрокоманда микропрограммы выполнения это- го режима, по которой в счетчик 78 записывается начальный адрес микропрограммы. После выполнения текущей микрокоманды в конце такта содержимое счетчика 78 увеличивается на единицу или заменяется новым из узла 80 в случае безусловного перехода, или при единичном состоянии входа 30 призна- i ка при условном переходе. При снятии сигнала на шине 28 устройство выпол- няет микрокоманды, выбираемые из узла 80 памяти микрокоманды по адресу из счетчика 78 адреса микрокоманды.

Рассмотрим работу устройства при выполнении базовой операции БПФо В i первом такте на шину 36 данных поступает операнд Ар нулевой базовой операции, который принимается в регистр 37. В этом же такте на шину 35 задания адреса поступает ноль - адрес весового коэффициента нулевой базовой операции, который записывается и регистр 11. Во втором такте операнд АС переписывается из регистра

О

37 а регистр 39 и, пройдя через ком- мутатоты 38 и 8, в регистр 2, на пину 36 данных поступает операнд А и записывается в регистр 37, из 12 памяти весовых коэффициентов по нулевом адресу выбирается коэффициент Wo , который принимается в реп о о-,

гистр 3, пройдя через коммутатор 7, а в регистр 1 1 записывается с шины 35 адреса адрес следующего весового коэффициента ч . В третьем такте происхо- от

дит умножение содержащего регистра 2 ja содержимое регистра 3 в умножителе 1 и произведение записывается в первый регистр 4 результата,

В этом же такте A-i из регистра 37

J О

в регистр 11 записывается адрес весового коэффициента W( В четвертом такте на тину 36 данных поступает операнд Bg и принимается в регистр

о

блока

AT .W-. Jo Jo

37, старшая половина разрядов произведения А( W из регистра 4 записывается в регистр 72 блока 23 регистровой памяти о Умножитель 1 выполняет умножение и произведение записывается в регистр 4, а в регистр 3 из блока 12 памяти записывается весовой коэффициент Wn . В пятом такте

о АИ переписывается из регистра 39 в

О

регистр 2, в регистр 37 с шины 36 данных записывается B-j , старшая

половина разрядов произведения Ат Wn из

.Jo Jo

регистра 4 поступает на вход сумматора-вычитателя 6, на другой вход которого из регистра 72 блока 23 поступает и результат вычитания AD -Vo -Ач W-, записывается в реin Г .п --К ч И-1

о 0 -, ° - О гистр 73 блока 23. В этом же такте

умножение -

из

регистиз регистра 2, и резуль- принимается в регистр 4

Вцр из регистра 37 переписывается в регистр 39, а из блока 12 памяти записывается в регистр 3, В шестом такте Вр из регистра 39, пройдя через коммутаторы 38 и 8,записьшается в регистр 75 блока регистровой памяти и через коммутатор 10 поступает на вход сумматора-вычитателя 6, на другой вход которого поступает содержимое регистра 73 блока 23 и результат суммирования GI принимается в регистр 74 блока 23 регистровой памяти

В этом же такде произведение Ат WD

.Jo к. о

из регистра 4 записывается в регистр

72 блока 23. Умножитель 1 выполняет умножение W из регистра 3 на А( из регистра 2, результат Ap J f-j записывается в регистр 4, а В--) из регистра 37 переписывается в регистр 39 о В седьмом такте С ( из регистра 74 блока 23 выдается на шину 70 и принимается в регистр , поступая на выход 24 устройства. В этом же такте Во

о

из регистра 75 бЛока регистровой памяти поступает на вход сумматора-вычитателя 6, на другой вход которого поступает содержимое регистра 73 блока 23 регистровой памяти Результат вычитания Dj принимается в регистр 74 блока 23, B«j из регистра 39, пройдя через коммутаторы 38 и 8, записывается в регистр 75 блока регистровой памяти, а в регистр 37 с шины 36 данных записывается операнд А( следую-с щей базовой операции

Кроме того, в этом такте А-, Wo

I/O Q

ИЗ регистра 72 блока 23 переписывается Б регистр 73 этого же блока, в регистр 72 блока 23 записывается

A.,-V. из регистра А, а с шины 35

° °11

адреса в регистр 1I принимается адрес весового коэффициента Wp следующей базовой операции.

В восьмом такте Рц из регистра 74 блока 23 выдается на шину 70 и принимается в регистр 5, Лд W-, из регистра 72 блока 23 поступает на вход сумматора-вычитателя 6, на другой вход которого поступает содержимое регистра 73 блока 23, и результат суммирования АК. Aj W принимается в регистр 74 блока 23. В этом

же такте An из регистра 37 переписы

вается в регистры 39 и 2, в регистр

37 с шины 36 записывается А т в pe-i

в

R;

ва на пход 35 - адресов весогистр 3 из блока 12 памяти записывает-20 вмх коэффициентов Wg, , W-j. на выходе

ся весовой коэффициент Wj , а в ре-24 появляются результаты соответстгистр 1 - адрес следующего весовоговенно Г, , , Ст| , D-j, . коэффициента W-i ,

В девятом такте В-, из регистра 75

0

блока 23 поступает на вход сумматора- 5 той. Для этого осуществляют две Ю1Кровычитателя 6, на другой вход которо-программы для вычисления базовой опего поступает содержимое регистра 73рации БПФ, которые отличаются лишь

Вычисление БПФ в устройстве производится с поблочно-плавающей запя24066

му такту: Ац переписывается из регистра 39 в регистр 2, Вц из регистра 37 - в регистр 39, в регистр 37 с ши1п,1 36 записывается B-jjqA W , из регистра 4 поступает на выход сумматора-вычитателя 6, на другой вход которого из регистра 72 блока 23 поступает Ац , и результат вычитания записывается в регистр 73 блока 23. Кроме того, выполняется умножение WR на АЧ и результат принимается в регистр 4, а W-, из блока 12 памяти записывается в регистр 3

Д;1лее работа устройства продолжается аналогично с периодом тесть тактов. При ритмичном поступлении на вх;1д 36 исходных данных А(; , А-э;

:о

в

R;

ва на пход 35 - адресов весо20 вмх коэффициентов Wg, , W-j. на выходе

венно Г, , , Ст| , D-j, .

Вычисление БПФ в устройстве производится с поблочно-плавающей запя

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для быстрого преобразования Фурье | 1985 |

|

SU1287175A1 |

| Устройство для быстрого преобразования Фурье | 1984 |

|

SU1206802A1 |

| Устройство для быстрого преобразования Фурье | 1989 |

|

SU1633425A1 |

| Устройство для быстрого преобразования Фурье | 1986 |

|

SU1392577A1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2010 |

|

RU2446461C2 |

| Устройство для вычисления функций | 1989 |

|

SU1705822A1 |

| Устройство для цифровой фильтрации | 1985 |

|

SU1381541A1 |

| Устройство для обработки данных | 1987 |

|

SU1513443A1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2446454C1 |

| Арифметическое устройство с плавающей точкой | 1985 |

|

SU1259248A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении систем цифровой обработки сигналов, основанных на выполнении быстрого преобразования Фурье. Цель изобретения - повышение точности. Предлагаемое устройство содержит два входных регистра, семь мультиплексоров, два регистра адреса, умножитель, регистр числа, регистр коэффициента, два регистра результата, сумматор-вычитатель, блок памяти весовых коэффициентов, блок памяти значений встроенных функций, три трехстабильных ключа, шифратор порядка, регистр порядка, блок сравнения, блок сдвига, элемент ИЛИ, синхронизатор и блок регистровой памяти. 3 ил.

блока 23, и результат суммирования С-1 В-1 АО W-i + Лт We принима+ Лп Wr, Jo с

Jfl Jo JO Jo O

ется в регистр 7 блока 23. Кроме того, в этом же такте происходит умножение W( из регистра 3 на А из регистра 2, результат которого принимается в регистр 4, A.-J из регистра 37 переписывается в регистр 2, в регистр 3 принимается весовой коэффициент V/-J , а в регистр 1 I записывается адрес весового коэффициента W. В десятом такте С-.| из регистра 74 блока 23 выдается на шину 70 и принимается в регистр 5, В-, из регистра 75 блока 23 поступает на вход сумматора-вычитателя 6, на другой вход которого поступает содержимое ре регистра 73 блока 23 и результат вычитания П-1 принимается в регистр 74

блока 23. В этом же такте Ар -Wn из

1 1 регистра 4 записывается в регистр 72

блока 23, умножитель 1 производит умножение А на Vf-j и результат умножения записьшается в регистр 4 Из блока 12 в регистр 3 поступает W в регистр П записывается адрес коэффициента W-) , а в регистр 37 с шины 36 поступает Bg

В одиннадцатом такте D-i из регист ора 74 блока 23 выдается на тину 70

и принимается в регистр 5 Далее действия выполняются аналогично пятотем, что в одной в мультиплексор о погтупают операнды без сдвига, а во

второй - со сдвигом на один разряд в сторону младших разрядов для уменьшения операнда вдвое. Первая программа задается в случае невозможности переполнения разрядной сетки

в процессе выполнения, а иначе задается вторая п кpoпpoгpaммao /1пя определения возможности перепол1гения результаты предащущей итерации БПФ анализируются схемой, состояпшй из шиф-

ратора 18 порядка, регистра 19 порядка, блока 20 сравнения и элемента ИЛИ 21, на наличие незначаидах разрядов перед старшим знача1цим разрядомо Это происходит следующим образом При

поступлении CR на шину 70 и далее на вход регистра 5 оно поступает и на вход шифратора 18, с выхода которого количество незначащих цифр С(;(порядок) записывается в регистр 19 при единичном сигнале на входе 69 как начальное значение для сравнения. По мере поступления следующих результатов блок 20 сравнения сравнивает минимальный порядок, зафиксированный в регистре 19, с порядком текущего результата и, если текущий порядок меньше, он записывается в регистр 19 (на входе 69 - нулевой уровень). В конце выполнения итераций БПФ в

10

регистре 18 оказывается порядок максимального числа в массиве результатов, который указывает масштаб массива результатов и выдается на вход- выход 27 порядка В следующей итерации, если зафиксирован нулевой порядок, задается микропрограмма базовой операции БПФ, в которой мультиплексор 8 сдвигает исходные данные на один разряд в сторону младших разрядов i

Вычисление спектра мощности в устройстве производится с плавающей запятой и вдвое увеличенной разрядной сеткой о В первом такте на вход 36 устройства поступает реальная часть нулевого операнда AR и принимается в регистр 37„ Во втором такте А пе- .реписывается в регистры 2 и 3, а в регистр 37 с входа 36 поступает мнимая часть операнда . В третьем такте происходит умножение содержимого регистров 2 и 3, и результат (А ц ) принимается в регистр 4, А переписывается из регистра 37 в регистры 2 и

из регистра 72 блока 23 и результат суммирования записывается в регистр 74 блока 23о Далее действия в этом такте вьшолняются аналогично второму такту: ется

АЙ из регистра 37 переписыва- в регистры 2 и 3, а в регистр 37

0

25

°

из регистра 4 переписывается в регистр 72 блоков 2,3 регистровой памяти, а младшая половина разрядов, пройдя через ключ 16,- в регистр 73 блока 23. В этом же такте происходит умножение содержимого регистров 2 и 3,

и результат (A-i ) принимается в ре- огистр 4о

В пятом такте младшая часть произведения (А( ) 23 изведения (Ат ) , которая поступает

«о

на сумма гор-вычитатель 6, пройдя ключ 16 и мультиплексор 10, и результат суммирования принимается в регистр 74 блока 23. В этом же такте старшая часть произведения (Ац ) регистра 72 блока 23 записывается в регистр 73, старшая часть (А--) ) из регистра 4 переписывается в регистр 72, а в регистр 37 записывается дей30

из регистра 73 блока

складывается с младшей частью проствительная часть Ац следующего операнда с входа 36 устройства

В шестом тат те младшая часть суммы

(Agjj) + (A;jg) из регистра 74 блока 23 выдается на шину 70 и принимается в регистр 33, старшая часть произведения (Ag / из регистра 73 блока 23 складывается на сумматоре- вычитателе 6 с учетом переноса со старшей частью произведения (А-, )

- D

записывается A-j с входа 36 устройства

В седьмом такте старшая часть сум2 2.

мы АО + А-, из регистра 74 блока 23

ло Jo выдается на шину 70 и принимается в

регистр 26, а с выхода шифратора 18 соответствующий код сдвига, Тое код количества незначащих разрядов суммы перед старшим значащем, принимается в регистр 19 порядка по единичному сигналу на входе 69 и выдается на шину Входа-выхода 27 порядка Далее действия в этом такте выполняются аналогично третьему такту.

В восьмом такте происходит нормализация полученного результата: значение суммы сдвигается на сдвигателе 25 в сторону старших разрядов на количество разрядов, записанное в регистре 19 порядка, и нормализованный результат принимается в регистр 5, пройдя через мультиплексор 9, и : появляется на выходе 24 устройства. Далее действия в этом такте выполняются аналогично четвертому такту

Далее работа устройства продолжается аналогично с периодом четыре такта. При ритмичном поступлении на вход 36 исходных данных Ар и А- на выходе 24 появляются соответствующие значения спектра мощности.

Вычисление модуля комплексного числа в устройстве производится с плавающей запятой следую1цим образом

В первом такте на вход 36 устройства поступает действительная часть из дс А)д нулевого операнда и принимается в регистр 37. Во втором такте Ад переписывается из регистра 37 в регистр 39, а также выдается через мультиплексор 38 и ключ 15 на шину 70, а количество незначащих в нем цифр (порядок) записывается в регистр 19 порядка при единичном сигнале на шине 69. В этом же такте мнимая часть А) нулевого операнда принимается с входа 36 устройства в регистр 37f а регистр 33 устанавливается в нулевое состояние сигналом на входе 57. В третьем такте А из регистра 37 выдается на шину 70 и принимает35

40

50

55

из регистра 72 блока 23 и результат суммирования записывается в регистр 74 блока 23о Далее действия в этом такте вьшолняются аналогично второму такту: ется

АЙ из регистра 37 переписыва- в регистры 2 и 3, а в регистр 37

ся в регистр 26, а порядок A-j с выхода шифратора 8 поступает на блок 20 сравнения, где сравнивается с порядком А( , записанным в регистр 19, и ,если порядок А- оказывается

меныче порядка А ,он записывается в регистр 19 при нулевом сигнале на входе 69. В противном случае в регисре 19 остается записанным порядок Ац Таким образом, в регистре 19 оказывается порядок К максимального из чисел А ц и А который выдается на вход-выход 27 порядка. В четвертом такте происходит сдвиг в сторону старших разрядов на К разрядов, записанное в регистре 19 и с выхода сдвигателя 25 сдвинутое Ат че

рез мультиплексор 8 выдается на шину

71 и принимается в регистрн 2 и 3, а из регистра 39 А( выдается на шину 70 и принимается в регистр 26 блока 13 сдвига

В пятом такте происходит умножени содержимого регистров 2 и 3 и с выхода умножителя 1 результат принимается в регистр 4, В этом же такте происходит сдвиг А( в сторону старших разрядов на К разрядов, записанное в регистре 19 и с выхода сдвигателя 25 АО 2 выдается на шину 71

(NO И принимается в регистры 2 и 3

В этом же такте в регистр 37 с входа 36 устройства принимается действительная часть A(| следующего

операнда. В шестом такте (А , 2 )

/ °

(старшая половина разрядов) из регистра 4 переписывается в регистр

72 блока 23, с выхода умножителя 1 / , ,

(Af 2 ) принимается в регистр 4,

AR ИЗ регистра 37 переписывается в регистр 39, выдается на шину 70 и принимается в регистр 26, а его порядок - в регистр 19 при единичном сигнале на входе 69, В седьмом такте происходит сложение содержимого регистра 72 и старших разрядов регистра 4 и результат (Af( 2 ) + ( 2 через мультиплексор 32 выдается нь шину 71 и принимается в регистр 31 адреса. В этом же такте А;) из регистра 37 выдается на шину 70 и принимается в регистр 26, а порядок h-j с выхода шифратора 18 поступает

В первом такте с входа 36 устройства в регистр 37 принт1мается усредняемый операнд 1, а с входа 35 в регистр 11 адреса записывается код текущего количества усреднений т.

t

4Q Во втором такте 1 из регистра 37 че рез мультиплексор 38 и ключ 15 выдается на шину 70 и принимается в регистр 33, а в регистр 26 записывается старший разряд Т,, (знак) по соответствующему сигналу на управляющем входе 56, с входа-выхода 27 порядка на вход кода сдвига сдвигателя поступает либо нуль, если порядок текущего среднего А оказывается мень шим порядка IQ, либо разность К порядков Ар и Тд в противном случае В этом же такте -в регистр 37 с входа 36 принимается текущее среднее

35

45

50

В третьем такте из блока 12 пана блок 20 сравнения, где сравнивает- мяти по адресу m выбирается 1/т и ся с порядком А, записанным в регистр принимается в регистр 3, а сдвинутое 19, а если порядок А- оказывается меньше порядка А( , он записывается в регистр 19 при нулевом сигнале

на нуль либо Kg разрядов в сторону младших разрядов 1ц принимается в регистр 2о Кроме того, Ад из регист ,

52406610

на входе 69. В восьмом такте происходит сдвиг АЗ на число К, разрядов, записанное в регистре 19, и с выхода сдвигателя 25 сдвинутое A-i выдается на шину 71 и принимается в регист ,

т.

е

10

5

20

25

ры 2 и 3, а из регистра 39 А выдается на шину 70 и принимается в регистр 26i В девятом такте по аргументу, записанному в регистре 31, из блок 14 памяти выбирается соответствующее значение корня квадрат- ного, т.е. (л(Ая 2 Г+ ()), Koi opoe выдается на шину 70, принимается в регистр 5 и поступает на выход 24 устройства,

Цалее действия выполняются аналогично пятому такту: происходит умножение содержимого регистров 2 и 3 и результат принимается в регистр 4о В регистр 37 с входа 36 принимается AR и с выхода сдвигателя 25 2 выдается на шину 71 и принимается в регистры 2 и 3.

Тля вычисления продолжаются аналогично с периодом четыре такта При ритмичном поступлении на вход 36 устройства соответственно действительной.и мнимой частей комплексных чисел на выходе 24 пояштяются соответствук/щие им значения модулей.

Усреднение массивов результатов в устройстве производится с п.лаваю- щей запятой следую1цим образом,

В первом такте с входа 36 устройства в регистр 37 принт1мается усредняемый операнд 1, а с входа 35 в регистр 11 адреса записывается код текущего количества усреднений т.

t

4Q Во втором такте 1 из регистра 37 через мультиплексор 38 и ключ 15 выдается на шину 70 и принимается в регистр 33, а в регистр 26 записывается старший разряд Т,, (знак) по соответствующему сигналу на управляющем входе 56, с входа-выхода 27 порядка на вход кода сдвига сдвигателя поступает либо нуль, если порядок текущего среднего А оказывается меньшим порядка IQ, либо разность К порядков Ар и Тд в противном случае В этом же такте -в регистр 37 с входа 36 принимается текущее среднее

30

35

45

50

В третьем такте из блока 12 памяти по адресу m выбирается 1/т и принимается в регистр 3, а сдвинутое

на нуль либо Kg разрядов в сторону младших разрядов 1ц принимается в регистр 2о Кроме того, Ад из регистpa 37 выдается на шину 7П и принимается в регистр 33, а в регистр 26 записывается знак АО, а с входа-выхода 27 порядка на вход кода сдвига сдви- гат еля поступает либо К, если в пре- дьодущем такте поступал нуль, либо нуль в противном случае, В случае, когда порядок текущего среднего А, меньше порядка jj,, в четвертом такте Q умножитель Ъ умножает содержимое регистров 2 и 3, и с его выхода произведение I./m принимается

разрядов и окончательный результат А 2

(1-1/:

m

) + I(,/m принимается в регистр 5 и поступает на выход 24 устройства Далее действия выполняются аналогично шестому такту дпя I J, и А и аналогично второму такту для I, жаются такта.

и А. Далее вычисления продол- аналогично с периодом четыре

Т ормула изобретения

в регистр 4, с выхода сдвигателя А„ 2 выдается на шину 71 и принимается 2, а в регистр 3 из блока 12 по адресу m выбирается и записывается (I- -I/m). В пятом такте содержимое регистра 4 записывается в регистры 72 (старшие разряды) и 73 (мпадшие разряды, С выхода умножителя 1 в регистр 4 записывается следующее усредняемое I,. В шестом такте мпадшие разряды произведения из регистра 4 записываются в регистр 75. а далее аналогично второму такту 1 из регистра 37 принимается в регистр 33, а его знак - в регистр 26. На вход кода сдвига сдвигателя 25 поступает либо нуль, либо К, а в регистр 37 записывается А. В седьмом такте сумматор-вычитатель 6 складывает младшие разряды полученных произведений, хранимых в регистрах 73 и 75, и результат записывается в регистр 74. Далее действия аналогичны третьему такту. В восьмом такте содержимое регистра 74 выдается на шину 70 и принимается в регистр 33, а сумматор- вычитатель 6 складывает с учетом переноса старшие разряды произведет НИИ, хранимые в регистрах 4 и 72, и результат записывается в регистр 74о Далее действия аналогичны четвертому такту.

В девятом такте содержимое регистра 74 переписывается в регистр 26, а его порядок 1 (количество незначащих разрядов перед первым значащим ) с выхода шифратора 18 записывается в регистр 19 и поступает на вход кода сдвига сдвигателя 25. В этом же такте в регистр 37 записывается следующий усредняемый операнд .. Далее действия выполняются аналогично пятому такту. В десятом такте происходит нормализация результата: он сдвигается на 1 разрядов в сторону старших

20

30

35

Устройство для быстрого преобразо- в регистр 15 вания Фурье, содержащее умножитель, регистр числа, регистр козффициента, первый и второй регистры результата, сумматор-вычитатель, первый регистр адреса, блок памяти весовых коэффициентов, блок сдвига, блок памяти значений встроенных функций,первый,второй и третий трехстабильные ключи, первый, второй ,третий и четвертый мультиплексоры, шифратор порядка и регистр по25 рядка, блок сравнения, элемент ИЛИ, синхронизатор и блок регистровой памяти, первый выход которого подключен к первому информационному входу пер вого мультиплексора, первый выход которого подключен к первому входу сум- матора-вычитателя, выход регистра коэффицжнта подключен к первому входу умножителя, второй вход которого подключен к выходу регистра числа,, информационный вход которого подключен к выходу первого ключа с трех- стабильным состоянием, информацион-i ным выходом устройства является выход первого регистра результата, ин4Q формационный вход которого подключен к выходу второго мультиплексора, выход первого регистра адреса подключен к адресному входу блока памяти весовых коэффициентов, выход которого подключен к первому информационному входу третьего мультиплексора, при этом блок сдвига содержит сдвигатель и регистр старших разрядов, выход которого подкпючен к входу старших разрядов сдвигателя, причем выход блока памяти значений встроенных функций соединен с выходами второго и третьего трехстабильных ключей и подключен к информационному входу регистра старших разрядов блока сдвига, выход шифратора порядка подключен к информационному входу регистра порядка, к первому входу блока сравнения, второй вход которого под45

50

55

разрядов и окончательный результат А 2

(1-1/:

m

) + I(,/m принимается в регистр 5 и поступает на выход 24 устройства Далее действия выполняются аналогично шестому такту дпя I J, и А и аналогично второму такту для I, жаются такта.

и А. Далее вычисления продол- аналогично с периодом четыре

Т ормула изобретения

13

ключей к выходу регистра порядка, вход разрешения записи которого подключен к выходу элемента И.Ш1, информационный вход третьего трехстабиль- ного ключа является входом задания порядка устройства, входами запуска и задания режима работы которого являются соответственно входы запуска и установки синхронизатора, вход признака которого подключен к выходу знакового разряда сумматора-вычи- тателя, отличающееся тем, что, с целью повышения точности, в него введены первый и второй входные регистры, пятый, шестой и седьмой мультиплексоры, второй регистр сдви га, а в блок сдвига введен регистр младших разрядов операнда, выход которого подключен к входу младших разрядов сдвигателя, блока сдвига, при этом выход второго регистра адреса подключен к адресному входу блока памяти значений встроенных функций, выход которого соединен с первым выходом блока регистровой памяти и подключен к второму информационному входу третьего и первым информационным входам второго и четвертого мультиплексоров, входы 1чифратора порядка и инфopмaциoннo fy входу регистра младших разрядов операнда блока сдвига, выход сдвигателя которого подключен к второму информационному входу второго мультиплексора и первому информационному входу пятого мультиплексора, выход которого соединен с выходом четвертого мультиплексора и подключен к третьему информационному входу третьего мультиплексора, информационному выходу регистра числа, первому информационному входу блока регистровой памяти, информационному входу первого регистра адреса и второму информационному входу первого мультиплексора, второй информационный вход четвертого мультиплексора соединен с вторым информационным входом блока регистровой памяти и подключен к выходу сумматора- вычитателя, третий информационный вход блока регистровой памяти соединен с третьим инфор fiциoнным входом первого мультиплексора и подключен к выходу старших разрядов второго регистра результата, четвертый информационный вход первого мультиплексора соединен с первым информационным входом шестого мультиплексора и под

52A066

ключен к третьему выходу блока регистровой памяти, четвертый выход которого подключен к второму информационному входу шестого мультиплексора, выход которого подключен к второ- му входу сумматора-вычитателя, вход умножителя подключен к информационному входу второго регистра результата,

JQ выход младших разрядов которого подключен к информационному входу первого трехстабильного ключа, выход регистра порядка является выходом порядка устройства и подключен к входу

с кода сдвигателя блока сдвига, информационный вход первого регистра адреса является входом задания адреса устройства, информационным входом которого является информационный вход

2Q первого входного регистра, выход которого подключен к первому информационному входу седьмого мультиплексора и информационному входу второго входного регистра, выход которого под25 ключен к второму информационному входу седьмого мультиплексора, выход которого подключен к информационному входу второго трехстабильного ключа и с вторым и третьим информационны3Q ми входами соответственно без сдвига и со сдвигом на один разряд в сторону мпадгиих разрядов пятого мультиплексора, выход блока сравнения подключен к первому входу элемента ИЛИ, группы выходов синхронизатора с первой по шестую подключены соответственно к группе входов синхронизации блока регистровой памяти, группа входов выборки зоны блока памяти весовых коэффициентов, группа управляющих входов сумматора-вычитателя и группы управ- ляюидих входов третьего, пятого и первого мультиплексоров, выходы синхронизатора с первого по десятый подключены соответственно к входам разрешения

35

40

50

45

записи первого и второго регистров,

регистра числа, регистра коэффициента, второго и первого регистров результата, первого и второго регистров адреса, регистра старших разрядов операнда и регистра младших разрядов операнда блока сдвига, выходь синхронизатора с одиннадцатого по шестнадцатый подключены к установочным входам регистра старших разрядов 5 операнда и регистра младших разрядов операнда блока сдвига, управляющими входами второго, четвертого, шестого и седьмого мультиплексоров, выходы

синхронизатора с семнадцатого по двадцать третий подключены к входам разрешения выдачи информации соответственно второго, первого и третьего трехстабильных ключей, пятого и четвертого мультиплексоров, блока памяти значений встроенной функции и регистра порядка, а двадцать четвертый выход синхронизатора подключен к второму входу элемента ИЛИ, причем блок регистровой памяти содержит входной и выходной мультиплексоры, первый, второй, третий и четвертый регистры, информационный вход первого регистра является третьим информационным входом блока, а выход первого регистра является третьим выходом блока 1 подключен к первому информационному входу входного мультиплексора, выход которого подключен к информационному входу второго регистра, выход которого является четвертым выходом блока, первым инфор35

0

мационным входом которого являются соединенные между собой второй информационный вход входного мультиплексора и информационный вход третьего регистра, выход которого является первым выходом блока и подключен к первому информационному входу выходного мультиплексора, выход которого является вторым выходом блока, вто- рым информационным входом которого являются соединенные между собой третий информационный вход входного мультиплексора и информационный вход четвертого регистра, выход которого подключен к второму информационному входу выходного мультиплексора, тактовые входы с первого по четвертый регистров, управляю1 щй вход выходного и первый и второй управляю дие входы выходного мультиплексоров являются соответственно с первого по седьмой входами синхронизации группы блока

2е 30 Z9

J/ W J/

ф ф ф ф

w t/s че 9 71

Фи.1

28 о 30

Фиг. I

29

Авторы

Даты

1989-11-23—Публикация

1988-04-25—Подача