113

изобретение относится к электротехнике и может бБ1ть использовано для создания образцовых источников параметров качества трехфазной сети. Целью изобретения является автомаизация процесса амплитудно-фазовой имметрии и повьтение точности восроизведения параметров качества выходного напряжения,

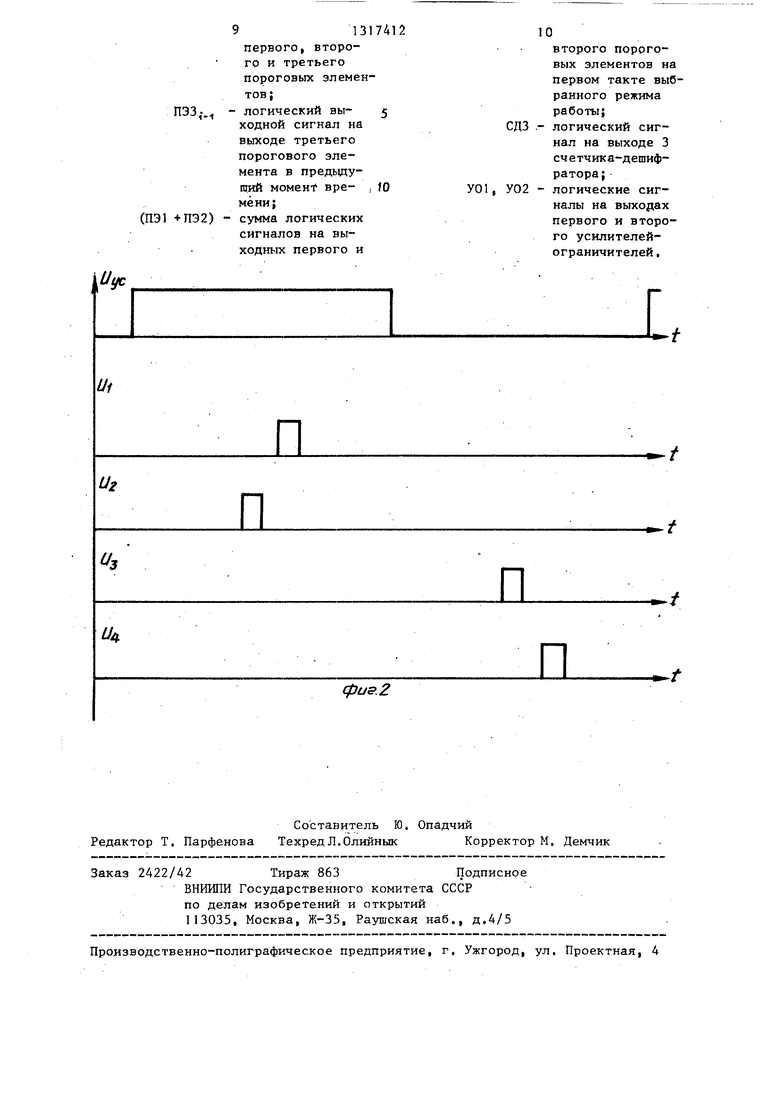

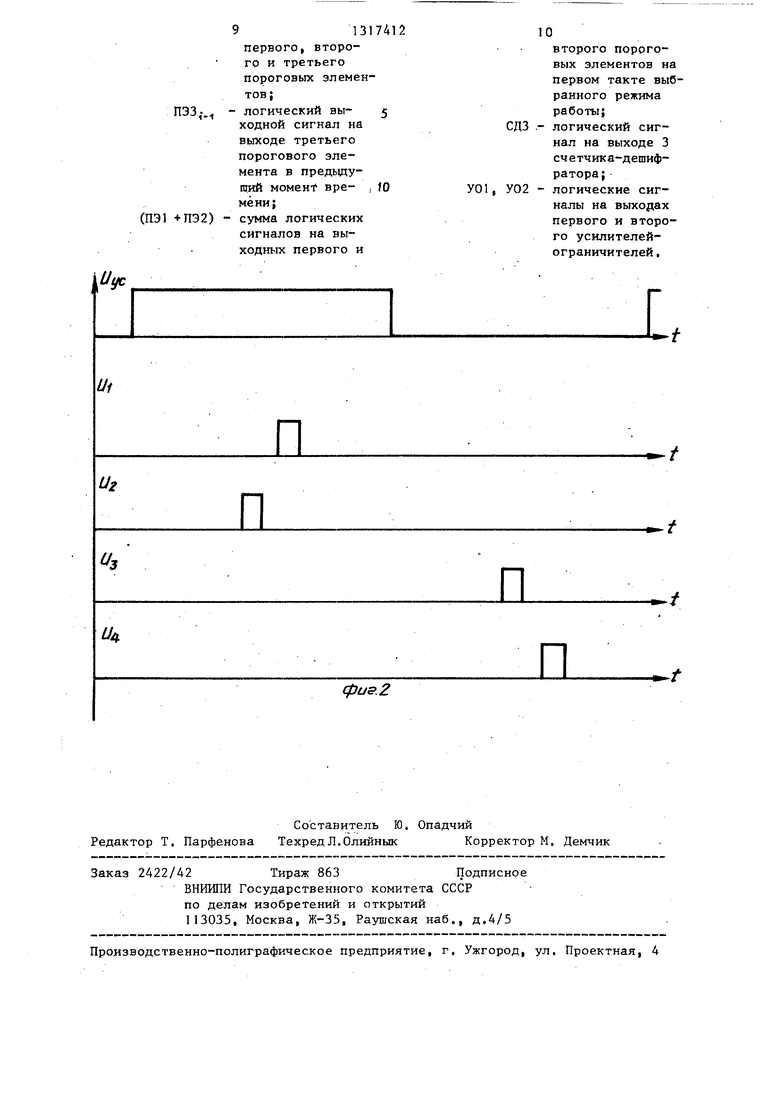

На фиг. приведена структурная схема предлагаемой стабилизированной трехфазной системы питания; на фиг,2- временные диаграммы, поясняющие рабо- ту блока синхронизации,

Устройство содержит преобразователь 1 однофазного напряжения в трехфазное с нулевым проводом (ПН), в цепь каждой фазы которого включены последовательно соединенные регулируемые фазовращатели (РФВ) 2-4, дополнительные регулируемые делители напряжения (ДЦН) 5-7, стабилизаторы (СПН) 8-10 первой гармоники переменного напряжения с трансформаторным выходом и основные регулируемые де-. лители напряжения (ОДН) П-13, входы и выходы которых через переключатель (ПЕР) 14 подключаются к узлу индикатора симметрии (ИС) 15, а также избирательный узел сравнения (ИУС) 16, один вход которого соединен с выходом опорного элемента 17 ц содержащего усилитель-ограничитель (УО) 18, выход которого подключен к управляющему входу прерывателя (ПР) 19, и источник опорного напряжения (ПОН) 20, выход которого соединен с входом ПР 19, выход ПР 19 является выходом опорного элемента 17. Выходы ОДН 11-13 соединены с информационными входами коммутатора (К) 21, выход которого подключен к второму входу ИУС 16 и к входу УО 18 опорного элемента 17. Выход ИУС 16 соединен с первым входом сумматора 22 и через аналоговое запоминающее устройство (АЗУ) 23 с вторым входом сумматора 22, а также с входами первого 24 и второго 25 пороговых элементов (ПЭ). Вход третьего ПЭ 26 соединен с выходом сумматора 22, а выходы всех ПЭ 24 - 26 через регистр (РГ) 27 подключены к информационным входам блока управления (БУ) 28, соединены соответственно со входами +1 и -1 пяти реверсивных счетчиков (PC) 29- 33 параллельно, выход V, соединен с входом первого PC 29, выход „- с

22

входом V второго PC 30, а выход Сч - с входом счетчика дешифратора (СчДС) 34, нулевой выход которого подключен параллельно к входу третьего PC 31

и первому управляющему входу К 21, первый выход - к входу V четвертого PC 32 и второму управляющему входу К 21 , второй выход- к входу Vпятого PC 33 и третьему управляющему входу К

21, выход 3 - к четвертому управляющему входу К 21, первому управляющему входу БУ 28, прямому и инверсивному входам логического блока (ЛБ) 35 и управляющему входу УО 18. Первый

информационный вход ЛБ 35 соединен с выходом УО 18 опорного элемента 17, второй информационный вход через УО 36 - с выходом одного из ОДН 13, а выход ЛБ 35 подключен к входу блока

синхронизации (БС) 37, первый выход которого соединен с управляющим входом АЗУ 23, второй выход - с управляющим входом РГ 27, третий и четвертый выходы - с вторьгм и третьим управляющими входами БУ 28 соответственно, Выходы PC 29-33 подключены к цифровым входам соответствующих циф- роаналоговых преобразователей (ЦАП ) 38-42. Управляющие входы второго и

третьего РФВ 3 и 4 соединены через свои ПАП 38 и 39 и 90°-ные фазовращатели 43 и 44 с выходами соответствующей фазы преобразователя 1. Управляющие входы СПН 8-10 соединены

через свои ЦАП с выходами ДЦН 5-7. Устройство работает следующим образом.

Выходной трехфазный сигнал преобразователя 1 однофазного напряжения трехфазное через РФВ 2-4 и ДДН 5- 7 поступают на СПН 8-10 амплитуды первой гармоники переменного напряения с трансформаторными выходами.

Углы сдвига фаз между выходными напряжениями СПН 8-10 определяются уровнем напряжения науправляющих входах торого и третьего РФВ 3 и 4, а уровень амплитуды выходных напряжений напряжением на управляющих входах ПН 8-10 и в начале работы могут не соответствовать номинальным значеним. Отработка номинального уровня мплитуды первой фазы начинается в

тот момент, когда СчДС 34 устанавлиается в состояние О, Сигнал на вы- оде О СчДС 34 поступает на первый управляющий вход К 21, в результате его К 21 подключает выход ОДН 11 к

313

входу ИУС 16 и опорного элемента 17, Сигнал, пропорциональный разнице амплитуд опорного напряжения и напряжения первой гармоники на выходе первой фазы устройства, поступает на ПЭ 24 и 25, первьй из. которых (24 ) настроен на положительньш знак разности сравниваемых напряжений, а другой (25) - на отрицательный. Импульсом управления со второго выхода БС 37 состояние пороговых элементов записывается в РГ 27, выходные сигналы которого поступают на входы БУ 28. Если разность опорного и выходного напряжения фазы положительна, 28 вырабатьгеает сигнал на йьгходе +1 , если отрицательна - то на выходе -1. Сигналы с выходов +1 и -1 БУ 28 поступают на входы +1 и -1 всех PC 29- 33, но так как .счетчик-дешифратор находится в состоянии О, то р данном случае работает только PC 31, который с помощью ЦАП 40 меняет уровень напряжения на управляющем входе СПН 8, что, в свою очередь, приводит к изменению уровня выходного напряжения на выходе СПН 10, Процесс повторяется до тех пор, пока сигнал разности на выходе избирательного узла сравнения не станет по модулю меньше, чем порог срабатывания ПЭ 24 и. 25. Б этом случае БУ 28 вырабатывает сигнал на выходе Сч, под действием которого СчДС 34 перейдет в новое состояние - 1, Б этом случае элементы избирательной обратной связи - ИУС 16, опорный элемент 17, ПЭ 24 и 25, PC 32, ЦАП 41 - включаются на ртработку номинального уровня амплитуды первой .гармоники второй фазы, бтработка номинального уровня ампли- .туды первой гармоники третьей фазы -начнется после того, как под действием сигнала на выходе Сч БУ 28 СчДС 34 перейдет в состояние 2.

Точность установки номинального уровня амплитуд выходных напряжений зависит от коэффициента усиления ИУС

16и порога срабатывания ПЭ 24 и 25, при этом использование одного, общего для всех фаз, опорного элемента

17со своим источником ПОН 20 позволяет получать строго идентичные по уровню с амплитуды выходные напряжения .

При переходе СчДС 34 в состояние 3 устройство переходит в режим установления фа зовой симметрии трехфаз-

24

ной системы напряже 1ий. Алгоритм работы устройства в этом режиме следующий. Под действием сигнала на выходе 3 СчДС 34 все информационные

входы К 21 подключаются к его выходу, запирается УО 18 опорного 17 элемента, ЛБ 35 переключает вход блока синхронизации на выход УО 36, связанного с выходом ОДН 13 одной из

фаз устройства, блок управления на выходе- ц формирует потенциал , разрешающий работу PC 29, В результате этого на первый вход ИУС 16 поступает сумма напряжений трехфазной системы; на второй вход поступает нулевой потенциал. Сумма равных по амплитуде напряжений равна нулю только в случае полной фазовой симметрии системы. Б противном случае, ПЭ 24 или

25 фиксируют ненулевой сигнал на вы- . ходе ИУС 16. После записи состояния ПЭ в РГ 27 аналоговое запоминающее устройство под действием сигнала с выхода БС 37 фиксирует уровень сигнала ошибки -симметрирования на выходе ИУС 16. Далее, под действием сигнала с выхода 3 БС 37 БУ 28 анализирует состояние РГ 27, при этом, если ср.аботал один из ПЭ 24 и 25,

то.БУ 28 формирует, на выходе +1 или -1, соответственно, импульс, изменяющий состояние PC 29, в противном случае - ПЭ 24 или 25 не сработали ввиду нулевого значения сигнала ошибки симметрирования - БУ 28 на выход Сч формирует сигнал, который перево; дит СчДС 34 в состояние О - режим стабилизации амплитуды первой фазы.

Изменение состояния PC 29 приво-- дит к изменению уровня напряжения на выходе ЦАП 38, которое повернут.о на 90° фазовращателем 43 относительно напряжения, действующего на входе

РФБ 3. В результате этог.о изменяется начальная фаза напряжения на выходе РФБ 3 и соответственно на выходе СПН 9, что в свою очередь приводит к изменению суммарного сигнала на

выходе ИУС 16, Этот сигнал сравнивается на сумматоре 22 с предыдущим значеним сигнала ошибки симметрирования, которое хранится в АЗУ 23, Если изменение состояния PC 29 прквело к уменьшению сигнала ошибки симметрирования, то сумматор 22 формирует сигнал, от которого срабытывает ПЭ 26, в противном случае ПЭ 26 остается в нулевом состоянии.

51

После очередного запуска БС 37 сигналом с выхода УО З б в РГ 27 записывается состояние ПЭ 24-26, затем АЗУ 23 фиксирует новое значение сигнала ошибки. Если в результате предыдуще- го изменения фазы выходного напряжен ния сигнал ошибки уменьшился до нуля (ЛЭ 24 и 25 не сработали), то БУ 28 формирует сигнал на выходе Сч. Если сигнал ошибки уменьшился, но не до нуля (сработал ПЭ 26), то ЕУ 28 формирует сигнал на тот же вход PC 29, что и в предьщущем случае, Если сигнал ошибки увеличился, то БУ 28 формирует сигнал на другой вход PC 29.

Изменение начальной фазы напряжения на выходе СПН 9 в выбранном направлении продолжается до тех пор, пока сигнал на выходе ИУС I6 не станет равным нулю, либо повторно начнет увеличиваться, В последнем случае БУ 28 снимает разрешающий сигнал с выхода Lf и подает его на выход 1 , что приводит, к отпиранию PC 30, управляющего начальной фазой напряжения .на выходе СПН 10. Изменение состояния PC 30 происходит по описанному алгоритму до тех пор„ пока сигнал на выходе ИУС 16 не станет равным нулю либо изменение кода PC 30 как в сторону уменьшения, так и увеличения будет увеличиваться сигнал на выходе ИУС 16. В случае повторного увеличения сигнала на выходе ИУС 16 при регулировании фазы напряжения на выходе СПН 10 БУ 28 вновь переключается на управление фазы напряжения на выходе СПН 9, Таким образом, путем поочередной регулировки фазы напряжений, регулируемых РФБ 3 и 4, система выходны.х напряжений устройств в конце концов установится в симметричное состояние. Под действием нулевого сигнала на выходе ИУС 16 БУ 28 сигналом с выхода 4 блока синхрони- зации устанавливается в исходное состояние и переходит из режима установления фазовой симметрии в режим контроля номинального уровня амплитуды

выходных напряжений устройства.

Б соответствии с описанным алгоритмом работы БУ 28 на своих выходах реализует следующие функции:

+ ПЭ1 (СДЗ+ПЭЗ-СДЗ+(ПЭ1+ПЭ2)) н

+ПЭ2ПЭа(ПЭ1+ПЭ2), СД3;

(СДЗ-нПЭЗ.СДЗ+(ПЭ1+ПЭ2),)+

+ПЭШЭЗ(ПЭ1+ПЭ2)СДЗ;

0

5

О -5

0 5 0 5

0

5

L ПЭЗ,.., n33-if2;

пэТ,-., йэз - , Up TisiT- пэТ,

где ПЭ1, ПЭ2, ПЭЗ.- состояние ПЭ

24-26 соответственно в текущий момент времени;

ПЭЗ-. - состояние ПЭ 26 в предыдущий момент времени; (ПЭ1+ПЭ2) - состояние ПЭ 24 и 25 на первом такте выработанного режима работы устройства; СДЗ - состояние выхода 3 счетчика дешифратора 34,

Приведенные функции позволяют методами формальной логики реализовать БУ 28.

ЛБ 35 реализует функцию вида

ЛС У018-СДЗ + У036-СДЗ

где У018, У036 - сигналы с выходов

УО 18 и 36 соответственно.

Формула изобретения

Стабилизированная трехфазная система питания, содержащая преобразователь однофазного напряжения в трехфазное с нулевым проводом, входом подключенным к входным клеммам, в цепь каждой выходной фазы которого включены последовательно соединенные регулируемые фазовращатели, дополнительные регулируемые делители напряжения, стабилизаторы первой гармоники переменного напряжения с трансформаторным выходом, подсоединенные к выходным клеммам, и основные регулируемые делители напряжений, входы и выходы которых через переключатель подключены к узлу индикации симметрии, а также избирательный узел сравнения, один вход которого соединен с первым выходом опорного элемента, отличающая- , с я тем, что, с целью автоматизации процесса амплитудно-фазовой симметрии и повьш1ения точности воспроизведения параметров качества выходного напряжения, в нее введены коммутатор,

713

информационные входы которого подсоединены через резисторы к выходам основных регулируемых делителей напряжения, а выход соединен с первым входом опорного элемента и параллельно с вторым входом избирательного узла сравнения, сумматор, один вход которого непосредственно, а другой через введенное аналоговое запоминающее устройство соединены с выходом избирательного узла сравнения, три пороговых элемента, первые два из которых своими входами подключены к выходу избирательного узла сравнения, вход третьего порогового элемента подключен к выходу сумматора, а выходы пороговых элементов -через введенный регистр подключены к информационным входам введенного блока управления, выходы +1 и -1 которой соединены соответственно с входами +1 и -1 пяти введенных реверсивных счетчиков параллельно, выход tfl соединен с входом V первого реверсивного счетчика, выход ц2 соединен с входом V второго реверсивнога счетчика, д выход Сч соединен с входом введенного счетчика-дешифратора, нулевой выход которого подключен параллельно к входу V третьего реверсивного счетчика и первому управляющему входу коммутатора, первый выход счетчика- дешифратора подключен к ВХОДУ четвертого реверсивного счетчика и второму управляющему входу коммутатора, второй выход счетчика-дешифратора подключен к входу V пятого реверсивного счетчика и третьему управляющему входу коммутатора, а третий выход счетчика-дешифратора подключен к четвертому управляющему входу коммутатора, второму входу опорного элемента, первому управляющему входу блока управления и прямому и инверсному входам введенного логического блока, первый информационный вход которого соединен с вторым выходом опорного элемента, а второй информационный вход через Первый введенный усилитель-ограничитель соединен с выходом одного из основных регулируемых делителей напряжения, а выход логического элемента соединен с входом введенного блока синхронизации, первый выход которого подключен к управляющему входу аналогового запоминающего устройства, второй выход подключен к управляющему входу регистра, а третий и четвертый выходы подключены к

8

второму и третьему управляющим входам блока управления соответственно, при этом выходы реверсивных счетчиков соединены с цифровыми входами

соответствующих введенных цифроана- логовых преобразователей, управляю- щие входы второго и третьего регулируемых фазовращателей соединены через последовательно включенные свои

цифроаналоговые преобразователи и введенные 90 -ные фазовращатели с выходами соответствующей фазы преобразователя однофазного напряжения в трехфазное, а управляющие входы

стабилизаторов первой гармоники соединены через свои цифроаналоговые преобразователи с выходами дополнительных делителей напряжения, опорный элемент включает в себя второй

усилитель-ограничитель, информационный вход которого соединен с первым входом опорного элемента а вход управления подключен к второму входу опорного элемента, выход второго

усилителя-ограничителя подключен к входу управления прерывателя и второму выходу опорного элемента, и источник опорного напряжения, выход которого через прерыватель подсоединен к первому выходу опорного элемента, причем блок управления реализует получение выходных сигналов по следующим логическим законам: по выходу +1

(СДЗ+ПЭЗ СДЗ+(ПЭ1+ПЭ2)у)+

40

+ ПЭ2-ПЭЗ(ПЭ1+ПЭ2)-СДЗ, по выходу -1

(СДЗ+ПЭЗ-СДЗ+(ПЭ1+ПЭ2))+

+ПЭ1-ПЭ1 (ПЭ1+ПЭ2)-СДЗ, по выходу 1/

1/, n33;,,n33-Lf , по выходу Lf

ПЭЗ; ПЭЗ - с/,

по выходу Сч

ПЭ1-ПЭ2,

логический элемент реализует следующий закон:

аых У02-СДТ+ У01-СДЗ,

где ПЭ1, ПЭ2, ПЭЗ - логические выходные сигналы соответственно

91317412

первого, второго и третьего пороговых элементов;

ПЭЗ-. логический вы- 5 ходной сигнал на выходе третьего порогового элемента в предьоду- щий момент вре- , 10 мёни;

Э +ПЭ2) - сумма логических сигналов на выходных первого и

Uyc

иг

и

иц.

cf)uff.2

Составитель Ю. Опадчий Редактор Т. Парфенова Техред Л.Олийнык Корректор М. Демчик

Заказ 2422/42 Тираж 863Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

10

второго пороговых элементов на первом такте выбранного режима работы;

СДЗ .- логический сигнал на выходе 3 счетчика-дешифратора;

01, У02 - логические сигналы на выходах первого и второго усилителей- ограничителей I

2

| название | год | авторы | номер документа |

|---|---|---|---|

| Разряд троичного комбинационного вычитателя | 1973 |

|

SU450165A1 |

| ТРОИЧНЫЙ ПОТЕНЦИАЛЬНЫЙ ТРИГГЕР | 1973 |

|

SU369715A1 |

| УСТРОЙСТВО И СПОСОБ УПРАВЛЕНИЯ САМОЧУВСТВИТЕЛЬНЫМ УЛЬТРАЗВУКОВЫМ ПЬЕЗОЭЛЕКТРИЧЕСКИМ ДВИГАТЕЛЕМ | 2015 |

|

RU2631332C2 |

| Способ декодирования информации с использованием свёрточных кодов | 2016 |

|

RU2637487C1 |

| Устройство для цифрового задания трехфазного напряжения | 1987 |

|

SU1728944A1 |

| Измеритель параметров качества электроэнергии трехфазной сети | 1979 |

|

SU1164616A1 |

| Цифровой измеритель температуры | 1984 |

|

SU1242725A1 |

| СПОСОБ КОРРЕКТИРОВКИ ХАРАКТЕРИСТИКИ ДАТЧИКА УГЛА ПОВОРОТА РЕЗИСТОРНОГО ТИПА | 2001 |

|

RU2199756C2 |

| Способ построения коммутируемой вибраторной антенны | 2022 |

|

RU2807422C1 |

| УСТРОЙСТВО ЗАЩИТЫ ОБМОТОК ОДНОФАЗНОГО ТРАНСФОРМАТОРА ОТ ПОВРЕЖДЕНИЙ | 2016 |

|

RU2638299C2 |

Изобретение относится к электротехнике и может быть использовано для образцовых источников параметров качества трехфазной сети. Цель изобретения - повышение точности воспроизведения параметров качества выходного напряжения. В устр-во.введены коммутатор 21, сумматор 22, пороговые элементы 24 - 26, аналоговое запоминающее устройство 23, регистр 27, счетчик-дешифратор 34, усилитель-ограничитель 18, логический блок 35, блок синхронизации 37, цифроаналого- вые преобразователи 38-42 и 90традус- ные фазовращатели 43 и 44. Цель достигается также определенным схемным по с тро- ением опорного элемента 17, а также KOHKpeTHbW логическим законом, которые реализует блок управления. 2 ил. СЛ CAD 1 ND

| Стабилизированная трехфазная системапиТАНия | 1978 |

|

SU849165A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Стабилизированная трехфазная система питания | 1981 |

|

SU983673A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1987-06-15—Публикация

1986-01-23—Подача