vj Ю 00 ЧЭ

J

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРОГРАММИРУЕМОЕ УСТРОЙСТВО ДЛЯ ЛОГИЧЕСКОГО УПРАВЛЕНИЯ ЭЛЕКТРОПРИВОДАМИ И СИГНАЛИЗАЦИЕЙ | 1996 |

|

RU2117978C1 |

| СПОСОБ УПРАВЛЕНИЯ ТРЕХФАЗНЫМ МОСТОВЫМ ПРЕОБРАЗОВАТЕЛЕМ | 2007 |

|

RU2379819C2 |

| УСТРОЙСТВО ХРАНЕНИЯ И СЧИТЫВАНИЯ ИНФОРМАЦИИ С КОРРЕКЦИЕЙ ОДИНОЧНЫХ ОШИБОК | 2023 |

|

RU2816550C1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В ИНТЕРВАЛ ВРЕМЕНИ | 2004 |

|

RU2263321C1 |

| СПОСОБ ПРЕОБРАЗОВАНИЯ НАПРЯЖЕНИЯ | 2001 |

|

RU2215363C2 |

| Цифровое устройство для управления тиристорным выпрямителем | 1991 |

|

SU1799494A3 |

| ПРОГРАММИРУЕМОЕ УСТРОЙСТВО ДЛЯ ЛОГИЧЕСКОГО УПРАВЛЕНИЯ ЭЛЕКТРОПРИВОДАМИ И СИГНАЛИЗАЦИЕЙ | 1994 |

|

RU2095846C1 |

| СИСТЕМА КОММУТАЦИИ ПРОЦЕССОРНЫХ ЭЛЕМЕНТОВ | 1992 |

|

RU2126990C1 |

| Цифровая система управления | 1986 |

|

SU1357917A1 |

| УСТРОЙСТВО ВВОДА-ВЫВОДА ИНФОРМАЦИИ ДЛЯ СИСТЕМЫ ЦИФРОВОГО УПРАВЛЕНИЯ | 1993 |

|

RU2042183C1 |

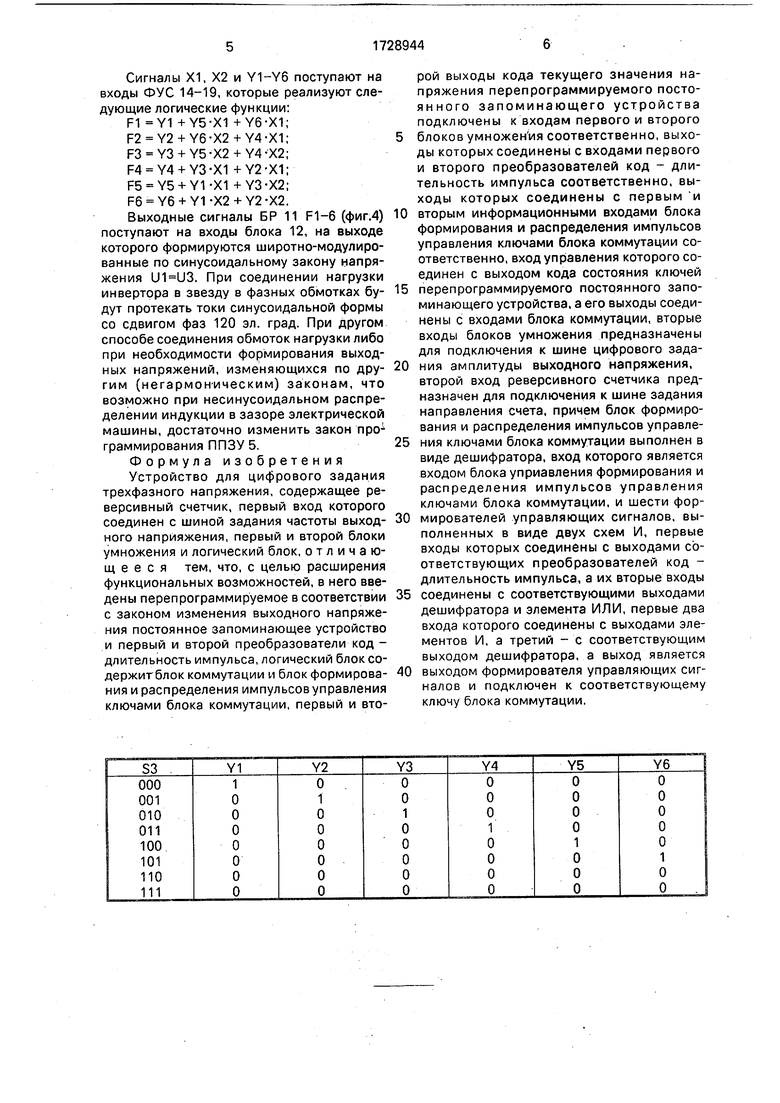

Изобретение относится к преобразовательной технике и может быть использовано в следяще-регулируемых электроприводах, которые управляются от цифровых вычислительных устройств, для преобразования постоянного напряжения в трехфазное переменное, амплитуда и частота которого задаются в цифровом виде. Целью изобретения является повышение точности задания выходного напряжения и расширение функциональных возможностей устройства за счет обеспечения задания любой формы выходного напряжения. Цель достигается введением программируемого постоянного запоминающего устройства 5, закон программирования которого определяет форму выходного напряжения. Амплитуда и частота выходного напряжения задаются поступающими извне сигналами, которые определяют параметры сигналов на выходах реверсивного счетчика 4 и блоков умножения 6 и 7. Управление силовой частью устройства, выполненной в виде блока коммутации 12, осуществляется блоком формирования и распределения импульсов управления ключами блока коммутации 11. 4 ил. Ё

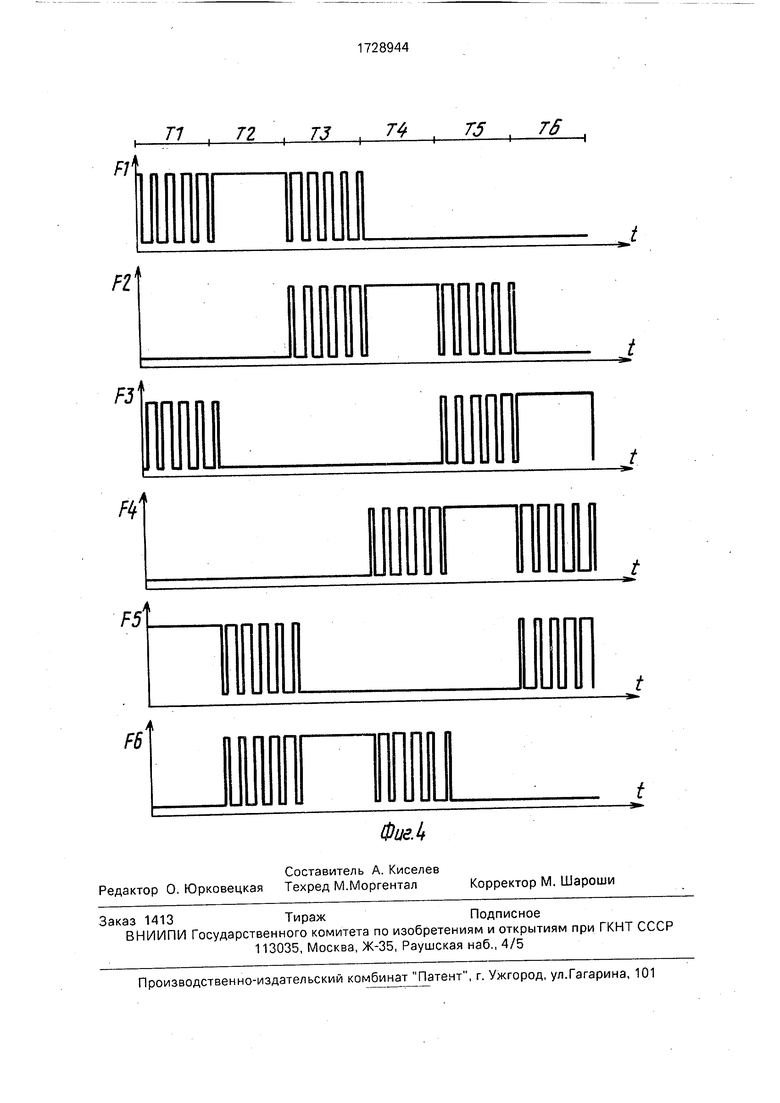

Фиг.1

Изобретение относится к преобразовательной технике и может быть использовано в следяще-регулируемых элеткроприводах, которые управляются от цифровых вычислительных устройств, для преобразования постоянного напряжения в трехфазное переменное выходное напряжение, регулируемое широтно-импульсным методом.

Цель изобретения - расширение функциональных возможностей, что способствует повышению КПД привода.

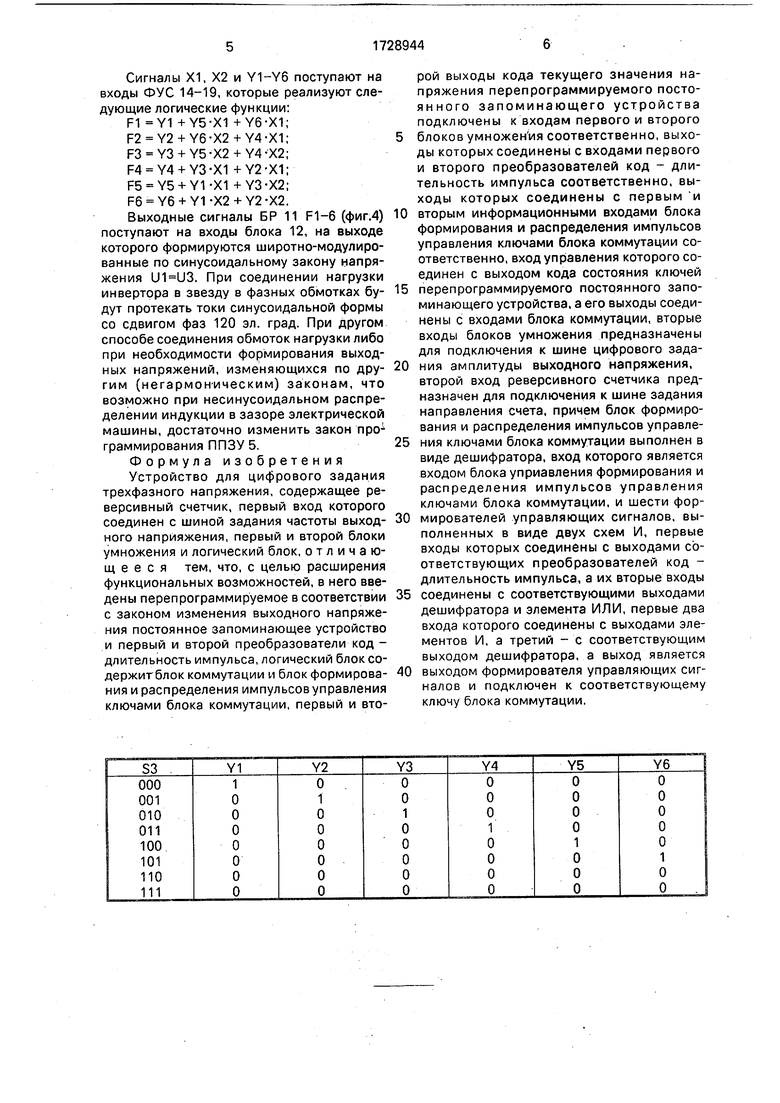

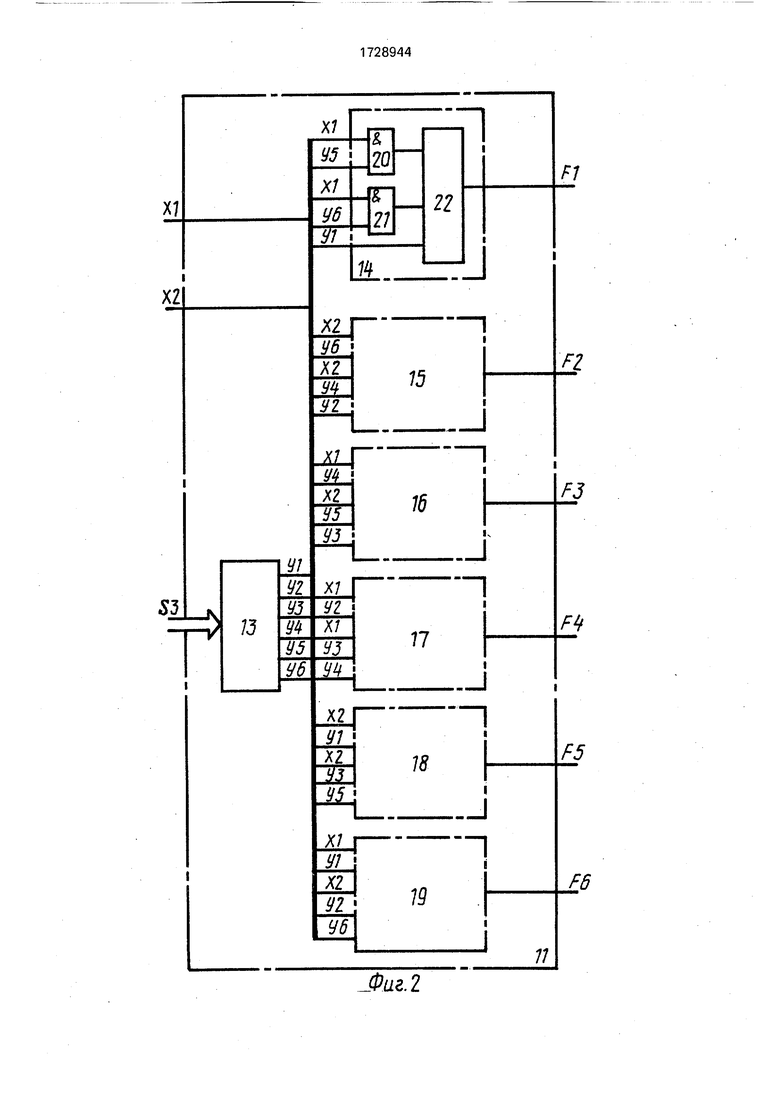

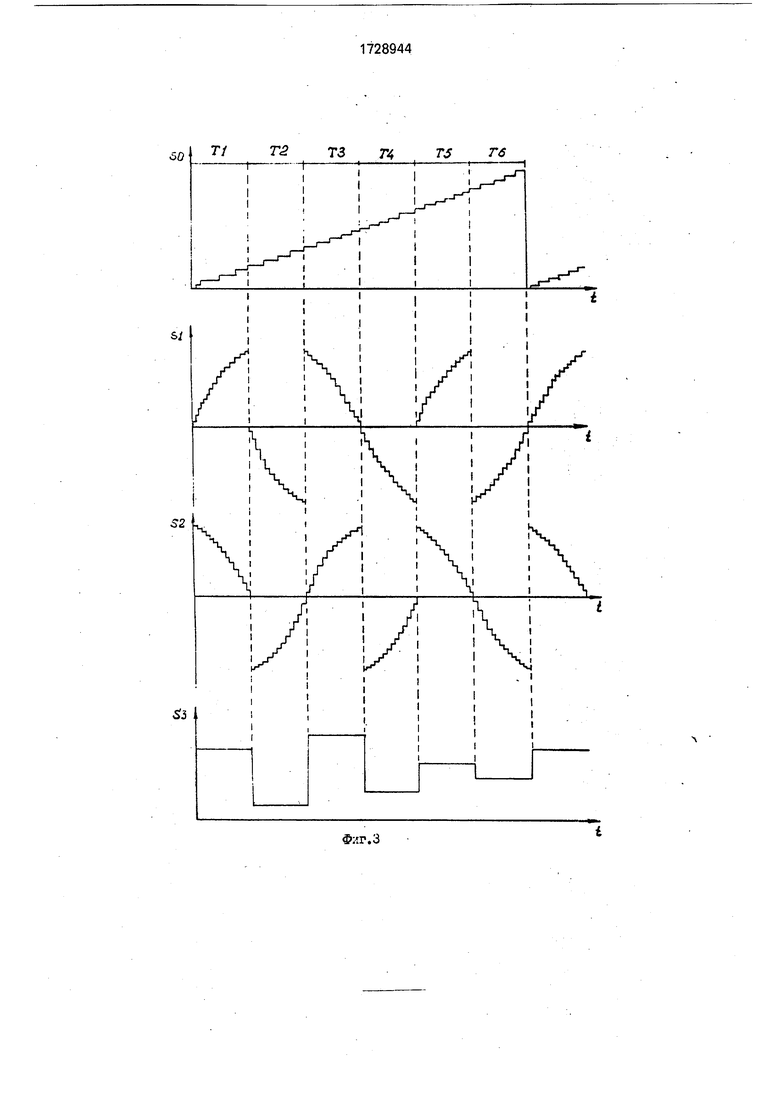

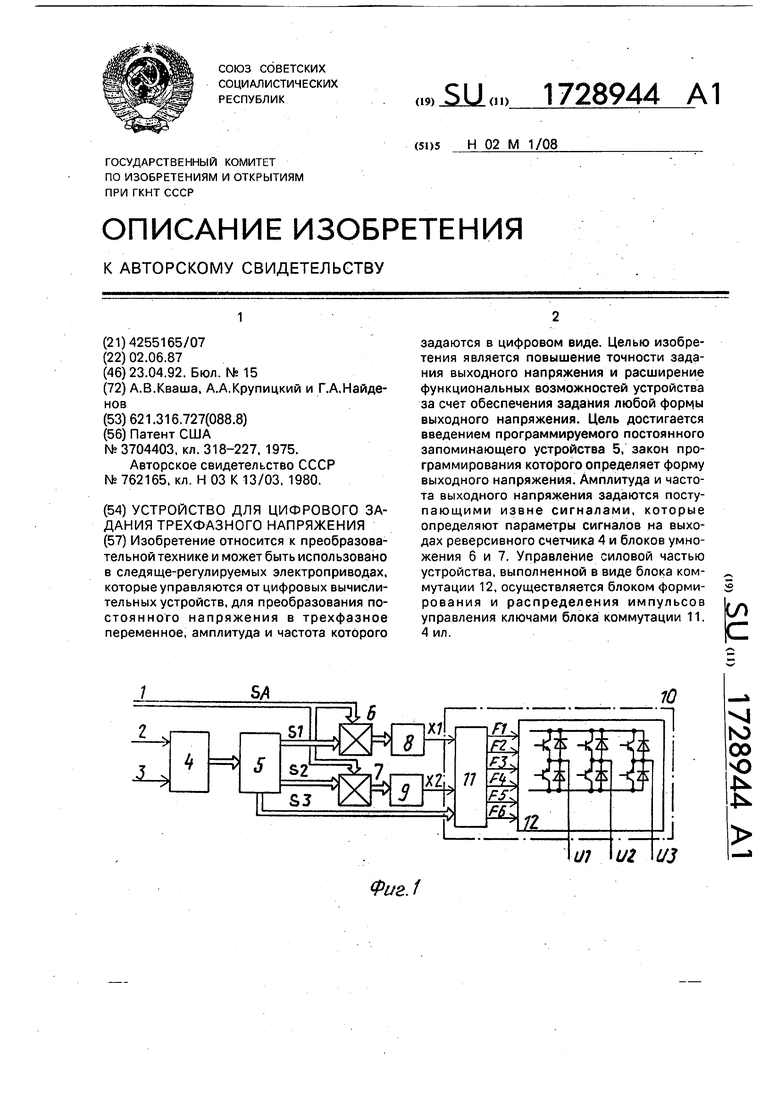

На фиг.1 приведена структурная схема предлагаемого устройства; на фиг.2 - структурная схема блока формирования и распределения импульсов управления ключами; на фиг.З - пример закона программирования перепрограммируемого постоянного запоминающего устройства для формирования выходных наприяжений, модулированных по гармоническому закону; на фиг.4 - временные диаграммы работы логического блока.

Устройство содержит шину 1 задания амплитуды выходного напряжения, шину 2 задания направления счета, шину 3 задания частоты выходного напряжения, реверсивный счетчик 4 (PC), перепрограммируемое постоянное запоминающее устройство 5 (ППЗУ), первый и второй блоки 6 и 7 умножения (БУ), первый и второй преобразователи 8 и 9 код - длительность импульса (ПКДИ), логический блок 10 (Л Б), блок 11 формирования и распределения импульсов управления (БР) ключами блока 12 коммутации (БК), дешифратор 13, формирователи 14-19 управляющего сигнала (ФУС), первую и вторую схемы И 20 и 21, элемент ИЛИ 22,

На фиг. 1-Й обозначены: SO - выходной код PC 4, S1, S2, S3 - выходные коды ППЗУ 5, SA - код задания амплитуды выходного напряжения, Т1-Т6 - интервалы коммутации, Х1 и Х2.- выходные сигналы первого и второго ПКДИ 8 и 9, Y1-Y6 - выходные сигналы дешифратора 13, F1-F6 - выходные сигналы БР 11, U1-U3 - выходные сигналы БК12.

Шина 3 задания частоты выходного напряжения (фиг.1) соединена с тактовым входом PC 4, вход задания направления счёта которого связан с шиной 2 задания направления, а выходная шина - с входом ППЗУ 5.

Первая и вторая выходные шины ППЗУ

5связаны с первыми входами первого 6 и второго 7 БУ, вторые входы которых соединены с шиной 1 задания амплитуды выходного напряжения. Выходные шины первого

6и второго 7 БУ соединены с входами соответственно первого и второго ПКДИ 8 и 9, выходы которых связаны с первым и вторым входами ЛБ 10. Третий вход ЛБ 10 связан с

третьей выходной шиной ППЗУ 5. Выходами ЛБ 10 являются входы БР 11, выходы которого соединены с входами БК 12, выходы которого являются выходами ЛБ 10. Пер- 5 вый и второй входы БР 11 (фиг.2) являются соответственно первыми и вторыми входами ФУС 14-19, третьи, четвертые и пятые входы которых соединены с соответствующими выходами дешифратора 13, вход кото0 рого является третьим входом ЛБ 10. В состав каждого из ФУС 14-19 входят первая 20 и вторая 21 схемы И и элемент ИЛИ 22. Первые входы схем И 20 и 21 являются первым и вторым входами ФУС 14-19, вторые

5 входы - соответственно третьим и четвертым входами ФУС 14-19, а выходы соединены с первым и вторым входами элемента ИЛИ 22, третий вход которого является пятым входом ФУС 14-19.

0 Устройство работает следующим образом.

PC 4 непрерывно суммирует импульсы, поступающие по шине 3 задания частоты выходного напряжения. При этом на выхо5 дах PC 4 появляется линейно нарастающий (спадающий, в зависимости от сигнала на шине 2 задания направления) цифровой код SO, который при заполнении PC 4 сбрасывается в исходное нулевое (максимальное)

0 состояние. Этот процесс происходит непрерывно.

В зависимости от цифрового кода SO на выходных шинах ППЗУ 5 появляются три цифровых сигнала: на первой и второй ши5 нах - коды текущего значения напряжения S1 и S2, на третьей шине - код состояния ключей S3, определяющий базовый (постоянно открытый) ключ на каждом из интервалов коммутации Т1-Т6.

0 Пример закона программирования ППЗУ 5 для формирования синусоидальной формы выходного сигнала приведен на фиг.З. Сигналы S1 и S2 по выходным шинам ППЗУ 5 поступают на первые входы БУ 6 и

5 7, где происходит их умножение на код амплитуды выходного напряжения SA, поступающий на вторые входы БУ 6 и 7 по шине 1 задания амплитуды выходного напряжения. ПКДИ 8 и 9 преобразуют выходные

0 коды БУ 6 и 7 в импульсные сигналы Х1 и Х2 с фиксированной частотой и длительностью, пропорциональной величине SA-S1 и SA-S2 соответственно. Сигналы Х1 и Х2 поступают на входы 1 и 2 ЛБ 10. На вход 3 ЛБ 10

5 поступает код состояния ключей S3. Дешифратор 13 преобразует этот цифровой код в логические сигналы Y1-Y6.

В таблице приведены выходные сигналы дешифратора в зависимости от S3.

Сигналы Х1, Х2 и Y1-Y6 поступают на входы ФУС 14-19, которые реализуют следующие логические функции:

F1 Y1 + Y5-X1 + Y6-X1;

F2 Y2 + Y6-X2 + Y4-X1;

F3 Y3 + Y5-X2 + Y4-X2;

F4 Y4 + Y3-X1 +Y2-X1;

F5 Y5 + Y1-X1 +Y3-X2;

F6 Y6 + Y1-X2 + Y2-X2.

Выходные сигналы БР 11 F1-6 (фиг.4) поступают на входы блока 12, на выходе которого формируются широтно-модулиро- ванные по синусоидальному закону напряжения . При соединении нагрузки инвертора в звезду в фазных обмотках будут протекать токи синусоидальной формы со сдвигом фаз 120 эл. град. При другом способе соединения обмоток нагрузки либо при необходимости формирования выходных напряжений, изменяющихся по другим (негармон-ическим) законам, что возможно при несинусоидальном распределении индукции в зазоре электрической машины, достаточно изменить закон про- граммирования ППЗУ 5.

Формула изобретения

Устройство для цифрового задания трехфазного напряжения, содержащее реверсивный счетчик, первый вход которого соединен с шиной задания частоты выходного напрйяжения, первый и второй блоки умножения и логический блок, отличающееся тем, что, с целью расширения функциональных возможностей, в него введены перепрограммируемое в соответствии с законом изменения выходного напряжения постоянное запоминающее устройство и первый и второй преобразователи код - длительность импульса, логический блок со- держитблок коммутации и блок формирования и распределения импульсов управления ключами блока коммутации, первый и второй выходы кода текущего значения напряжения перепрограммируемого посто- янного запоминающего устройства подключены к входам первого и второго

блоков умножен ия соответственно, выходы которых соединены с входами первого и второго преобразователей код - длительность импульса соответственно, выходы которых соединены с первым и

вторым информационными входами блока формирования и распределения импульсов управления ключами блока коммутации соответственно, вход управления которого соединен с выходом кода состояния ключей

перепрограммируемого постоянного запоминающего устройства, а его выходы соединены с входами блока коммутации, вторые входы блоков умножения предназначены для подключения к шине цифрового задания амплитуды выходного напряжения, второй вход реверсивного счетчика предназначен для подключения к шине задания направления счета, причем блок формирования и распределения импульсов управления ключами блока коммутации выполнен в виде дешифратора, вход которого является входом блока уприавления формирования и распределения импульсов управления ключами блока коммутации, и шести формирователей управляющих сигналов, выполненных в виде двух схем И, первые входы которых соединены с выходами соответствующих преобразователей код - длительность импульса, а их вторые входы

соединены с соответствующими выходами дешифратора и элемента ИЛИ, первые два входа которого соединены с выходами элементов И, а третий - с соответствующим выходом дешифратора, а выход является

выходом формирователя управляющих сигналов и подключен к соответствующему ключу блока коммутации.

И768Ш

| Патент США № 3704403, кл | |||

| Способ изготовления фасонных резцов для зуборезных фрез | 1921 |

|

SU318A1 |

| Авторское свидетельство СССР № 762165,кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-04-23—Публикация

1987-06-02—Подача