1.

Изобретение относится к импульсно технике и может быть использовано в системах передачи информации с высокой надежностью.

Цель изобретения - повышение надежности устройства путем обеспечения работоспособности при некоторых видах отказов порогового элемента.

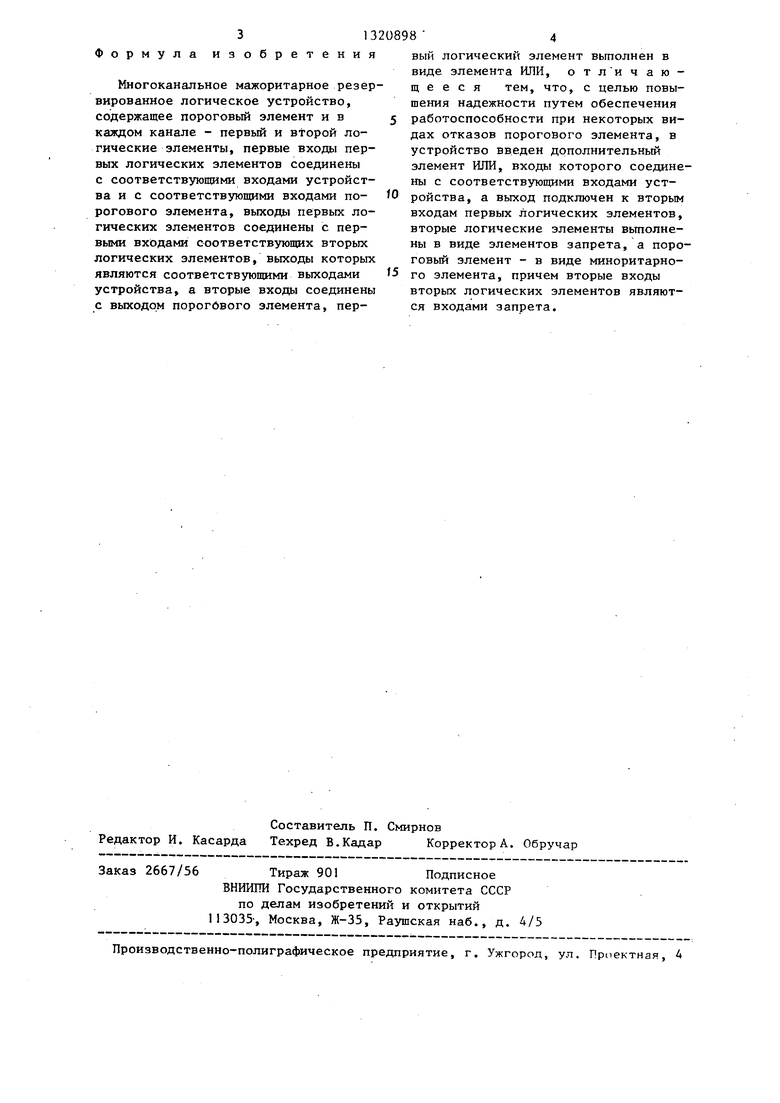

На чертеже представлена функциональная схема многоканального мажоритарного резервированного логического устройства.

Многоканальное мажоритарное резервированное логическое устройство содержит пороговый элемент I и в каждом канале - первьй 2 и второй 3 логические элементы. Первые входы первых логических элементов соединены с соответствующими входами 4 устройства и с соответствующими входами порогового элемента 1.

Выходы первых логических элементов соединены с первыми входами соответствующих вторых логических элементов , выходы которых являются соответствующими выходами 5 устройства, а вторые входы соединены с выходом порогового элемента. Первый логический элемент выполнен в виде элемента ИЛИ, а второй логический элемент - в виде элемента запрета. Устройство также содержит дополнитель- ньш элемент 6 ИШ1, входы которого соединены с соответствующими входами устройства, а выход подключен к вторым входам первых логических элементов. Пороговый элемент выполнен в виде, миноритарного элемента, причем вторые входы вторых логических элементов являются входами запрета.

Миноритарный элемент, использованный в устройстве, реализует пороговую функиш-т вида

О, при (11х;-п)0

П1

У sghCZl Х;-п)

Г1

1 , при (IIx--n) о,

где х - характеристика сигнала на

i-M входе (х; 0 или 1 для i 1 , га);

m - количество входов; п - порог срабатывания. Устройство работает следующим образом.

У82

При исправной работе всех элементов, входящих в состав устройства, и поступлении входной информации без ошибок на всех входах 4 устройства

в каждый момент времени имеются одинаковые потенциалы - либо на всех входах - логический нуль, либо на всех входах - логическая единица. . В первом случае в соответствии с

логической функцией, выполняемой

миноритарным элементом, на его выходе имеется сигнал логической единицы, закрывающий элементы 3 запрета по входу запрета. В этом случае на выходах всех элементов запрета и соответственно на всех выходах устройства имеется потенциал логического нуля.

Во втором случае на выходе миноритарного элемента - потенциал логического нуля, открывающий элементы 3 запрета и разрешающий прохождение сигналов с выходов элементов ИЛИ 2, т.е. на всех выходах устройства - сигнал логической единицы.

При появлении на одном из входов 4 устройства ощибки типа ложного нуля На всех выходах 5 устройства устанавливается логическая единица за счет исправления ошибки правильным сигналом, логической единицы, поступающим на второй вход элементов ИЛИ 2, пришедшим с выхода дополнительного элемента ИЛИ 6. I.

При появлении на одном из входов

4 устройства ошибки типа ложной единицы, на всех выходах элементов

ИЛИ 2 устанавливается сигнал Ложная единица. Однако на выходах 5 устройства устанавливается правильный логический нуль за счет поступления

на вторые входы элементов 3 запрета единичного сигнала с выхода миноритарного элемента.

При отказе элементов ИЛИ 2 и запрета 3 в каналах ошибочные сигналы

в худшем случае могут появиться только на соответствующих выходах устройства, не препятствуя исправлению ошибок, возникающих на других входах стройства.

При отказе миноритарного элемента устройство исправляет ошибки типа ожного нуля. При отказе дополнительного элемента ИЛИ устройство исправяет ошибки типа ложной единицы.

Формула изобретения

Многоканальное мажоритарное резервированное логическое устройство, содержащее пороговый элемент и в каждом канале - первый и второй логические элементы, первые входы первых логических элементов соединены с соответствующими входами устройства и с соответствующими входами порогового элемента, выходы первых логических элементов соединены с первыми входами соответствующих вторых логических элементов, выходы которых являются соответствующими выходами устройства, а вторые входы соединены с выходом порогбвого элемента, пер

вый логический элемент выполнен в виде элемента ИЛИ, отл ичаю- щ е е с я тем, что, с целью повышения надежности путем обеспечения работоспособности при некоторых видах отказов порогового элемента, в устройство введен дополнительный элемент ИЛИ, входы которого соединены с соответствующими входами устройства, а выход подключен к вторым входам первых логических элементов, вторые логические элементы вьтолне- ны в виде элементов запрета, а пороговый элемент - в виде миноритарного элемента, причем вторые входы вторых логических элементов являются входами запрета.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное мажоритарное резервированное логическое устройство | 1979 |

|

SU894870A1 |

| Адаптивное резервированное устройство | 1973 |

|

SU506857A1 |

| Мажоритарное устройство | 1980 |

|

SU892732A1 |

| Трехканальное восстанавливающее резервированное логическое устройство | 1982 |

|

SU1018255A1 |

| Мажоритарное устройство | 1981 |

|

SU991613A2 |

| СПОСОБ КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2011 |

|

RU2450436C1 |

| Мажоритарное устройство | 1983 |

|

SU1094151A1 |

| Резервированное устройство | 1976 |

|

SU608277A1 |

| Устройство для обнаружения и исправления ошибок в блоках памяти | 1988 |

|

SU1525746A1 |

| Способ кодовой цикловой синхронизации для каскадного кода Рида-Соломона и Боуза-Чоудхури-Хоквингема [РС(32,16,17), БЧХ(31,16,7)] при одновременном применении жестких и мягких решений | 2020 |

|

RU2747623C1 |

Изобретение относится к импульсной технике и может быть использовано в системах передачи информации. Цель изобретения - повышение надежности многоканального мажоритарного резервированного логического устройства путем обеспечения его работоспособности при некоторых видах отказов порогового элемента. Устройство содержит пороговый элемент 1 и в каждом канале - логические элементы 2 и 3, входы 4 и выходы 5 устройства. Первый логический элемент выполнен на элементе ИЛИ, второй - в виде элемента запрета. Устройство также содержит дополнительный элемент ИЛИ 6. При отказе элементов 2 и 3 ошибочные сигналы могут появиться только на соответствующих выходах устройства, не препятствуя исправлению ошибок, возникающих на других выходах устройства. В устройстве исправляется также ошибк.а типа ложного нуля, а при отказе элемента ИЛИ 6 исправляется ошибка типа ложной единипы. 1 ил. а 9 (Л i-I 5.2 5.т-1 с tsD О СХ) со 00

| Многоканальное восстанавливающее логическое устройство | 1982 |

|

SU1061262A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Многоканальное мажоритарное резервированное логическое устройство | 1979 |

|

SU894870A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-06-30—Публикация

1985-04-01—Подача