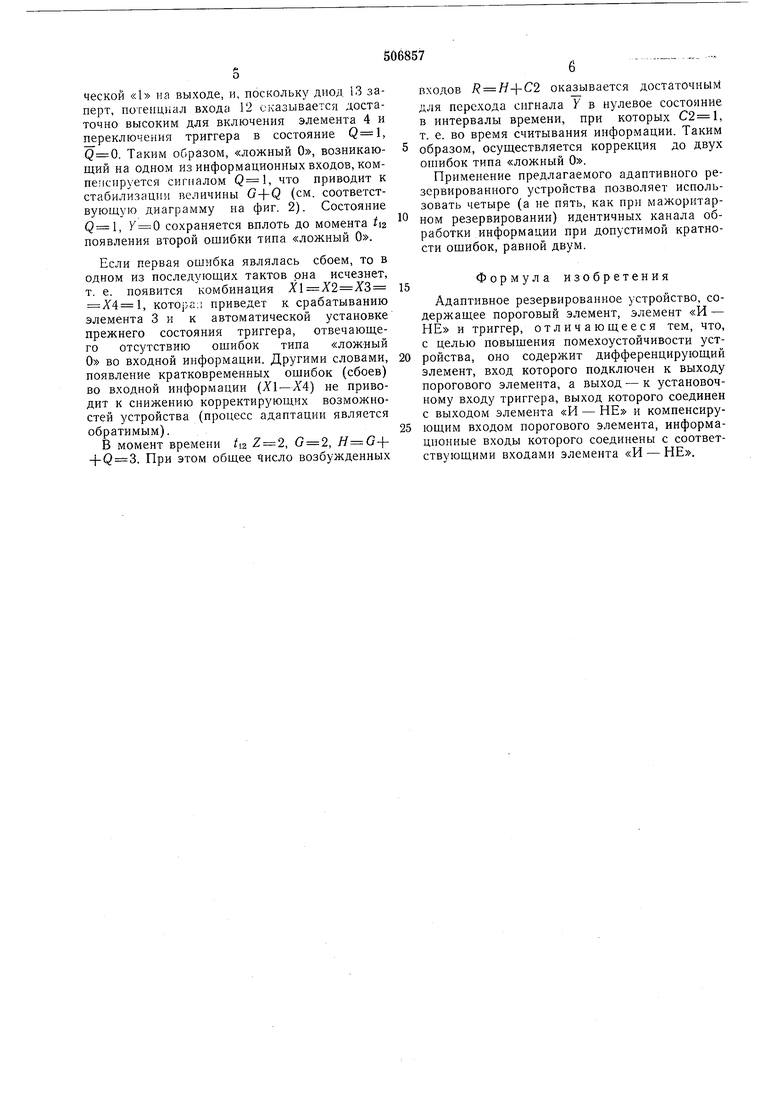

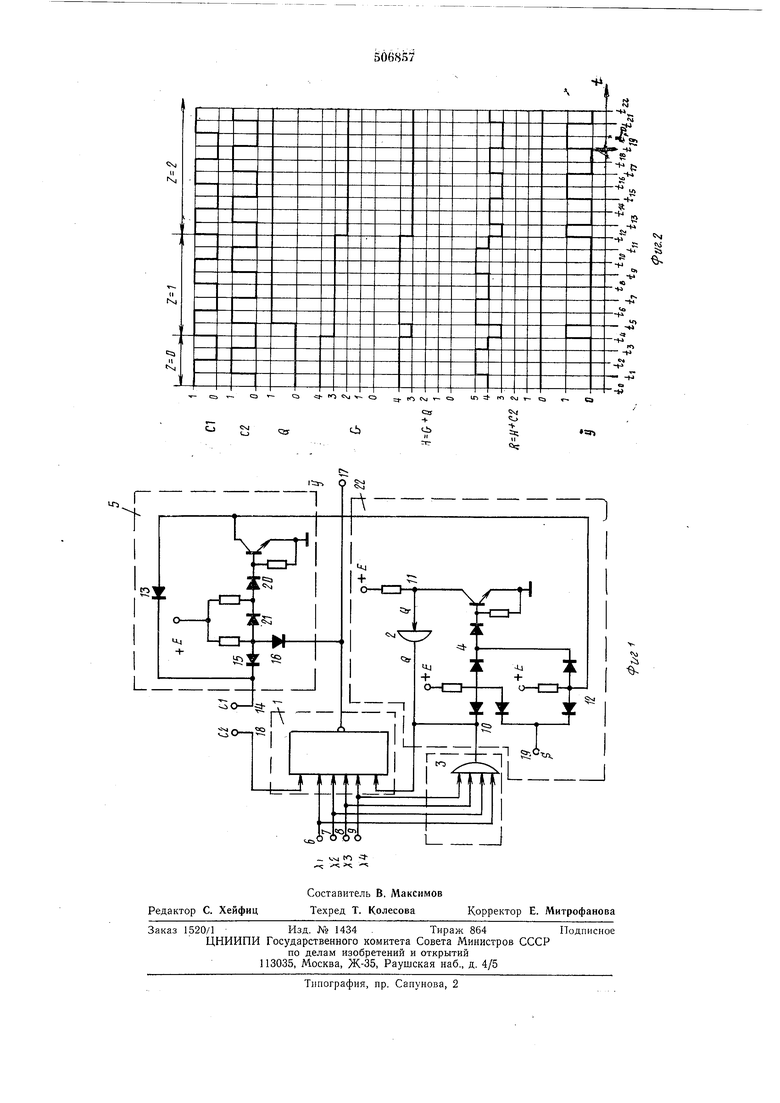

Условием правильного функционирования устройства является ординариость потока отказов типа «ложный О. Эго означает, что время между появлением двух постоянных ошибок типа «ложный О на различных входах устройства должно быть достаточно большим для обнаружения первой из этих ошибок, а именно, за это время на входах устройства должна хотя бы один раз появиться информация, соответствующая логической единице, т. е. на всех информационных входах, кроме неисправного, должны появиться логические единицы. Другими словами, одиовремениое появление двух ошибок типа «ложный О на входах устройства недопустимо. Подобное ограничение по отношению к ошибкам типа «ложная 1 отсутствует. Во всех случаях принимается, что логическому «О соответствует близкий к нулю потенциал, а логический «1 - высокий цоложительный потенциал. Устройство приводится в исходное состояние кратковременным воздействием сигнала на вход 19 начальной установкн устройства. При этом сигналы на выходах 10 и 11 равны нулю и единице, соответственно (Q 0, ). Синхронизация устройства может осуществляться сериями импу;1ьсов С1 и С2 (см. фиг. 2), подаваемыми, соответственно, на входы 14 и 18. Входная информация (XI-.Y4) подается на входы устройства в моменты, соответствующие ноложительным фронтам импульсов С1 (to, /4, 8, , tie и т. д.) и фиксируется на время, равное периоду тактовых импульсов. Пороговый элемент 1 вырабатывает на выходе 17 сигнал логического нуля только в тех случаях, когда число возбужденных входов (т. е. входов, на которые поданы логические единицы) равно или превышает величину порога Т, равную четырем. Исправленная инверсная информация (сигнал У) может быть считана с выхода устройства в интервалы времени, когда . Рассмотрим случай, соответствующий постоянной входной информации при отсутствии ошибок типа «ложная 1. В этом режиме сигнал на выходе устройства Y соответствует инверсному значению любого из входных сигналов и равен единице. Действительно, сумма возбужденных входов линейного сумматора не может превысить двух (сумма равна при и при условии, что ранее возникшая ошибка типа «ложный О уже перевела триггер на элементах 2 и 4 в состояние в соответствии с процессом адаптации, описанным ниже), следовательно, сумма лежит ниже значения порога Т, что обеспечивает поддержание высокого уровня напряжения (логической единицы) на выходе 17. При переходе сигнала С1 из состояния «единица в состояние «нуль возникает кратковременное запирание выходного транзистора ДТЛ элемента 5 за счет эффекта рассасывания заряда, накопленного диодами 20 и 21 за время лЧействия положител1)ного имнхльса. Это приводит к повышению потенциала входа 12, который, однако, фиксируется па уровне, близком к порогу отпирапия диода 13, так как на катод последнего в это время подан низкий потенциал (С1: 0). Повышение потенциала входа 12 не может изменить состояние триггера на элементах 2 и 4, в каком бы состоянии он не находился. Таким образом, при .ХЗ и произвольном исходном состоянии триггера (Q 0 или на выходе У постоянно поддерживает «единицу, яа выходе ДТЛ элемента 5 в моменты, соответствующие переходу С1 из «единицы в «нуль, появляются положительные импульсы малой амплитуды, причем состояние триггера остается неизменным. Проведенный выше анализ состояний устройства может быть повторен для случая, когда на его входах появляются одна или две ошибки типа «ложная 1 (в последнем случае предполагается, что на входах ранее не возникали ошибки типа «ложный О, которые, как будет показано, приводят к переключению триггера в состояние ). Поскольку при этом число возбужденных входов порогового элемента 1 не превышает трех, сигнал также остается равным единице. Иными словами, ошибки типа «ложная I исправляются. Рассмотрим теперь случай, соответствуюший постоянной информации ХЗ и последовательному возникновению ошибок типа «ложный О, число которых обозначим через Z (см. фиг. 2). Пусть при /о /4 , т. е. величина С Х1-{Х2-}-ХЗ+Х4 (сумма арифметическая) равна четырем, а сигнал Q 0. Поскольку в рассматриваемом интервале времени G T, то на выходе Y возникает логический «О, на выходе элемента 5 постоянно присутствует низкий потенциал, элемент 3 вырабатьшает на выходе логический «О, «подтверждая исходное состояние триггера (Q 0). Пусть в момент времени 4 на вход устройства поступает информация, содержащая три «истинных единицы и один «ложный О {Z 1). При ,t5 величина 0 3, что недостаточно для включения порогового элемента 1, следовательно, на выходе У появляется высокий потенциал, который совместно с высоКИМ потенциалом на входе 14 вызывает прохождение прямого тока через диоды с накоплением заряда 20 и 21. Состояние триггера при этом не изменяется. В момент времени tf, сигнал 0 1 увеличивает сумму возбужденных входов на единицу (6+ + ), что приводит к срабатыванию элемента 1 и переходу сигнала У из «1 в «О. ри этом благодаря эффекту накопления заяда в диодах 21 и 22 за время элеент 5 временно переходит в состояние логиЧеской «1 на выходе, и, поскольку диод 13 заперт, потенциал входа 12 оказывается достаточно высоким для включения элемента 4 и переключения триггера в состояние , Q 0. Таким образом, «ложный О, возникающий на одном из информационных входов, компе;1сируется сигналом , что приводит к стабилизации величины (см. соответствующую диаграмму на фиг. 2). Состояние , сохраняется вплоть до момента 12 появления второй ошибки типа «ложный О. Если первая ошибка являлась сбоем, то в одном из последующих тактов она исчезнет, т. е. появится комбинация , которз;; приведет к срабатыванию элемента 3 и к автоматической установке прежнего состояния триггера, отвечающего отсутствию ошибок типа «ложный О во входной информации. Другими словами, появление кратковременных ошибок (сбоев) во входной информации (XI-ЛЧ) не приводит к снижению корректирующих возможностей устройства (процесс адаптации является обратимым). В момент времени tiz Z 2, G 2, + -(-Q 3. При этом общее Число возбужденных входов / Я+С2 ока ь1вается достаточным для перехода сигнала Y в нулевое состояние в интервалы времени, при которых , т. е. во время считывания информации. Таким образом, осуществляется коррекция до двух ошибок типа «ложный О. Применение предлагаемого адаптивного резервированного устройства позволяет использовать четыре (а не пять, как при мажоритарном резервировании) идентичных канала обработки информации при допустимой кратности ошибок, равной двум. Формула изобретения Адаптивное резервированное устройство, содержащее пороговый элемент, элемент «И - НЕ и триггер, отличающееся тем, что, с целью повышения помехоустойчивости устройства, оно содержит дифференцирующий элемент, вход которого подключен к выходу порогового элемента, а выход - к установочному входу триггера, выход которого соединен с выходом элемента «И - НЕ и компенсирующим входом порогового элемента, информационные входы которого соединены с соответствующими входами элемента «И - НЕ.

Ci - h O Njv-CD .- tr c jT-ca in Kicsj,- ca

5j

V

r.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2011 |

|

RU2450436C1 |

| Способ кодовой цикловой синхронизации для каскадного кода Рида-Соломона и Боуза-Чоудхури-Хоквингема [РС(32,16,17), БЧХ(31,16,7)] при одновременном применении жестких и мягких решений | 2020 |

|

RU2747623C1 |

| Декодирующее устройство | 1989 |

|

SU1681388A1 |

| Устройство для восстановления информации | 1974 |

|

SU548861A1 |

| Устройство для контроля схем сравнения | 1979 |

|

SU960822A1 |

| Многоканальное мажоритарное резервированное логическое устройство | 1985 |

|

SU1320898A1 |

| Резервированное запоминающее устройство | 1987 |

|

SU1467572A1 |

| Устройство для исправления пачек ошибок | 1982 |

|

SU1043658A1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ С МЯГКИМИ РЕШЕНИЯМИ | 2010 |

|

RU2428801C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ T-КОДОВ | 1991 |

|

RU2026608C1 |

s

Авторы

Даты

1976-03-15—Публикация

1973-02-09—Подача