Изобретение относится к информационно-измерительным системам, в частности к системам автоматического контроля электрических параметров и качества продукции, и может быть использовано для контроля качества обмоток трехфазных электрическ машин.

Цель изобретения - повышение достоверности результатов контроля и производительности за счет совмещения во времени операции контроля и автоматического распознавания четырех видов дефекта испытуемых обмоток.

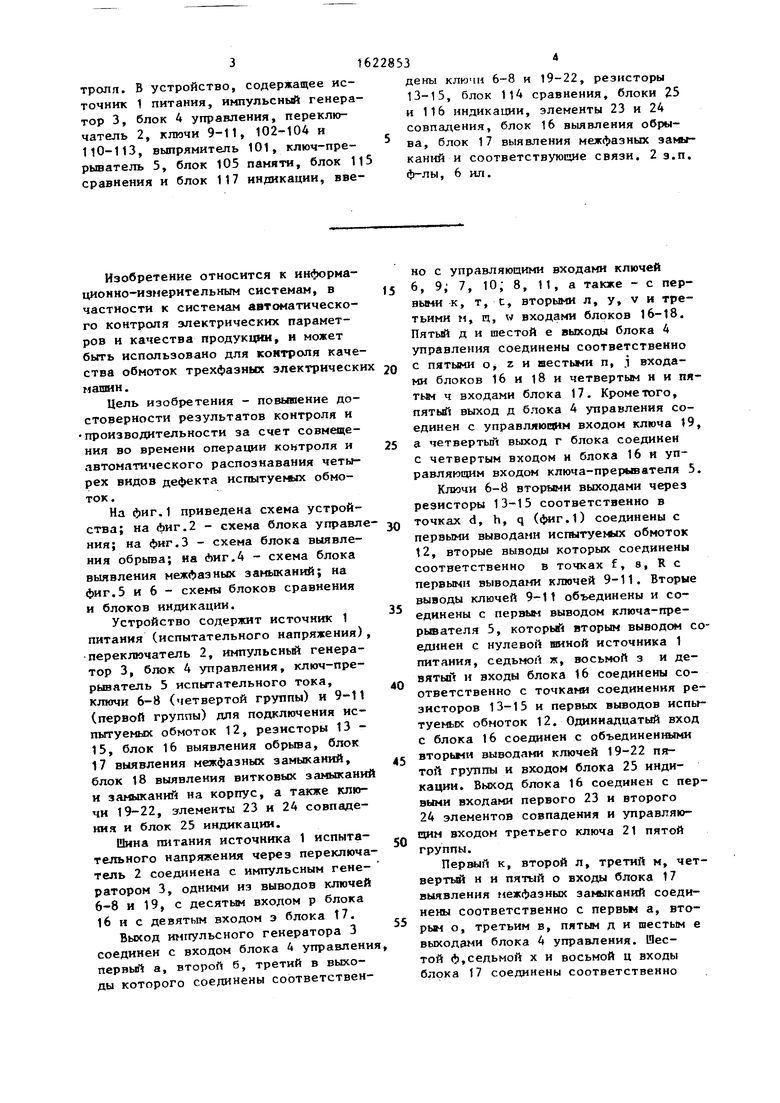

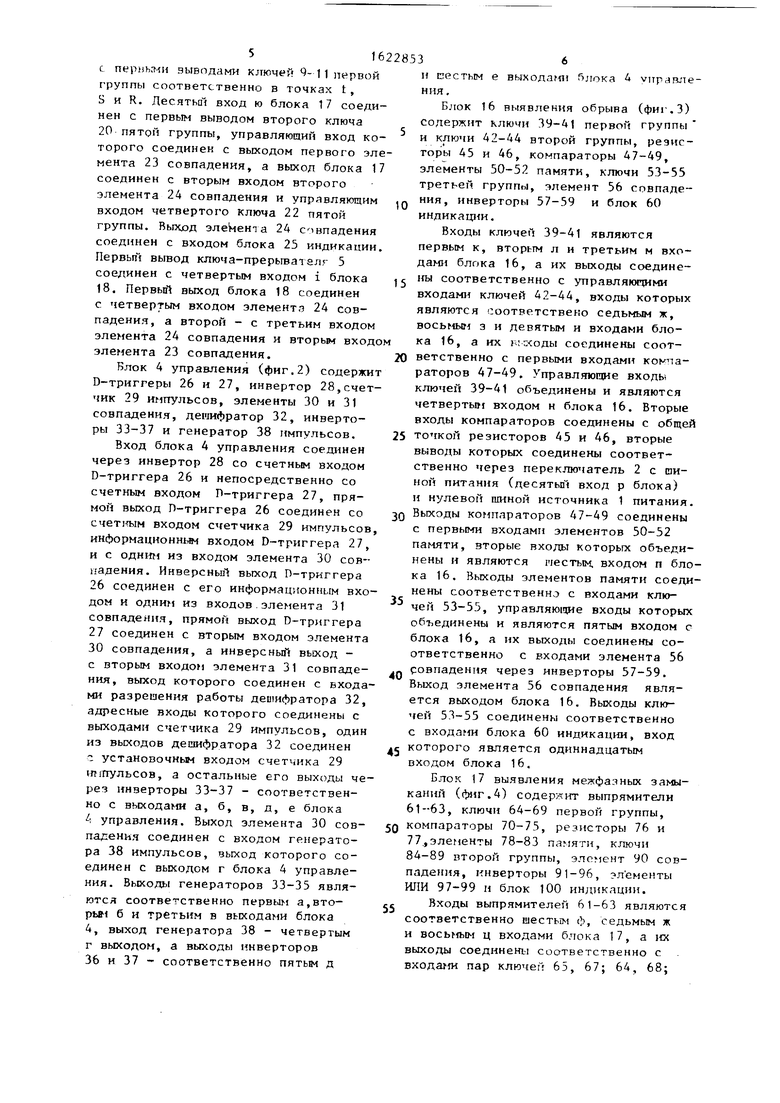

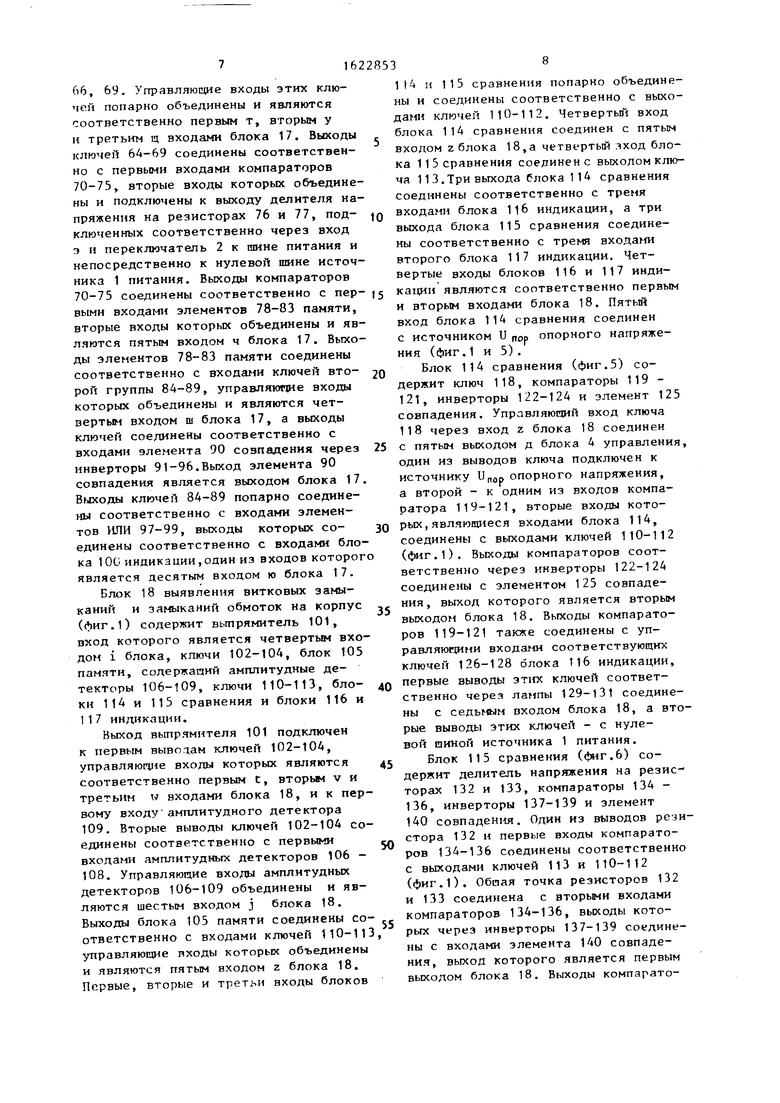

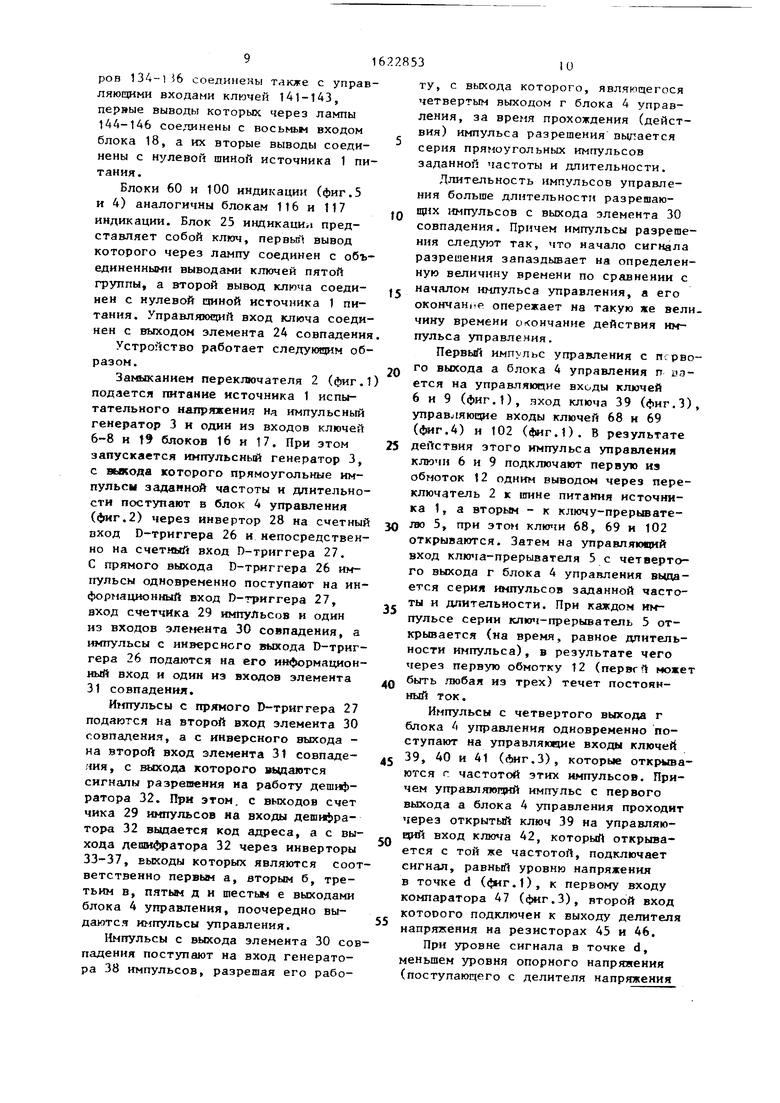

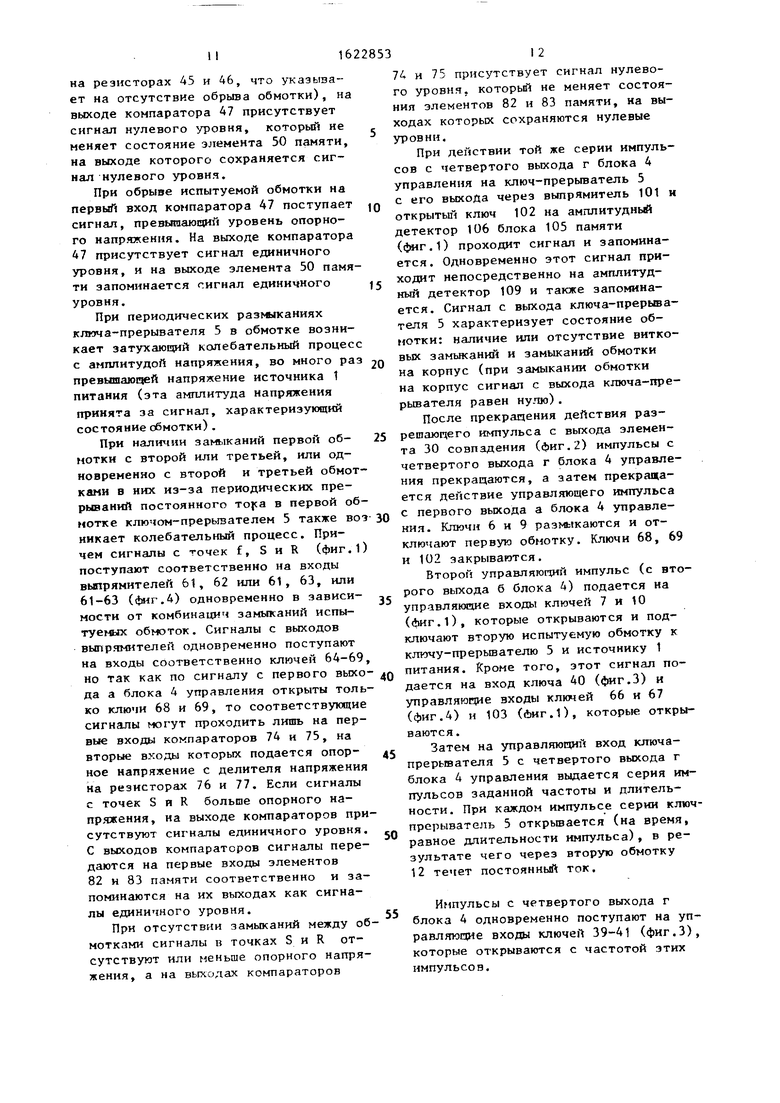

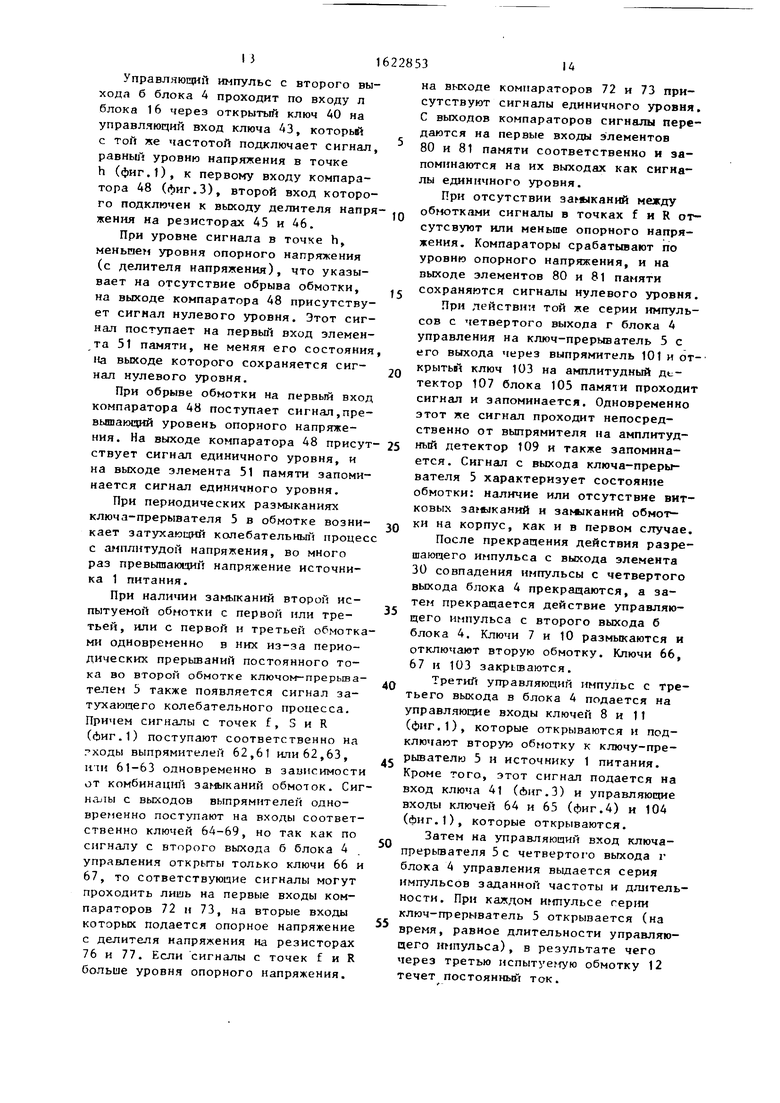

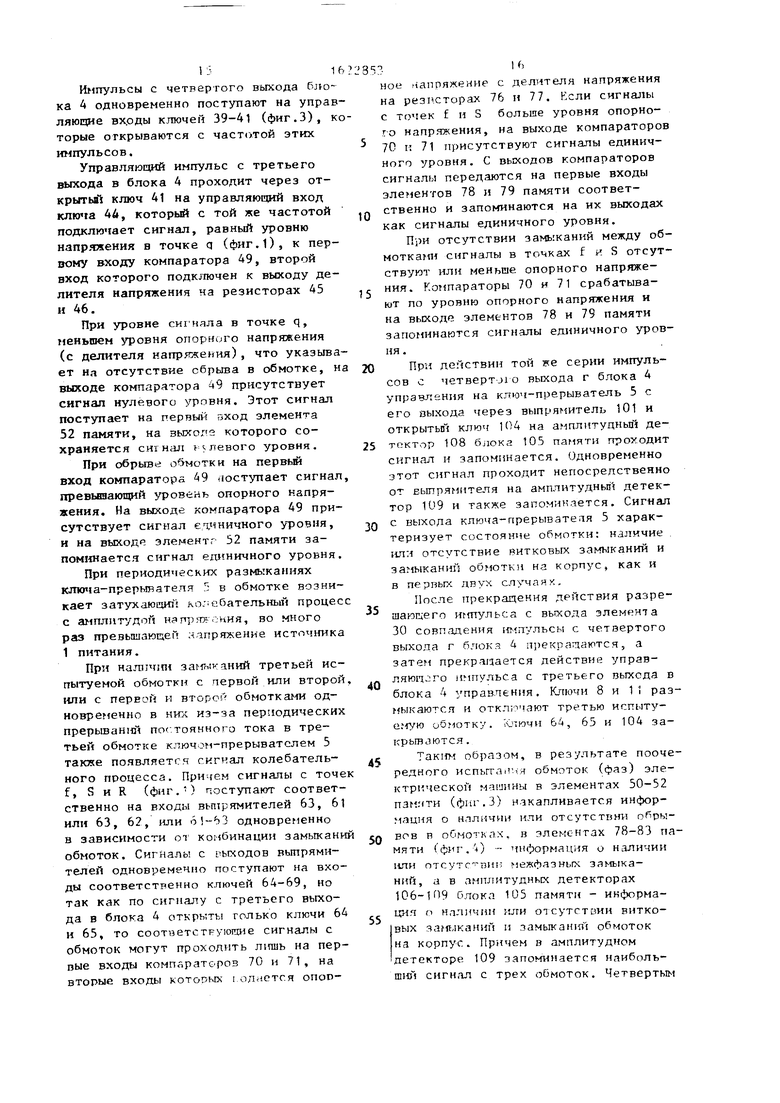

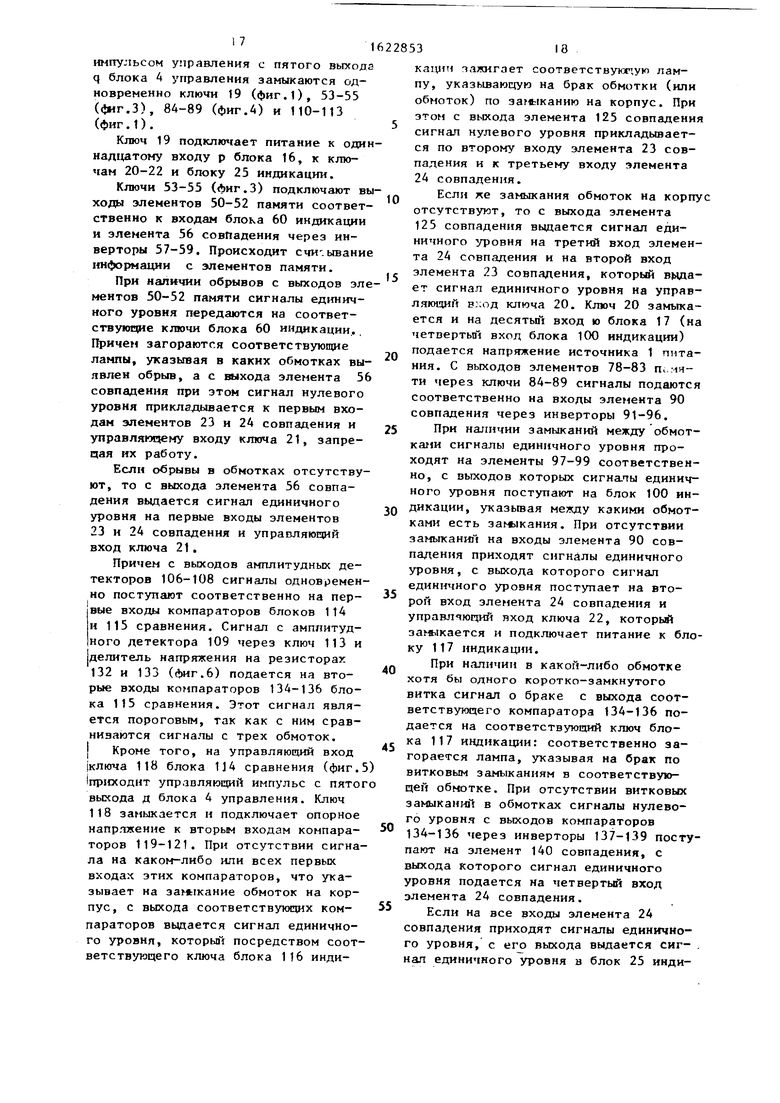

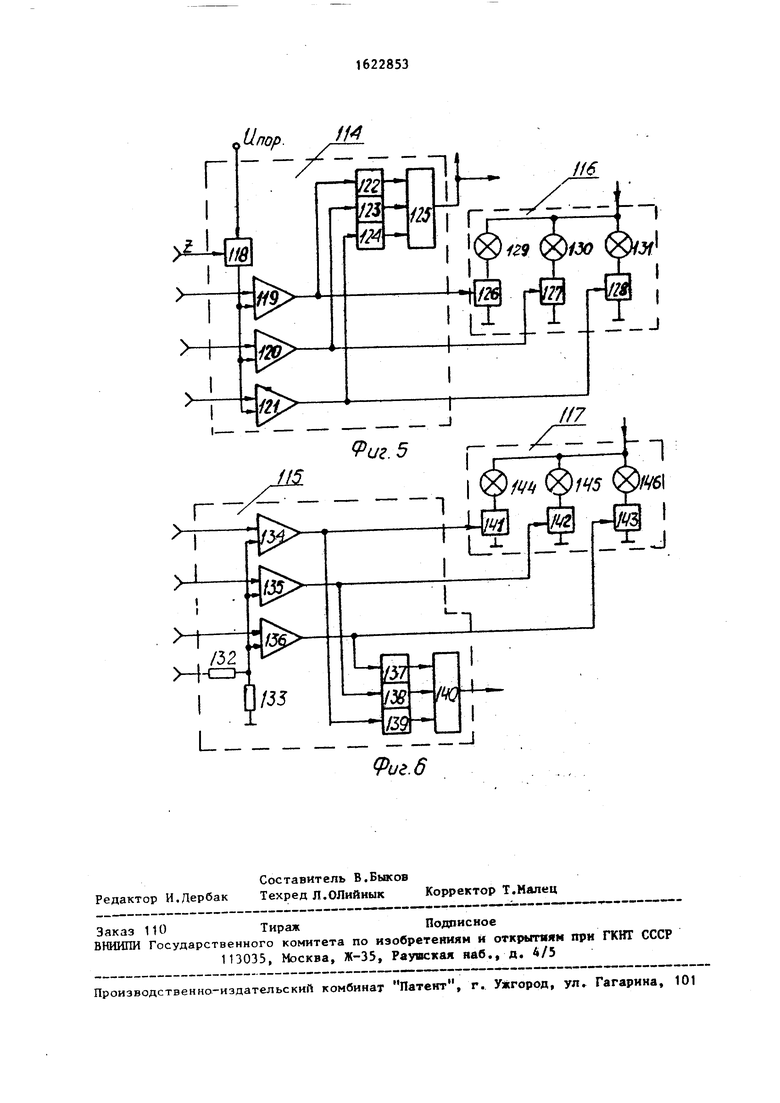

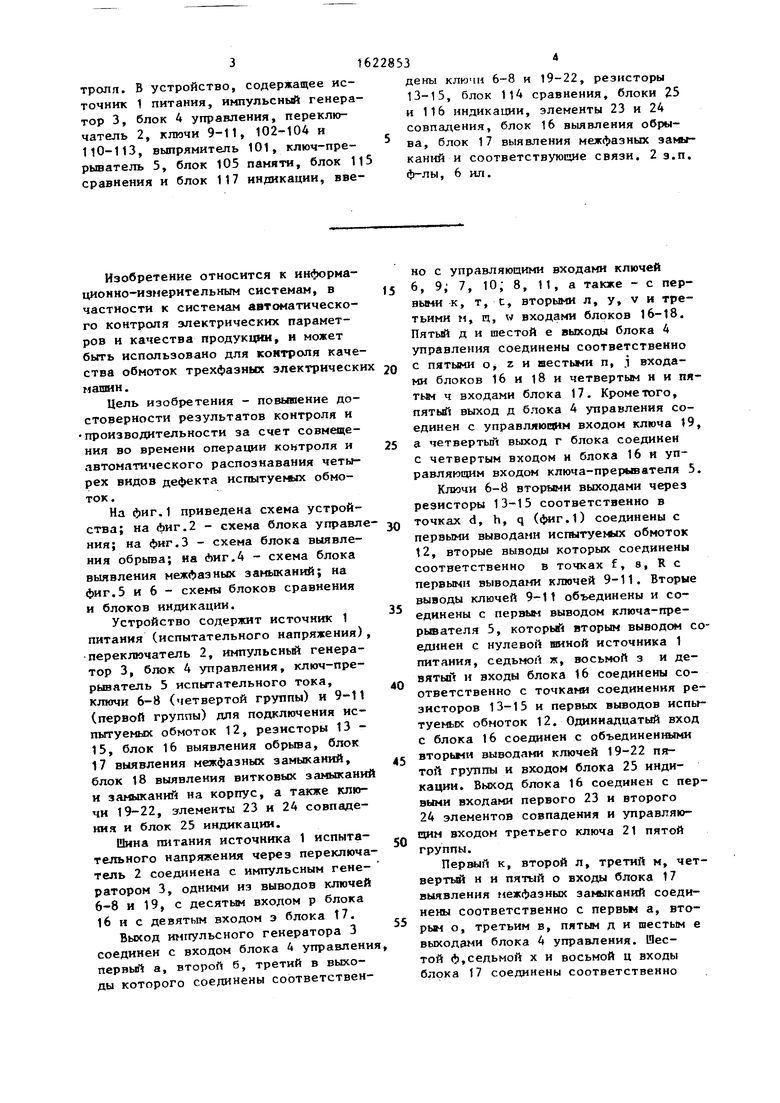

На фиг.1 приведена схема устройства; на фиг.2 - схема блока управл ния; на фиг.З - схема блока выявления обрыва; на Аиг.4 - схема блока выявления межфаэных замыканий; на фиг.5 и 6 - схемы блоков сравнения и блоков индикации.

Устройство содержит источник 1 питания (испытательного напряжения) переключатель 2, импульсный генератор 3, блок 4 управления, ключ-прерыватель 5 испытательного тока, ключи 6-8 (четвертой группы) и 9-11 (первой группы) для подключения испытуемых обмоток 12, резисторы 13 - 15, блок 16 выявления обрыва, блок 17 выявления межфазных замыканий, блок 18 выявления витковых замыканий и замыканий на корпус, а также ключи 19-22, элементы 23 и 24 совпадения и блок 25 индикации.

Шина питания источника 1 испытательного напряжения через переключатель 2 соединена с импульсным генератором 3, одними из выводов ключей 6-8 и 19, с десятым входом р блока 16 и с девятым входом э блока 17.

Выход импульсного генератора 3 соединен с входом блока 4 управлени первый а, второй б, третий в выходы которого соединены соответствен

5

5 0

5

Q

0

5

0

5

но с управляющими входами ключей 6, 9; 7, 10; 8, 11, а также - с первыми к, т, с, вторыми л, у, v и третьими м, ц, w входами блоков 16-18. Пятый д и шестой е выходы блока 4 управления соединены соответственно с пятыми о, z и шестыми п, j входами блоков 16 и 18 и четвертым н и пятым ч входами блока 17. Кроме того, пятый выход д блока 4 управления соединен с управляющим входом ключа 19, а четвертый выход г блока соединен с четвертым входом н блока 16 н управляющим входом ключа-прерывателя 5.

Ключи 6-8 вторыми выходами через резисторы 13-15 соответственно в точках d, h, q (фиг.1) соединены с первыми выводами испытуемых обмоток 12, вторые выводы которых соединены соответственно в точках f, s, Re первыми выводами ключей 9-11. Вторые выводы ключей 9-11 объединены и соединены с первым выводом ключа-прерывателя 5, который вторым выводом соединен с нулевой шиной источника 1 питания, седьмой ж, восьмой з и девятый и входы блока 16 соединены соответственно с точками соединения резисторов 13-15 и первых выводов испытуемых обмоток 12. Одиннадцатый вход с блока 16 соединен с объединенными вторыми выводами ключей 19-22 пятой группы и входом блока 25 индикации. Выход блока 16 соединен с первыми входами первого 23 и второго 24 элементов совпадения и управляющим входом третьего ключа 21 пятой группы.

Первый к, второй л, третий м, четвертый н и пятый о входы блока 17 выявления межфазных замыканий соединены соответственно с первым а, вторым о, третьим в, пятым д и шестым е выходами блока 4 управления. Шестой ф,седьмой х и восьмой ц входы блока 17 соединены соответственно

с первыми выводами ключей 9- 11 первой группы соответственно в точках t, S и R. Десятый вход ю блока 17 соединен с первым выводом второго ключа 20 пятой группы, управляющий вход которого соединен с выходом первого элемента 23 совпадения, а выход блока 17 соединен с вторым входом второго элемента 24 совпадения и управляющим входом четвертого ключа 22 пятой группы. Выххзд элемента 24 совпадения соединен с входом блока 25 индикации. Первый вывод ключа-прерывачглг 5 соединен с четвертым входом i блока 18. Первый выход блока 18 соединен с четвертым входом элемент, 24 совпадения, а второй - с третьим входом элемента 24 совпадения и вторым входо элемента 23 совпадения.

Блок 4 управления (фиг.2) содержит D-триггеры 26 и 27, инвертор 28,счетчик 29 импульсов, элементы 30 и 31 совпадения, дешифратор 32, инверторы 33-37 и генератор 38 импульсов.

Вход блока 4 управления соединен через инвертор 28 со счетным входом D-триггера 26 и непосредственно со счетным входом D-триггера 27, прямой выход П-триггера 26 соединен со счеткым входом счетчика 29 импульсов, информационным входом D-триггера 27, и с одним из входом элемента 30 совпадения. Инверсный выход П-триггера

26соединен с его информационным входом и одним из входов элемента 31 совпадения, прямой выход D-триггера

27соединен с вторым входом элемента 30 совпадения, а инверсный ВЬЕХОД с вторым входом элемента 31 совпадения, выход которого соединен с входами разрешения работы дешифратора 32, адресные входы которого соединены с выходами счетчика 29 импульсов, один из выходов дешифратора 32 соединен i установочным входом счетчика 29 (шпульсов, а остальные его выходы через инверторы 33-37 - соответственно с выходами а, б, в, д, е блока 4 управления. Выход элемента 30 сов- парения соединен с входом генератора 38 импульсов, выход которого соединен с выходом г блока 4 управления. Выходы генераторов 33-35 являются соответственно первым а,вторь б и третьим в выходами блока 4, выход генератора 38 - четвертым г выходом, а выходы инверторов 36 и 37 - соответственно пятым д

5

0

и сестым е выходами блока 4 vnpdBJTe- ния,

Блок 16 выявления обрыва (фиг.З) содержит ключи 39-41 первой группы и ключи 42-44 второй группы, резисторы 45 и 46, компараторы 47-49, элементы 50-52 памяти, ключи 53-55 третьей группы, элемент 56 совпадения, инверторы 57-59 и блок 60 индикации.

Входы ключей 39-41 являются первым к, вторым л и третьим м входами блока 16, а их выходы соединены соответственно с управляющими входами ключей 42-44, входы которых являются соответствено седьмым ж, восьмым з и девятым и входами блока 16, а их ргкоды соединены соответственно с первыми входами кокяа- раторов 47-49. Управляющие входы ключей 39-41 объединены и являются четвертым входом н блока 16. Вторые входы компараторов соединены с общей

5 точкой резисторов 45 и 46, вторые выводы которых соединены соответственно через переключатель 2 с шиной питания (десятый вход р блока) н нулевой шиной источника 1 питания.

0 Выходы компараторов 47-49 соединены с первыми входами элементов 50-52 памяти, вторые входы которых объединены и являются шестым, входом п блока 16. Выходы элементов памяти соединены соответственно с входами ключей 53-55, управлякнцие входы которых объединены и являются пятым входом с блока 16, а их выходы соединены соответственно с входами элемента 56 совпадения через инверторы 57-59. Выход элемента 56 совпадения является выходом блока 16. Выходы ключей 53-55 соединены соответственно с входами блока 60 индикации, вход

с которого является одиннадцатым входом блока 16.

Блок 17 выявления межфазных замыканий (фиг.4) содеркит выпрямители 61-63, ключи 64-69 первой группы,

Q компараторы 70-75, резисторы 76 и 77,элементы 78-83 памяти, ключи 84-89 второй группы, элемент 90 совпадения, инверторы 91-96, элементы ИЛИ 97-99 и блок ЮО индикации.

Входы выпрямителей 61-63 являются соответственно шестым ф, седьмым ж и восьмым ц входами блока 17, а их выходы соединены соответственно с входами пар ключей 65, 67; 64, 68;

0

66, 69. Управляющие входы этих ключей попарно объединены и являются соответственно первым т, вторым у и третьим ц входами блока 17. Выходы ключей 64-69 соединены соответственно с первыми входами компараторов 70-75, вторые входы которых объединены и подключены к выходу делителя напряжения на резисторах 76 и 77, подключенных соответственно через вход з и переключатель 2 к шине питания и непосредственно к нулевой шине источника 1 питания. Выходы компараторов

1(4 н 115 сравнения попарно объединены и соединены соответственно с выходами ключей 110-112. Четвертый вход блока 114 сравнения соединен с пятым входом z блока 18,а четвертый лход блока 115 сравнения соединен с выходом ключа 11З.Тривыхода блока 114 сравнения соединены соответственно с тремя входами блока 116 индикации, а три выхода блока 115 сравнения соединены соответственно с тремя входами второго блока 117 индикации. Четвертые входы блоков 116 и 117 инди

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения межвитковых замыканий в обмотках трехфазных электрических машин | 1985 |

|

SU1328772A1 |

| Устройство для контроля операционных усилителей в электронных блоках | 1988 |

|

SU1674018A1 |

| Устройство для контроля интегральных схем | 1983 |

|

SU1171795A1 |

| АНАЛИЗАТОР РАБОТЫ СИСТЕМ ДВИГАТЕЛЯ ВНУТРЕННЕГО СГОРАНИЯ | 2015 |

|

RU2626282C2 |

| ЭЛЕКТРОПРИВОД ПЕРЕМЕННОГО ТОКА | 1992 |

|

RU2054223C1 |

| Устройство контроля витковых замыканий в обмотке ротора электрической машины | 1992 |

|

SU1831744A3 |

| АНАЛИЗАТОР РАБОТЫ СИСТЕМ ДВИГАТЕЛЯ ВНУТРЕННЕГО СГОРАНИЯ | 2007 |

|

RU2347203C1 |

| Устройство для контроля электрических параметров конденсаторов | 1989 |

|

SU1684729A1 |

| УСТРОЙСТВО ИНДИКАЦИИ ПЛЕНКИ В ЛЕНТОПРОТЯЖНОМ ТРАКТЕ ФОТОАППАРАТА | 1992 |

|

RU2047881C1 |

| АНАЛИЗАТОР РАБОТЫ СИСТЕМ ДВИГАТЕЛЯ ВНУТРЕННЕГО СГОРАНИЯ | 2011 |

|

RU2532990C2 |

Изобретение относится к информационно-измерительной технике, в частности к системам автоматического контроля электрических параметров и качества продукции, и может быть использовано для контроля качества обмоток трехфазных электрических машин. Цель изобретения - повышение достоверности устройства путем распознавания четырех видов дефекта и совмещения во времени операций кон

70-75 соединены соответственно с пер- 15 кации являются соответственно первым выми входами элементов 78-83 памяти, и вторым входами блока 18. Пятый вторые входы которых объединены и являются пятым входом ч блока 17. Выходы элементов 78-83 памяти соединены

20

соответственно с входами ключей второй группы 84-89, управляющие входы которых объединены и являются четвертым входом ш блока 17, а выходы ключей соединены соответственно с входами элемента 90 совпадения через инверторы 91-96.Выход элемента 90 совпадения является выходом блока 17. Выходы ключей 84-89 попарно соединены соответственно с входами элементов ИЛИ 97-99, выходы которых соединены соответственно с входами блока 100 индикации,один из входов которого является десятым входом ю блока 17.

Блок 18 выявления витковых замыканий и замыканий обмоток на корпус (фиг.1) содержит выпрямитель 101, вход которого является четвертым входом i блока, ключи 102-104, блок 105 памяти, содержащий амплитудные детекторы 106-109, ключи 110-113, блоки 114 и 115 сравнения и блоки 116 и 117 индикации.

Выход выпрямителя 101 подключен к первым выводам ключей 102-104, управляющие входы которых являются соответственно первым t, вторым v и третьим w входами блока 18, и к первому входу амплитудного детектора 109. Вторые выводы ключей 102-104 соединены соответственно с первыми входами амплитудных детекторов 106 - 108. Управляющие входы амплитудных детекторов 106-109 объединены и являются шестым входом j блока 18. Выходы блока 105 памяти соединены соответственно с входами ключей 110-113, управляющие входы которых объединены и являются пятым входом z блока 18. Первые, вторые и третьи входы блоков

25

вход блока 114 сравнения соединен с источником U П0р опорного напряжения (фиг.1 и 5).

Блок 114 сравнения (фиг.5) содержит ключ 118, компараторы 119 - 121, инверторы 122-124 и элемент 125 совпадения. Управляющий вход ключа 118 через вход z блока 18 соединен с пятым выходом д блока 4 управления один из выводов ключа подключен к источнику Unop опорного напряжения, а второй - к одним из входов компаратора 119-121, вторые входы кото- 3Q рых,являющиеся входами блока 114, соединены с выходами ключей 110-112 (фиг.1). Выходы компараторов соответственно через инверторы 122-124 соединены с элементом 125 совпадения, выход которого является вторым выходом блока 18. Выходы компараторов 119-121 также соединены с управляющими входами соответствующих ключей 126-128 блока 116 индикации, первые выводы этих ключей соответственно через лампы 129-131 соединены с седьмым входом блока 18, а вторые выводы этих ключей - с нулевой шиной источника 1 питания.

Блок 115 сравнения (фиг.6) содержит делитель напряжения на резисторах 132 и 133, компараторы 134 - 136, инверторы 137-139 и элемент 140 совпадения. Один из выводов резистора 132 н первые входы компараторов 134-136 соединены соответственно с выходами ключей 113 и 110-112 (фиг.1). Обшая точка резисторов 132 и 133 соединена с вторыми входами компараторов 134-136, выходы которых через инверторы 137-139 соединены с входами элемента 140 совпадения, выход которого является первым выходом блока 18. Выходы компарато35

40

45

50

55

5 кации являются соответственно первым и вторым входами блока 18. Пятый

5

вход блока 114 сравнения соединен с источником U П0р опорного напряжения (фиг.1 и 5).

Блок 114 сравнения (фиг.5) содержит ключ 118, компараторы 119 - 121, инверторы 122-124 и элемент 125 совпадения. Управляющий вход ключа 118 через вход z блока 18 соединен с пятым выходом д блока 4 управления, один из выводов ключа подключен к источнику Unop опорного напряжения, а второй - к одним из входов компаратора 119-121, вторые входы кото- Q рых,являющиеся входами блока 114, соединены с выходами ключей 110-112 (фиг.1). Выходы компараторов соответственно через инверторы 122-124 соединены с элементом 125 совпадения, выход которого является вторым выходом блока 18. Выходы компараторов 119-121 также соединены с управляющими входами соответствующих ключей 126-128 блока 116 индикации, первые выводы этих ключей соответственно через лампы 129-131 соединены с седьмым входом блока 18, а вторые выводы этих ключей - с нулевой шиной источника 1 питания.

Блок 115 сравнения (фиг.6) содержит делитель напряжения на резисторах 132 и 133, компараторы 134 - 136, инверторы 137-139 и элемент 140 совпадения. Один из выводов резистора 132 н первые входы компараторов 134-136 соединены соответственно с выходами ключей 113 и 110-112 (фиг.1). Обшая точка резисторов 132 и 133 соединена с вторыми входами компараторов 134-136, выходы которых через инверторы 137-139 соединены с входами элемента 140 совпадения, выход которого является первым выходом блока 18. Выходы компарато5

0

5

9

ров 134-1 56 соединены также с управляющими входами ключей 141-143, первые выводы которых через лампы 144-146 соединены с восьмым входом блока 18, а их вторые выводы соединены с нулевой шиной источника 1 питания.

Блоки 60 и 100 индикации (фиг.5 и 4) аналогичны блокам 116 и 117 индикации. Блок 25 индикации представляет собой ключ, первый вывод которого через лампу соединен с объединенными выводами ключей пятой группы, а второй вывод ключа соединен с нулевой щиной источника 1 питания. Управляющий вход ключа соединен с выходом элемента 24 совпадени

Устройство работает следующим образом.

Замыканием переключателя 2 (фиг. подается питание источника 1 испытательного напряжения На импульсный генератор 3 и один из входов ключей 6-8 н t9 блоков 16 и 17, При этом запускается импульсный генератор 3, с выхода которого прямоугольные им- пульсм заданной частоты и длительности поступают в блок 4 управления (фиг.2) через инвертор 28 на счетны вход D-трнггера 26 и непосредственно на счетный вход D-триггера 27. С прямого выхода D-триггера 26 импульсы одновременно поступают на информационный вход D-григгера 27, вход счетчика 29 импульсов и один из входов элемента 30 совпадения, а импульсы с инверсного выхода D-триггера 26 подаются на его информационный вход и один из входов элемента 31 совпадения.

Импульсы с прямого D-триггера 27 подаются на второй вход элемента 30 совпадения, а с инверсного выхода - на второй вход элемента 31 совпадения, с выхода которого выдаются сигналы разрешения на работу дешифратора 32. При этом, с выходов счет чика 29 импульсов на входы дешифратора 32 выдается код адреса, а с выхода дешифратора 32 через инверторы 33-37, выходы которых являются сооветственно первым а, вторым б, третьим в, пятым д и шестым е выходами блока 4 управления, поочередно выдаются импульсы управления.

Импульсы с выхода элемента 30 сопадения поступают на вход генератора 38 импульсов, разрешая его рабо

to

5

0

5

2853

0

5

0

5

0

5

10

ту, с выхода которого, являющегося четвертым выходом г блока 4 управления, за время прохождения (действия) импульса разрешения выдается серия прямоугольных импульсов заданной частоты и длительности.

Длительность импульсов управления больше длительности разрешающих импульсов с выхода элемента 30 совпадения. Причем импульсы разрешения следуют так, что начало сигнала разрешения запаздывает на определенную величину времени по сравнении с началом импульса управления, а его окончание опережает на такую же величину времени окончание действия импульса управления.

Первый импульс управления с п.-рво- го выхода а блока 4 управления п иэ- ется на управляющие входы ключей 6 и 9 (фиг.1), яход ключа 39 (фнг.З), управляющие входы ключей 68 н 69 (фиг.4) и 102 (фнг.1). В результате действия этого импульса управления ключи 6 и 9 подключают первую из обмоток 12 одним выводом через переключатель 2 к шине питания источника 1 , а вторым - к ключу-прерывате- JBO 5, при этом ключи 68, 69 и 102 открываются. Затем на управлякмций вход ключа-прерывателя 5 с четвертого выхода г блока 4 управления выдается серия импульсов заданной частоты и длительности. При каждом импульсе серии ключ-прерыватель 5 открывается (на время, равное длительности импульса), в результате чего через первую обмотку 12 (перart может быть любая из трех) течет постоянный ток.

Импульсы с четвертого выхода г блока 4 управления одновременно поступают на управляюеще входы ключей 39, 40 и 41 (биг.З), которые открываются с частотой этих импульсов. Прячем угфавляют кй импульс с первого выхода а блока 4 управления проходит через открытый ключ 39 на управляющий вход ключа 42, который открывается с той же частотой, подключает сигнал, равный уровню напряжения в точке d (фиг.1), к первому входу компаратора 47 (фнг.З), второй вход КОТОРОГО подключен к выходу делителя напряжения на резисторах 45 и 46.

При уровне сигнала в точке d, меньшем уровня опорного напряжения (поступающего с делителя напряжения

10

15

20

25

Ч162285312

74 и 75 присутствует сигнал нулевого уровня, который не меняет состояния элементов 82 и 83 памяти, на выходах которых сохраняются нулевые уровни.

При действии той же серии импульсов с четвертого выхода г блока 4 управления на ключ-прерыватель 5 с его выхода через выпрямитель 101 и открытый ключ 102 на амплитудный детектор 106 блока 105 памяти (фиг.1) проходит сигнал и запоминается. Одновременно этот сигнал приходит непосредственно на амплитудный детектор 109 и также запоминается. Сигнал с выхода ключа-прерывателя 5 характеризует состояние обмотки: наличие или отсутствие витко- вых замыканий и замыканий обмотки на корпус (при замыкании обмотки на корпус сигнал с выхода ключа-прерывателя равен нулю).

После прекращения действия разрешающего импульса с выхода элемента 30 совпадения (фиг.2) импульсы с четвертого выхода г блока 4 управления прекращаются, а затем прекращается действие управляющего импульса с первого выхода а блока 4 управления. Ключн 6 и 9 размыкаются и отключают первую обмотку. Ключн 68, 69 и 102 закрываются.

Второй управляющий импульс (с второго выхода б блока 4) подается на управляющие входы ключей 7 и 10 (6иг.1), которые открываются и подключают вторую испытуемую обмотку к ключу-прерывателю 5 и источнику 1

сигналу с первого выхо- дл питания. Кроме того, этот сигнал подается на вход ключа 40 (фиг.З) и управляющие входы ключей 66 и 67 (фиг.4) и 103 (Фиг.1), которые открываются.

Затем на управляющий вход ключа- прерывателя 5 с четвертого выхода г блока 4 управления выдается серия импульсов заданной частоты и длительности. При каждом импульсе серии ключ- прерыватель 5 открывается (на время, равное длительности импульса), в результате чего через вторую обмотку 12 течет постоянный ток.

на резисторах 45 и 46, что указывает на отсутствие обрыва обмотки), на выходе компаратора 47 присутствует сигнал нулевого уровня, который не меняет состояние элемента 50 памяти, на выходе которого сохраняется сигнал нулевого уровня.

При обрыве испытуемой обмотки на первый вход компаратора 47 поступает сигнал, превышающий уровень опорного напряжения. На выходе компаратора 47 присутствует сигнал единичного уровня, и на выходе элемента 50 памяти запоминается сигнал единичного уровня.

При периодических размыканиях ключа-прерывателя 5 в обмотке возникает затухающий колебательный процесс с амплитудой напряжения, во много раз превышающей напряжение источника 1 питания (эта амплитуда напряжения принята за сигнал, характеризующий состояние обмотки).

При наличии замыканий первой обмотки с второй или третьей, или одновременно с второй и третьей обмотками в них из-за периодических прерываний постоянного тока в первой обмотке ключом-прерывателем 5 также воэ 30 ннкает колебательный процесс. Причем сигналы с точек f, S и R (фиг.1) поступают соответственно на входы выпрямителей 61, 62 или 61, 63, или 61-63 (фиг.4) одновременно в зависимости от комбинацим замыканий испытуемых обмоток. Сигналы с выходов выпрямителей одновременно поступают на входы соответственно ключей 64-69, но так как по

да а блока 4 управления открыты только ключи 68 и 69, то соответствующие сигналы могут проходить лишь на первые входы компараторов 74 и 75, на вторые входы которых подается опорное напряжение с делителя напряжения на резисторах 76 и 77. Если сигналы с точек S и R больше опорного напряжения, на выходе компараторов присутствуют сигналы единичного уровня. С выходов компараторов сигналы передаются на первые входы элементов 82 и 83 памяти соответственно и запоминаются на их выходах как сигналы единичного уровня.

При отсутствии замыканий между обмотками сигналы в точках S и R отсутствуют или меньше опорного напряжения, а на выходах компараторов

35

45

50

55

Импульсы с четвертого выхода г блока 4 одновременно поступают на управляющие входы ключей 39-41 (фиг.З), которые открываются с частотой этих импульсов.

Импульсы с четвертого выхода г блока 4 одновременно поступают на управляющие входы ключей 39-41 (фиг.З), которые открываются с частотой этих импульсов.

Управляющий импульс с второго выхода б блока 4 проходит по входу л блока 16 через открытый ключ 40 на управляющий вход ключа 43, который с той же частотой подключает сигнал, равный уровню напряжения в точке h (фиг.1), к первому входу компаратора 48 (фиг.З), второй вход которого подключен к выходу делителя напряжения на резисторах 45 и 46.

При уровне сигнала в точке h, меньшем уровня опорного напряжения (с делителя напряжения), что указывает на отсутствие обрыва обмотки, на выходе компаратора 48 присутствует сигнал нулевого уровня. Этот сигнал поступает на первый вход элемента 51 памяти, не меняя его состояния на выходе которого сохраняется сигнал нулевого уровня.

При обрыве обмотки на первый вход компаратора 48 поступает сигнал,превышающий уровень опорного напряжения. На выходе компаратора 48 присут ствует сигнал единичного уровня, и на выходе элемента 51 памяти запоминается сигнал единичного уровня.

При периодических размыканиях ключа-прерывателя 5 в обмотке возникает затухающий колебательный процес с амплитудой напряжения, во много раз превышающий напряжение источника 1 питания.

При наличии замыканий второй испытуемой обмотки с первой или третьей, или с первой и третьей обмотками одновременно в них из-за периодических прерываний постоянного тока во второй обмотке ключом-прерывателем 5 также появляется сигнал затухающего колебательного процесса. Причем сигналы с точек f, S и R (фиг.1) поступают соответственно на . выпрямителей 62,61 или 62,63, или 61-63 одновременно в заиисимости от комбинации замыканий обмоток. Сигналы с выходов выпрямителей одновременно поступают на входы соответственно ключей 64-69, но так как по сигналу с второго выхода б блока 4 управления открыты только ключи 66 и 67, то сответствующие сигналы могут проходить лишь на первые входы компараторов 72 и 73, на вторые входы которых подается опорное напряжение с делителя напряжения на резисторах 76 и 77. Если сигналы с точек f и R больше уровня опорного напряжения.

O

5

0

5

0

5

0

5

0

5

на выходе компараторов 72 и 73 присутствуют сигналы единичного уровня. С выходов компараторов сигналы передаются на первые входы элементов 80 и 81 памяти соответственно и запоминаются на их выходах как сигналы единичного уровня.

При отсутствии замыканий между обмотками сигналы в точках f и R от- сутсвуют или меньше опорного напряжения. Компараторы срабатывают по уровню опорного напряжения, и на выходе элементов 80 и 81 памяти сохраняются сигналы нулевого уровня. При действии той же серии импульсов с четвертого выхода г блока 4 управления на ключ-прерыватель 5 с его выхода через выпрямитель 101 и открытый ключ 103 на амплитудный детектор 107 блока 105 памяти проходит сигнал и запоминается. Одновременно этот же сигнал проходит непосредственно от выпрямителя на амплитудный детектор 109 и также запоминается. Сигнал с выхода ключа-прерывателя 5 характеризует состояние обмотки: наличие или отсутствие вит- ковых замыканий и замыкании обмотки на корпус, как и в первом случае. После прекращения действия разрешающего импульса с выхода элемента 30 совпадения импульсы с четвертого выхода блока 4 прекращаются, а затем прекращается действие управляющего импульса с второго выхода б блока 4. Ключи 7 и 10 размыкаются и отключают вторую обмотку. Ключи 66, 67 и ЮЗ закрываются.

Третий управляющий импульс с третьего выхода в блока 4 подается на управляющие входы ключей 8 и 11 (фиг.1), которые открываются и подключают вторую обмотку к ключу-прерывателю 5 и источнику 1 питания. Кроме того, этот сигнал подается на вход ключа 41 (бнг.З) и управляющие входы ключей 64 и 65 (фиг.4) и 104 (фиг.1), которые открываются.

Затем на управляющий вход ключа- прерывателя 5 с четвертого выхода г блока 4 управления выдается серия импульсов заданной частоты и длительности. При каждом импульсе герни ключ-прерыватель 5 открывается (на время, равное длительности управляющего импульса), в результате чего через третью испытуемую обмотку 12 течет постоянный ток.

i : 1

Импульсы с четвертого выхода блока 4 одновременно поступают на управляющие вх.оды ключей 39-41 (фиг.З), к торые открываются с частотой этих импульсов.

Управляющий импульс с третьего выхода в блока 4 проходит через открытый ключ 41 на управляющий вход ключа 44, который с той же частотой подключает сигнал, равный уровню напряжения в точке q (фиг.1), к первому входу компаратора 49, второй вход которого подключен к выходу делителя напряжения ча резисторах 45 и 46.

При уровне сигнала в точке q, меньшем уровня опорниго напряжения (с делителя напряжения), что указывает на отсутствие обрыва в обмотке, н выходе компаратора ч9 присутствует сигнал нулевого уровня. Этот сигнал поступает на первый вход элемента 52 памяти, на выхоли которого сохраняется сигнал i елевого уровня.

При обрыва обмотки на первый вход компаратора 49 поступает сигнал превышающий уровень опорного напряжения. На выходе компаратора 49 присутствует сигнал единичного уровня, и на выходе элемент 52 памяти запоминается сигнал единичного уровня.

При периодических размыканиях ключа-прерывателя 5 в обмотке возни кает затухающий колебательный процес с амплитудой напр,чу.ния, во много раз превышающей дапрязкение источника 1 питания.

При наличии заггмканий третьей испытуемой обмотки с первой или второй или с первой и второй обмотками одновременно в них из-за периодических прерываний по тоянного тока в третьей обмотке ключом-прерывателем 5 также появляется сигнал колебательного процесса. Примем сигналы с точе f, S и R (фиг.1) поступают соответственно на входы выпрямителей 63, 61 или 63, 62, или одновременно в зависимости от комбинации замыканий обмоток. Сигналы с выходов выпрямителей одновременно поступают на входы соответственно кпючей 64-69, но так как по сигналу с третьего выхода в блока 4 открыты только ключи 64 и 65, то соответстгующие сигналы с обмоток могут проходить лшь на первые входы компараторов 70 и 71, на вторые входы которых iсдастся ОПОР-

J3T

10

15

20

25

30

35

40

45

50

5

16

ное напряжение с делителя напряжения на резисторах 76 и 77. Если сигналы с точек f и S больше уровня опорного напряжения, на выходе компараторов 70 и 71 присутствуют сигналы единичного уровня. С выходов компараторов сигналы передаются на первые входы элементов 78 и 79 памяти соответственно и запоминаются на их выходах как сигналы единичного уровня.

При отсутствии замыканий между обмотками сигналы в точках f и S отсутствуют или меньше опорного напряжения. Компараторы 70 и 71 срабатывают по уровню опорного напряжения и на выходе элементов 78 и 79 памяти запоминаются сигналы единичного уровня .

При действии той ве серии импульсов с четвертло выхода г блока 4 управления на ключ-прерыватель 5 с его выходз через выпрямитель 101 и открытьй ключ 104 на амплитудный детектор 108 блока 105 памяти проходит сигнал и запоминается. Одновременно этот сигнал проходит непосрелствеяно от Еыпрямителя на амплитудный детектор 109 и также запоминается. Сигнал с выхода ключа-прерывателя 5 характеризует состояние обмотки: наличие или oTcvTCTBHe РИТКОВЫХ замыканий и замыкании обмотки на корпус, как и в пе р вьгх дв vx ел уч а я к .

После прекращения действия разрешающего импульса с выхода элемента 30 совпадения импульсы с четвертого выхода г блок ч 4 прекращаются, а затем прекращается действие управляющего импульса с третьего выхода в блока 4 управтения. Ключи 8 и 11 раз- мыкаются и отклрчают третью испытуемую обмотку. Члючн 6, 65 и 104 закрываются.

Таким образом, в результате поочередного испытаем обмоток (фаз) электрической машины в элементах 50-52 памяти (фнг.З) накапливается информация о наличии или отсутствии обрывов в обмотках, в элементах 78-83 памяти (фиг. ч) -- информация и наличии или отсутг виг межфазньгх замыканий, а в амплитудных детекторах 106-109 Опока 105 памяти - информация о наличии или отсутствии внтко- вых замыканий и замыканий обмоток на корпус. Причем в амплитудном детекторе 109 запоминается наибольший сигнал с трех обмоток. Четвертым

импульсом упрявления с пятого выхода q блока 4 управления замыкаются одновременно ключи 19 (фиг.1), 53-55 (фиг.З), 84-89 (фиг.4) и 110-113 (фиг.1).

Ключ 19 подключает питание к одиннадцатому входу р блока 16, к ключам 20-22 и блоку 25 индикации.

Ключи 53-55 (фиг.З) подключают выходы элементов 50-52 памяти соответственно к входам блока 60 индикации и элемента 56 совпадения через инверторы 57-59. Происходит счиг. ывание информации с элементов памяти.

При наличии обрывов с выходов элементов 50-52 памяти сигналы единичного уровня передаются на соответствующие ключи блока 60 индикации.. Причем загораются соответствующие лампы, указывая в каких обмотках выявлен обрыв, а с выхода элемента 56 совпадения при этом сигнал нулевого уровня прикладывается к первым входам элементов 23 и 24 совпадения и управляющему входу ключа 21, запрещая их работу.

Если обрывы в обмотках отсутствуют, то с выхода элемента 56 совпадения выдается сигнал единичного уровня на первые входы элементов 23 и 24 совпадения и управляющий вход ключа 21,

Причем с выходов амплитудных детекторов 106-108 сигналы одновременно поступают соответственно на первые входы компараторов блоков 114 и 115 сравнения. Сигнал с амплитудного детектора 109 через ключ 113 и делитель напряжения на резисторах 132 и 133 (фиг.6) подается на вторые входы компараторов 134-136 блока 115 сравнения. Этот сигнал является пороговым, так как с ним сравниваются сигналы с трех обмоток. j Кроме того, на управляющий вход (ключа 118 блока 134 сравнения (фиг.5 1прнходнт управляющий импульс с пятог выхода д блока 4 управления. Ключ 118 замыкается и подключает опорное напряжение к вторым входам компараторов 119-121. При отсутствии сигнала на каком-либо или всех первых входах этих компараторов, что указывает на замыкание обмоток на корпус, с выхода соответствующих компараторов выдается сигнал единичного уровня, который посредством соответствующего ключа блока 116 инди0

5

0

5

0

5

0

5

0

5

кации тажигает соответствующую лампу, указывающую на брак обмотки (или обмоток) по замыканию на корпус. При этом с выхода элемента 125 совпадения сигнал нулевого уровня прикладывается по второму входу элемента 23 совпадения и к третьему входу элемента 24 совпадения.

Если же замыкания обмоток на корпус отсутствуют, то с выхода элемента 125 совпадения выдается сигнал единичного уровня на третий вход элемента 24 совпадения и на второй вход элемента 23 совпадения, который выдает сигнал единичного уровня на управляющий в:.од ключа 20. Ключ 20 замыкается и на десятый вход ю блока 17 (на четверти вход блока 100 индикации) подается напряжение источника 1 питания. С выходов элементов 78-83 ш мч- ти через ключи 84-89 сигналы подаются соответственно на входы элемента 90 совпадения через инверторы 91-96.

При наличии замыканий между обмотками сигналы единичного уровня проходят на элементы 97-99 соответственно, с выходов которых сигналы единичного уровня поступают на блок 100 индикации, указывая между какими обмотками есть замыкания. При отсутствии замыканий на входы элемента 90 совпадения приходят сигналы единичного уровня, с выхода которого сигнал единичного уровня поступает на второй вход элемента 24 совпадения и управляющий вход ключа 22, который замыкается и подключает питание к блоку 117 индикации.

При наличии в какой-либо обмотке хотя бы одного коротко-замкнутого витка сигнал о браке с выхода соответствующего компаратора 134-136 подается на соответствующий ключ блока 117 индикации: соответственно загорается лампа, указывая на брак по витковым замыканиям в соответствующей обмотке. При отсутствии витковых замыканий в обмотках сигналы нулевого уровня с выходов компараторов 134-136 через инверторы 137-139 поступают на элемент 140 совпадения, с выхода которого сигнал единичного уровня подается на четвертый вход элемента 24 совпадения.

Если на все входы элемента 24 совпадения приходят сигналы единичного уровня, с его выхода выдается сиг- . нал единичного уровня в блок 25 индикацни, где jaropat ггя .ымпа, учазывэч что испытуемые обмотки в норме.

Процесс оценки результатов контроля и испытаний проходит еле; ующим образом.

При наличии обрыва (обрывов обмоток) с выхода блока 16 сигнал нулевого уровня запрещает работу элемента 23 совпадения и ключа 21, что запрещает оценку результатов контроля блока I7 выявления меяфазных замыканий и блоками сравнения 114 и индикации 116, которые выявляют замыкание обмотки на корпус. Такой запрет необходим, так i т при обрыве обмотки дальнейшие проверки теряют смысл.

При отсутствии обрыва обмотки (обмоток) разрешается работа ключа 21, который открывается, производится оценка реч лыл-чш на наличие или отсутствие з мы с-пий обмоток на корпус. При их на №41 и за сеется лампа в блоке 11о и иди к. пин, оказывающая на Наличие , я /лхода блока 114 сравнения IHM- сч сигнал нулевого уровня на элемент 73 совпадения, запрещал дальне t оценки результатов контроля.

При oTcvTCTjfliM яз ыканий на корпус с вьпсол блока 114 сравнения выдается сип1 а единичного уровня на второй Е vO.p элемента 23 совпадения и TPJTI - 1 -мечта 24. Происходит совпадение -л лов на входе элемента 2 тея, который череэ ключ 20 выдает зрешение на подключение mrvr «. ,. енки результатов кочтротя в Споке 1 выявления меж- фазных замычзнлй.

В случ1е . аличия межфазных замыканий об этлм « гиализирует блок 100 индикации, f-wxoin блока 17 сигнал нулевого л т) о г ч я прикладывается к второму входу элемента 24 совпадения и управляют - /3.nv ключа 22, запрещая их работу , г.J. оценку результатов в блоке 11: срзлчснкя и блоке 117

индикациь.

При отсу ст -ни межбазных замыканий сигнал ч# 1ЛЧНОГ о уровня выдается на яторон вход элемента 24 совпадения и у рарпяю ий вход ключа 22. Подключае™сч чмтаьче к блоку 1t7 индикации, Лри чаличии витковых замыканий ь бмлт-ка а олоке 117 индикации зягсрлпсэ соответствующая лампа, укачмв-р ьа так ч соответствую- цей обутке-, ч вых да блока 115

0

5

5

0

5

0

S

0

5

cpaiMVrMH на элемент 24 совпадения выдается сигнал нулевого уровня.

При отсутствии брака по витковым замыканиям с выхода блока 115 сравнения выдается сигнал единичного уровня на элемент 24 совпадения, на входы которого таким образом приходят одновременно четыре единичных сигнала, где загорается лампа, сигнализирующая о том, что испытуемые обмотки в норме.

Пятым управляюсрю импульсом с шестого выхода е блока 4 управления элементы памяти блоков 16 и 17 и блок 105 памяти блока 18 устанавливаются в исходное положение (сброс информации) , а переключателем 2 отключается источник t питания. Устройство устанавливается в исходное положение. При подключении следующей машины цикл контроля и испытаний полностью Повторяется.

Использование новых элементов - ключей четвертой группы с резистора-i ми, блоков выявления обрыва, межфазных замыканий, выявления витковых замыканий и замыканий на корпус, ключей пятой группы и элементов совпадения и новых связей, позволяет повысить достоверность результатов контроля и испытаний, обеспечить автоматизацию процесса контроля,повысить производительность контроля и испытаний за счет одновременного проведения различных операций, а также снизить трудоемкость процесса контроля и повысить его объективность, так как весь процесс контроля и испытаний выполняется автоматически.

Устройство может найти широкое применение для испытаний обмоток трехфазных электрических машин при операционном контроле, при приемо-сда- точных испытаниях собранных машин, например в составе испытательной станции при серийном и массовом производстве, а также ч процессе эксплуатации и ремонта электрических машин.

Формула изобретения

блок памяти, блок сравнения и блок индикации, выход источника питания через переключатель соединен с импульсным генератором, выход импульсного генератора соединен с входом блока управления, первый, второй и третий выходы которого соединены соответственно с входами управления первых, вторых и третьих ключей первой и второй групп, первые выходы ключей первой группы соединены с пер BUN 1 выводами объекта контроля,вторые выходы ключей первой группы объединены, вторые входы ключей второй группы объединены, четвертый выход блока управления соединен с входом ключа-прерывателя, первый выход которого соединен с вторыми выходами ключей первой группы и входом выпрямителя, а второй выход - с нулевой шиной питания, выход выпрямителя соединен с вторыми входами ключей второй группы и первым входом блока памяти, второй, третий и четвертый входы которого соединены с соответ- ствуюгцжи выходами первого, второго и третьего ключей второй группы, пятый вход блока памяти соединен с шестым выходом блока управления, выходи блока памяти соединены с первыми входами ключей третьей группы, вторые входы которых объединены и соединены с пятым выходом блока управления, выходы ключей третьей группы соединены с соответствующими входами блока сравнения,три выхода которого соединены с соответствующими входами блока индикации, отличающееся тем, что, с целью повышения производительности и достоверности контроля, в него введены три ключа четвертой группы, три резистора, второй блок сравнения и второй блок индикации, четыре ключа пятой группы, мерный и второй элементы совпадения, третий блок индикации, блок выявления обрыва и блок выявления межфазных замыканий, причем ключи четвертой ггуппы первыми выводами подключены через соответствующие резисторы к вторым выводам объекта контроля, вторые выводы которых объединены и подключены через переключатель к источнику питания, а управляющие входы этих ключей соединены соответственно с первым, вторым и третьим выходами блока управления, первый, второй и третий входы второго блока

0

5

0

5

0

5

0

5

сравнения соединены соответственно с первым, вторым и третьим входами первого блока сравнения, четвертый вход второго блока сравнения соединен с пятым выходом блока управления, три выхода второго блока сравнения соединены соответственно с тремя входами второго блока индикации, четвертый выход первого блока сравнения соединен с четвертым входом второго элемента совпадения,а четвертый выход второго блока сравнения соединен с третьим входом второго элемента совпадения и вторым входом первого элемента совпадения, первые шесть входов блока выявления обрыва соединены соответственно с первым - шестым выходами блока управления, седьмой, восьмой и девятый входы блока выявления обрыва соединены соответственно с вторыми выводами объекта контроля, десятый вход объединен с девятым входом блока выявления межфазных замыканий и первым выводом первого ключа пятой группы, а через переключатель соединен с источником питания, одиннадцатый вход соединен с объединенными вторыми выводами ключей пятой группы и входом третьего блока индикации, управляющий вход первого ключа пятой группы соединен с пятым выходом блока управления, а выход блока выявления обрыва соединен с первыми входами первого и второго элементов совпадения и управляющим входом третьего ключа пятой группы, первый, второй, третий, четвертый и пятый входы блока выявления межфазных замыканий соединены соответственно с первым, вторым, третьим, пятым и шестым выходами блока управления, шестой, седьмой и восьмой входы соединены соответственно с первыми выводами ключей первой группы, десятый вход блока соединен с первым выводом второго ключа пятой группы, управляющий вход которого соединен с выходом первого элемента совпадения, а выход блока выявления межфазных замыканий соединен с вторым входом второго элемента совпадения и управляющим входом четвертого ключа пятой группы, выход второго элемента совпадения соединен с вторым входом третьего блока индикации.

5

0

5

0

5

0

5

раторов, шесть элементов памяти,элемент совпадения, шесть инверторов, три элемента ИЛИ, блок индикации, причем входы выпрямителей соединены соответственно с седьмым, восьмым и девятым входами блока, выходы выпрямителей соединены соответственно с входами второго и четвертого, первого и пятого, третьего и шестого ключей первой группы, выходы которых соединены соответственно с первыми входами второго и четвертого, первого и пятого, третьего и шестого компараторов, а управляющие входы ключей пятого и шестого, третьего и четвертого, первого и второго попарно объединены и соединены соответственно с первым, вторым и третьим входами блока, вторые входы компараторов объединены и соединены с объединенными выводами резисторов, вторые- выводы которых подключены соответственно к шинам источника питания, выходы компараторов соединены соответственно с первыми входами элементов памяти, вторые входы которых объединены и соединены с пятым входом блока, выходы элементов памяти соединены соответственно с входами ключей второй группы, управляющие входы которых объединены и соединены с четвертым входом блока, а выходы этих ключей соединены через инверторы с соответствующими входами элемента совпадения, причем выходы первого, четвертого и второго ключей соединены соответственно с первыми входами первого, второго и третьего элементов ИЛИ, вторые входы которых соединены соответственно с выходами третьего, пятого и шестого ключей, а выходы элементов ИЛИ соединены с соответствующими входами блока индикации, выход элемента совпадения соединен с выходом блока, четвертый вход блока индикации соединен с десятым входом блока.

IgjL

Г

116

1

т QO/V5 Ат

| Способ контроля изоляции обмоток статоров электрических машин и устройство для его осуществления | 1985 |

|

SU1257580A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для обнаружения межвитковых замыканий в обмотках трехфазных электрических машин | 1985 |

|

SU1328772A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1991-01-23—Публикация

1989-01-10—Подача