Изобретение относится к измерительной технике и предназначено для измерения частоты синусоидального сигнала при наличии помех за время, меньшее периода измеряемого сигнала.

Целью изобретения является повышение точности измерений за счет уменьшения погрешности, вносимой помехами, т.е. за счет повышения помехозащищенности, а также расширение функциональных возможностей.

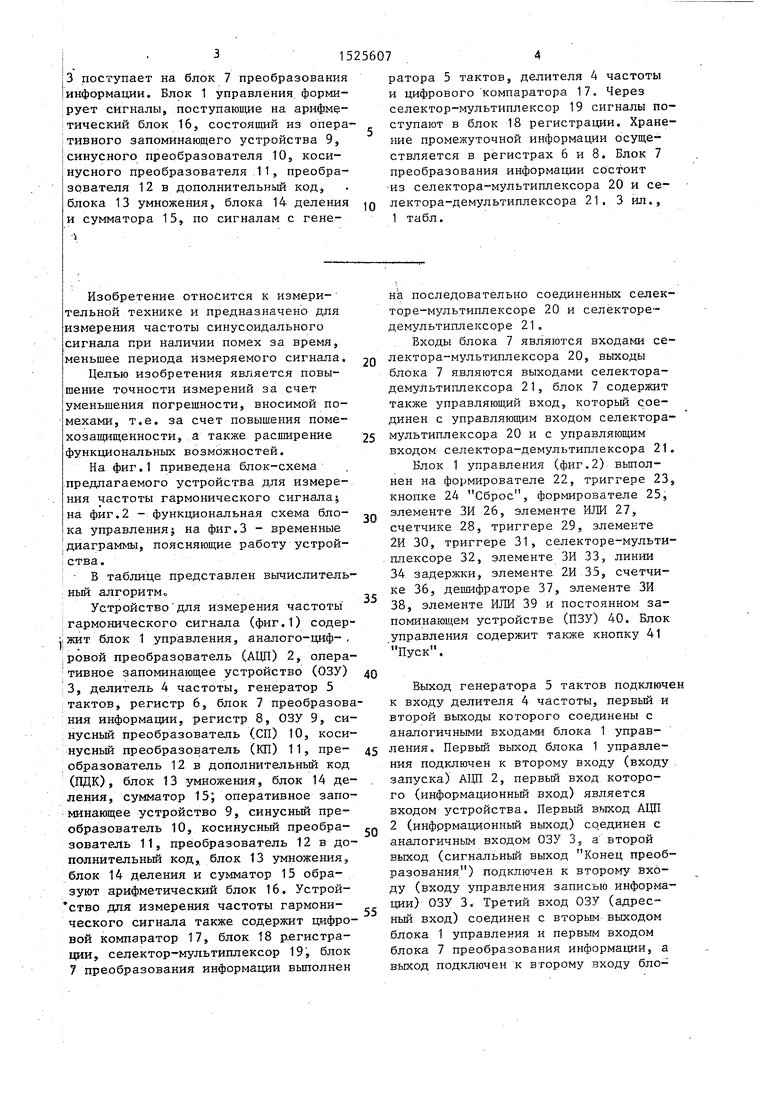

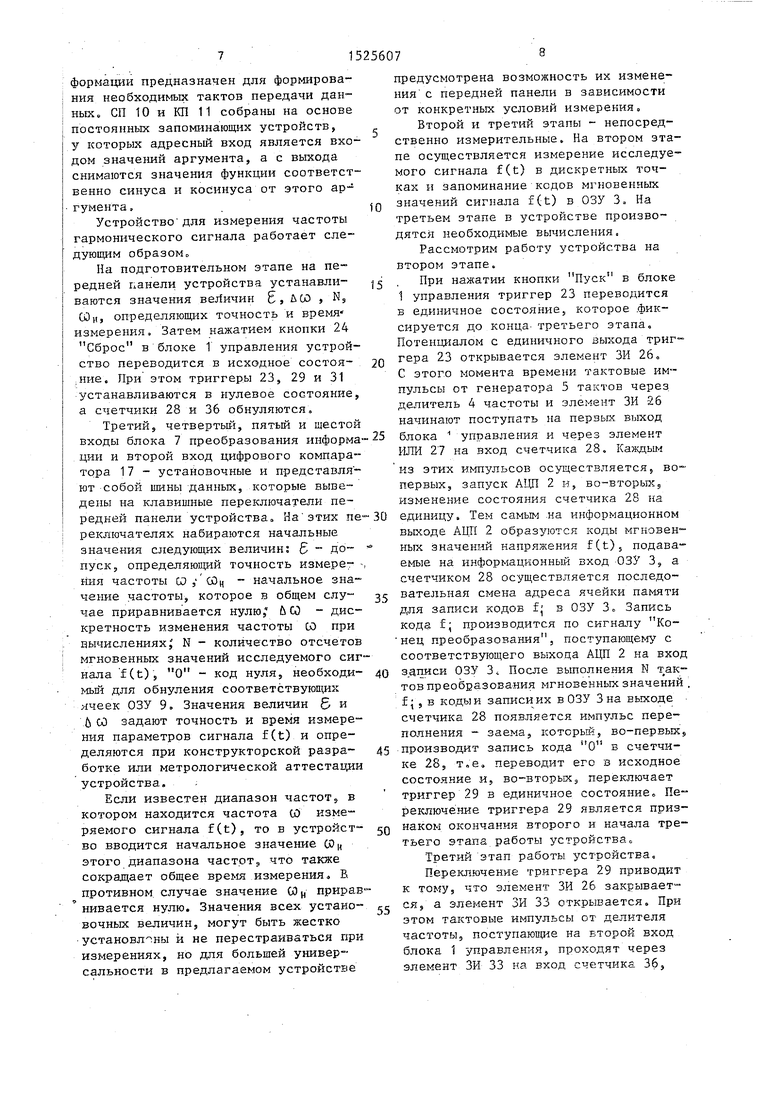

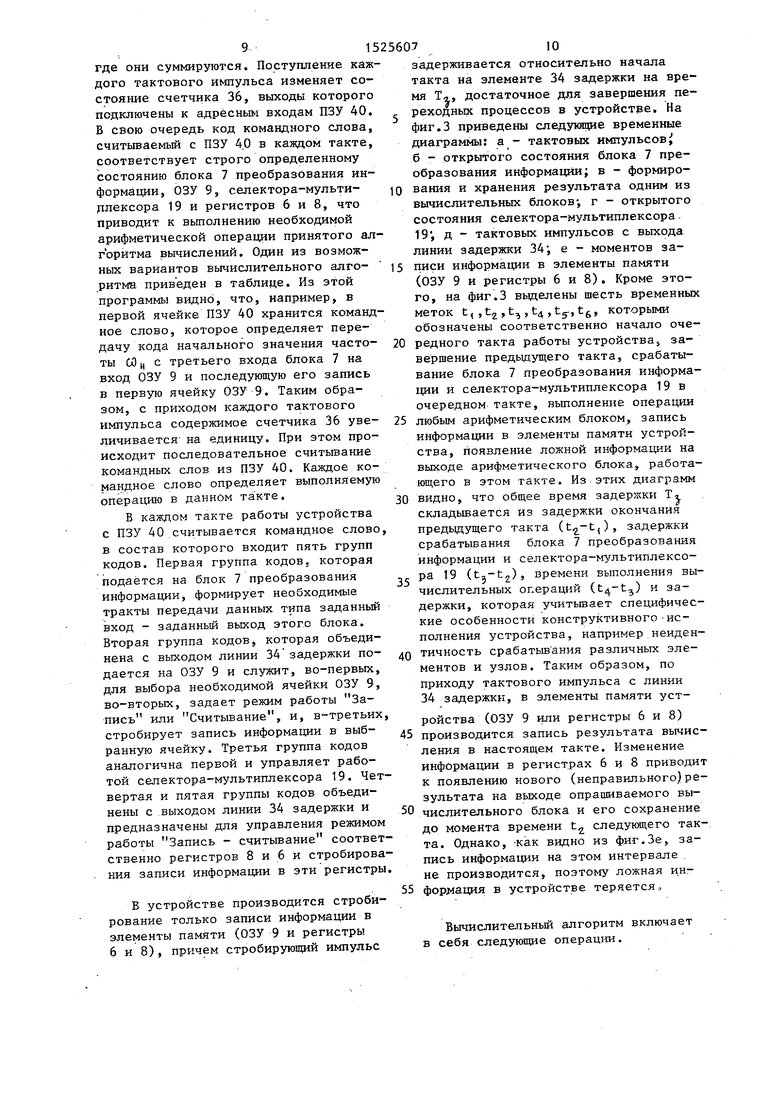

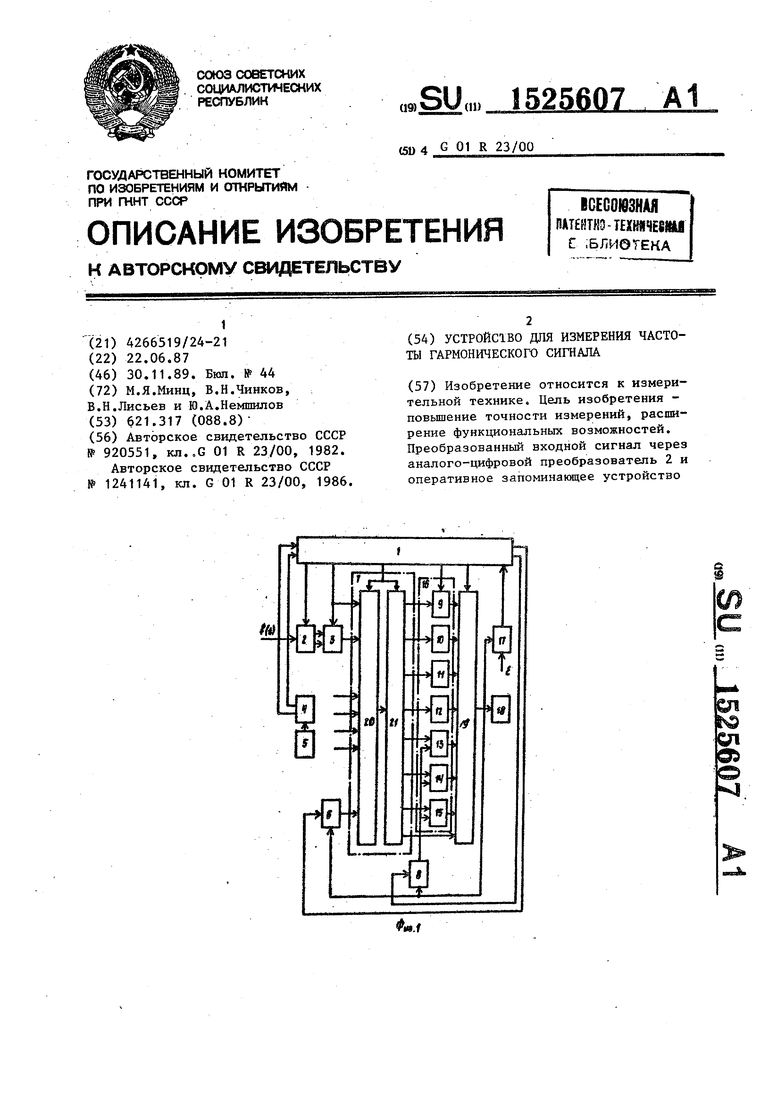

На фиг.1 приведена блок-схема предлагаемого устройства для измерения частоты гармонического сигнала; на фиг.2 - функциональная схема блока управления} на фиг.З - временные

Iдиаграммы, поясняющие работу устрой- i ства.

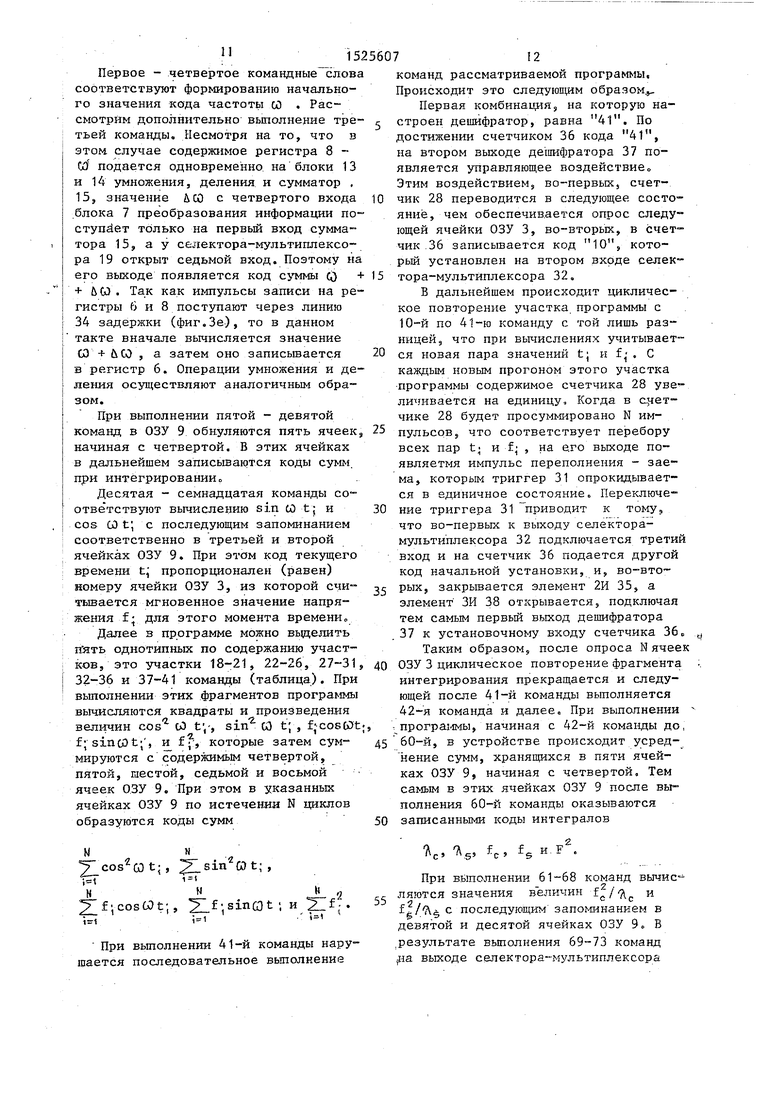

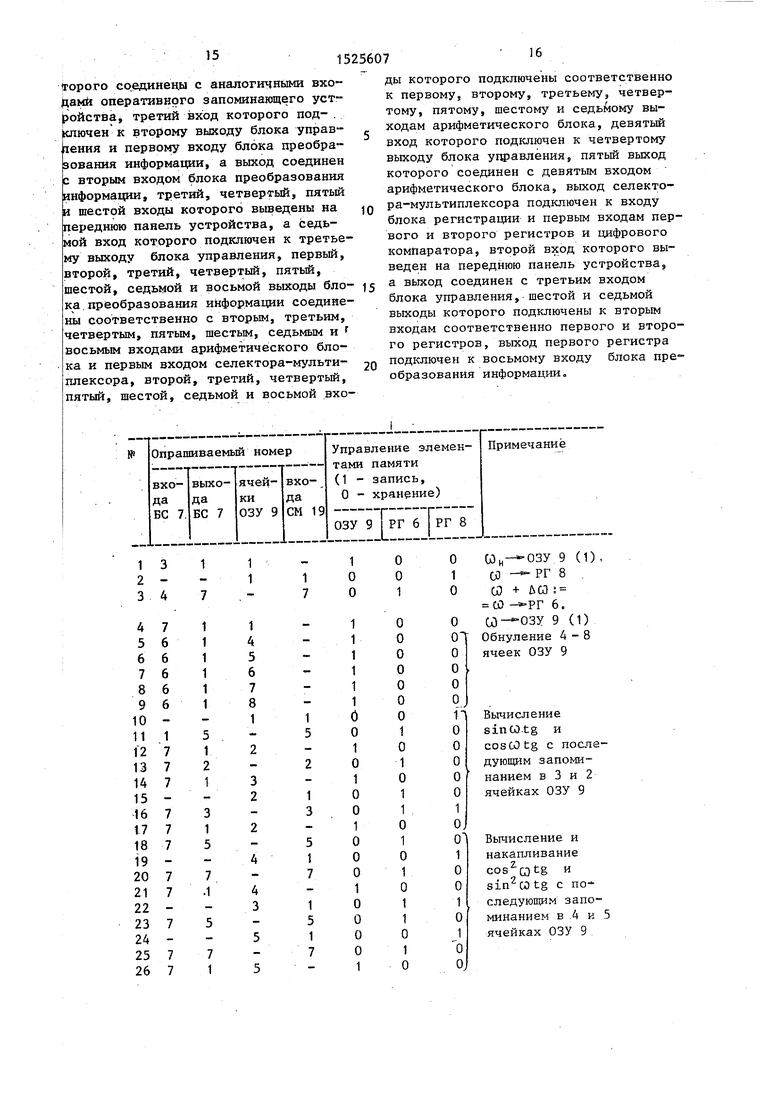

В таблице представлен вьгчислитель- ньй алгоритм

Устройство для измерения частоты гармонического сигнала (фиг.1) содерIIжит блок 1 управления, аналого-циф-, провой преобразователь (АЦП) 2, опера- тивное запоминающее устройство (ОЗУ) ;3, делитель 4 частоты, генератор 5

тактов, регистр 6, блок 7 преобразования информации, регистр 8, ОЗУ 9, си- нусньй преобразователь (СП) 10, коси- нусньш преобразователь (КП) 11, преобразователь 12 в дополнительный код (ПДК), блок 13 умножения, блок 14 деления, сумматор 15; оперативное запоминающее устройство 9, синусный преобразователь 10, косинусный преобразователь 11, преобразователь 12 в дополнительный код, блок 13 умножения, блок 14 деления и сумматор 15 образуют арифметический блок 16. Устрой- ство для измерения частоты гармонического сигнала также содержит цифровой компаратор 17, блок 18 регистрации, селектор-мультиплексор 19, блок 7 преобразования информации выполнен

0

5

0

5

0

5

0

5

на последовательно соединенных селекторе-мультиплексоре 20 и селекторе- демультиплексоре 21 ,

Входы блока 7 являются входами селектора-мультиплексора 20, выходы блока 7 являются выходами селектора- демультиплексора 21, блок 7 содержит также управляющий вход, которьй соединен с управляющим входом селектора- мультиплексора 20 и с управляющим входом селектора-демулътиплексора 21.

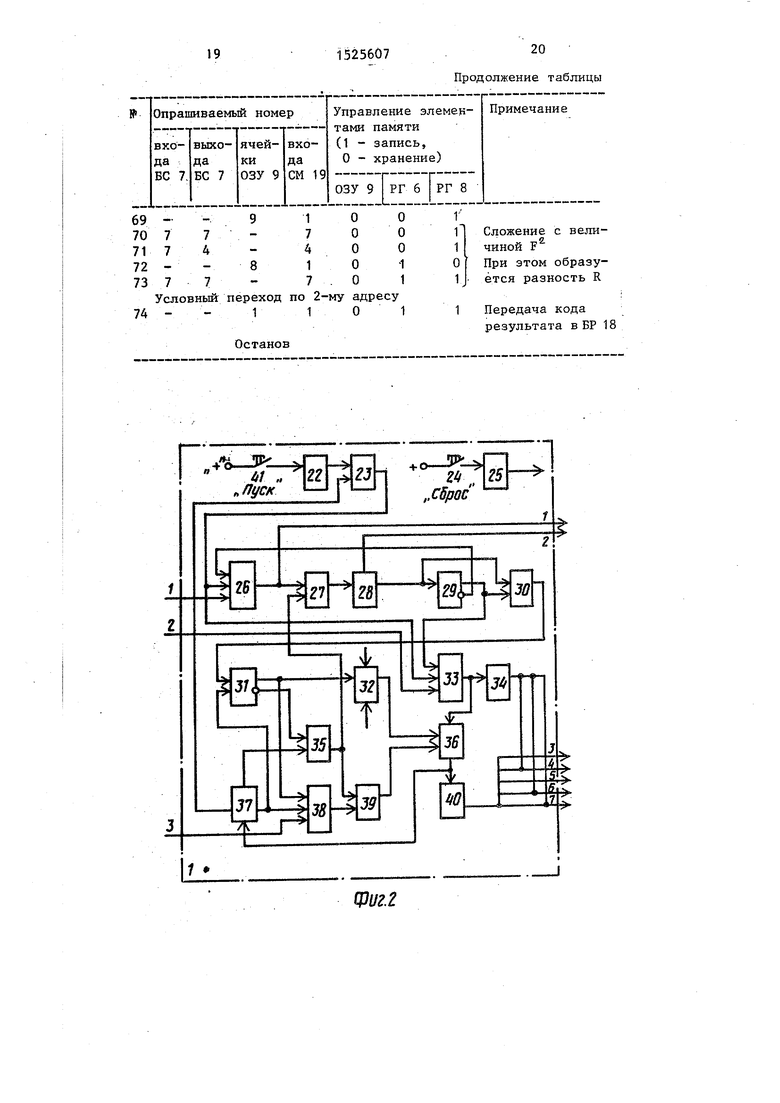

Блок 1 управления (фиг.2) вьшол- нен на формирователе 22, триггере 23, кнопке 24 Сброс, формирователе 25, элементе ЗИ 26, элементе ИЛИ 27, счетчике 28, триггере 29, элементе 2И 30, триггере 31, селекторе-мульти- . плексоре 32, элементе ЗИ 33, линии 34 задержки, элементе 2И 35, счетчике 36, дешифраторе 37, элементе ЗИ 38, элементе ИЛИ 39 и постоянном запоминающем устройстве (ПЗУ) 40. Блок управления содержит также кнопку 41 .

Выход генератора 5 тактов подключен к входу делителя 4 частоты, первый и второй выходы которого соединены с аналогичными входами блока 1 управления. Первый выход блока 1 управления подключен к второму входу (входу . запуска) AIJJI 2, первый вход которого (информационньй вход) является входом устройства. Первый выход АЦП 2 (инфррмационньй вьтход) срединен с аналогичным входом ОЗУ 3, а второй выкод (сигнальньй выход Конец преобразования) подключен к второму входу (входу управления записью информации) ОЗУ 3. Третий вход ОЗУ (адрес- ньй вход) соединен с вторым выходом блока 1 управления и первым входом блока 7 преобразования информации, а выход подключен к второму входу блока 7. Третий, четвертый, пятый и шестой входы блока 7 преобразования информации - установочные и вьгеедены на переднюю панель устройства. Восьмой вход блока 7 преобразования информации (управляющий вход) соединен с третьим выходом блока 1 управления а первьй, второй, третий, четвертый,

пятый, шестой, седьмой и восьмой вы-

ходы блока 7 преобразования информации подключены соответственно к входам ОЗУ 9, СП 10, КП 11, ПДК 12, пер вьм входам блока 13 умножения, блока 14 деления, сумматора 15 и первому входу селектора-мультиплексора 19. Выходы ОЗУ 9, СП 10, КП 11, ПДК 12, блоков 13 и 14, умножения и деления, сумматора 15 соединены соответственно с .вторым., третьим, четвертым, пя- тым, шестым, седьмым и восьмым входами селектора-мультиплексора 19. Девятьй вход селектора-мультиплексора 19 (управляющий вход) подключен к четвертому выходу блока 1 управле- ния, пятьй выход которого соединен с вторым входом (объединенным адресным и управляющим записью входами) ОЗУ 9. Выход селектора-мультиплексора 19 подключен к входу блока 18 ре- гистрации и первым входам регистров 6 и 8 и цифрового компаратора 17, второй вход которого является уста-, новочньм и выведен на переднюю панел устройства для задания величины допуска, определяющего точность измерения частоты W . Выход цифрового компаратора 17 соединен с третьим входом блока 1 управления, шестой и седьмой выходы которого подключены к вторым входам соответственно регистров 8 и 6. Выход регистра 8 соединен со вторыми входами блоков 13 и 14, умножения и деления и сумматора 15. Выход регистра 6 подключен к седьмому входу блока 7 преобразования информации.

Кнопку Пуск блока 1 управления последовательно через формирователь

22подключена к первому (единичному) входу триггера 23, второй вход которого (нулевой) соединен с первым выходом депифратора 37. Выход триггера

23подключен первым входам элементов

ЗИ 26 и 33, вторые входы которых яв- ляются первым и вторым входами блока 1 управления. Выход элемента ЗИ 26 является первым выходом блока .1 управления и одновременно соединен с

5 О Q с

0

с

5

первым входом элемента ИЛИ 27, у которого второй вход подключен к выходу элемента 2И 35 и первому входу элемента ИЛИ 39. Выход элемента ИЛИ 27 соединен с суммирующим входом счетчика 28, первый выход которого является вторым выходом блока 1 управления , Второй выход (выход переполнения - заема) счетчика 28 подключен к первому входу элемента 2И 30 и входу триггера 29, второй выход которого (инверсный выход) соединен с третьим входом элемента ЗИ 26. Первый выход (прямой выход) триггера 29 подключен к третьему входу элемента ЗИ 33 и второму входу элемента 2И 30 Выход элемента 2И 30 соединен с первым входом триггера 31, второй (инверсный) выход которого подключен к первому входу элемента 2И 35о Первый (прямой) выход триггера 31 соединен с первым входом элемента ЗИ 38 и входом селектора-мультиплексора 32, на втором и третьем входах которого набраны коды начальной установки счетчика 36. Выход селектора-мультиплексора 32 подключен к первому входу (входу ввода дополнения) счетчика 36, второй вход которого (счетный вход) соединен с выходом элемента ЗИ 33 и входом линии 34 задержки, а третий вход (вход записи кода дополнения) пбд- ключен к выходу элемента ИЛИ 39. Выход счетчика 36 соединен с входом дешифратора 37 и входом ПЗУ 40, выход которого представляет шину данных, разведенную .на третий, четвертый и совместно с выходом линии 34 задержки на пятый, шестой и седьмой выходы блока 1 управления. Второй выход дешифратора 37 подключен к второму входу элемента 2И 35, а третий вькод соединен с вторыми входами триггера 31 и элемента ЗИ 38, третий вход которого является одноименным входом блока 1 управления. Выход элемента ЗИ 38 подключен к второму входу элемента ИЛИ 39, Кнопка 24 Сброс последовательно через формирователь 25 соединена с установочными входами триггеров 23, 29 н. 31 и счетчиков 28 и 36

Наличие двух выходов у делителя 4 частоты связано с тем, что дискрети- за11ия входного сигнала .и обработка результатов измерений в устройстве осуществляется с различной тактовой частотой Блок 7 преобразования инормации предназначен для формирования необходимых тактов передачи даных. СП 10 и КП 11 собраны на основе остоянньк запоминающих устройств, KOTopbiX адресный вход является вхоом значе1шй аргумента, а с выхода снимаются значения функции соответственно синуса и косинуса от этого аргумента ,

Устройство для измерения частоты гармонического сигнала работает слеующим образомо

На подготовительном этапе на передней панели устройства устанавливаются значения веЛичин 5, ДСО , Nj Ck),,, определяющих точность и время измерения. Затем нажатием кнопки 24 Сброс в блоке Т управления устройство переводится в исходное состоя- :Ние. При этом триггеры 23, 29 и 31 устанавливаются в нулевое состояние, а счетчики 28 и 36 обнуляются.

Третий, четвертый, пятый и шестой входы блока 7 преобразования информации и второй вход цифрового компаратора 17 - установочные и представляют собой шины данных, которые выведены на клавишные переключатели передней панели устройства. На этих переключателях набираются начальные значения следующих величин: - до- пуск, определяющий точность измере- , ния частоты СО, сОц - начальное значение частоты, которое в общем случае приравнивается нулю, Ь СО - дискретность изменения частоты СО при вычисленияхJ N - количество отсчетов мгновенных значений исследуемого сигнала f(t), О - код нуля, необходи- ь-шй для обнуления соответствующих ячеек ОЗУ 9. Значения величин б и ,6 СО задают точность и время измерения параметров сигнала f(t) и определяются при конструкторской разработке или метрологической аттестации устройства.

Если известен диапазон частот, в котором находится частота ОЭ измеряемого сигнала f(t), то в устройст во вводится начальное значение СО ц этого диапазона частотj что также сокращает общее время измерения. Е противном случае значение 00 прирав- нивается нулю. Значения всех установочных величин, могут быть жестко установл ны и не перестраиваться при измерениях, но для большей универсальности в предлагаемом устройстве

предусмотрена возможность их изменения с передней панели в зависимости от конкретных условий измерения,

Второй и третий этапы - непосредственно измерительные. На втором этапе осуществляется измерение исследуемого сигнала f(t) в дискретных точках и запоминание кодов мгновенных

значений сигнала f(t) в ОЗУ 3. На третьем этапе в устройстве производятся необходимые вычисления.

Рассмотрим работу устройства на втором этапе.

. При нажатии кнопки Пуск в блоке 1 управления триггер 23 переводится в единичное состояние, которое .фиксируется до конца- третьего этапа. Потенциалом с единичного выхода триггера 23 открывается элемент ЗИ 26, С этого момента времени тактовые им-- пульсы от генератора 5 тактов через, делитель 4 частоты и элемент ЗИ 26 начинают поступать на первых выход

блока управления и через элемент 1ШИ 27 на вход счетчика 28. Каждьм

из этих импульсов ос уществляется, во- первых, запуск АЦП 2 и, во-вторыхj изменение состояния счетчика 28 на

единицу. Тем самым .на информационном выходе АЦП 2 образуются коды мгновенных значений напряжения fCt), подаваемые на информационный вход ОЗУ 3, а счетчиком 28 ос уществляется последовательная смена адреса ячейки памяти для записи кодов fj в ОЗУ 3„ Запись кода f; производится по сигналу Ко нец преобразования 5 поступающему с соответствующего выхода АЦП 2 на вход

записи ОЗУ 3 После выполнения N товпреобразования мгновенных значений . f , в коды и записи их в ОЗУ 3 на выходе счетчика 28 появляется импульс переполнения - заема, которьш, во-первых,

производит запись кода О в счетчике 28, т,е, переводит его в исходное состояние и, во-вторых, переключает триггер 29 в единичное состояние, Пе реключёние триггера 29 является признаком окончания второго и начала третьего этапа работы устройства. Третий этап работы, устройства. Переключение триггера 29 приводит к тому, что элемент ЗИ 26 закрывается, а элемент ЗИ 33 открывается. При этом тактовые импульсы от делителя частоты, поступающие на второй вход блока 1 управления, проходят через элемент ЗИ 33 на вход счетчика 36}

где они суммируются. Поступление каждого тактового импульса изменяет состояние счетчика 36, выходы которого подключены к адресным входам ПЗУ 40. В свою очередь код командного слова, считываемый с ПЗУ 40 в каждом такте, соответствует строго определенному состоянию блока 7 преобразования информации, ОЗУ 9, селектора-мульти- длексора 19 и регистров 6 и 8, что приводит к вьшолнению необходимой арифметической операции принятого алгоритма вычислений. Один из возможных вариантов вычислительного алгоритма приведен в таблице. Из этой программы видно, что, например, в первой ячейке ПЗУ 40 хранится командное слово, которое определяет передачу кода начального значения частоты СО ц с третьего входа блока 7 на вход ОЗУ 9 и последующую его запись в первую ячейку ОЗУ 9. Таким образом, с приходом каждого тактового импульса содержимое счетчика 36 увеличивается на единицу. При этом происходит последовательное считьшание командных слов из ПЗУ 40. Каждое командное слово определяет выполняемую операцию в данном та кте.

В каждом такте работы устройства с ПЗУ 40 считывается командное слово в состав которого входит пять групп кодов. Первая группа кодов, которая подается на блок 7 преобразования информации, формирует необходимые тракты передачи данных типа заданньй вход - заданный выход этого блока. Вторая группа кодов, которая объединена с выходом линии 34 задержки подается на ОЗУ 9 и слуткит, во-первых, для выбора необходимой ячейки ОЗУ 9, во-вторых, задает режим работы Запись или Считывание, и, в-третьих стробирует запись информации в выбранную ячейку. Третья группа кодов аналогична первой и управляет работой селектора-мультиплексора 19. Четвертая и пятая группы кодов объединены с выходом линии 34 задержки и предназначены для управления режимом работы Запись - считывание соответственно регистров 8 и 6 и стробирова ния записи информации в эти регистры

В устройстве производится строби- рование только записи информации в элементы памяти (ОЗУ 9 и регистры. 6 и 8), причем стробирующий импульс

задерживается относительно начала такта на элементе 34 задержки на время То, достаточное для завершения переходных процессов в устройстве. На фиг.З приведены следующие временные диаграммы: а - тактовых импульсовi б - открытого состояния блока 7 преобразования информации; в - формирования и хранения результата одним из вычислительных блоков-, г - открытого состояния селектора-мультиплексора. 19, д - тактовых импульсов с выхода линии задержки 34; е - моментов зациси информации в элементы памяти (ОЗУ 9 и регистры 6 и 8). Кроме этого, на фиг.З выделены шесть временных меток t, ,t2 , t, , Ц ,tj., tg, которыми обозначены соответственно начало очередного такта работы устройства; завершение предьщущего такта, срабатывание блока 7 преобразования информации и селектора-мультиплексора 19 в очередном такте, вьтолнение операции

любым арифметическим блоком, запись информации в элементы памяти устройства, появление ложной информации на выходе арифметического блока, работающего в этом такте. Из этих диаграмм

видно, что общее время задержки Т, складьшается из задержки окончания предыдущего такта (,), задержки срабатывания блока 7 преобразования информации и селектора-м льтиплексора 19 (tj-t), времени выполнения вычислительных операций () и задержки, которая учитьшает специфические особенности конструктивного-исполнения устройства, например неидентичность срабатьш ания различных элементов и узлов. Таким образом, по приходу тактового импульса с линии 34 задержки, в элементы памяти устройства (ОЗУ 9 или регистры 6 и 8)

производится запись результата вычисления в настоящем такте. Изменение информации в регистрах 6 и 8 приводит к появлению нового (неправильного)результата на выходе опрашиваемого вычислительного блока и его сохранение до момента времени t следующего такта. Однако, -как видно из фиг.Зе, запись информации на этом интервале не производится, поэтому ложная и.нформация в устройстве теряется о

Вычислительный алгоритм включает в себя следующие операц1Ш.

Первое - четвертое комавдные слова соответствуют формированию начального значения кода частоты Q . Рассмотрим дополнительно вьшолнение третьей команды. Несмотря на то, что в этом, случае содержимое регистра 8 - СО подается одновременно на блоки 13 и 14 умножения, деления и сумматор , 15, значение &СО с четвертого входа .блока 7 преобразования информации по- ступйет только на первьй вход сумма тора 15, а у селектора-мультиплексора 19 открыт седьмой вход. Поэтому на его выходе появляется код суммы СО + + ЬСО , Так как импульсы записи на регистры 6 и 8 поступают через линию 34 задержки (фиг.Зе), то в данном такте вначале вычисляется значение СО + UCO , а затем оно записывается в регистр 6. Операции умножения и деления осуществляют аналогичным образом.

При выполнении пятой - девятой

команд в ОЗУ 9 обнуляются пять ячеек, 25 пульсов, что соответствует перебору

всех пар t- и f; , на его выходе поначиная с четвертой. В этих ячейках в дальнейшем записьшаются коды сумм, при интегрированиио

Десятая - семнадцатая команды со- отве тствуют вычислению sin сО t; и cos СОt; с последующим запоминанием соответственно в третьей и второй ячейках ОЗУ 9. При этом код текущего времени t пропорционален (равен) номеру ячейки ОЗУ 3, из которой счи- тьшается мгновенное значение напряжения f- для этого момента времени.

Далее в программе можно вьщелить Пить однотипных по содержанию участков, это участки 18-21, 22-26, 27-31, 32-36 и 37-41 команды (таблица). При выполнении этих фрагментов программы вычисляются квадраты и произведения величин cos оЭ t ,-, sin &0 t; , f;costx5t;. f; sin cot; , i f; , которые затем суммируются с содержимым четвертой, пятой, шестой, седьмой и восьмой ячеек ОЗУ 9. При этом в указанных ячейках ОЗУ 9 по истечении N циклов образуются коды сумм

1 являетмя импульс переполнения - заема, которым триггер 31 опрокидывается в единичное состояние. Переключе30 ние триггера 31 приводит к тому, что во-первьпс к выходу селектора- мультиплексора 32 подключается трети вход и на счетчик 36 подается другой код начальной установки, и, во-вто

22 рых, закрывается элемент 2И 35, а элемент ЗИ 38 открывается, подключая тем самым первый выход дешифратора 37 к установочному входу счетчика 36 Таким образом, после опроса N ячее

40 ОЗУ 3 циклическое повторение фрагмента интегрирования прекращается и следующей после 41-й команды вьшолняется 42-я команда и далее. При выполнении i .програ Ф Ы, начиная с 42-й команды до

45 60-й, в устройстве происходит усред- нение сумм, хранящихся в пяти ячейках ОЗУ 9, начиная с четвертой. Тем самым в этих ячейках ОЗУ 9 после выполнения 60-й команды оказываются

50 записанными коды интегралов

команд рассматриваемой программы. Происходит это следующим образом.,Первая комбинация, на которую настроен дешифратор, равна 41. По достижении счетчиком 36 кода 41, на втором выходе де щифратора 37 появляется управляющее воздействие Этим воздействием, во-первых, счетчик 28 переводится в следующее состояние, чем обеспечивается опрос следующей ячейки ОЗУ 3, во-вторых, в счетчик 36 записывается код 10, который установлен на втором входе селектора-мультиплексора 32,

В дальнейшем происходит циклическое повторение участка программы с 10-й по 41-ю команду с той лишь разницей, что при вычислениях учитывается новая пара значений t; и f , С каждым новым прогоном этого участка программы содержимое счетчика 28 уве личивается на единицу. Когда в с,чет- чике 28 будет просуммировано N имвсех пар t- и f; , на его выходе являетмя импульс переполнения - заема, которым триггер 31 опрокидывается в единичное состояние. Переключение триггера 31 приводит к тому, что во-первьпс к выходу селектора- мультиплексора 32 подключается третий вход и на счетчик 36 подается другой код начальной установки, и, во-вто

рых, закрывается элемент 2И 35, а элемент ЗИ 38 открывается, подключая тем самым первый выход дешифратора 37 к установочному входу счетчика 36„ Таким образом, после опроса N ячеек

ОЗУ 3 циклическое повторение фрагмента интегрирования прекращается и следующей после 41-й команды вьшолняется 42-я команда и далее. При выполнении - програ Ф Ы, начиная с 42-й команды до,

60-й, в устройстве происходит усред- нение сумм, хранящихся в пяти ячейках ОЗУ 9, начиная с четвертой. Тем самым в этих ячейках ОЗУ 9 после выполнения 60-й команды оказываются

записанными коды интегралов

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вывода информации | 1985 |

|

SU1285460A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Устройство для измерения характеристик синусоидального сигнала | 1990 |

|

SU1758575A1 |

| Устройство для распознавания образов | 1989 |

|

SU1709359A1 |

| Устройство для отладки многопроцессорных систем | 1988 |

|

SU1644145A1 |

| Многоканальный программируемый преобразователь код-фаза | 1990 |

|

SU1742998A1 |

| Многоканальное устройство для сопряжения ЭВМ | 1988 |

|

SU1695311A1 |

| Устройство пункта управления системы телемеханики | 1986 |

|

SU1374265A1 |

| КОДОИМПУЛЬСНОЕ ПЕРЕДАЮЩЕЕ УСТРОЙСТВО С СОКРАЩЕНИЕМ ИЗБЫТОЧНОСТИ ИНФОРМАЦИИ | 2001 |

|

RU2234738C2 |

Изобретение относится к измерительной технике. Цель изобретения - повышение точности измерений, расширение функциональных возможностей. Преобразованный входной сигнал через аналого-цифровой преобразователь 2 и оперативное запоминающее устройство 3 поступает на блок 7 преобразования информации. Блок 1 управления формирует сигналы, поступающие на арифметический блок 16, состоящий из оперативного запоминающего устройства 9, синусного преобразователя 10, косинусного преобразователя 11, преобразователя 12 в дополнительный код, блока 13 умножения, блока 14 деления и сумматора 15, по сигналам с генератора 5 тактов, делителя 4 частоты и цифрового компаратора 17. Через селектор - мультиплексор 19 сигналы поступают в блок 18 регистрации. Хранение промежуточной информации осуществляется в регистрах 6 и 8. Блок 7 преобразования информации состоит из селектора - мультиплексора 20 и селектора - демультиплексора 21. 3 ил., 1 табл.

М

COSTCO tj, sin Ot;,

NNH ,,

2Ifvcos60t;, 21f sinCOt . « 2Ifbii i

При вьтолнении 41-й команды нарушается последовательное вьшолнение

г, 0 s и F .

При выполнении 61-68 команд вычис- ляются значения величин f / -Ap и f / Лг: с последующим запоминанием в

6 -

девятой и десятой ячейках ОЗУ 9. В результате выполнения 69-73 команд -la выходе селектора-мультиплексора

19 образуется код разности. ( + +f5/ Aa)R В этом месте программы (по необходимости) нарушается после- . довательное выполнение команд рас- 5 сматриваемой программы. Это объясняется тем, что код разности R является признаком окончания вычислительного процессао Если он равен или меньшеjS , то заданная точность вычисления 10 частоты СО достигнута и вычисления завершаются. В противном случае происходит возврат ко второй команде и вычисления повторяются для следующе-. го значения частоты. Возврат ко вто- 15 рой команде происходит следующим об- разом. Второй код, на которьй настроен дешифратор 37, равен 73. Если код на счетчике 36 равне 73, а на цифровом компараторе код R больше , 20 то импульсом с дешифратора 37 в счетчик 36 записывается начальный код, равный двум, и триггер 31 устанавливается в нулевое состояние. В дальнейшем описанньш алгоритм повторяет- ся до тех пор, пока код R не становится меньшим или равным . Для условия R на выходе цифрового компаратора 17 формируется управляющее воздействие, которым запирается 30 элемент ЗИ 38, и управляющий импульс начальной установки на счетчик 36 не происходит. Поэтому следующей выполняемой командой будет 74-я команда, при вьтолнении которой из первой 35 ячейки ОЗУ 9 извлекается результат - код частоты СО и передается в блок 18 регистрации.

На номер последней вычислительной команды настроен третий код дешифра- 40 тора 37. В этом случае импульсом с третьего выхода дешифратора.37- триггер 23 переключается в нулевое состояние и подача тактовых испульсов через элементы ЗИ 33, 38 прекращает- 45 ся. На этом третий этап, а в целом и алгоритм измерения 0) заканчивается.

Повышение точности измерений обеспечивается за счет уменьшения случай- 50 ной составляющей погрешности, вносимой внешними и внутренними помехами.

Для приближенной оценки погрешности, вносимой помехами, можно воспользоваться хорошо известным в измере- ВИЯХ соотношением

Sy

У

у -.

относительное значение

случайной составляющей погрешности одного измерения (в нашем случае аналого- цифрового преобразования одного мгновенного значения, которое можно принять

В УХ

I).

Г

откуда следует, что погрешность вносимая помехами, будет не менее, чем в -4N раз меньше по сравнению с погрешностями известных способов и устройств.

Расширение функциональных возможностей достигается за счет того, что появляется возможность измерения тем же устройством дополнительно амплитуды и фазы гармонического сигнала соответственно по формулам

J (|..) , (

1J СО SO

::- - со

SO

где f ,f ,., Хсо значение тех

же величин на измеренной частоте СО СОо ..

Формула изобретения

Устройство для измерения частоты гармонического сигнала, содержащее аналого-цифровой преобразователь, цифровой компаратор, первьп регистр, последовательно соединенные второй регистр и арифметический блок, блок регистрации, вход аналого-цифрового преобразователя является входом устройства, отличающееся тем, что, с целью повьш1ения точности и расширения функциональных возможностей, в него введены последовательно соединенные генератор тактов, делитель частоты и блок управления, оперативное -запоминающее устройство, блок преобразования информации, селектор-мультиплексор, второй выход делителя частоты соединен с вторым входом блока управления, первьй выход блока управления подключен к второму входу аналого-цифрового преобразователя, первый и второй выходы коiroporo соединещл с аналогичными вхо- Аамй оперативного запоминанлцего уст- ойства, третий вход которого под-, йпючен к второму выходу блока управ- пения и первому входу блока преобразования информации, а выход соединен с вторым входом блока преобразования информации, третий, четвертый, пятый и шестой входы которого выведены на переднюю панель устройства, а седьмой вход которого подключен к третьему выходу блока управления, первьй, второй, третий, четвертый, пятый, тестой, седьмой и восьмой выходы бло- ка преобразования информации соединены соответственно с вторым, третьим, четвертым, пятым, шестым, седьмым и f восьмым входами арифметического блока и первым входом селектора-мульти- плексора, второй, третий, четвертьй, пятый, шестой, седьмой и восьмой входы которого подключены соответственно к первому, второму, третьему, четвертому, пятому, шестому и седьмому выходам арифметического блока, девятый вход которого подключен к четвертому выходу блока управления, пятый выход которого соединен с девятым входом арифметического блока, выход селектора-мультиплексора подключен к входу блока регистрации и первьм входам первого и второго регистров и цифрового комйаратора, второй вход которого выведен на переднюю панель устройства, а выход соединен с третьим входом блока управления, шестой и седьмой выходы которого подключены к вторым входам соответственно первого и второго регистров, выход первого регистра подключен к восьмому входу блока пре образования информации.

9 (1) , СО - РГ 8 .

СО + йса s со 6.

9(1) Обнуление 4-8 ячеек ОЗУ 9

Вьмисление sinCO.tg и cosODtg с после- запоминанием в 3 и 2 ячейках ОЗУ 9

Вычисление и накапливание и tg с ПО следующим запоминанием в .4 и 5 ячейках ОЗУ 9

Продолжение таблицы

sinCOtg/N) и запоминание 8,4,5,6 и 7 ячейках ОЗУ 9 Вычгсление сум fc/ A.-bfs/ s. перевод ее в дополнительный код

9

8

переход по 2-му адресу

1 1 О 1

Останов

Продолжение таблицы

Сложение с величиной F

При этом образуется разность R

Передача кода результата вБР 18

IL

a) U J

«I

{

3)

Фиг.З

| Способ измерения инфранизкой частоты синусоидального сигнала | 1979 |

|

SU920551A1 |

| Способ измерения частоты гармонического сигнала | 1984 |

|

SU1241141A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1989-11-30—Публикация

1987-06-22—Подача