1

Изобретение относится к импул},с- ной технике и может быт.. использовл- но в устройствах для контроля, обработки и передачи информации.

Цель Изобретения - расширение функциональных возможностей за счет обеспечения контроля пачек импульсов а также контроля импульсных последовательностей с неравномерным периодом и повышение помехоустойчивости.

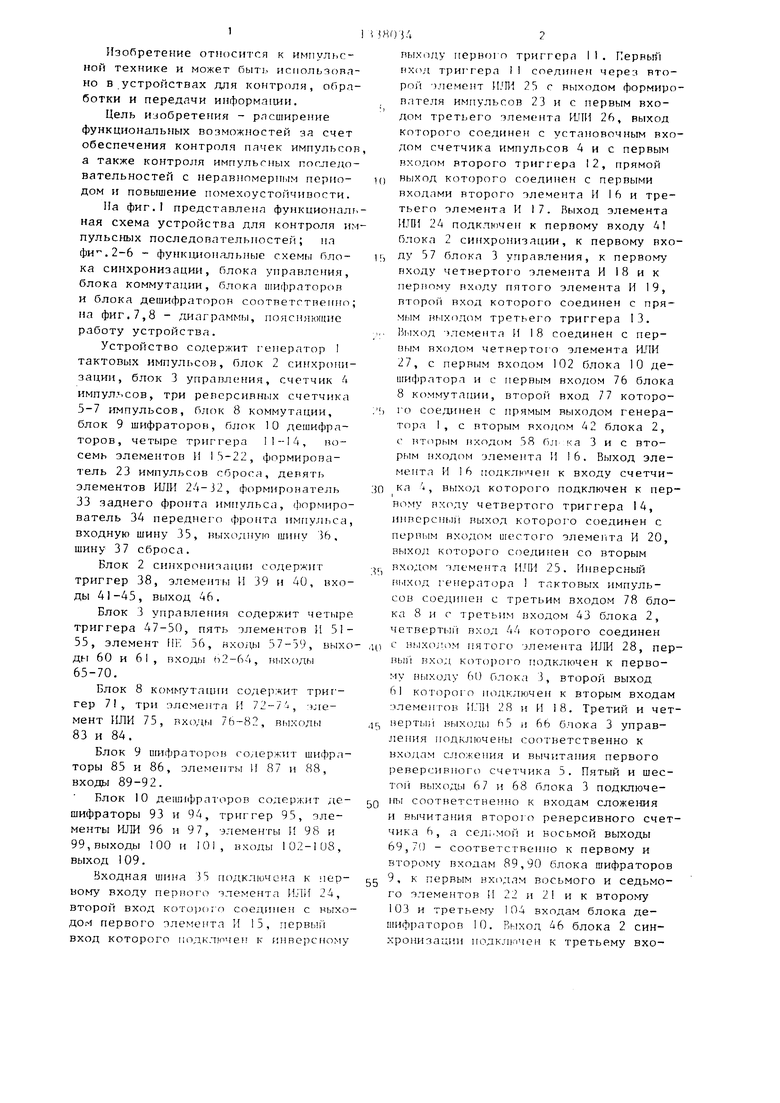

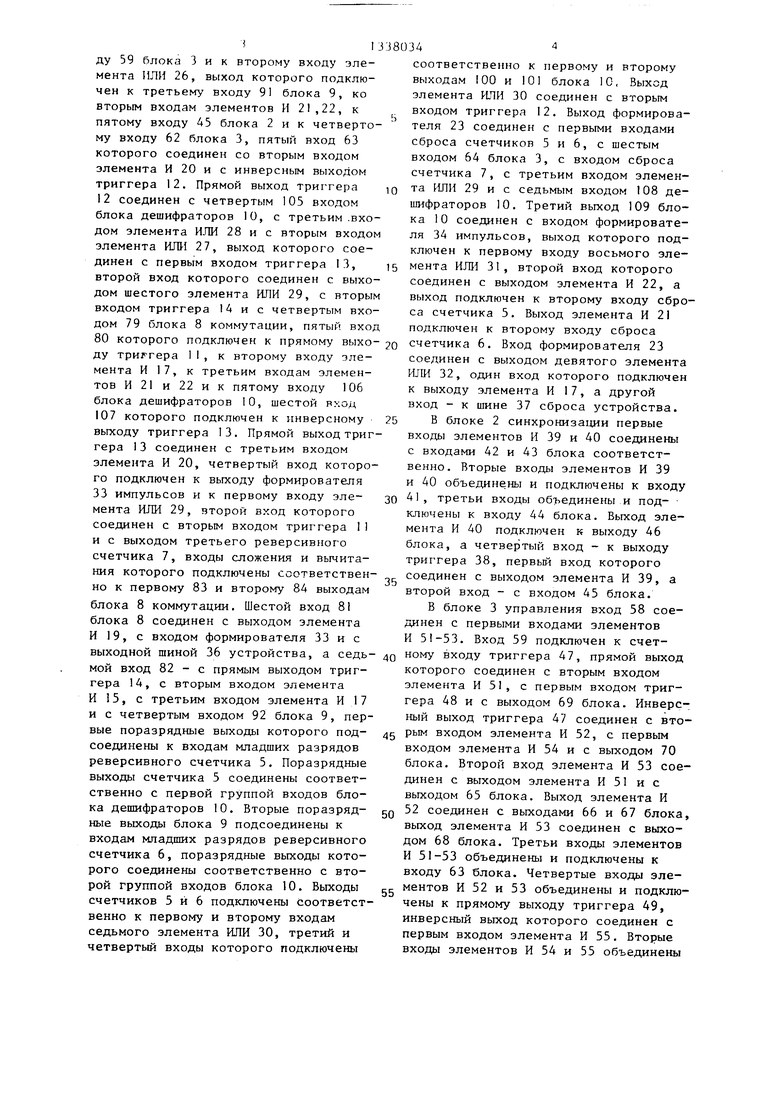

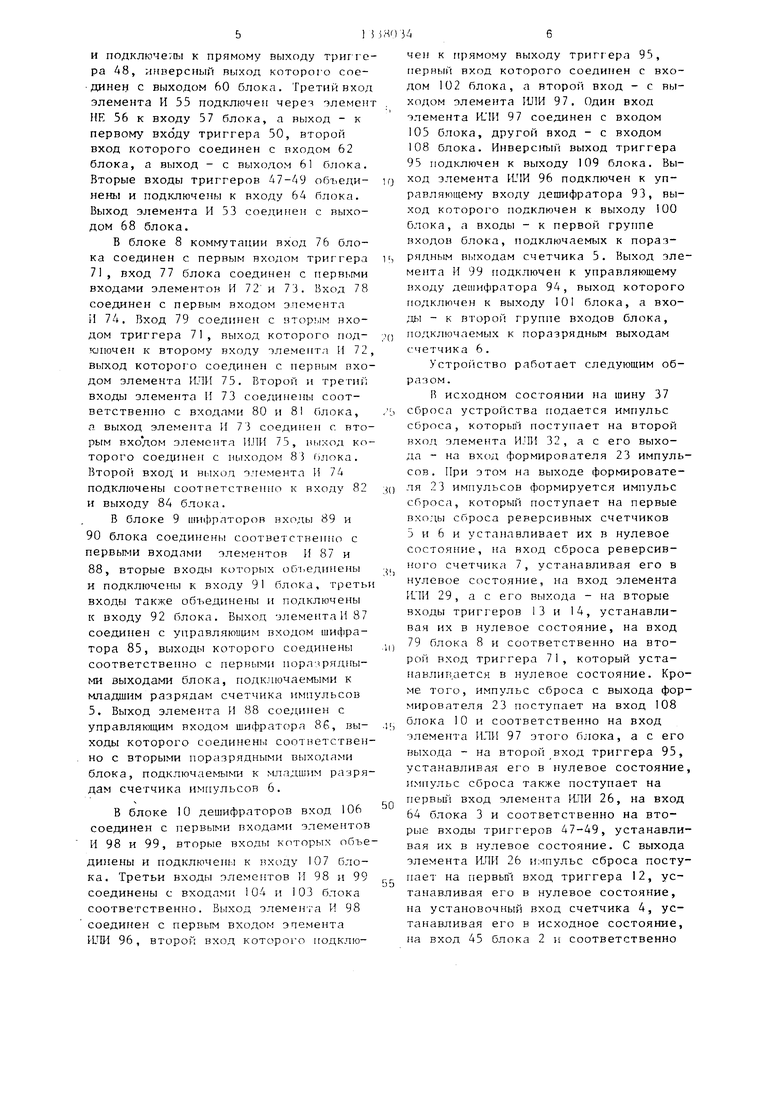

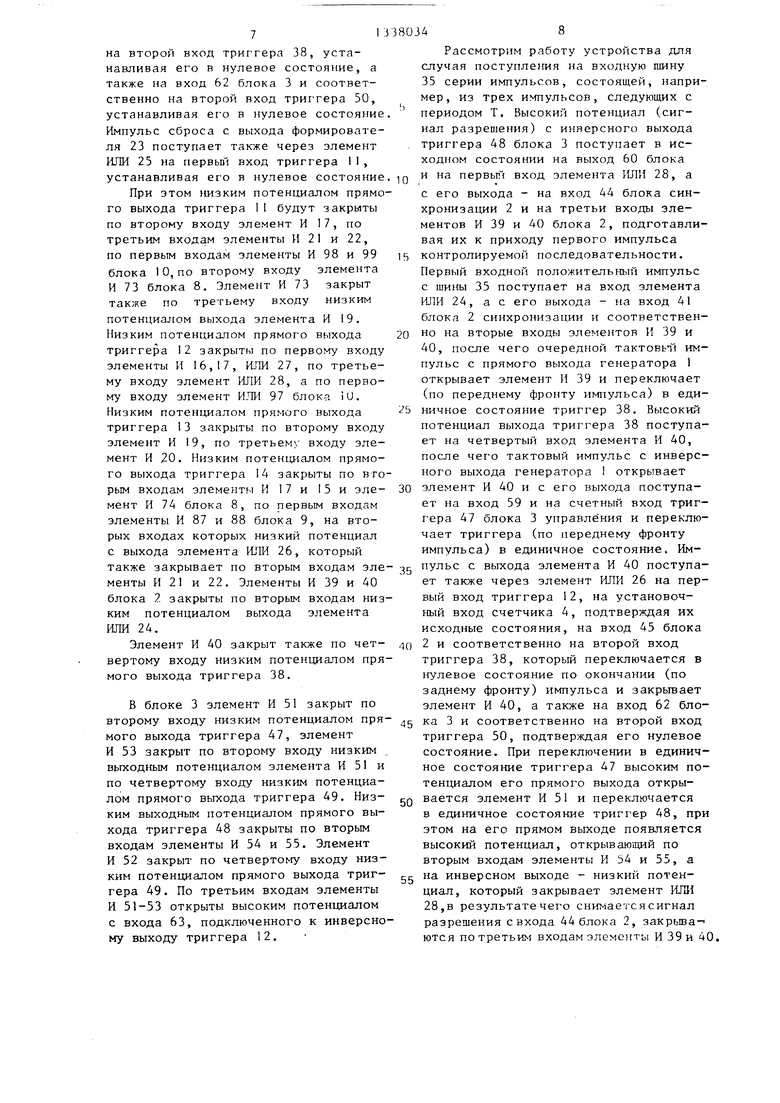

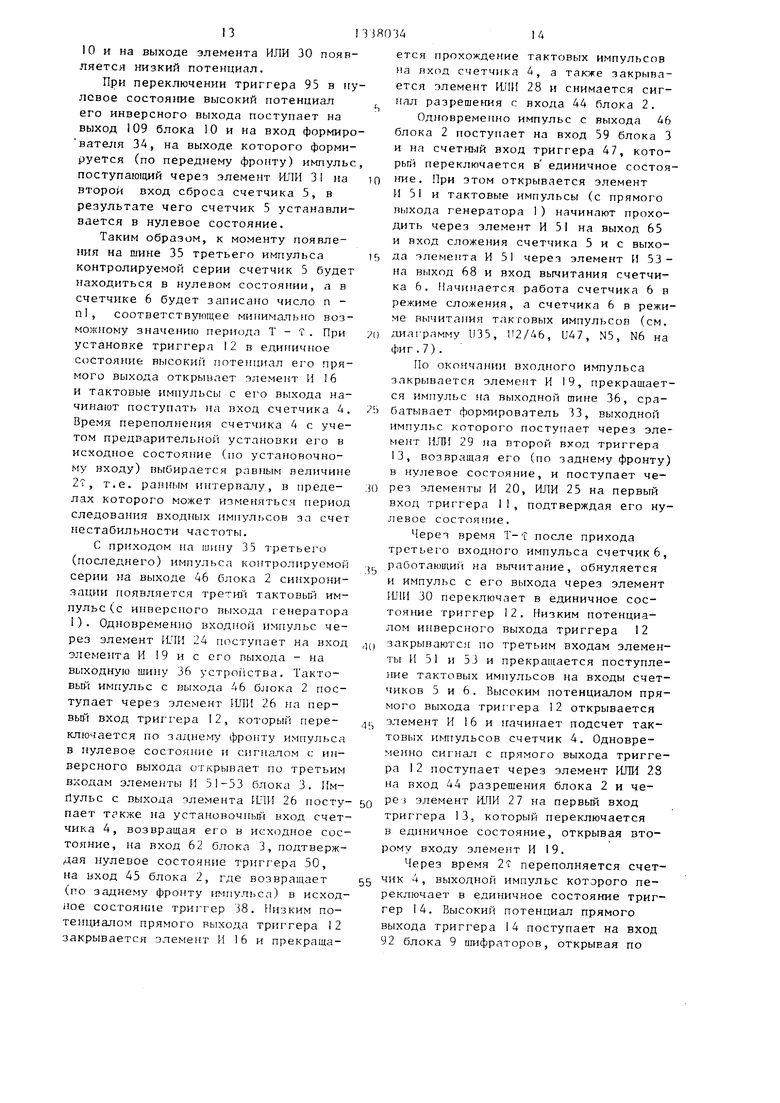

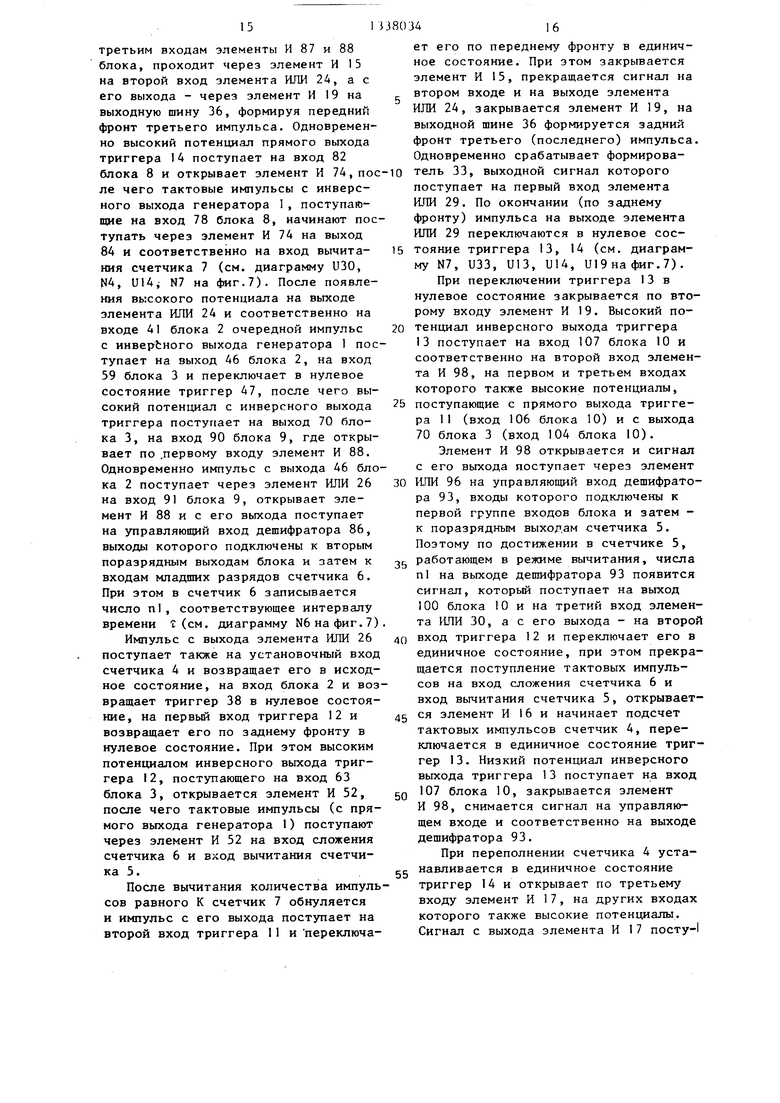

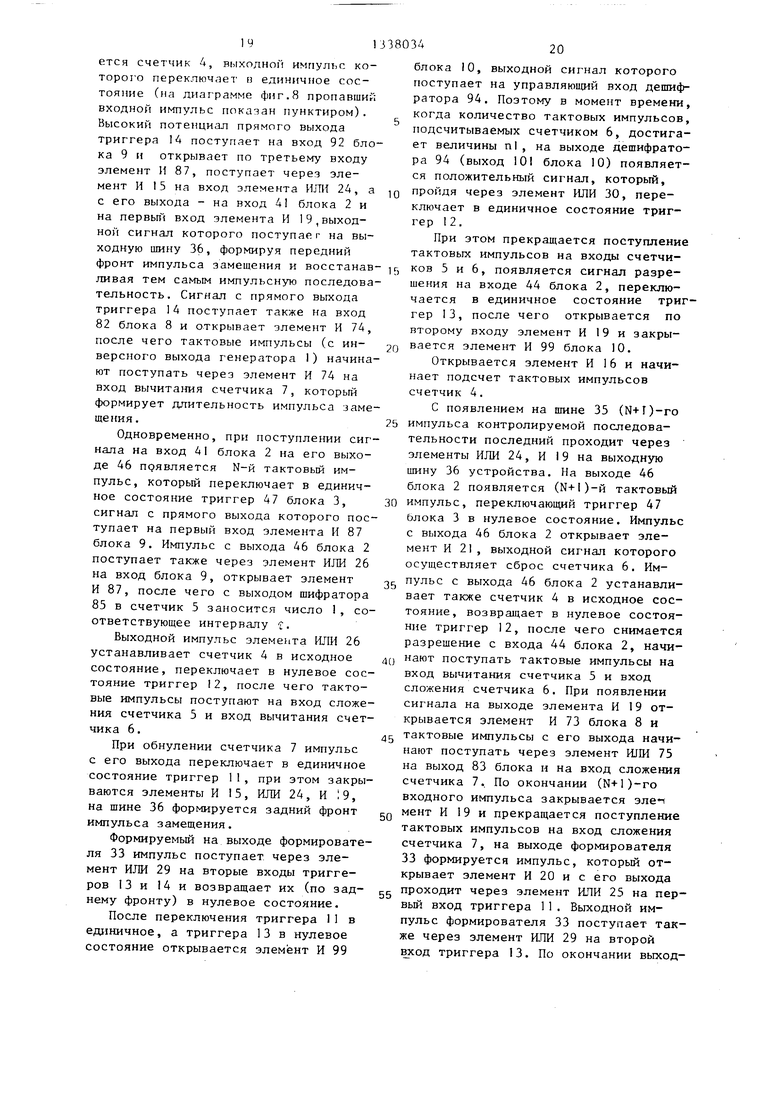

На фиг.1 представлена функционалг ная схема устройства для контроля импульсных последопательпостей; на фи .2-6 - функнлоняльные схем|,1 блока синхронизации, блока управления, блока коммутации, блока шифраторов и блока дешифраторов соответственно; на фиг, 7,8 - диаграммы, гюясняккцис работу устройства.

Устройство содержит г енератор 1 тактовых импульсов, блок 2 синхронизации, блок 3 управления, счетчик -А импул.ьсов, три реверсивных счетчика 5-7 импульсов, блок 8 коммутации, блок 9 шифраторов, блок 10 дешифраторов, четыре триггера 11-14, восемь элементов 11 13-22, формирователь 23 импульсов сброса, девять элементов ИЛИ , формирователь 33 заднего фронта импульса, (1)ормиро- ватель ЗА переднего фронта импульса, входную шину 35, выходную miniy 36, шину 37 сброса.

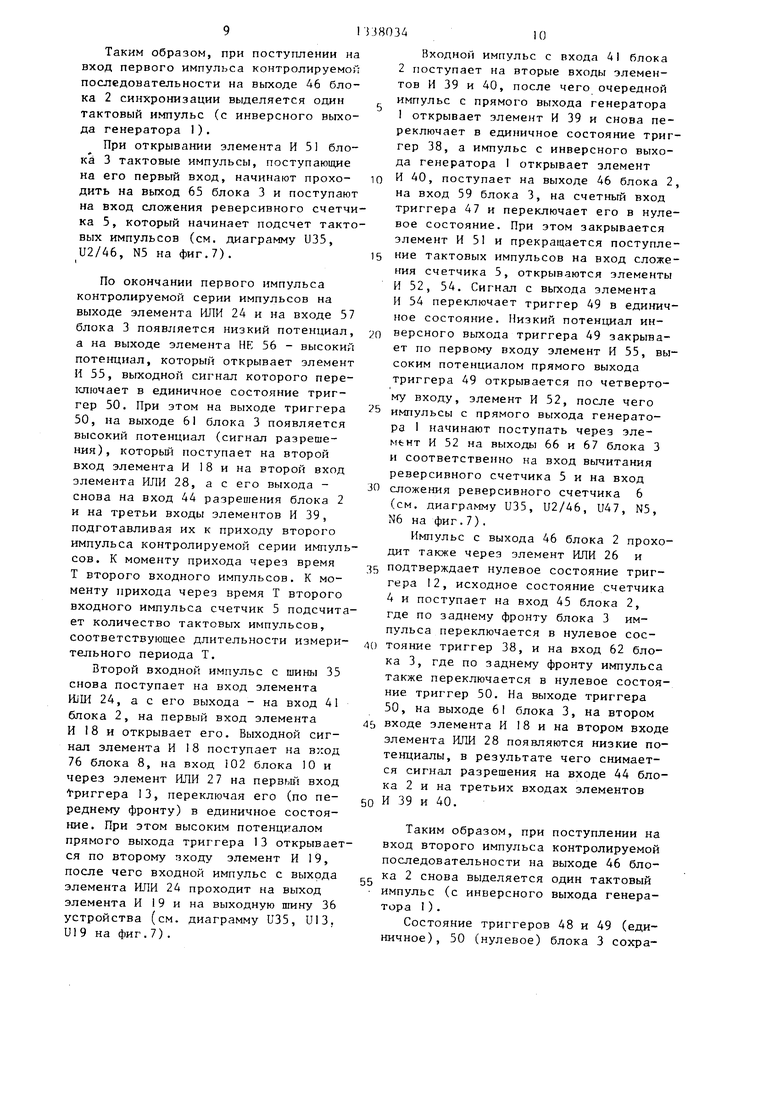

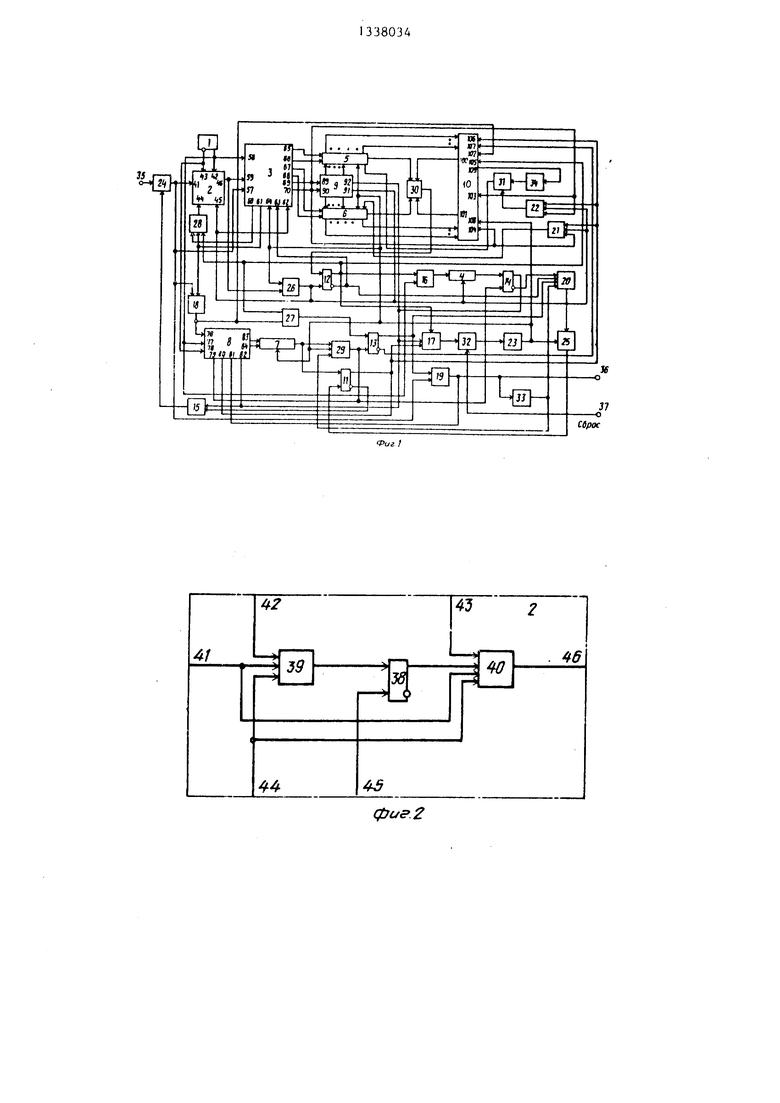

Блок 2 синхронизации содержит триггер 38, элемен1ы И 39 и 40, входы 41-45, выход 46.

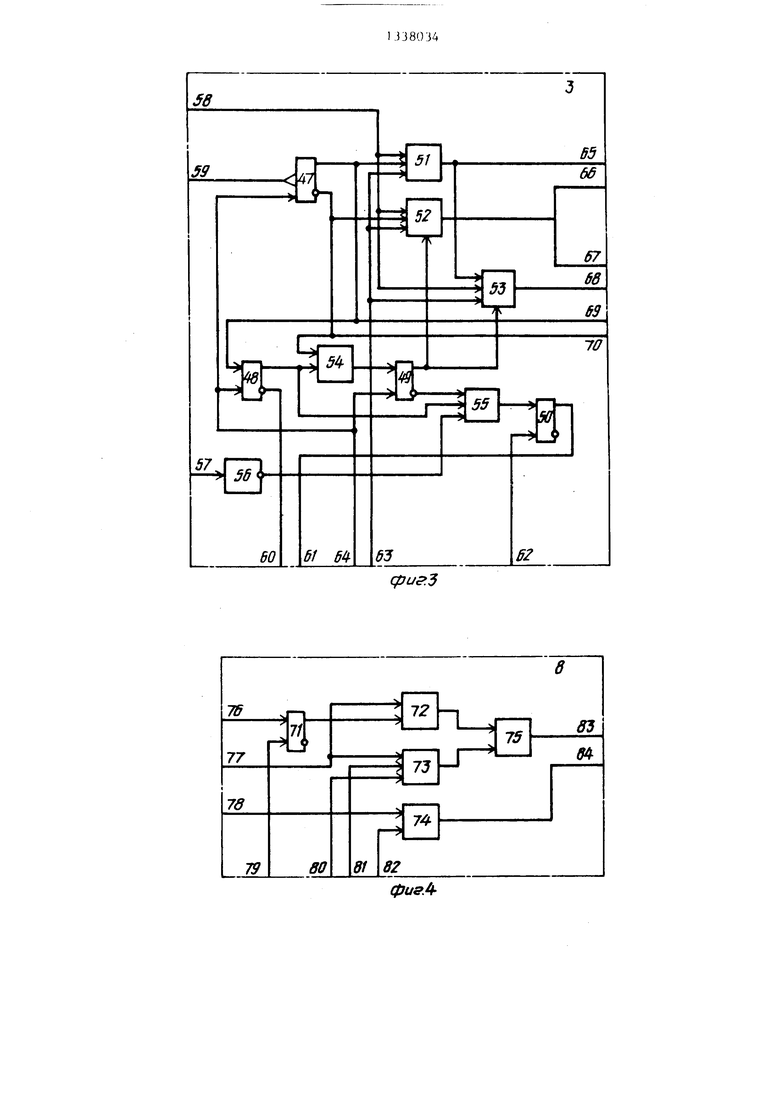

Блок 3 управле {ия содержит четыре триггера 47-50, пять элементов И 51- 55, элемент НЕ 56, входы 57-59, вь:хо ды 60 и 61, входы т2-64, выходы 65-70.

Блок 8 кoм ryтaцпи содержит триг-- гер 71, три элемента И 72-7, элемент ИЛИ 75, nx(. 76-82, выходы 83 и 84.

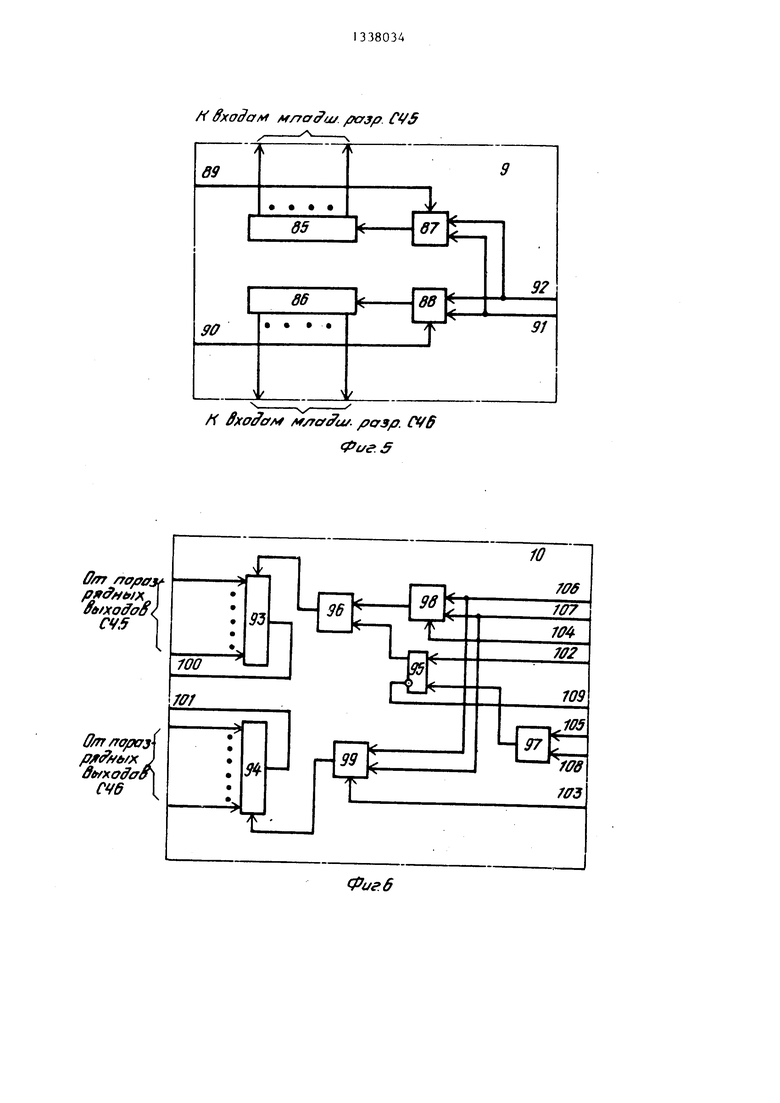

Блок 9 шифраторов содержит шифраторы 85 и 86, элементы И 87 и 88, входы 89-92.

Блок 10 дешифраторов содержит дешифраторы 93 и 94, триггер 95, элементы ИЛИ 96 и 97, элементы И 98 и 99,выходы 100 и 101, входы 102-108, выход 109.

Входная шина 3S подключена к первому входу первого элемента ИЛИ 24, второй вход которого соединен с выходом первого элемента И 15, первьи вход которого подключен к иннерсрюму

НП-)42

выходу первого триггера II. Первьш вход триггера I1 соединен через второй элемент ИЛИ 25 с выходом формирователя импульсов 23 и с первым входом третьего элемента Ш1И 26, выход которого соединен с установочным входом счетчика импульсов 4 и с первым входом второго триггера 12, прямой 10 выход которого соединен с первыми

входами второго элемента И I6 и третьего элемента И 17. Выход элемента И.Ш1 24 подключеп к первому входу 41 блока 2 сир{хронизации, к первому вхо- 1 г, ду 57 блока 3 управления, к первому входу четвертого элемента И 18 и к первому входу пятого элемента И 19, второй вход которого соединен с прямым выходом третьего триггера 13. 5г11ход элемента И 18 соединен с пер- входом четвертого элемента ИЛИ 27, с первым входом 102 блока 10 дешифратора и с первым входом 76 блока 8 коммутации, второй вход 77 которо- ; (, го соединен с прямым выходом генератора 1, с вторым входом 42 блока 2, с вторым входс)М 58 Г)л ка 3 и с вторым входом элемента И 16. Выход элемента И 16 подключен к входу счетчи- 30 ка 4, выход которого подключен к первому входу четвертого триггера 14, инверснып выход которого соединен с первым входом uiecToro элемента И 20, выход которого соединен со вторым .;, входом элемента ИЛИ 25. Инверсный В1.1ХОД генератора 1 тактовых импульсов соединен с третьим входом 78 блока 8 и с третьим вхолдом 43 блока 2, четверть) вход 44 которого соединен ,ц) t HbixojioM ятого элеме та ИЛИ 28, пер- вход которо о подключен к первому в |ходу 60 блока 3, второй выход 61 Koi oporo одключеп к вторым входам :1леме1 ов ИЛИ 28 и И 18. Третий и чет- ,jr верть Bb xo;ui 65 и 66 блока 3 управ- одкл очены соответственно к входам CJ oжeния и вычитания первого реверсив ого счетчика 5. Пятый и шес- то 67 и 68 блока 3 подключе- № соответствеи о к входам сложения и в,читания второго реверсивного счет- 6, а седьмо и восьмой выходы 69,70 - соответстве 1 О к первому и BTopoN y BxoziaM 89,90 блока шифраторов ,;(j 9, к первым BXiv taM восьмого и седьмого элеме 1тов И 22 и 21 и к второму 103 и третьеьгу 104 входам блока дешифраторов 10. Вь1ход 46 блока 2 син- хро 1изации одк.г юче1- к третьему входу 59 блока 3 и к второму входу элемента ИЛИ 26, выход которого подключен к третьему входу 91 блока 9, ко вторым входам элементов И 21,22, к пятому входу А5 блока 2 и к четвертому входу 62 блока 3, пятый вход 63 которого соединен со вторым входом элемента И 20 и с инверсным выходом триггера 12. Прямой выход триггера 12 соединен с четвертым 105 входом блока дешифраторов 10, с третьим .входом элемента ИЛИ 28 и с вторым входом элемента ИЛИ 27, выход которого соединен с первым входом триггера 13, второй вход которого соединен с выходом шестого элемента ИЛИ 29, с вторым входом триггера 14 и с четвертым входом 79 блока 8 коммутации, пятый вход 80 которого подключен к прямому выхо- ду триггера II, к второму входу элемента И 17, к третьим входам элементов И 21 и 22 и к пятому входу 106 блока дешифраторов 10, шестой вход 107 которого подключен к инверсному выходу триггера 13. Прямой выход триггера 13 соединен с третьим входом элемента И 20, четвертый вход которого подключен к выходу формирователя 33 импульсов и к первому входу эле- мента ИЛИ 29, второй вход которого соединен с вторым входом триггера 11 и с выходом третьего реверсивного счетчика 7, входы сложения и вычитания которого подключены соответственно к первому 83 и второму 84 выходам блока 8 коммутации. Шестой вход 81 блока 8 соединен с выходом элемента И 19, с входом формирователя 33 и с выходной шиной 36 устройства, а седь- мой вход 82 - с прямым выходом триггера 14, с вторым входом элемента И 15, с третьим входом элемента И 17 и с четвертым входом 92 блока 9, первые поразрядные выходы которого под- соединены к входам младших разрядов реверсивного счетчика 5. Поразрядные выходы счетчика 5 соединены соответственно с первой группой входов блока дешифраторов 10. Вторые поразряд- ные выходы блока 9 подсоединены к входам младших разрядов реверсивного счетчика 6, поразрядные выходы которого соединены соответственно с второй группой входов блока 10. Выходы счетчиков 5 и 6 подключены соответственно к первому и второму входам седьмого элемента ИЛИ 30, третий и четвертый входы которого подключены

5 0 5 о о 5 Q g

5

соответственно к первому и второму выходам 100 и 101 блока 10. Выход элемента ИЛИ 30 соединен с вторым входом триггера 12. Выход формирователя 23 соединен с первыми входами сброса счетчиков 5 и 6, с шестым входом 64 блока 3, с входом сброса счетчика 7, с третьим входом элемента ИЛИ 29 и с седьмым входом 108 дешифраторов 10. Третий выход 109 блока 10 соединен с входом формирователя 34 импульсов, выход которого подключен к первому входу восьмого элемента ИЛИ 31, второй вход которого соединен с выходом элемента И 22, а выход подключен к второму входу сброса счетчика 5. Выход элемента И 21 подключен к второму входу сброса счетчика 6. Вход формирователя 23 соединен с выходом девятого элемента ИЛИ 32, один вход которого подключен к выходу элемента И 17, а другой вход - к шине 37 сброса устройства.

В блоке 2 синхронизации первые входы элементов И 39 и 40 соединены с входами 42 и 43 блока соответственно. Вторые входы элементов И 39 и 40 объединены и подключены к входу 41, третьи входы объединены и под- ключены к входу 44 блока. Выход элемента И 40 подключен к выходу 46 блока, а четвертый вход - к выходу триггера 38, первый вход которого соединен с выходом элемента И 39, а второй вход - с входом 45 блока.

В блоке 3 управления вход 58 соединен с первыми входами элементов И 51-53. Вход 59 подключен к счетному входу триггера 47, прямой выход которого соединен с вторым входом элемента И 51, с первым входом триггера 48 и с выходом 69 блока. Инверсный выход триггера 47 соединен с вторым входом элемента И 52, с первым входом элемента И 54 и с выходом 70 блока. Второй вход элемента И 53 соединен с выходом элемента И 51 и с выходом 65 блока. Выход элемента И 52 соединен с выходами 66 и 67 блока, выход элемента И 53 соединен с выходом 68 блока. Третьи входы элементов И 51-53 объединены и подключены к входу 63 блока. Четвертые входы элементов И 52 и 53 объединены и подключены к прямому выходу триггера 49, инверсный выход которого соединен с первым входом элемента И 55. Вторые входы элементов И 54 и 55 объединены

и подключе; ы к прямому выходу тригтс ра 48, инверсный выход которого сое- динен с выходом 60 блока. Третий вход элемента И 55 подключен через элемен НЕ 56 к входу 57 блока, а выход - к первому входу триггера 50, второй вход которого соединен с входом 62 блока, а выход - с выходом 61 блока. Вторые входы триггеров 47- t9 объединены и подключены к входу 64 блока. Выход элемента И 53 соединен с выходом 68 блока.

В блоке 8 коммутации вход 76 блока соединен с первым входом триггера 71 , вход 77 блока соединен с первыми входами элементов И 72 и 73. Вход 78 соединен с первым входом элемента И 74. Вход 79 соединен с вторым нхо- дом триггера 71, выход которого подключен к второму входу элеметгта И 72 выход которог о соединен с первым входом элемента ИЛИ 75. Второй и третий входы элемента И 73 соединены соот- ветстве}ию с входами 80 и 81 блока, а выход элемента И 73 соединен с вторым входом элемента ИЛИ 75, ылход которого coexyiiien с пыходом 83 Г)лока. Второй вход и ныход элемента И 74 подключены соответственно к входу 82 и выходу 84 блока.

В блоке 9 111И|1)раторов входы 89 и 90 блока соединены соответстве1гно с первыми входами элементов И 87 и 88, вторые входы которых объединены и подключены к входу 91 блока, третьи входы также объединены и подключены к входу 92 блока. Выход элемента И 87 соединен с управляюиц1м входом шифратора 85, выходы которого соединены соответственно с первыми поразрядными выходами блока, подключаемыми к младшим разрядам счетчика импульсов 5. Выход элемента И 88 соединен с управляющим входом шифратора 86, выходы которого соединены соотнетствен- но с вторыми поразрядными выходами блока, подключаемыми к младшим разрядам счетчика импульсов 6.

В блоке 0 дешифраторов вход 106 соединен с первыми входами элементов И 98 и 99, вторые входы которых объе ди)1ены и подключепы к входу 107 блока. Третьи входы элементов И 98 и 99 соединены с входами 104 и 103 блока соответственно. Выход элемента И 98 соедиг ен с первым входом эпемента ЯТИ 96, второй вход которого подклю

0

346

чен к прямому выходу триггера 95, парный вход которого соединен с входом 102 блока, а второй вход - с выходом элемента ИЛИ 97. Один вход элемента 97 соединен с входом 105 блока, другой вход - с входом 108 блока. Инверсный выход триггера 95 подключен к выходу 109 блока. Выход элемента ЯЧИ 96 подключен к управляющему входу дешифратора 93, выход которого подключен к выходу 100 блока, а входы - к первой группе входов блока, подключаемых к поразрядным В1)1ходам счетчика 5. Выход элемента И 99 подключен к управляющему входу дешифратора 94, выход которого подключен к выходу 101 блока, а входы - к второй группе входов блока, подключаемых к поразрядным выходам счетчика 6.

YcTpoiicTBo работает следующим образом.

В исходном состоянии на шину 37 сброса устройства подается импульс сброса , которьпТ постугтает на второй вход элемеь1та ИЛИ 32 , ас его выхода - на вход формирователя 23 импульсов. При этом на выходе формирователя 23 импульсов формируется импульс сброса, который поступает на первые входы сброса реверсивных счетчиков 5 и 6 и устанавливает их в нулевое состояние, на вход сброса реверсивного счетчика 7, устанавливая его в нулевое состояние, на вход элемента Я1И 29, а с его выхода - на вторые входы триггеров 13 и 14, устанавливая их в нулевое состояние, на вход 79 блока 8 и соответственно на вто рой вход триггера 71, который уста- Р1авлигк1ется в нулевое состояние. Кроме того, импульс сброса с выхода формирователя 23 поступает на вход 108 блока 10 и соответственно на вход элемента ИЛИ 97 этого блока, а с его выхода - на второй вход триггера 95, устанавливая его в нулевое состояние, импульс сброса также поступает на перньш вход элемента -ШИ 26, на вход 64 блока 3 и соответственно на вторые входы триггеров 47-49, устанавливая их в нулевое состояние. С выхода элемента ИЛИ 26 импульс сброса поступает на первьп вход триггера 12, устанавливая его в нулевое состояние, на установочный вход счетчика 4, устанавливая его в исходное состояние, на вход 45 блока 2 и соответственно

7П

на второй вход триггера 38, устанавливая его в нулевое состояние, а также на вход 62 блока 3 и соответственно на второй вход триггера 50, устанавливая его в нулевое состояние Импульс сброса с выхода формирователя 23 поступает также через элемент ИЛИ 25 на первый вход триггера 1I, устанавливая его в нулевое состояние

При этом ушзким потенциалом прямого выхода триггера 11 будут закрыты по второму входу элемент И 17, по третьим входам элементы И 21 и 22, по первым входам элементы И 98 и 99 блока 10,по второму входу элемента И 73 блока 8. Элемент И 73 закрыт также по третьему входу низким потенциалом выхода элемента И 19. Низким потенциалом прямого выхода триггера 12 закрыты по первому входу элементы И 16,17, ИЛИ 27, по третьему входу элемент ИЛИ 28, а по первому входу элемент ИЛИ 97 блока iU. Низким потенциалом прямого выхода триггера 13 закрыты по второму входу элемент И 19, по третьему входу элемент И 20. Низким потенциалом прямого выхода триггера 14 закрыты по вторым входам элементы И 17 и 15 и элемент И 74 блока 8, по первым входам элементы И 87 и 88 блока 9, на вторых входах которых низкий потенциал с выхода элемента ИЛИ 26, который также закрывает по вторым входам элементы И 21 и 22. Элементы И 39 и 40 блока 2 закрыты по вторым входам низким потенциалом выхода элемента ИЛИ 24.

Элемент И 40 закрыт также по четвертому входу низким потенциалом прямого выхода триггера 38.

В блоке 3 элемент И 51 закрыт по второму входу низким потенциалом прямого выхода триггера 47, элемент И 53 закрыт по второму входу низким выходным потенциалом элемента И 51 и по четвертому входу низким потенциалом прямого выхода триггера 49. Низким выходным потенциалом прямого выхода триггера 48 закрыты по вторым входам элементы И 54 и 55. Элемент И 52 закрыт по четвертому входу низким потенциалом прямого выхода триггера 49. По третьим входам элементы И 51-53 открыты высоким потенциалом с входа 63, подключенного к инверсному выходу триггера 12.

48

Рассмотрим работу устройства для случая поступле)шя на входную шину 35 серии и тульсов, состоящей, например, из трех импульсов, следующих с периодом Т. Высокий потенциал (сигнал разрешения) с инверсного выхода триггера 48 блока 3 поступает в исходном состоянии на выход 60 блока

и на первьш вход элемента ИЛИ 28, а с его выхода - на вход 44 блока синхронизации 2 и на третьи входы элементов И 39 и 40 блока 2, подготавливая их к приходу первого импульса

контролируемой последовательности. Первый входной положительный импульс с шины 35 поступает на вход элемента ИЛИ 24, ас его выхода - на вход 41 блока 2 синхронизации и соответствен-

но на вторые входы элементов И 39 и 40, после чего очередной тактовьт импульс с прямого выхода генератора 1 открывает элемент И 39 и переключает (по переднему фронту импульса) в единичное состояние триггер 38. Высокий потенциал выхода триггера 38 поступает на четвертый вход элемента И 40, после чего тактовый импульс с инверсного выхода генератора 1 открывает

элемент И 40 и с его выхода поступает на вход 59 и на счетный вход триггера 47 блока 3 управления и переключает триггера (по переднему фронту импульса) в единичное состояние. Импульс с выхода элемента И 40 поступает также через элемент ИЛИ 26 на первый вход триггера 12, на установочный вход счетчика 4, подтверждая их исходные состояния, на вход 45 блока

2 и соответственно на второй вход триггера 38, который переключается в нулевое состояние по окончании (по заднему фронту) импульса и закрьгаает элемент И 40, а также на вход 62 блока 3 и соответственно на второй вход триггера 50, подтверждая его нулевое состояние. При переключении в единичное состояние триггера 47 высоким потенциалом его прямого выхода открывается элемент И 51 и переключается в единичное состояние триггер 48, при этом на его прямом выходе появляется высокий потенциал, открывающий по вторым входам элементы И 54 и 55, а

на инверсном выходе - низкий потенциал, который закрывает элемент ИЛИ 28,в результате чего снимае ссясигнал разрешения с входа 44 блока 2, закрьша-| ются по третьим входам элементы И 39 и 40.

Таким образом, при поступлении на вход первого импульса контролируемой последовательности на выходе 46 блока 2 синхронизации выделяется один тактовый импульс (с инверсного выхода генератора 1).

При открывании элемента И 51 блоки 3 тактовые импульсы, поступаюицче на его первый вход, начинают проходить на выход 65 блока 3 и поступают на вход сложения реверсивного счетчика 5, который начинает подсчет тактовых импульсов (см. диаграмму U35, U2/46, N5 на фиг,7).

По окончании первого импульса контролируемой серии импульсов на выходе элемента ИЛИ 24 и на входе 37 блока 3 появляется низкий потенциал, а на выходе элемента НЕ 56 - высокий потенциал, который открывает элемент И 55, выходной сигнал которого переключает в единичное состояние триггер 50. При этом на выходе триггера 50, на выходе 61 блока 3 появляется высокий потенциал (сигнал разрешения), которьй поступает на второй вход элемента И 18 и на второй вход элемента ИЛИ 28, ас его выхода - снова на вход 44 разрешения блока 2 и на третьи входы элементов И 39, подготавливая их к приходу второго импульса контролируемой серии импульсов. К моменту прихода через время Т второго входного импульсов. К моменту прихода через время Т второго входного импульса счетчик 5 подсчитает количество тактовых импульсов, соответствующее длительности измерительного периода Т.

Второй входной импульс с шины 35 снова поступает на вход элемента ШШ 24, а с его выхода - на вход 41 блока 2, на первый вход элемента И 18 и открывает его. Выходной сигнал элемента И I8 поступает на вход 76 блока 8, на вход 102 блока 10 и через элемент ИЛИ 27 на первьш вход триггера 13, переключая его (по переднему фронту) в единичное состояние. При этом высоким потенциалом прямого выхода триггера 13 открывается по второму 13ХОДУ элемент И 19, после чего входной импульс с выхода элемента ИЛИ 24 проходит на выход элемента И 19 и на выходную шику 36 устройства (см. диаграмму U35, U13. U19 на фиг.7).

Входной импульс с входа 41 блока 2 поступает на вторые входы элементов И 39 и 40, после чего очередной импульс с прямого выхода генератора 1 открывает элемент И 39 и снова переключает в единичное состояние три1- гер 38, а импульс с инверсного выхода генератора I открывает элемент

И 40, поступает на выходе 46 блока 2, на вход 59 блока 3, на счетный вход триггера 47 и переключает его в нулевое состояние. При этом закрывается элемент И 51 и прекращается поступление тактовых импульсов на вход сложения счетчика 5, открываются элементы И 52, 54. Сигнал с выхода элемента И 54 переключает триггер 49 в единичное состояние. Низкий потенциал инверсного выхода триггера 49 закрывает по первому входу элемент И 55, высоким потенциалом прямого выхода триггера 49 открывается по четвертому входу, элемент И 52, после чего импульсы с прямого выхода генератора 1 начинают поступать через элемент И 52 на выходы 66 и 67 блока 3 и соответственно на вход вычитания реверсивного счетчика 5 и на вход

сложения реверсивного счетчика 6 (см. диаграмму U35, U2/46, U47, N5, N6 на фиг.7).

Импульс с выхода 46 блока 2 проходит также через элемент ИЛИ 26 и

подтверждает нулевое состояние триггера 12, исходное состояние счетчика 4 и поступает на вход 45 блока 2, где по заднему фронту блока 3 импульса переключается в нулевое состояние триггер 38, и на вход 62 блока 3, где по заднему фронту импульса также переключается в нулевое состояние триггер 50. На выходе триггера 50, на выходе 61 блока 3, на втором

входе элемента И 18 и на втором входе элемента ИЛИ 28 появляются низкие потенциалы, в результате чего снимается сигнал разрешения на входе 44 блока 2 и на третьих входах элементов

И 39 и 40.

5

Таким образом, при вход второго импульса последовательности на ка 2 снова выделяется импульс (с инверсного тора 1).

Состояние триггеров ничное), 50 (нулевое)

поступлении на контролируемой выходе 46 бло- один тактовый выхода генера48 и 49 (еди- блока 3 сохраняется до окончания прохождения контролируемой серии.

При поступлении импульса с выхода элемента И 18 на вход 76 блока 8 переключается в единичное состояние триггер 71, высокий выходной потенциал которого открывает элемент И 72 после чего тактовые импульсы с прямого выхода генератора 1, поступающие на вход 77 блока 8, начинают проходить через элементы И 72, ИЛИ 75 на выход 83 и на вход сложения реверсивного счетчика. 7. Счетчик 7 начинает подсчет импульсов. К моменту окончания второго импульса контролируемой серии сЧетчик 7 подсчитает количество тактовых импульсов, равное К, соответствующее длительности входного импульса.

По Окончании второго входного импульса закрывается элемент И 19 и прекрап1ается импульс на его выходе и на выходной шине 36 устройства. При этом на выходе формирователя 33 формируется импульс, который поступает на вход элемента ИЛИ 29, а с его выхода - на вход 79 блока 8 и на второй вход триггера 71, переключая его (по переднему фронту) в нулевое состояние, после чего закрывается элемент И 72 и прекращается поступление тактовых импульсов на вход сложения счетчика 7 (см. диаграмму U35, U13, N7, иЗЗ, U19 на фиг.7). Кроме того, выходной импульс элемента ИЛИ 29 поступает на второй вход триггера 14 и подтверждает нулевое состояни е триггера и на второй вход триггера

13, который по заднему фронту импуль- 40 28 и с его выхода сигнал разрешения .са переключается в нулевое состояние. Импульс с выхода формирователя 33 открывает также элемент И 20 и с его

проходит на вход 44 блока 2 и третьи входы элементов И 39 и 40, подготавливая их к приходу третьего входного импульса. Высокий потенциал прямого выхода триггера 12 поступает также через элемент ИЛИ 27 на первый вход триггера 13 и переключает его в единичное состояние (см диаграмму N5, N6, U13 на фиг.7). При переключении триггера 13 в единичное состояние открывается по второму входу выходной элемент И 19, высокий потенциал прямого выхода триггера 12 поступает также на вход 105 блока 10, на вход gg элемента ИЛИ 97, ас его выхода - на второй вход триггера 95 и переключает его в нулевое состояние. При этом на управляющем входе дешифратора 93 и на его выходе, на выходе 100 блока

выхода поступает через элемент ИЛИ 25 на первый вход триггера 11, подтверждая его нулевое состояние.

Таким образом, с появлением на входной шине 35 второго импульса контролируемой последовательности последний проходит на выходе устройства, счетчик 7 начинает подсчет тактовых импульсов (в течение длительности входного импульса), счетчик 6 начинает работать в режиме сложения, а счетчик 5 переключается на режим вычитания тактовых импульсов.

Как отмечено выше, с приходом второго импульса контролируемой последовательности импульс с выхбда элемен

5

0

5

0

5

та И 18 поступает на вход блока lOT дешифраторов 10. С входа 102 импульс поступает на первый вход триггера 95, переключая его в единичное состояние.

При этом высокий потенциал прямого выхода триггера поступает через элемент ИЛИ 96 на управляющий вход дешифратора 93, входы которого подключены к первой группе входов блока и затем к поразрядным выходам счетчика 5. Поэтому в момент времени, когда количество тактовых импульсов, подсчитываемых счетчиком 5, достигается величины п1, на выходе дешифратора 93 появится положительный сигнал, который поступает с выхода 100 блока 10 на третий вход элемента ИЛИ 30, а с его выхода - на второй вход триггера 12, переключая его (по переднему фронту) в единичное состояние (см. диаграмму U30, U12 на фиг.7). Число п1 соответствует интервалу времени С , на величину которого может изменяться (в одну или другую сторону от номинального значения) период следования контролируемых импульсов за счет нестабильности частоты.

При переключении триггера 12 в единичное состояние низкий потенциал инверсного выхода триггера поступает на вход 63 блока 3, при этом закрывается элемент И 52 и прекращается поступление тактовых импульсов с выходов 66 и 67 блока на входы вычитания и сложения реверсивных счетчиков 5 и 6 соответственно. Высокий потенциал прямого выхода триггера 12 поступает на третий вход элемента ИЛИ

28 и с его выхода сигнал разрешения

проходит на вход 44 блока 2 и третьи входы элементов И 39 и 40, подготавливая их к приходу третьего входного импульса. Высокий потенциал прямого выхода триггера 12 поступает также через элемент ИЛИ 27 на первый вход триггера 13 и переключает его в единичное состояние (см диаграмму N5, N6, U13 на фиг.7). При переключении триггера 13 в единичное состояние открывается по второму входу выходной элемент И 19, высокий потенциал прямого выхода триггера 12 поступает также на вход 105 блока 10, на вход элемента ИЛИ 97, ас его выхода - на второй вход триггера 95 и переключает его в нулевое состояние. При этом на управляющем входе дешифратора 93 и на его выходе, на выходе 100 блока

13

IО и на выходе элемента ИЛИ 30 появляется низкий потенциал.

При переключении триггера 95 в нулевое состояние высокий потенциал его инверсного выхода поступает на выход 109 блока 10 и на вход формиро вателя 34, на выходе которого формируется (по переднему фронту) импульс поступа 01ций через элемент ИЛИ 31 на второй вход сброса счетчика 5, в результате чего счетчик 5 устанавливается в нулевое состояние.

Таким образом, к моменту появления на шине 35 третьего импульса контролируемой серии счетчик 5 будет находиться в нулевом состоянии, а в счетчике 6 будет записано число п - п1, соответствующее минимально возможному значению периода Т - Т . При установке триггера 12 в еди1гичное состояние высокий потенциал его прямого выхода открывает элемент И 16 и тактовые импульсы с его выхода начинают поступать Ж1 вход счетчика 4 Время переполнения счетчика 4 с учетом предварительной установки его в исходное состояние (по установочному входу) выбирается равным величине 2т, т.е. ранным интервалу, в преде- лах которого может изменяться период следования входных импул сов за счет нестабильности частоты.

С приходом на шипу 35 третьего (последнего) импульса контролируемой серии на выходе 46 блока 2 синхронизации появляется третшЧ тактовый импульс (с ипверспого выхода генератора 1). Одновременно входной импульс через элемент {ПИ 24 поступает на вход И 19 и с его выхода - на выход1гую шину 36 устройства. Тактовый импульс с выхода 46 блока 2 поступает через элемент ИЛИ 26 на первый вход триггера 12, который пере- ключается по зацне -гу фронту импульса в нулевое состояние и сигналом с инверсного выхода открывает по третьим входам элементы 1 51-53 блока 3. Им- йульс с выхода элемента РШИ 26 посту пает также на установочный вход счетчика 4, возвращая его в исходное состояние, на вход 62 блока 3, подтверждая нулевое состояние триггера 50, на вход 45 блока 2, где возвращает (по заднему фронту импульса) в исходное состояние триггер 38. Низким потенциалом прямого выхода триггера 12 закрывается элемент И 16 и прекраща

5 i) Ь о

() ,: 0 5

5

14

ется прохождение тактовых импульсов на вход счетчика 4, а также закрывается элемент ИИИ 28 и снимается си1- нал разрешения с входа 44 блока 2.

Одновреме1П1о импульс с выхода 46 блока 2 поступает на вход 59 блока 3 и на счетный вход триггера 47, кото- рьй переключается в единичное состоящее. При этом открывается элемент И 51 и тактовые импульсы (с прямого выхода генератора 1) начинают проходить через элемент И 51 на выход 65 и вход сложения счетчика 5 и с выхода элемента И 51 через элемент И 53- на выход 68 и вход вычитания счетчика 6. Начинается работа счетчика 6 в режиме сложения, а счетчика 6 в режиме вычитания тактовых импульсов (см. диаграмму U35, U2/46, U47, N5, N6 на фиг.7).

По окончании Bxontioro импульса закрывается элемент И 19, прекращается импульс на выходной шине 36, срабатывает формирователь 33, выходной импульс которого поступает через элемент ИЛИ 29 на второй вход триггера 13, возвращая его (по заднему фронту) в нулевое состояние, и поступает через элементы И 20, ИЛИ 25 на первый вход триггера 11, подтверждая его нулевое состояние.

Через время Т- С после прихода третьего входного импульса счетчик 6, работающий на вычитание, обнуляется и импульс с его выхода через элемент ИЛИ 30 переключает в единичное состояние триггер 12. Низким потенциалом инверсного выхода триггера 12 закрываются по третьим входам элементы И 51 и 53 и прекращается поступле- HPte тактовых импульсов на входы счетчиков 5 и 6. Высоким потенциалом прямого выхода триггера 12 открывается элемент И 16 и начинает подсчет тактовых импульсов счетчик 4. Одновременно сигнал с прямого выхода триггера I2 поступает через элемент ИЛИ 28 на вход 44 разрешения блока 2 и через элемент ИЛИ 27 на первый вход триггера 13, который переключается в единичное состояние, открывая второму входу элемент И 19.

Через время 2 переполняется счетчик 4, выходной импульс которого переключает в еди 1ичное состояние триггер 14. Высокий потенциал прямого выхода триггера 14 поступает на вход 92 блока 9 шифраторов, открывая по

третьим входам элементы И 87 и 88 блока, проходит через элемент И 15 на второй вход элемента ИЛИ 24, а с его выхода - через элемент И 19 на выходную шину 36, формируя передний фронт третьего импульса. Одновременно высокий потенциал прямого выхода триггера 14 поступает на вход 82

блока 8 и открывает элемент И 74, пос-ю тель 33, выходной сигнал которого

ле чего тактовые импульсы с инверсного выхода генератора 1, поступающие на вход 78 блока 8, начинают поступать через элемент И 74 на выход 84 и соответственно на вход вычитания счетчика 7 (см. диаграмму U30, N4, U14j N7 на фиг.7). После появления высокого потенциала на выходе элемента ИЛИ 24 и соответственно на входе 41 блока 2 очередной импульс с инверЬного выхода генератора 1 поступает на выход 46 блока 2, на вход 59 блока 3 и переключает в нулевое состояние триггер 47, после чего высокий потенциал с инверсного выхода триггера поступает на выход 70 блока 3, на вход 90 блока 9, где открывает по .первому входу элемент И 88. Одновременно импульс с выхода 46 блока 2 поступает через элемент ИЛИ 26 на вход 91 блока 9, открывает элемент И 88 и с его выхода поступает на управляю1ций вход дешифратора 86, выходы которого подключены к вторым поразрядным выходам блока и затем к входам младших разрядов счетчика 6. При этом в счетчик 6 записывается число п1, соответствующее интервалу времени 1 (см. диаграмму N6 на фиг.7)

Импульс с выхода элемента ИЛИ 26 поступает также на установочный вход счетчика 4 и возвращает его в исходное состояние, на вход блока 2 и возвращает триггер 38 в нулевое состояние, на первый вход триггера 12 и возвращает его по заднему фронту в нулевое состояние. При этом высоким потенциалом инверсного выхода триггера 12, поступающего на вход 63 блока 3, открывается элемент И 52, после чего тактовые импульсы (с прямого выхода генератора 1) поступают через элемент И 52 на вход сложения счетчика 6 и вход вычитания счетчика 5.

После вычитания количества импульсов равного К счетчик 7 обнуляется и импульс с его выхода поступает на второй вход триггера 11 и переключает его по переднему фронту в единичное состояние. При этом закрывается элемент И 15, прекращается сигнал на втором входе и на выходе элемента ИЛИ 24, закрывается элемент И 19, на выходной шине 36 формируется задний фронт третьего (последнего) импульса. Одновременно срабатывает формирова

поступает на первый вход элемента ИЛИ 29. По окончании (по заднему фронту) импульса на выходе элемента ИЖ 29 переключаются в нулевое состояние триггера 13, 14 (см. диаграмму N7, иЗЗ, U13, U14, и19нафиг.7).

При переключении триггера 13 в нулевое состояние закрывается по второму входу элемент И 19. Высокий потенциал инверсного выхода триггера 13 поступает на вход 107 блока 10 и соответственно на второй вход элемента И 98, на первом и третьем входах которого также высокие потенциалы, поступающие с прямого выхода триггера 11 (вход 106 блока 10) и с выхода 70 блока 3 (вход 104 блока 10).

Элемент И 98 открывается и сигнал с его выхода поступает через элемент ИЛИ 96 на управляющий вход дешифратора 93, входы которого подключены к первой группе входов блока и затем - к поразрядным выходам счетчика 5. Поэтому по достижении в счетчике 5, работающем в режиме вычитания, числа п1 на выходе дешифратора 93 появится сигнал, который поступает на выход 100 блока 10 и на третий вход элемента ИЛИ 30, а с его выхода - на второй вход триггера 12 и переключает его в единичное состояние, при этом прекращается поступление тактовых импульсов на вход сложения счетчика 6 и вход вычитания счетчика 5, открывается элемент И 16 и начинает подсчет тактовых импульсов счетчик 4, переключается в единичное состояние триггер 13. Низкий потенциал инверсного выхода триггера 13 поступает на вход 107 блока 10, закрывается элемент И 98, снимается сигнал на управляющем входе и соответственно на выходе дешифратора 93.

При переполненрш счетчика 4 устанавливается в единичное состояние триггер 14 и открывает по третьему входу элемент И 17, на других входах которого также высокие потенциалы. Сигнал с выхода элемента И I7 посту-1

171

пает через элемент ИЛИ 32 на вход формирователя 23 импульсов сброса, на выходе которого формируется импульс сброса, устанавливающий все счетчики и триггеры устройства в исходное состояние, после чего устройство готово к приему и контролю следующей импульсной последовательности (см. диаграмму N5, N6, N4, U30, U12, U13, U14, U23 на фиг.7).

Таким образом, при поступлении на вход контролируемой серии, состояще из N импульсов, на выходной шине устройства формируется серия, состоящая также из N импульсов, равных по длительности входным, и сдвинутая относительно входной на один период следования импульсов. Устройство реагирует на импульсы контролируемой последовательности, выделяя на выходе 46 блока 2 синхронизации один такто- пый импульс (с инверсного выхода генератора 1) по каждому входному импульсу последовательности. Выделение тактового импульса на выходе 46 блока 2 осуществляется при условии наличия сигнала разрешения на входе 44 блока, который формируется каждый раз к моменту поступления входного импульса и снимается по окончании (по заднему фронту) тактового импульса с выхода 46 блока 2. Поэтому при появлении и fпyльcoв помех п интервалах между импульсами контролируемой последовательности устройство реагировать на их появление не будет.

В исходном состоянии перед поступлением на шину 35 первого импульса контролируемой последовательности сигнал разрешения поступает на вход 44 блока 2 с выхода 60 блока 3 и снимается после прохождения первого тактового импульса с выхода 46 блока 2, По окончании первог о входного импульса сигнал разрешения поступает с выхода 61 блока 3 и снимается после прохождения (по заднему фронту) второго тактового импульса на выходе 46 блока 2. В дальнейшем сигналы разрешения подаются с прямого выхода триггера 12, переключаемого в единичное состояние при обнулении счетчиков 5 или 6. Одновременно с формиро- сигнала разрешения переключается в единичное состояние триггер 13, подготавл1 вая элемент И 19 к пропусканию на выход входного импульса контролируемой последовательности

418

Снимается сигнал разрешения по окончании тактового импульса на выходе 46 блока 2, когда триггер 12 возвра-, щается в нулевое состояние. Поэтому на импульсы помех, появляющиеся на шине 35 в интервалах между контролируемыми импульсами (начиная со второго периода контролируемой последовательности), устройство реагировать не будет. Импульсы помех не будут проходить на выход устройства.

При пропадании импульса в контролируемой последовательности устройство восстанавливает на выходе потерянный импульс путем формирования импульса замены.

Рассмотрим работу устройства при пропадании, например, N-ro импульса

в контролируемой последовательности. Из диаграммы на фиг.8 видно, что с поступлением на шину 35 (N-l)-ro импульса последовательности на выходе 46 блока 2 появляется (К-1)-й тактовый импульс, переключаются в нулевое состояние триггер 47 блока 3, триггер 12, устанавливается в исходное состояние счетчик 4, начинают работать в режиме вычитания счетчик 5

и в режиме сложения счетчик 6. Входной (N-1)-и импульс контролируемой последовательности проходит на выход элемента И I9 и на шину 36 устройства. По окончании входного импульса

импульс с выхода формирователя 33 возвращает триггер 13 в нулевое состояние .

По истечении времени Т-Т (минимально возможное значение контролируемого периода) от момента прихода (N-1)- го входного импульса обнуляется счетчик 5, выходной импульс которого поступает через элемент ИЛИ 30 на второй вход триггера 12 и переключает его в единичное состояние. При этом подается сигнал разрешения на вход 44 блока 2, прекращается поступление тактовых импульсов на входы счетчиков 5 и 6, переключается в единичное состояние триггер 13, открывая по второму входу элемент И 19, открывается эле- мент И. 16 и тактовые импульсы с его выхода начинают поступать на вход счетчика 4. При отсутствии входного импульса по истечении времени, равного интервалу, в пределах которого может изменяться период следования контролируемых импульсов, переполня

ется счетчик 4, выходной импульс которого переключает в единичное состояние (на диаграмме фиг.8 пропавший входной импульс показан пунктиром). Высокий потенциал прямого выхода триггера 14 поступает на вход 92 бло ка 9 и открывает по третьему входу элемент И 87, поступает через элемент И 15 на вход элемента ИЛ 24, а с его выхода - на вход 41 блока 2 и на первьш вход элемента И 19,выходной сигнал которого поступает на выходную шину 36, формируя передний фронт импульса замещения и восстанав ливая тем самым импульсную последова тельность. Сигнал с прямого выхода триггера 14 поступает также на вход 82 блока 8 и открывает элемент И 74, после чего тактовые импульсы (с инверсного выхода генератора I) начина ют поступать через элемент И 74 на вход вычитания счетчика 7, который формирует длительность импульса заме щения.

Одновременно, при поступлении сиг нала на вход 41 блока 2 на его выходе 46 прявляется N-й тактовый импульс, который переключает в единичное состояние триггер 47 блока 3, сигнал с прямого выхода которого пос тупает на первый вход элемента И 87 блока 9. Импульс с выхода 46 блока 2 поступает также через элемент ИЖ 26 на вход блока 9, открывает элемент И 87, после чего с выходом шифратора 85 в счетчик 5 заносится число 1, со стветствующее интервалу 1.

Выходной импульс элемента ИЛИ 26 устанавливает счетчик 4 в исходное состояние, переключает в нулевое сое тояние триггер 12, после чего тактовые импульсы поступают на вход сложе ния счетчика 5 и вход вычитания счет чика 6.

При обнулении счетчика 7 импульс с его выхода переключает в единичное состояние триггер 11, при этом закры Баются элементы И 15, ИЛИ 24, И 19, на шине 36 формируется задний фронт импульса замещения.

Формируемый на выходе формировате ля 33 импульс поступает через элемент ИЛИ 29 на вторые входы триггеров 13 и 14 и возвращает их (по заднему фронту) в нулевое состояние.

После переключения триггера 11 в единичное, а триггера 13 в нулевое состояние открывается элемент И 99

блока 10, выходной сигнал которого поступает на управляющий вход дешифратора 94, Поэтому в момент времени, когда количество тактовых импульсов, подсчитываемых счетчиком 6, достигает величины п1, на выходе дешифратора 94 (выход 101 блока 10) появляется положительный сигнал, который,

д пройдя через элемент ИЛИ 30, переключает в единичное состояние триггер 1 2.

При этом прекращается поступление тактовых импульсов на входы счетчи- 1г, ков 5 и 6, появляется сигнал разрешения на входе 44 блока 2, переключается в единичное состояние триггер 13, после чего открывается по второму входу элемент И 19 и закры2Q вается элемент И 99 блока 10.

Открывается элемент И 16 и начинает подсчет тактовых импульсов счетчик 4.

С появлением на шине 35 (N+r)-ro

25 импульса контролируемой последовательности последний проходит через элементы ИЛИ 24, И 19 на выходную шину 36 устройства. На выходе 46 блока 2 появляется (М+1)-й тактовьй

30 импульс, переключающий триггер 47 блока 3 в нулевое состояние. Импульс с выхода 46 блока 2 открывает элемент И 21, выходной сигнал которого осуществляет сброс счетчика 6. пульс с выхода 46 блока 2 устанавливает также счетчик 4 в исходное состояние, возвращает в нулевое состояние триггер 12, после чего снимается разрешение с входа 44 блока 2, начидо нают поступать тактовые импульсы на вход вычитания счетчика 5 и вход сложения счетчика 6. При появлении сигнала на выходе элемента И 19 открывается элемент И 73 блока 8 и

g тактовые импульсы с его выхода начинают поступать через элемент ШШ 75 на выход 83 блока и на вход сложения счетчика 7. По окончании (N+l)-ro входного импульса закрывается эле

gg мент И 19 и прекращается поступление тактовых импульсов на вход сложения счетчика 7, на выходе формирователя 33 формируется импульс, который открывает элемент И 20 и с его выхода

проходит через элемент ИЛИ 25 на первый вход триггера 11. Выходной импульс формирователя 33 поступает также через элемент ИЛИ 29 на второй вход триггера 13. По окончании выход21

ного импульса формирователя 33 триггеры 11 и 13 снова переключаются в нулерое состояние и т.д.

Таким образом, при пропадании им- 1гульса в контролируемой последовательности (начиная с 3-го входного импульса) устройство восстанавливает на выходе потерянньй импульс путем формирования импульса замещения. Импульс на прямом выходе триггера 14 сигнализирует о пропадании импульса во входной последовательности.

Устройство позволяет осуществлять контроль импульсных последовательное тей при наличии неравномерности периода следования импульсов за счет нестабильности частоты. Это обеспечивается тем, что сигнал разрешения (на прямом выходе триггера 12) форми руется каждый раз через время Т - Т от момента поступления 9 предыдущего входного импульса и снимается с приходом очередного входного импульса или в момент времени Т +Т в случае пропадания импульса контролируемой последовательности при формировании импульса замены, восстанавливающего входную последовательность. Величины Т - Г и Т + Г являются соответственно минимально и максимально возможными значениями периода следования импульсов контролируемой последовательности за счет нестабильности частоты.

Формула изобретения

Устройство для контроля импульсных последовательностей, содержащее генератор тактовых импульсов, счетчик импульсов, первый, второй и третий триггеры, первый и второй формирователи импульсов, первый, второй, третий и четвертый элементы И, первый, второй и третий элементы ИЛИ, входную шину, подключенную к первому входу первого элемента ИЛИ, второй вход которого соединен с выходом Лервого элемента И, первый вход которого подключен к инверсному выходу первого триггера, первый вход которого через второй элемент ИЛИ соединен с выходом первого формирователя импульсов и с первым входом третьего элемента ИЛИ, выход которого соединен с установочным входом счетчика, прямой выход второго триггера соединен с первыми входами второго и тре380

тьего элементов И, отличающее с я тем, что, с целью расширения функциональных возможностей и повьшения помехоустойчивости, в него введены блок синхронизации, блок управления, первый, второй и третий реверсивные счетчики импульсов, блок коммутации, блок шифраторов, блок де- 10 шифраторов, третий формирователь импульсов, четвертый триггер, пятый, шестой, седьмой и восьмой элементы И, четвертый, пятьй, шестой, седьмой, восьмой и девятый элементы ИЛИ, при

15 этом выход первого элемента ИЛИ подключен к первым входам блока синхронизации, блока управления, к первому входу четвертого элемента И и к первому входу пятого элемента И, второй

20 вход которого соединен с прямым выходом третьего триггера, выход четвертого элемента И соединен с первым входом четвертого элемента ИЛИ, с первым входом блока дешифраторов и с

5 первым входом блока коммутации, второй вход которого соединен с прямым выходом генератора тактовых импульсов, с вторыми входами блока синхронизации и блока управления, с вторым

30 входом второго элемента И, выход которого подключен к входу счетчика импульсов, выход которого подключен к первому входу четвертого триггера, инверсный выход которого соединен с первым входом шестого элемента И выход которого соединен с вторым входом второго элемента ИЛИ, инверсный выход генератора тактовых импульсов соединен с третьими входами блока

40 коммутации и блока синхронизации, четвертый вход которого соединен с выходом пятого элемента ИЛИ, первый вход которого подключен к первому выходу блока управления, второй выход

45 которого подключен к вторым входам пятого элемента ИЛИ и четвертого элемента И, третий и четвертый выходы блока управления подключены соответственно к входам сложения и вычита50 кия первого реверсивного счетчика, пятый и шестой выходы блока управления подключены соответственно к входам сложения и вычитания второго реверсивного счетчика, седьмой и вось5g мой выходы блока управления подключены соответственно к первому и второму входам блока шифраторов, к первым входам восьмого и седьмого элементов Ник второму и третьему

.n

входам блок,-) aciMHifipaTopoB, выход блока синхронизации ткжключен к третьему входу блока управления и к второму входу третьего элемента И.ПИ, выход которого подключен к пepвo fy входу второго триггера, к третьему входу блока шифраторов, к вторым входам седьмого и восьмого элементов И, к пятому входу блока синхронизации и к четвертому входу блока управления, пятьй вход которого соединен с вторым входом шестого элемента И и с инверсным выходом второго триггера, прямой выход которого с:оединен с четвертым входом блока дешифраторов, с третьим входом пятого элемента ИЛИ и с вторым входом четвертого элемента ИЛИ, выход которого соединен с первым входом третьего триггера, второй вход которого соединен с выходом шестого элемента ИЛИ, с вторым входом четвертого триггера и с четвертым входом блока коммутации, пятый вход которого подключен к прямому выходу первого триггера, к второму входу третьего элемента И, к третьим входам седьмого и восьмого элементов Инк пятому входу блока дешифраторов, шестой вход которого подключен к инверсному выходу третьего триггера, прямой выход которого соединен с третьим входом шестого элемента И, четвертый вход которого подключен к выходу второго формирователя импульсов и к первому входу шестого элемента ИЛИ, второй вход которого соединен с вторым входом первого триггера и с выходом третьего реверсивного счетчика импульсов, входы сложения и вычитания которого подключены соответственно к первому и второму выходам блока коммутации, шестой вход которого соединен с выходом пятого элемента И, с входом второго формирователя импульсов и с выходной шиной устройства, седьмой вход блока коммутации соединен с прямым выходом четвертого триг38034

24

гера, с вторым входом первого элемента И, с третьим входом третьего элемента И, с четвертым входом блока шифраторов, первые поразрядные выходы которого подсоединены к входам младших разрядов первого реверсивного счетчика, поразрядные выходы которого соединены соответственно с первой группой входов блока дешифраторов, вторые поразрядные выходы блока шифраторов подсоединены к входам младших разрядов второго реверсивного счетчика, поразрядные выходы которого соединены соответственно с второй группой входов блока дешифраторов, выходы первого и второго реверсивных счетчиков подключены соответственно к первому и второму входам

седьмого элемента ИЛИ, третий и четвертый входы которого подключены соответственно к первому и второму выходам блока дешифраторов, выход седьмого элемента ИЛИ соединен с вторым входом второго триггера, при

этом выход первого формирователя импульсов соединен с первыми входами сброса первого и второго реверсивных счетчиков, с-шестым входом блока управления, с входом сброса третьего реверсивного счетчика, с третьим входом шестого элемента ИЛИ и с седьмым входом блока дешифраторов, третий выход которого соединен с входом

третьего формирователя импульсов, выход которого подключен к первому входу восьмого элемента ИЛИ, второй вход которого соединен с выходом восьмого элемента И, а выход подключен к второму входу сброса первого реверсивного счетчика, выход седьмого элемента И подключен к второму входу сброса второго реверсивиого счетчика, вход первого формирователя

импульсов соединен с выходом девятого элемента ИЛИ, один вход которого подключен к выходу третьего элемента И, а другой вход-к шине сброса устройства.

CSfloc

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления очередностью обслуживания | 1987 |

|

SU1481765A2 |

| Селектор импульсов по длительности | 1980 |

|

SU917331A2 |

| Устройство для контроля резервированного генератора | 1980 |

|

SU907887A1 |

| Селектор импульсов по длительности | 1980 |

|

SU892692A1 |

| Селектор импульсов по длительности | 1983 |

|

SU1150746A1 |

| Селектор импульсов по длительности | 1980 |

|

SU892691A1 |

| Устройство для приема информации | 1988 |

|

SU1550562A1 |

| Устройство для измерения абсолютного отклонения частоты | 1982 |

|

SU1205050A1 |

| Пересчетное устройство | 1980 |

|

SU921093A1 |

| Устройство для индикации | 1978 |

|

SU734755A1 |

Изобретение может быть использовано в устройствах для контроля, обработки и передачи информации. Цель изобретения - расширение функциональных возможностей, достигается путем обеспечения контроля пачек импульсов, а также контроля импульсных последовательностей с неравномерным периодом и повьппение помехоустойчивости. Устройство выполнено на логических элементах и микросхемах и позволяет осуществить контроль импульсных последовательностей при наличии неравномерности периода следования импульсов при нестабильности частоты. Это обеспечивается тем, что сигнал разрешения формируется каждый раз через время Т - Т от момента поступления предьщущего входного импульса и снимается с приходом очередного входного импульса или в момент времени Т + L в случае пропадания импульсов контролируемой последовательности при формировании импульса замены, восстанавливающего входную последовательность. Величины Т -1 и Т Г являются соответственно минимально и максимально возможными значениями периода следования импульсов контролируемой последовательности за счет нестабильности частоты. 8 ил. с (Л оэ со сх о со 4

фигЗ

76

77

7J

75

8Ъ 64

78

79

80 81 82

74

фигЛ

XT ffxodoft . зр. CVS

/Y ff)( /tif/ref u/. /Усгзр. t/e.S

O/ f7aflff3

ff /xoffoS) CVS

O/rr/Topayi

J

ff xoffaff CV6

Фиг 6

an utg

I I

U35

m

HI

иго

Составитель В.Малныкин Редактор Н.Киштулинец Техред М.ДццыкКорректор С.Шекмар

4143/54

Тираж 901Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Устройство для контроля импульсных последовательностей | 1980 |

|

SU930609A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для формирования импульсов | 1982 |

|

SU1064447A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| t | |||

Авторы

Даты

1987-09-15—Публикация

1986-01-03—Подача