(54) ПЕРЕСЧЕТНОЕ УСТРОЙСТВО

1

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах автоматического контроля и управления.

Известно пересчетное устройство, содержащее счетчик, триггер, элемент задержки и элемент И 7 1.

Недостаток устройства - ограниченные возможности выявления сбоев в работе.

Наиболее близким по технической сущности является пересчетное устройство, которое содержит счетчик, суммирующий вход которого подключен к источнику тактовых импульсов, а разрядные выходы - к дешифратору непосредственно и через элемеить задержки - к первым входам элементов И, ко вторым входам которых подключены выходы элементов ИЛИ, к входам котор 1х подключены четные выходы дещифратора, выходной полусумматор, один вход которого соединен с источником тактовых импульсов, а второй вход - с выходом элемента ИЛИ, входы которого подключены к выходам элементов И и к нечетным выходам дешифратора 2.

Однако этому пересчетному устройству присущи недостаточная достоверность выявления неисправностей и ограниченные возможности выявления неисправностей и ограниченные возможности выявления нарушений в работе, которые проявляются .в следующем: при неисправности во входной цепи, когда отсутствуют тактовые импульсы, импульс на выход полусумматора не поступает и Сигнал ощибки не формируется после того, как сформировался схемой контроля импульс отклика, дальнейшие изменения состояний счетчика под действием помех или сбоев не выявляются, т.е. контроль состояния счетчика является не непрерывным, а кратковременным; ложные переходы состояt5 НИИ счетчика при поступлении счетных импульсов выявляются лишь частично. Например, остаются невыявленными ложные переходы в нечетное число.

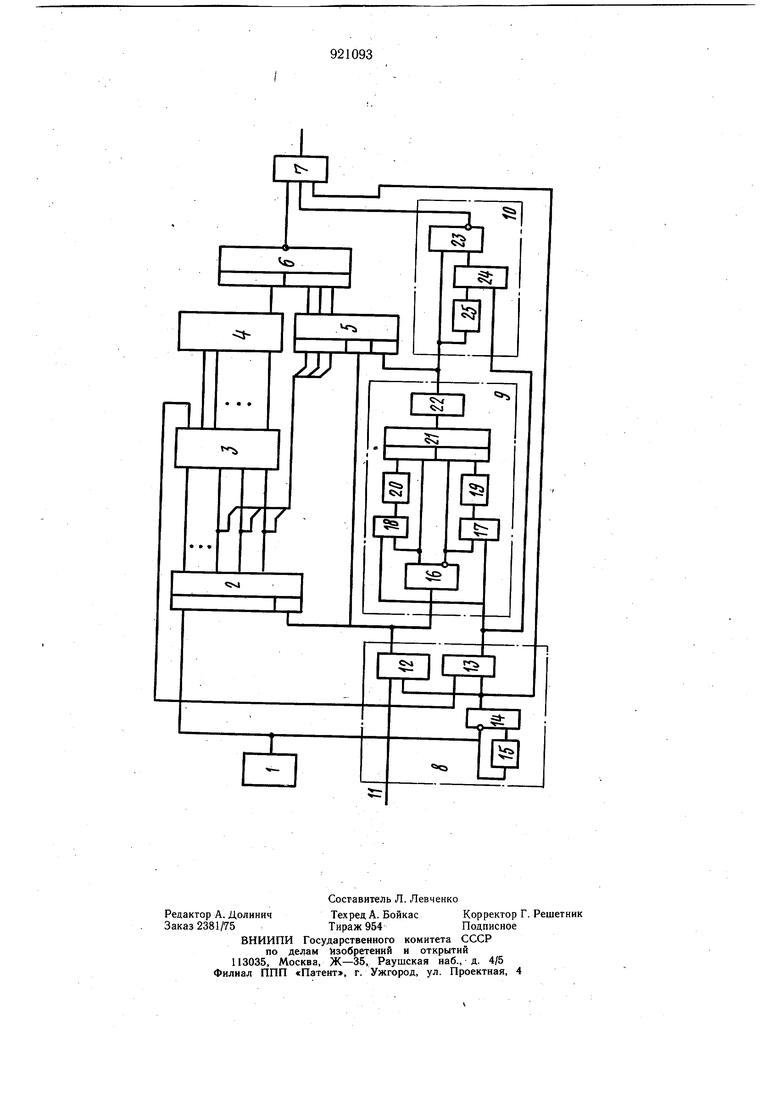

Кроме того, устройство не позволяет произродить сброс счетчика, так как в этом случае может сформироваться сигнал неисправности вследствие изменения порядка чередования показаний счетчика, что ограничивает возможности известного устройства контролем только счетчиков без сброса. Цель изобретения - повышение достоверности выявления неисправностей и расширение возможностей контроля. Поставленная цель достигается тем, что в пересчетное устройство, содержаш,ее п-разрядный счетчик импульсов, суммирующий вход которого подключен к генератору тактовых импульсов, а выходы - к дешифратору, и выходной элемент И, введены регистр, элемент поразрядного сравнения, формирователь заданного интервала, двухканальный элемент задержки, блок синхронизации и шифратор, входы которого соединены с выходами дешифратора, а выходы - с входами элемента поразрядного сравнения, другие входы которого соединены с выходами регистра, а выход - с первым входом выходного элемента И, второй вход которого соединен с выходом формирователя заданного интервала, а третий вход - с первым выходом блока синхронизации, первый, второй и третий входы которого соединены соответственно с генератором тактовых импульсов, с шиной сброса и с соответствующим выходом дешифратора, второй выход - с входам двухканального элемента задержки и с первым входом формирователя заданного интервала, а третий выход - с входом сброса счетчика, с управляющим входом двухканального элемента задержки и с установочным входом регистра, информационные входы которого coeдинekы с выходами ш старших разрядов счетчика, а вход синхронизации - с выходом двухканального элемента задержки и со вторым входом формирователя заданного интервала, кроме того, формирователь заданного интервала содержит триггер, элемент ИЛИ и элемент задержки, выход которого через элемент ИЛИ подключен к нулевому входу триггера, при этом второй вход элемента ИЛИ, установочный вход триггера с подключенным к нему входом элемента задержки и инверсный выход триггера являются соответственно первым и вторым входами и выходом формирователя заданного интервала, кроме того, двухканальный элемент задержки содержит элемент И-ИЛИ, к выходу которого подключен формирователь импульсов, два элемента задержки, выходы которых подключены к первым входам первого и второго элементов И элемента И-ИЛИ; а входы - к выходам третьего и четвертого элементов И, первые входы которых объединены и являются информационным входом двухканального элемента задержки, а вторые входы соединены со вторыми входами первого и второго элементов И элемента И-ИЛИ и соответственно с Лрямым и инверсным выходами триггера, счетный вход которого является управляющим входом двухканального элемента задержки, кроме того, блок синхронизации содержит Щ-триггер, элемент И и элемент ИЛИ, инверсный вход которого соединен с его прямым входом через элемент задержки, а выход - с управляющим входом 1К-триггера и с первым входом элемента И, при этом инверсный вход элемента ИЛИ, 1-вход триггера и второй вход элемейта И являются соответственно первым, вторым и третьим входами блока синхронизации, а выход элемента ИЛИ, выход элемента И и выход 1К-триггера соответственно первым, вторым и третьим выходами блока синхронизации. На чертеже представлена схема пересчетного устройства. Устройство содержит генератор 1 тактовых импульсов, счетчик 2, дешифратор 3, шифратор 4, регистр 5, элемент 6 поразрядного сравнения, элемент И 7 выходной блок 8 синхронизации, элемент 9 задержки двухканальный, формирователь 10 заданного интервала, шину 11 сброса устройства. Первый, второй и третий входы блока 8 синхронизации подключены соответственно к генератору 1, шине 11 и к выходу дешифратора 3, соответствующему нулевому состоянию (), младших разрядов счетчика 2. Блок 8 синхронизации содержит триггер 12, элемент И 13 и элемент ИЛИ 14, инверсный вход которого через элемент задержки 15 соединен с его прямым входом, а выход - с первым входом элемента И 13 и с управляющим входом триггера 12. Элемент 9 задержки двухканальный содержит триггер 16, элементы И 17 и 18, элементы задержки 19 и 20, элемент И-ИЛИ 21 и выходной формирователь 22. Формирователь 10 заданного интервала содержит триггер 23, элемент ИЛИ 24 И элемент 25 задержки. .Устан эвочный вход триггера 23 через элемент 25 задержки подключен к одному входу элемента ИЛИ 24, выход которого соединен с нулевым входом триггера 23. Устройство работает следующим образом. В исходном состоянии устройства все триггеры находятся в нулевом состоянии, при котором на -инверсных выходах триггеров единичные сигналы, счетчик 2 в нулевом состоянии, а все разряды регистра 5 - в единичном состоянии. Сигналы с дешифратора 3 преобразуются шифратором 4 в т-разрядный двоичный код, значение которого на единицу меньше поступающего на дешифратор 3 показания ш старших разрядов счетчика 2. Код с выхода шифратора 4 поступает на одни входы элемента 6 поразрядного сравнения, на другие входы которого лоступает т-разрядный код с регистра 5. При совпадении входных кодов на выходе элемента 6 поддерживается нулевой сигнал, который закрывает по первому входу выходной элемент И 7. Тактовые импульсы с генератора Ivпоступают на суммирующ ий вход счетчика 2 и на вход формирователя, образованного элементом ИЛИ 14 и элементом 15 зддержки. Счетчик 2 подсчитывает тактовые импульсы, с его выходов .сигналы поступают на дешифратор 3, а сигналы ш старших разрядов счетчика. 2 - и на вход регистра 5. Показания ш старших разрядов счетчика 2 периодически переписываются на регистр 5. Запись на регистр 5 кода производится по команде, поступающей на его вход синхронизации с выхода элемента 9 задержки, которая формируется непосредственно перед каждым очередным изменением показания старших разрядов счетчика 2. Отрицательный сигнал на выходе формирователя 10 задает временной интервал, в течение которого происходит перезапись на регистр 5 показания старших разрядов счетчика 2, а затем увеличение показания m старших разрядов счетчика 2. Таким образом, хранящийся на регистре 5 код все время отстает на единицу от показания старших разрядов счетчика 2, а преобразованное дешифратором 3 и шифратором 4 показание счетчика 2 на выходе шифратора 4 все время совпадает ,с показанием регистра 5, за исключением коротких интервалов времени перезаписи информации на регистр и переключения показания счетчика, в течение которых запрещается по второму или третьему входам срабатывание элементов И 7. Совпадение входных сигналов непрерывно контролируется элементом 6 поразрядного сравнения. При нормальной работе устройства сигналы на входах элемента 6 совпадают и отрицательный сигнал с выхода элемента 6 закрывает по первому входу элемент И 7. Поступающий на входную шину сброса 11 сигнал сброса вызывает срабатывание триггера 12, с выхода которого сигнал, синхронизированный тактовыми импульсами, поступает на возврат счетчика 2 и регистра 5 в исходное состояние. Синхронизацией импульса возврата счетчика 2 и регистра 5 в исходное состояние достигается уменьШение разбросов задания формирователем 10 временных интервалов и тем самым исключение возможности формирования ложной команды при нормальной работе устройства. После возврата счетчика 2 и регистра 5 в исходное состояние сигналы на.входах элемента 6 поразрядного сравнения совпадают, поэтому на есо выходе сигнал неисправности не формируется. Сброс устройства может быть осуществлен в произвольный момент времени без выдачи ложной команды неисправности: При нарушении работы счетчика 2, приводящем к неправильным переходам его СОСТОЯНИЙ относительно зафиксированных регистром 5, а также при нарушении работы дешифратора 3, шифратора 4 или регистра. 5 сигналц на входах элемента 6 перестают совпадать, на выходе элемента 6 формируется единичный сигнал, который поступает на выходной, элемент И 7 и вызывает его срабатывание, тем самым фиксируется воз1 икшее нарушение. Нарушения работы генератора 1 (изменение периода следования тактовых импульсов свыше граничных значений), сбои (п-т), младших разрядов счетчика 2 или пропуски счетных импульсов вызывают расфазировку моментов переключения входных кодов, поступающих на элемент 6 поразрядного сравнения, при этом на выходе элемента 6 появляется единичный сигнал,, вызывающий срабатывание элемента И 7, тем самым фиксируется возникшее нарушение работы. При прекращении работы генератора 1 (отсутствие тактовых импульсов) показание счетчика 2 перестает изменяться. В этом случае код на регистре 5 выравнивается с показанием старших разрядов счетчика 2, а так как выходной код дешифратора 4 на единицу меньше показания старших разрядов счетчика 2, то на входе элемента.б коды не Совпадают и на его выходе устанавливается единичный сигнал, который вызывает. срабатывание элемента И 7, тем самым фиксируется возникшее нарушение работы. Нарушения работы блока 8 синхронизации, элемента 9 задержки или формирователя 10, которые вызывают расфазировку моментов переключения информации на входах элемента 6 или расфазировку импульсов запрета контроля на втором и третьем входах элемента И 7 с момента изменения показаний счетчика, также вызывают срабатывание элемента И 7 и тем самым фиксируются выходным сигналом. Таким образом, работа генератора 1, счетчика 2, дешифратора 3, шифратора 4 и регистра 5 непрерывно контролируется по совпадению сигналов на входах элемента 6 поразрядного сравнения, на одни входы которой поступают преобразованные дешифратором 3 и шифратором 4 текущие показания счетчика 2, а на другие входы -.- зафиксированные регистром 5 предыдущие показания старших разрядов счетчика 2, которые переписываются на регистр 5 перед каждым очередным изменением по управляющим командам, которые вырабатываются блоком 8 синхронизации и элементом 9 задержки. Возврат счетчика 2 и регистра 5 в исходное состояние импульсом сброса не нарушают непрерывный контроль работь устройства и не приводит к выдаче ложной команды. Блок 8 синхронизации вырабатывает импульсы кратковременного запрета выходно- го элемента И 7 на время распространения счетного импульса, формирует сигнал на вход элемента 9 задержки по выявляемо79210му дешифратором 3 нулевому состоянию младших разрядов счетчика, а также формирует сигналы сброса счетчика 2, установки регистра 5 и переключения канала элемента 9 задержки. Вырабатываемые блоком 8 сирхрониза- s ции, элементом 9 задержки и формирователем 10 сигналы управляют работой элемента И 7, счетчика 2 и регистра 5 таким образом, что контроль работы узлов по совпадению сигналов на входе элемента 6 поразрядного сравнения осуществляется не- прерывно, а не на отдельных коротких интервалах времени, а контролем охвачен и генератор 1 тактовых импульсов. Использование для записи на регистр 5 только m старших разрядов счетчика 2 позволяет обеспечить полноту контроля, ограничив величиной m число разрядов регистра 5 и элемента 6 поразрядного сравнения, а также длину выходного кода шифратора 4 без чрезмерного усложнения устройства и без уменьшения полноты контроля. Формула изобретения L Пересчетное устройство, содержащее п-разрядный счетчик импульсов, суммирую--с щий вход которого подключен к генератору тактовых импульсов, а выходы - к дешифратору, и выходной элемент И, отличающееся тем, что, с целью повышения достоверности выявления неисправностей и расширения возможностей контроля, в него введе- зо ны регистр, элемент поразрядного сравнения, формирователь заданного иртервала, двухканальный элемент задержки, блок синхронизации и шифратор, входы которого соединены с выходами дешифратора, а выходы - с входами элемента поразрядного сравне- 35 кия, другие входы которого соединены с выходами регист;ра, а выход - с первым входом выходного элемента И, второй вход которого соединен с выходом формирователя заданного интервала, а третий вход - с п-ервым выходом блока синхронизации, первый, второй и третий входы которого соединены соответственно с генератором тактовых импульсов, с шиной сброса и с COOTвет.ствующиМ выходом дешифратора, второй выход - с входом двухканального элемен- 45 та задержки и с первым входо и формирователя заданного интервала, а третий выход - с входом сброса счетчика, с управляющим входом двухканального элемента задержки и с установоч38ным входом регистра, информационные вхо Ды которого соединены с выходами ш старших разрядов счетчика, а вход синхронизации - с выходом двухканального элемента задержки и с вторым входом формирователя заданного интервала. 2. Устройство по п. 1, отличающееся тем, что формирователь заданного интервала содержит триггер, элемент ИЛИ и элемент задержки, .выход которого через элемент ИЛИ подключен к нулевому входу триггера, при этом второй вход элемента ИЛИ, установочный вход триггера с подключенным к нему входом элемента задержки, и инверсный выход триггера являются соответственно первым и вторым входами и выходом формирователя заданного интервала. 3. Устройство по п. I, отличающееся тем, чта двухканальный элемент задержки содержит элемент И-ИЛИ, к выходу которого подключен формирователь импульсов, Два элемента задержки, выходы которых подключены к первым входам первого и второго элементов И элемента И-ИЛИ, а входы - к выходам третьего и четвертого элементов И, первые входы которых объединены и являются информационным входом двухканального элемента задержки, а вторые входы соединены с вторыми входами первого и второго элементов И элемента И-ИЛИ и соответственно с прямым и инверсным выходами триггера, счетный вход которого является управляющим входом двухканального элемента задержки, 4. Устройство по п. 1, отличающееся тем, что блок синхронизации содержит 1К-триггер, элемент И и элемент ИЛИ, инверсный вход которого соединен с его прямым входом через элемент задержки, а вы- . ход - с управляющим входом 1К-триггера и с первым входом элемента И, при этом инверсный вход элемента ИЛИ, 1-вход триггера и второй вход элемента И являются соответственно первым, вт.орым и третьим входами блока синхронизации, а выход элемента ИЛИ, выход элемента И и выход К-триггера - соответственно первым, вторым и третьим выходами блока синхронизации. Источники, информации, принятые во внимание при экспертизе I. Авторское свидетельство СССР № 457179, кл. Н 03 К 21/34, 1873. 2. Авторское свидетельство СССР № 702526, кл. Н 03 К 21/34, 1-976 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля резервированного генератора | 1980 |

|

SU907887A1 |

| Многоканальное устройство контроля для управляющих вычислительных систем | 1983 |

|

SU1101829A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ РЕГЕНЕРАЦИЕЙ В ПОЛУПРОВОДНИКОВОМ ДИНАМИЧЕСКОМ ЗАПОМИНАЮЩЕМ УСТРОЙСТВЕ | 1994 |

|

RU2040808C1 |

| Устройство для контроля импульсных последовательностей | 1986 |

|

SU1338034A1 |

| Устройство для вычисления @ | 1983 |

|

SU1156067A1 |

| СЕЛЕКТОР ИМПУЛЬСОВ | 2011 |

|

RU2474043C1 |

| МОДУЛЬ МУЛЬТИМИКРОПРОГРАММНОЙ СИСТЕМЫ | 1997 |

|

RU2116665C1 |

| Устройство для измерения абсолютного отклонения частоты | 1982 |

|

SU1205050A1 |

| Быстродействующий аналого-цифровой преобразователь | 1985 |

|

SU1254584A1 |

| Устройство для сопряжения микроЭВМ с внешним устройством | 1985 |

|

SU1283780A1 |

Авторы

Даты

1982-04-15—Публикация

1980-07-04—Подача