Изобретение относится к электросвязи и может быть использовано на приемной строке в системах передачи информации.

Цель изобретения - повышение достоверности приема информации,

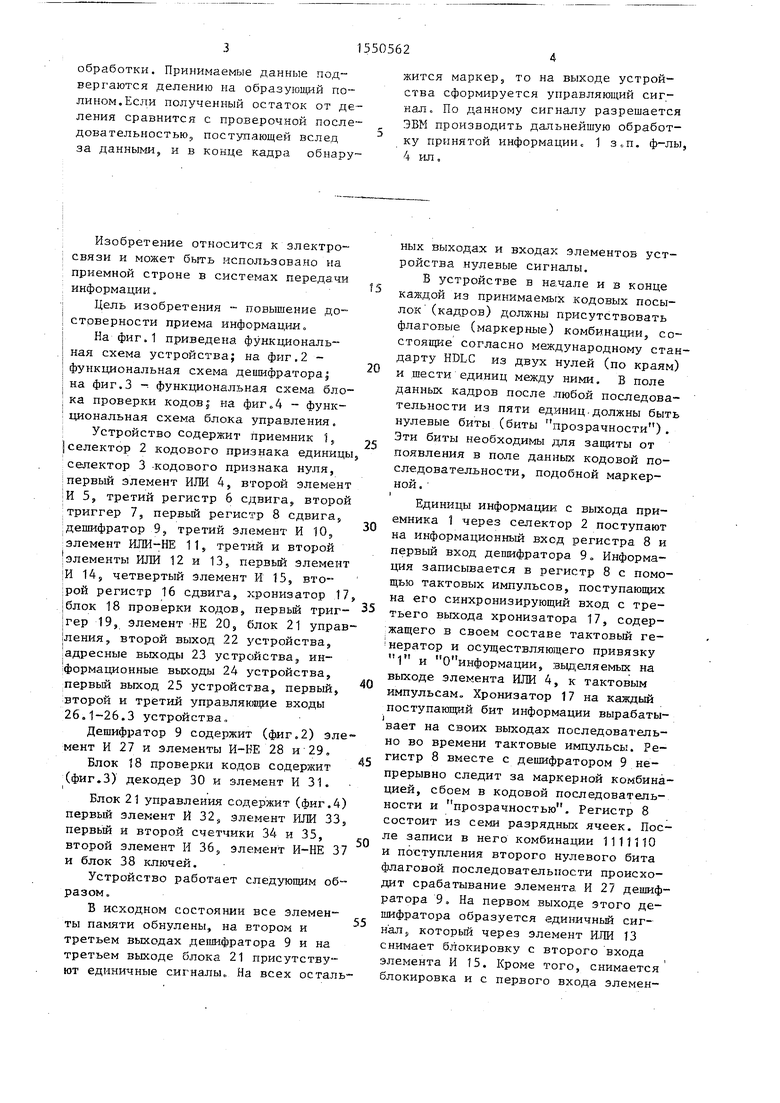

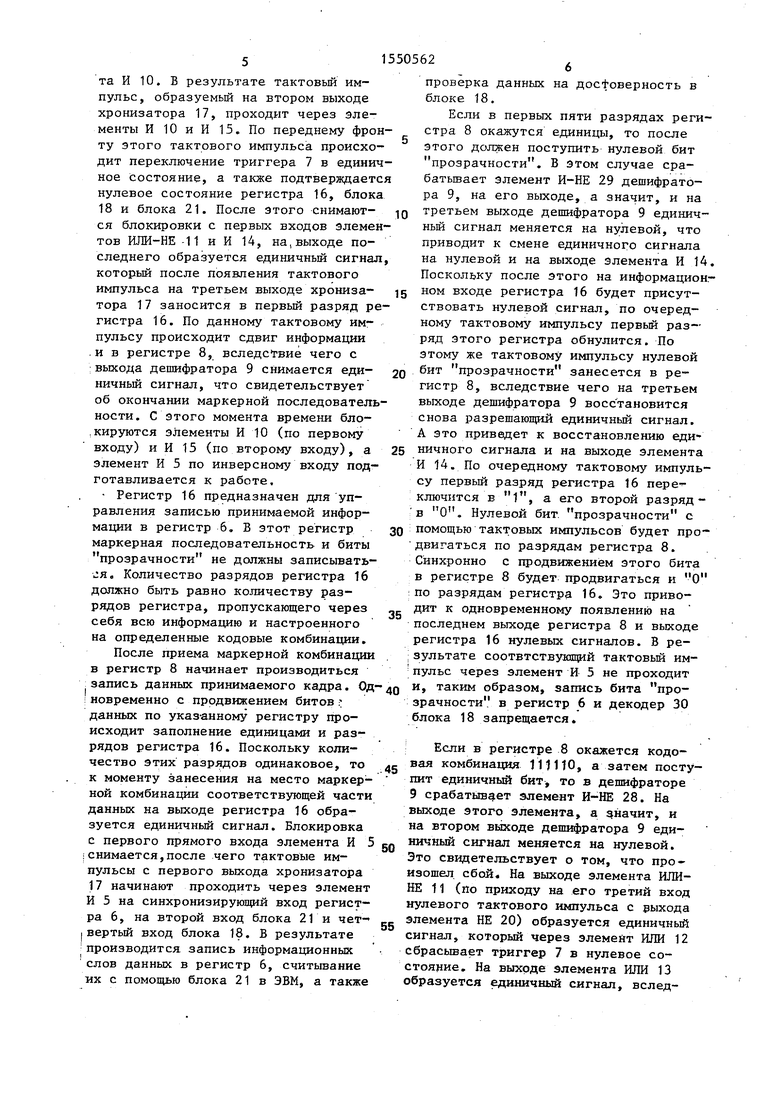

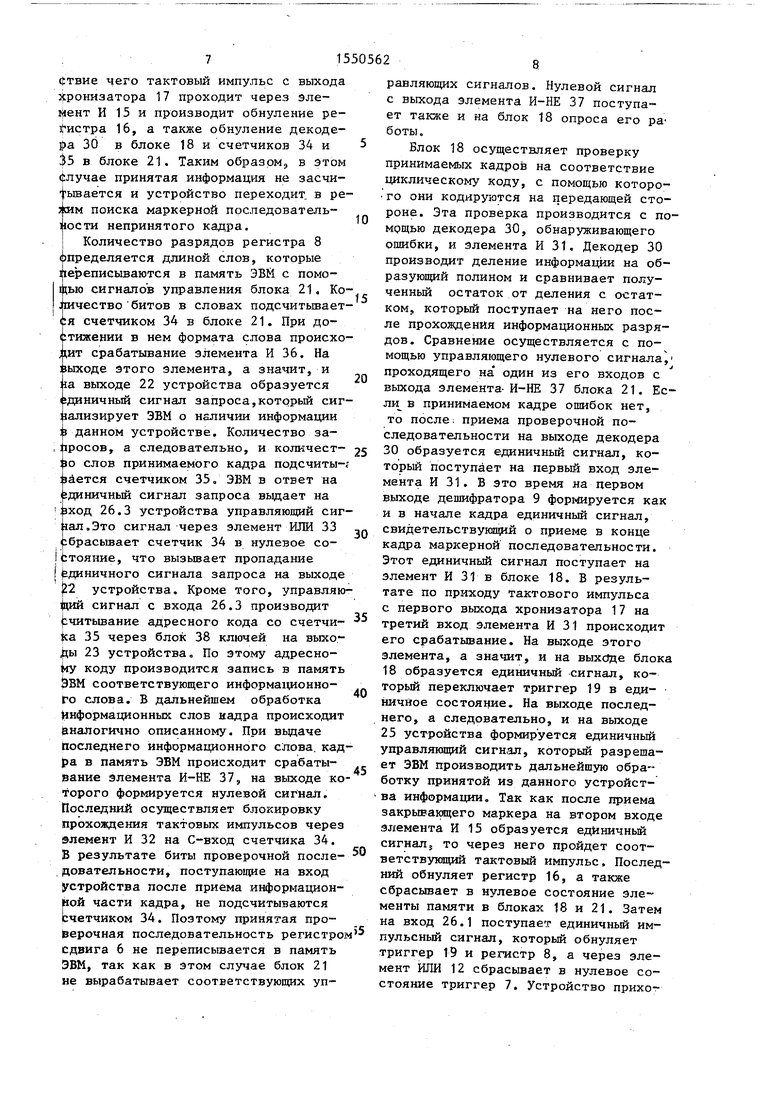

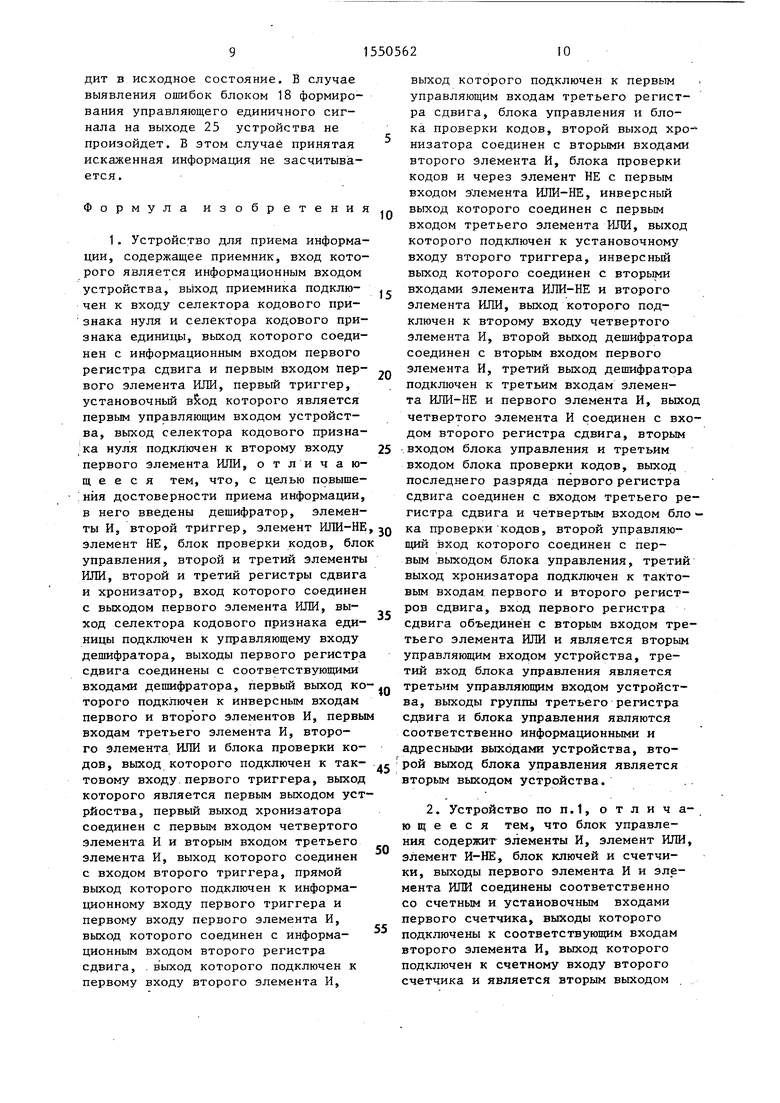

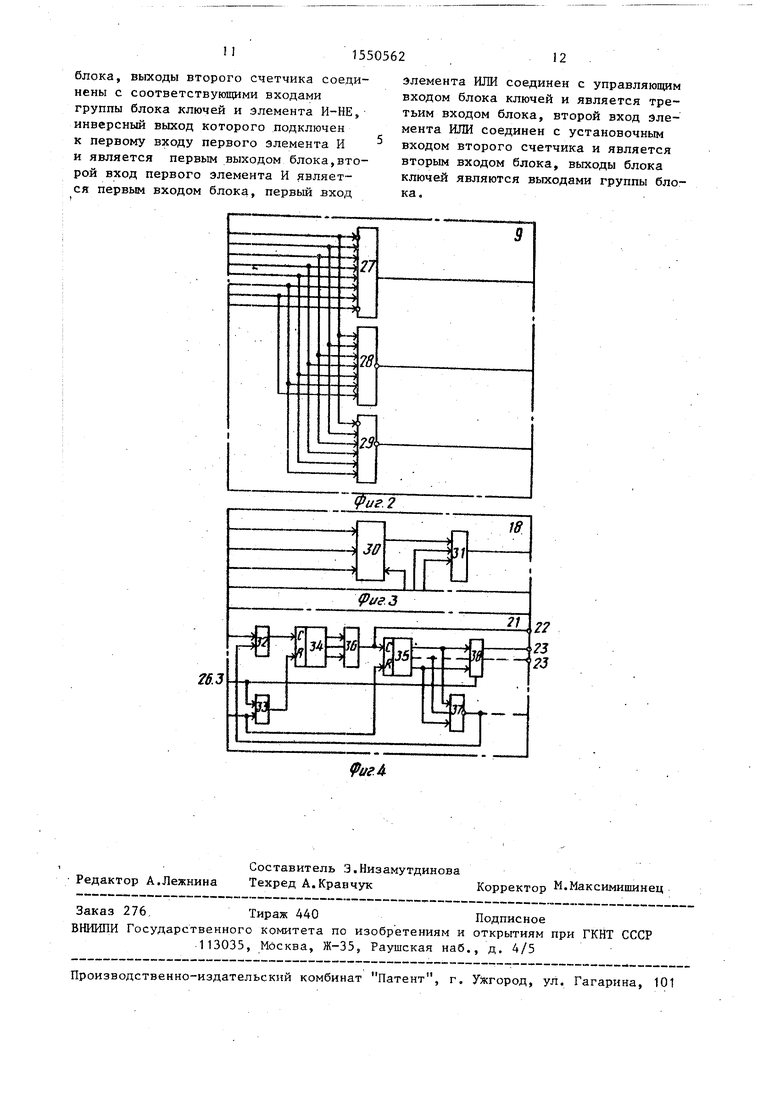

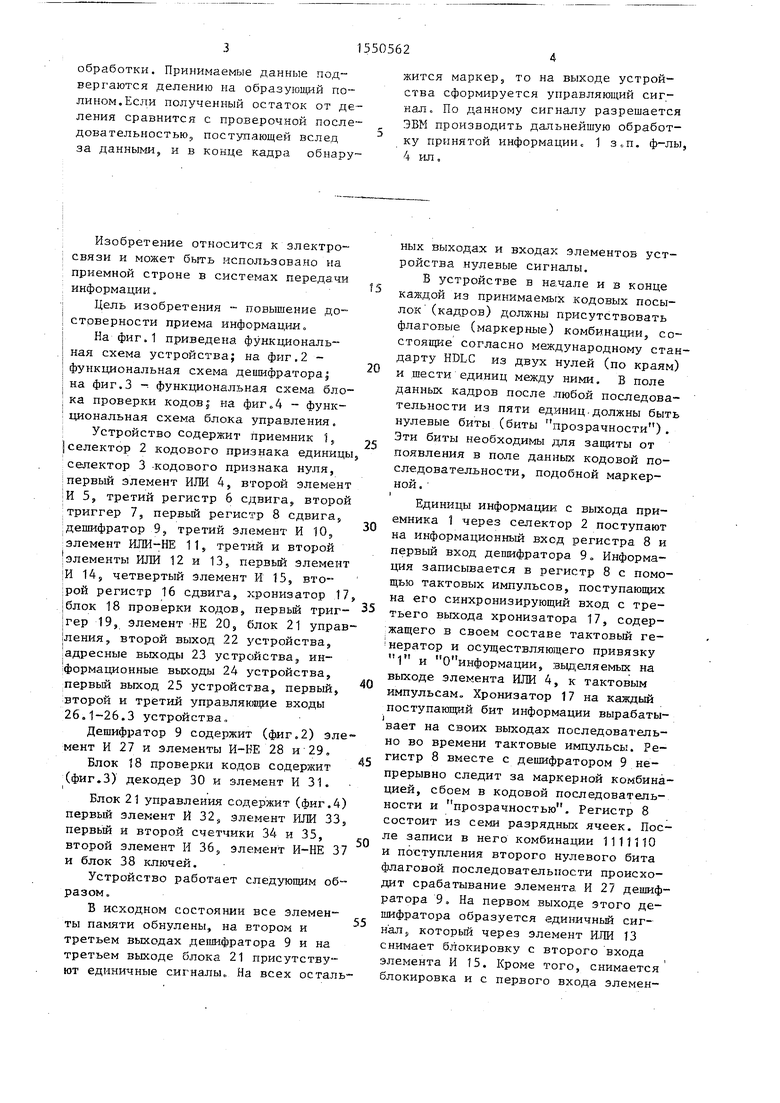

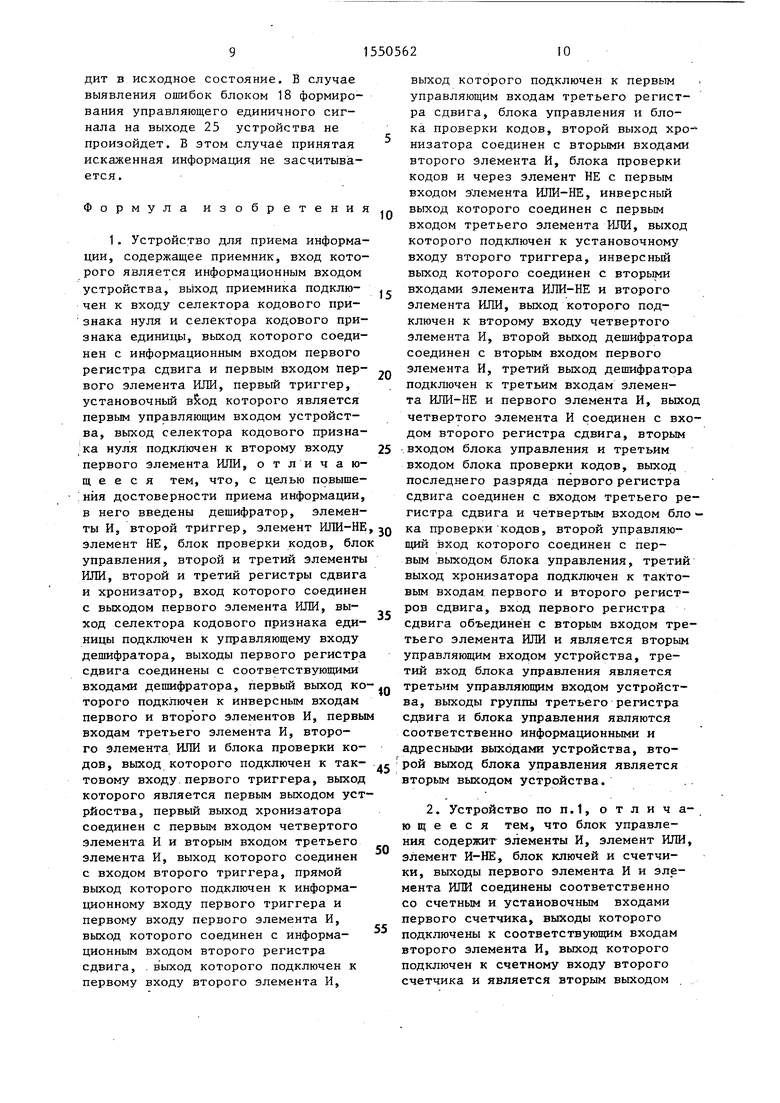

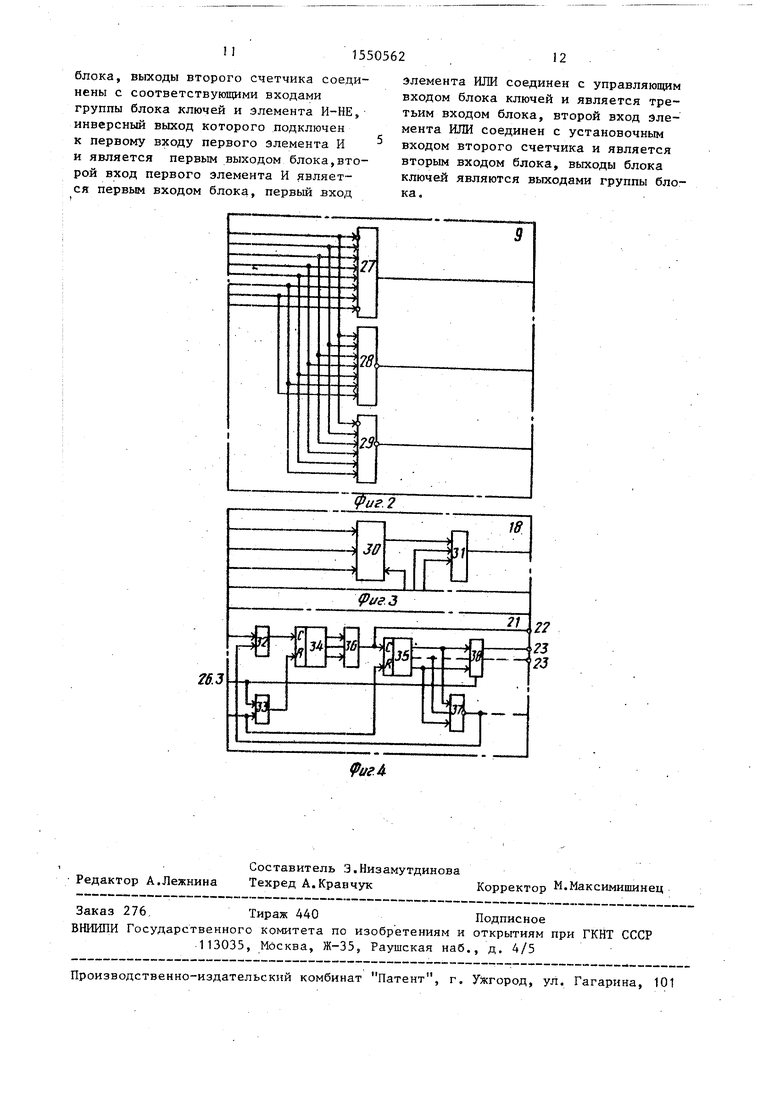

На фиг.1 приведена функциональная схема устройства; на фиг,2 - функциональная схема дешифратораj на фиг.З - функциональная схема блока проверки кодовj на фиг.4 - функциональная схема блока управления.

Устройство содержит приемник 1, |селектор 2 кодового признака единицы селектор 3 кодового признака нуля, первый элемент ИЛИ 4, второй элемент И 5, третий регистр 6 сдвига, второй триггер 7, первый регистр 8 сдвига, дешифратор 9, третий элемент И 10, элемент ИЛИ-НЕ 11, третий и второй элементы ИЛИ 12 и 13, первый элемент И 14, четвертый элемент И 15, второй регистр 16 сдвига, хронизатор 17 блок 18 проверки кодов, первый триг- гер 19, элемент НЕ 20, блок 21 управления, второй выход 22 устройства, адресные выходы 23 устройства, информационные выходы 24 устройства, первый выход 25 устройства, первый, второй и третий управляющие входы 26.1-26.3 устройства

Дешифратор 9 содержит (фиг.2) элемент И 27 и элементы И-FE 28 и 29.

Блок 18 проверки кодов содержит (фиг.З) декодер 30 и элемент И 31.

I

Блок 21 управления содержит (фиг,4) первый элемент И 32s элемент ИЛИ 33, первый и второй счетчики 34 и 35, второй элемент И 36, элемент И-НЕ 37 и блок 38 ключей.

Устройство работает следующим образом.

В исходном состоянии все элементы памяти обнулены, на втором и третьем выходах дешифратора 9 и на третьем выходе блока 21 присутствуют единичные сигналы. На всех осталь

5

0

ъ 5

п

0

5

5

ных выходах и входах элементов устройства нулевые сигналы.

В устройстве в начале и в конце каждой из принимаемых кодовых посылок (кадров) должны присутствовать флаговые (маркерные) комбинации, состоящие согласно международному стандарту HDLC из двух нулей (по краям) и шести единиц между ними. В поле данных кадров после любой последовательности из пяти единиц должны быть нулевые биты (биты прозрачности). Эти биты необходимы для защиты от появления в поле данных кодовой последовательности, подобной маркерной.

Единицы информации с выхода приемника 1 через селектор 2 поступают на информационный вхсд регистра 8 и первый вход дешифратора 9, Информация записывается в регистр 8 с помощью тактовых импульсов, поступающих на его синхронизирующий вход с третьего выхода хронизатора 17, содержащего в своем составе тактовый генератор и осуществляющего привязку ) и 0 информации, выделяемых на выходе элемента ИЛИ 4, к тактовым импульсам. Хронизатор 17 на каждый

поступающий бит информации вырабаты- j

вает на своих выходах последовательно во времени тактовые импульсы. Регистр 8 вместе с дешифратором 9 непрерывно следит за маркерной комбинацией, сбоем в кодовой последовательности и прозрачностью. Регистр 8 состоит из семи разрядных ячеек. После записи в него комбинации 1111110 и поступления второго нулевого бита флаговой последовательности происходит срабатывание элемента И 27 дешифратора 9. На первом выходе этого дешифратора образуется единичный сигнал, который через элемент ИЛИ 13 снимает блокировку с второго входа элемента И 15. Кроме того, снимается блокировка и с первого входа элемен20

25

та И 10. В результате тактовьй импульс, образуемый на втором выходе хронизатора 17, проходит через элементы И 10 и И 15. По переднему фронту этого тактового импульса происходит переключение триггера 7 в единичное состояние, а также подтверждается нулевое состояние регистра 16, блока 18 и блока 21. После этого снимают- 10 ся блокировки с первых входов элементов ИЛИ-НЕ 11 и И 14, на,выходе последнего образуется единичный сигнал, который после появления тактового импульса на третьем выходе хрониза- 15 тора 17 заносится в первый разряд регистра 16. По данному тактовому импульсу происходит сдвиг информации и в регистре 8, вследствие чего с выхода дешифратора 9 снимается единичный сигнал, что свидетельствует об окончании маркерной последовательности. С этого момента времени блокируются элементы И 10 (по первому входу) и И 15 (по второму входу), а элемент И 5 по инверсному входу подготавливается к работе,

Регистр 16 предназначен для управления записью принимаемой информации в регистр 6. В этот регистр маркерная последовательность и биты прозрачности не должны записываться. Количество разрядов регистра 16 должно быть равно количеству разрядов регистра, пропускающего через себя всю информацию и настроенного на определенные кодовые комбинации.

После приема маркерной комбинации в регистр 8 начинает производиться запись данных принимаемого кадра. Од- 4Q новременно с продвижением битов данных по указанному регистру происходит заполнение единицами и разрядов регистра 16. Поскольку количество этих разрядов одинаковое, то к моменту занесения на место маркерной комбинации соответствующей части анных на выходе регистра 16 образуется единичный сигнал. Блокировка с первого прямого входа элемента И 5 нимается,после чего тактовые имульсы с первого выхода хронизатора 17 начинают проходить через элемент 5 на синхронизирующий вход региста 6, на второй вход блока 21 и чет- ертый вход блока 18. В результате роизводится запись информационных лов данных в регистр 6, считывание х с помощью блока 21 в ЭВМ, а также

30

35

45

50

55

20

25

10 15 4Q

30

35

45

0

5

проверка данных на достоверность в блоке 18.

Если в первых пяти разрядах регистра 8 окажутся единицы, то после этого должен поступить нулевой бит прозрачности. В этом случае срабатывает элемент И-НЕ 29 дешифратора 9, на его выходе, а значит, и на третьем выходе дешифратора 9 единичный сигнал меняется на нулевой, что приводит к смене единичного сигнала на нулевой и на выходе элемента И 14. Поскольку после этого на информационном входе регистра 16 будет присутствовать нулевой сигнал, по очередному тактовому импульсу первый разряд этого регистра обнулится. По этому же тактовому импульсу нулевой бит прозрачности занесется в регистр 8, вследствие чего на третьем выходе дешифратора 9 восстановится снова разрешающий единичный сигнал. А это приведет к восстановлению единичного сигнала и на выходе элемента И 14. По очередному тактовому импульсу первый разряд регистра 16 переключится в 1, а его второй разряд - в 0й. Нулевой бит прозрачности с помощью тактовых импульсов будет продвигаться по разрядам регистра 8. Синхронно с продвижением этого бита в регистре 8 будет продвигаться и О по разрядам регистра 16. Это приводит к одновременному появлению на последнем выходе регистра 8 и выходе регистра 16 нулевых сигналов. В результате соотвтствующий тактовый им- пульс через элемент И 5 не проходит и, таким образом, запись бита прозрачности в регистр 6 и декодер 30 блока 18 запрещается.

Если в регистре 8 окажется кодовая комбинация 1ИИО, а затем поступит единичный бит, то в дешифраторе 9 срабатывает элемент И-НЕ 28. На выходе этого элемента, а значит, и на втором выходе дешифратора 9 единичный сигнал меняется на нулевой. Это свидетельствует о том, что произошел сбой. На выходе элемента ИЛИ- НЕ 11 (по приходу на его третий вход нулевого тактового импульса с выхода элемента НЕ 20) образуется единичный сигнал, который через элемент ИЛИ 12 сбрасывает триггер 7 в нулевое состояние. На выходе элемента ИЛИ 13 образуется единичный сигнал, вслед

Ствие чего тактовый импульс с выхода хронизатора 17 проходит через элемент И 15 и производит обнуление регистра 16, а также обнуление декодера 30 в блоке 18 и счетчиков 34 и 35 в блоке 21. Таким образом, в этом Случае принятая информация не засчи- фывается и устройство переходит в ре- зоим поиска маркерной последовательности непринятого кадра. | Количество разрядов регистра 8 Определяется длиной слов, которые йереписываются в память ЭВМ с помо- цью сигналов управления блока 21. Количество битов в словах подсчитывается счетчиком ЗА в блоке 21. При достижении в нем формата слова происходит срабатывание элемента И 36. На пыходе этого элемента, а значит, и на выходе 22 устройства образуется единичный сигнал запроса,который сигнализирует ЭВМ о наличии информации данном устройстве. Количество за- ,росов, а следовательно, и колкчест- Јо слов принимаемого кадра подсчиты-; лается счетчиком 35. ЭВМ в ответ на единичный сигнал запроса выдает на 1 ;зход 26.3 устройства управляющий сигнал. Это сигнал через элемент ИЛИ 33 сбрасывает счетчик 34 в нулевое со- Стояние, что вызывает пропадание {Единичного сигнала запроса на выходе J22 устройства. Кроме того, управляющий сигнал с входа 26.3 производит считывание адресного кода со счетчи- fca 35 через блок 38 ключей на выходы 23 устройства. По этому адресному коду производится запись в память ЭВМ соответствующего информационного слова. В дальнейшем обработка (информационных слов надра происходит аналогично описанному. При выдаче Последнего информационного слова, кад (а в память ЭВМ происходит срабатывание элемента И-НЕ 37, на выходе которого формируется нулевой сигнал. Последний осуществляет блокировку Прохождения тактовых импульсов через элемент И 32 на С-вход счетчика 34. В результате биты проверочной после- довательности, поступающие на вход устройства после приема информационной части кадра, не подсчитываются счетчиком 34. Поэтому принятая проверочная последовательность регистро сдвига 6 не переписывается в память ЭВМ, так как в этом случае блок 21 не вырабатывает соответствующих уп

0

5 0 0

0

равляющих сигналов. Нулевой сигнал с выхода элемента И-НЕ 37 поступает также и на блок 18 опроса его ра боты.

Блок 18 осуществляет проверку принимаемых кадров на соответствие циклическому коду, с помощью которо- го они кодируются на передающей стороне. Эта проверка производится с по- мрщью декодера 30, обнаруживающего ошибки, и элемента И 31. Декодер 30 производит деление информации на образующий полином и сравнивает полученный остаток от деления с остатком, который поступает на него после прохождения информационных разрядов. Сравнение осуществляется с помощью управляющего нулевого сигнала 1 проходящего на один из его входов с выхода элемента-И-НЕ 37 блока 21. Если в принимаемом кадре ошибок нет, то после. приема проверочной последовательности на выходе декодера 30 образуется единичный сигнал, ко- то рый поступает на первый вход элемента И 31. В это время на первом выходе дешифратора 9 формируется как и в начале кадра единичный сигнал, свидетельствующий о приеме в конце кадра маркерной последовательности. Этот единичный сигнал поступает на элемент И 31 в блоке 18. В результате по приходу тактового импульса с первого выхода хронизатора 17 на третий вход элемента И 31 происходит его срабатывание. На выходе этого элемента, а значит, и на выходе блока 18 образуется единичный сигнал, который переключает триггер 19 в единичное состояние. На выходе последнего, а следовательно, и на выходе 25 устройства формируется единичный управляющий сигнал, который разрешает ЭВМ производить дальнейшую обработку принятой из данного устройства информации. Так как после приема закрывающего маркера на втором входе элемента И 15 образуется единичный сигналз то через него пройдет соответствующий тактовый импульс. Последний обнуляет регистр 16, а также сбрасывает в нулевое состояние элементы памяти в блоках 18 и 21. Затем на вход 26.1 поступает единичный импульсный сигнал, который обнуляет триггер 19 и регистр 8, а через элемент ИЛИ 12 сбрасывает в нулевое состояние триггер 7. Устройство приходит в исходное состояние. В случае выявления ошибок блоком 18 формирования управляющего единичного сигнала на выходе 25 устройства не произойдет. В этом случае принятая искаженная информация не засчитывается.

Формула изобретения

1. Устройство для приема информации, содержащее приемник, вход которого является информационным входом устройства, выход приемника подклю- чен к входу селектора кодового признака нуля и селектора кодового признака единицы, выход которого соединен с информационным входом первого регистра сдвига и первым входом пер- вого элемента ИЛИ, первый триггер, установочный вход которого является первым управляющим входом устройства, выход селектора кодового призна- ,ка нуля подключен к второму входу первого элемента ИЛИ, отличающееся тем, что, с целью повышения достоверности приема информации, в него введены дешифратор, элементы И, второй триггер, элемент ИЛИ-НЕ элемент НЕ, блок проверки кодов, блок управления, второй и третий элементы ИЛИ, второй и третий регистры сдвига и хронизатор, вход которого соединен с выходом первого элемента ИЛИ, выход селектора кодового признака единицы подключен к управляющему входу дешифратора, выходы первого регистра сдвига соединены с соответствующими входами дешифратора, первый выход ко- торого подключен к инверсным входам первого и втор ого элементов И, первым входам третьего элемента И, второго элемента ИЛИ и блока проверки кодов, выход которого подключен к так- товому входу первого триггера, выход которого является первым выходом уст- рйоства, первый выход хронизатора соединен с первым входом четвертого элемента И и вторым входом третьего элемента И, выход которого соединен с входом второго триггера, прямой выход которого подключен к информационному входу первого триггера и первому входу первого элемента И, выход которого соединен с информационным входом второго регистра сдвига, выход которого подключен к первому входу второго элемента И,

10

, 2 25 JQ ,. .,

35

0

5

выход которого подключен к первым управляющим входам третьего регистра сдвига, блока управления и блока проверки кодов, второй выход хро- низатора соединен с вторыми входами второго элемента И, блока проверки кодов и через элемент НЕ с первым входом элемента ИЛИ-НЕ, инверсный выход которого соединен с первым входом третьего элемента ИЛИ, выход которого подключен к установочному входу второго триггера, инверсный выход которого соединен с вторыми входами элемента ИЛИ-НЕ и второго элемента ИЛИ, выход которого подключен к второму входу четвертого элемента И, второй выход дешифратора соединен с вторым входом первого элемента И, третий выход дешифратора подключен к третьим входам элемента ИЛИ-НЕ и первого элемента И, выход четвертого элемента И соединен с входом второго регистра сдвига, вторым входом блока управления и третьим входом блока проверки кодов, выход последнего разряда первого регистра сдвига соединен с входом третьего регистра сдвига и четвертым входом бло - ка проверки кодов, второй управляющий вход которого соединен с первым выходом блока управления, третий выход хронизатора подключен к тактовым входам первого и второго регистров сдвига, вход первого регистра сдвига объединен с вторым входом третьего элемента ИЛИ и является вторым управляющим входом устройства, третий вход блока управления является третьим управляющим входом устройства, выходы группы третьего регистра сдвига и блока управления являются соответственно информационными и адресными выходами устройства, второй выход блока управления является вторым выходом устройства.

2. Устройство поп.1, отличающееся тем, что блок управления содержит элементы И, элемент ИЛИ, элемент И-НЕ, блок ключей и счетчики, выходы первого элемента И и элемента ИЛИ соединены соответственно со счетным и установочным входами первого счетчика, выходы которого подключены к соответствующим входам второго элемента И, выход которого подключен к счетному входу второго счетчика и является вторым выходом

блока, выходы второго счетчика соединены с соответствующими входами группы блока ключей и элемента И-НЕ, инверсный выход которого подключен к первому входу первого элемента И и является первым выходом блока,второй вход первого элемента И является первым входом блока, первый вход

элемента ИЛИ соединен с управляющим входом блока ключей и является третьим входом блока, второй вход элемента ИЛИ соединен с установочным входом второго счетчика и является вторым входом блока, выходы блока ключей являются выходами группы блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ | 2000 |

|

RU2187887C2 |

| Устройство для приема дискретной информации | 1982 |

|

SU1030829A2 |

| Станция локальной сети | 1987 |

|

SU1478221A1 |

| Телеметрическая система со сжатием информации | 1991 |

|

SU1837349A1 |

| Устройство для приема информации | 1983 |

|

SU1140145A1 |

| Устройство для сопряжения вычислительной машины с каналом связи | 1985 |

|

SU1291994A1 |

| Устройство цикловой синхронизации воспроизведения цифровой информации с носителя магнитной записи | 1989 |

|

SU1599895A1 |

| Устройство для записи цифровой информации на магнитный носитель | 1978 |

|

SU711619A1 |

| Имитатор абонентов | 1983 |

|

SU1291987A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

Изобретение относится к электросвязи. Цель изобретения - повышение достоверности приема. Устройство содержит приемник 1, селектор 2 единиц, селектор 3 нулей, элементы ИЛИ 4, 12, 13, элементы И 5, 10, 14, 15, элемент ИЛИ-НЕ 11, элемент НЕ 20, регистры сдвига 6, 8, 16, триггеры 7, 19, дешифратор 9, хронизатор 17, блок 18 проверки кадров и блок 21 управления. Устройство позволяет производить прием кодовых посылок (кадров), имеющих в начале и в конце маркерные комбинации. В поле данных этих кадров могут быть выявлены фиктивные нулевые биты (биты "прозрачности") для исключения комбинаций, подобных маркерной. Устройство непрерывно следит за появлением указанных комбинаций. После выявления маркера в начале кадра начинается прием его рабочих данных. Эта часть данных в виде информационных слов переписывается в память ЭВМ с помощью соответствующих сигналов управления. При выявлении битов "прозрачности" устройство исключает их из дальнейшей обработки. Принимаемые данные подвергаются делению на образующий полином. Если полученный остаток от деления сравнится с проверочной последовательностью, поступающей вслед за данными, и в конце кадра обнаружится маркер, то на выходе устройства сформируется управляющий сигнал. По данному сигналу разрешается ЭВМ производить дальнейшую обработку принятой информации. 1 з.п. ф-лы, 4 ил.

21

27

23 23

ВДт

| Дискретное устройство синхронизации | 1979 |

|

SU786034A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1990-03-15—Публикация

1988-06-14—Подача