Изобретение относится к измерительной технике и может быть использовано в системах ввода аналоговых данных устройств цифровой обработки сигналов.

Целью изобретения является повышение быстродействия.

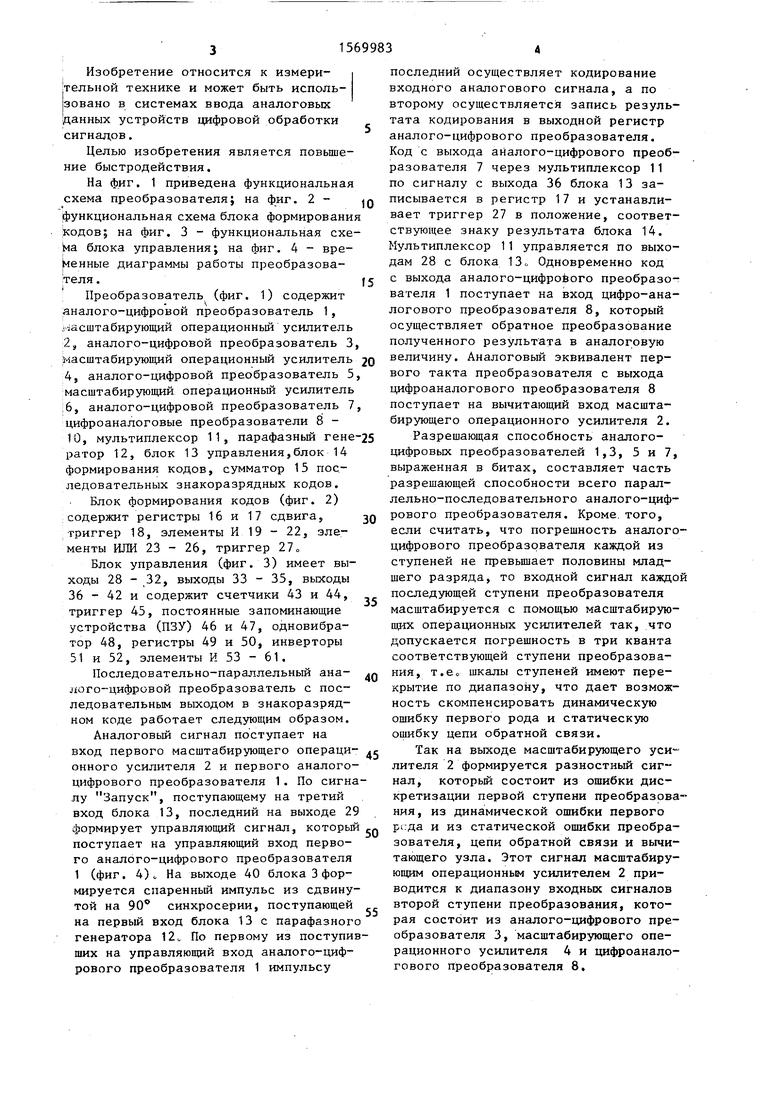

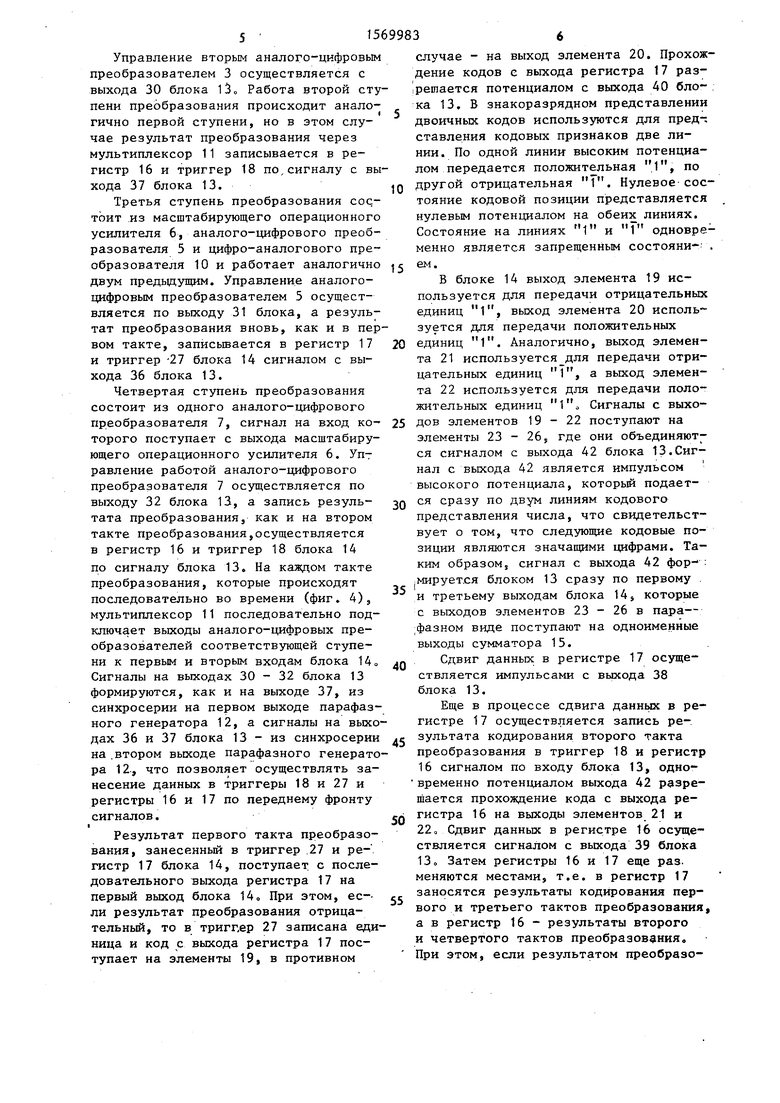

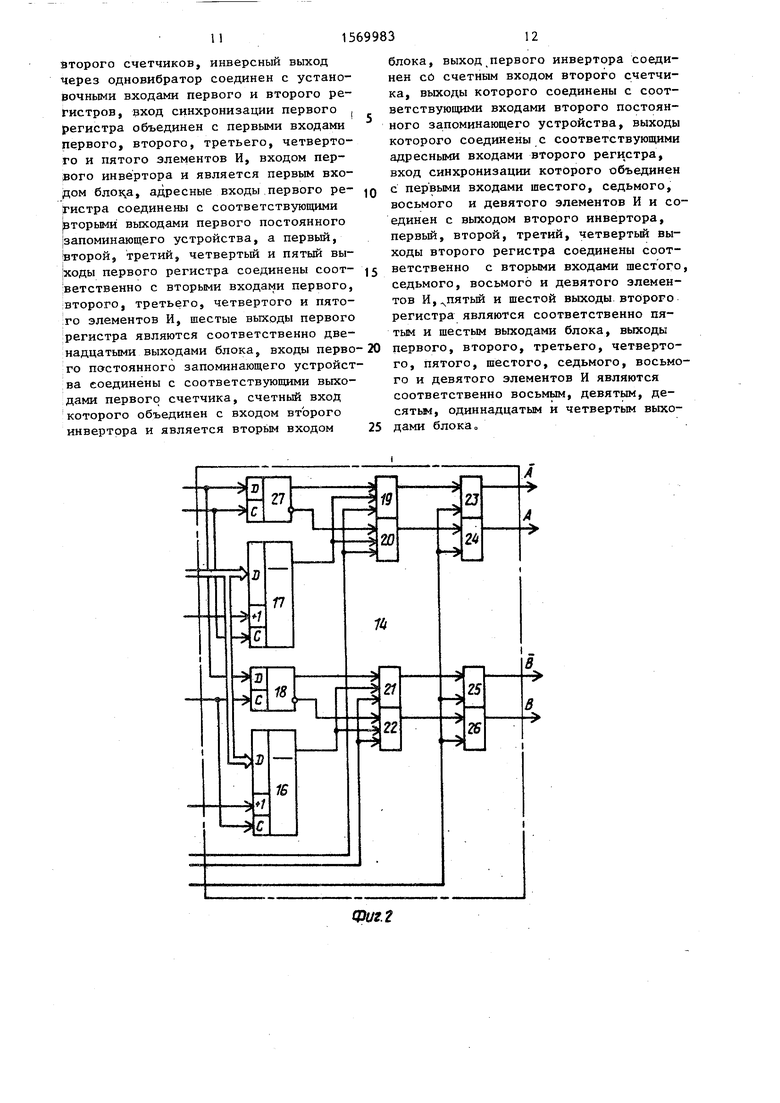

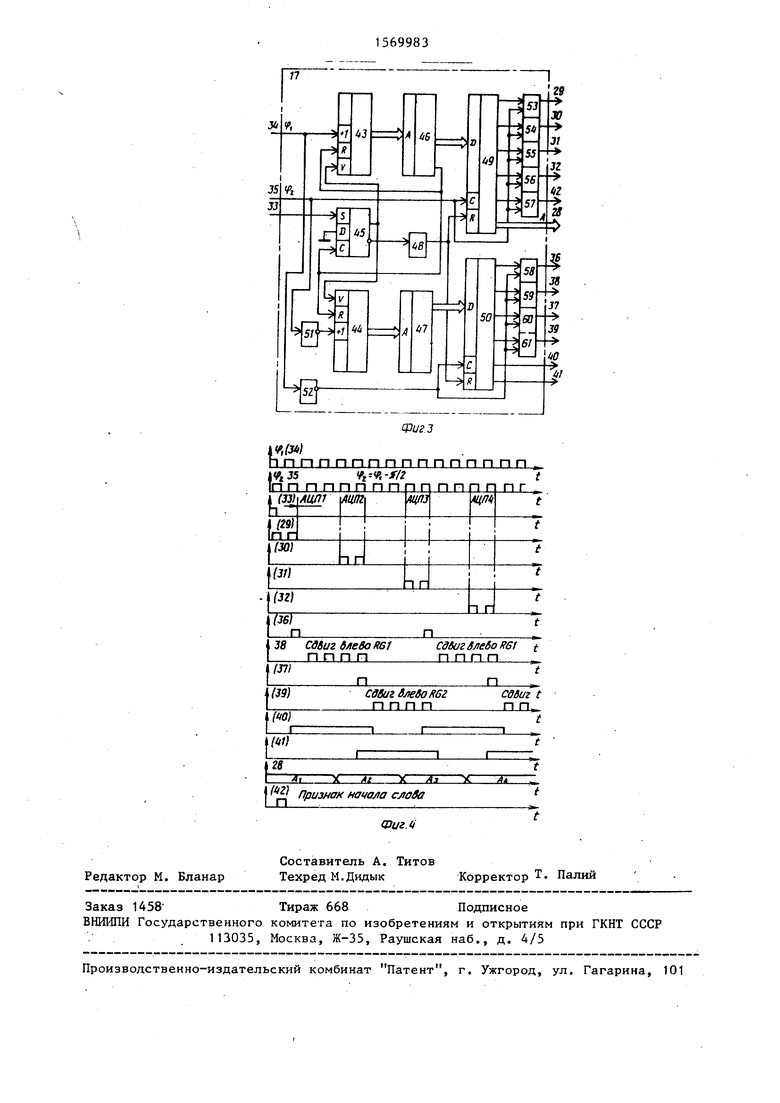

На фиг. 1 приведена функциональная схема преобразователя; на фиг. 2 - функциональная схема блока формирования кодов; на фиг. 3 - функциональная схема блока управления; на фиг. 4 - вре- йенные диаграммы работы преобразователя.

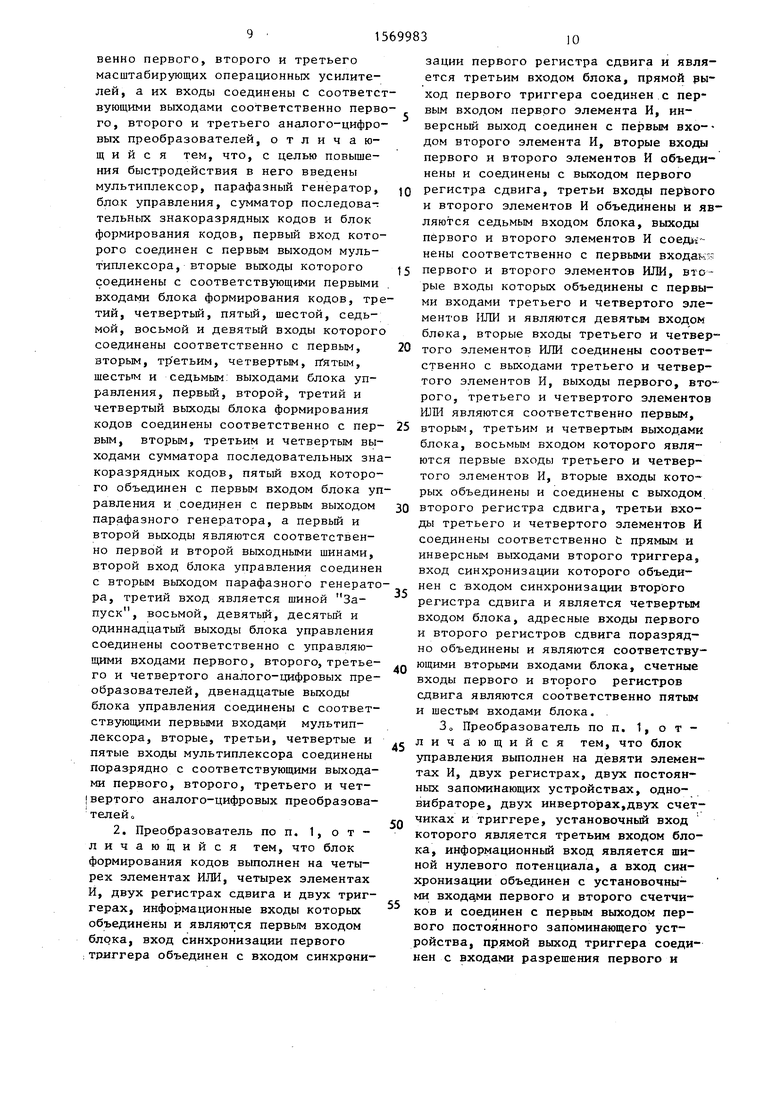

Преобразователь (фиг. 1) содержит аналого-цифровой преобразователь 1, масштабирующий операционный усилитель 2, аналого-цифровой преобразователь 3, масштабирующий операционный усилитель 4, аналого-цифровой преобразователь 5, масштабирующий операционный усилитель 6, аналого-цифровой преобразователь 7, цифроаналоговые преобразователи 8 - 10, мультиплексор 11, парафазный гене ратор 12, блок 13 управления,блок 14 формирования кодов, сумматор 15 последовательных знакоразрядных кодов. Блок формирования кодов (фиг. 2) содержит регистры 16 и 17 сдвига, триггер 18, элементы И 19 - 22, элементы ИЛИ 23 - 26, триггер 27 о

Блок управления (фиг. 3) имеет выходы 28 - 32, выходы 33 - 35, выходы 36 - 42 и содержит счетчики 43 и 44, триггер 45, постоянные запоминающие устройства (ПЗУ) 46 и 47, одновибра- тор 48, регистры 49 и 50, инверторы 51 и 52, элементы И 53 - 61.

Последовательно-параллельный аналого-цифровой преобразователь с последовательным выходом в знакоразряд- ном коде работает следующим образом.

Аналоговый сигнал поступает на вход первого масштабирующего операци- онного усилителя 2 и первого аналого- цифрового преобразователя 1. По сигналу Запуск, поступающему на третий вход блока 13, последний на выходе 29 о ормирует управляющий сигнал, который поступает на управляющий вход первого аналого-цифрового преобразователя 1 (фиг. 4)о На выходе 40 блока 3 формируется спаренный импульс из сдвинутой на 90° синхросерии, поступающей на первый вход блока 13 с парафазного генератора 12„ По первому из поступивших на управляющий вход аналого-цифрового преобразователя 1 импульсу

0

S

0 5

,0

5

40

55

последний осуществляет кодирование входного аналогового сигнала, а по второму осуществляется запись результата кодирования в выходной регистр аналого-цифрового преобразователя. Код с выхода аналого-цифрового преобразователя 7 через мультиплексор 11 по сигналу с выхода 36 блока 13 записывается в регистр 17 и устанавливает триггер 27 в положение, соответствующее знаку результата блока 14. Мультиплексор 11 управляется по выходам 28 с блока 13 о Одновременно код с выхода аналого-цифрового преобразователя 1 поступает на вход цифро-аналогового преобразователя 8, который осуществляет обратное преобразование полученного результата в аналоговую величину. Аналоговый эквивалент первого такта преобразователя с выхода цифроаналогового преобразователя 8 поступает на вычитающий вход масштабирующего операционного усилителя 2.

Разрешающая способность аналого- цифровых преобразователей 1,3, 5 и 7, выраженная в битах, составляет часть разрешающей способности всего параллельно-последовательного аналого-цифрового преобразователя. Кроме того, если считать, что погрешность аналого- цифрового преобразователя каждой из ступеней не превышает половины младшего разряда, то входной сигнал каждой последующей ступени преобразователя масштабируется с помощью масштабирующих операционных усилителей так, что допускается погрешность в три кванта соответствующей ступени преобразования, т.е, шкалы ступеней имеют перекрытие по диапазону, что дает возможность скомпенсировать динамическую ошибку первого рода и статическую ошибку цепи обратной связи.

Так на выходе масштабирующего усилителя 2 формируется разностный сигнал, которьй состоит из ошибки дискретизации первой ступени преобразования , из динамической ошибки первого р. да и из статической ошибки преобразователя, цепи обратной связи и вычитающего узла. Этот сигнал масштабирующим операционным усилителем 2 приводится к диапазону входных сигналов второй ступени преобразования, которая состоит из аналого-цифрового преобразователя 3, масштабирующего операционного усилителя 4 и цифроаналогового преобразователя 8,

515699836

Управление вторым аналого-цифровым случае - на выход элемента 20. Прохож- преобразователем 3 осуществляется с дение кодов с выхода регистра 17 разрешается потенциалом с выхода 40 блока 13. В знакоразрядном представлении двоичных кодов используются для представления кодовых признаков две ливыхода 30 блока 13« Работа второй ступени преобразования происходит аналогично первой ступени, но в этом случае результат преобразования через мультиплексор 11 записывается в регистр 16 и триггер 18 по сигналу с выхода 37 блока 13.JQ

Третья ступень преобразования состоит из масштабирующего операционного усилителя 6, аналого-цифрового преобразователя 5 н цифро-аналогового прении. По одной линии высоким потенциалом передается положительная другой отрицательная 1.

1

по

Нулевое состояние кодовой позиции представляется нулевым потенциалом на обеих линиях. Состояние на линиях 1 и одновременно является запрещенным состояни- . образователя 10 и работает аналогично ем.

двум предыдущим. Управление аналоге- В блоке 14 выход элемента 19 ис- цифровым преобразователем 5 осуществляется по выходу 31 блока, а результат преобразования вновь, как и в первом такте, записывается в регистр 17 и триггер 27 блока 14 сигналом с выхода 36 блока 13.

Четвертая ступень преобразования состоит из одного аналого-цифрового преобразователя 7, сигнал на вход ко- 25 Д°в элементов 19-22 поступают на торого поступает с выхода масштабиру- элементы 23 - 26, где они объединяют- ющего операционного усилителя 6. Управление работой аналого-цифрового преобразователя 7 осуществляется по выходу 32 блока 13, а запись результата преобразования, как и на втором такте преобразования,осуществляется

пользуется для передачи отрицательных единиц 1, выход элемента 20 исполь зуется для передачи положительных 20 единиц 1. Аналогично, выход элемента 21 используется для передачи отрицательных единиц Т, а выход элемента 22 используется для передачи поло- 111 о Сигналы с выхожительных единиц

ся сигналом с выхода 42 блока .Сигнал с выхода 42 является импульсом высокого потенциала, который подает- 3Q ся сразу по двум линиям кодового

представления числа, что свидетельствует о том, что следующие кодовые позиции являются значащими цифрами. Таким образомs сигнал с выхода 42 фор-1 мируется блоком 13 сразу по первому

в регистр 16 и триггер 18 блока 14 по сигналу блока 13. На каждом такте преобразования, которые происходят

представления числа, что свидетельст вует о том, что следующие кодовые по зиции являются значащими цифрами. Та ким образомs сигнал с выхода 42 фор-1 мируется блоком 13 сразу по первому

эс i -- - .-.

последовательно во времени (фиг. 4), и третьему выходам блока 14S которые мультиплексор 11 последовательно под- с выходов элементов 23 - 26 в пара-

нии. По одной линии высоким потенциалом передается положительная другой отрицательная 1.

1

по

Нулевое сос тояние кодовой позиции представляется нулевым потенциалом на обеих линиях. Состояние на линиях 1 и одновре менно является запрещенным состояни- ем.

В блоке 14 выход элемента 19 ис-

Д°в элементов 19-22 поступают на элементы 23 - 26, где они объединяют-

пользуется для передачи отрицательных единиц 1, выход элемента 20 исполь зуется для передачи положительных единиц 1. Аналогично, выход элемента 21 используется для передачи отрицательных единиц Т, а выход элемента 22 используется для передачи поло- 111 о Сигналы с выхожительных единиц

Д°в элементов 19-22 поступают на элементы 23 - 26, где они объединяют-

ся сигналом с выхода 42 блока .Сигнал с выхода 42 является импульсом высокого потенциала, который подает- ся сразу по двум линиям кодового

представления числа, что свидетельствует о том, что следующие кодовые позиции являются значащими цифрами. Таким образомs сигнал с выхода 42 фор-1 мируется блоком 13 сразу по первому

i -- - .-.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ УГЛОВЫХ ПЕРЕМЕЩЕНИЙ | 1999 |

|

RU2178868C2 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1547062A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1988 |

|

SU1594699A1 |

| Устройство для регистрации информации | 1985 |

|

SU1304170A1 |

| Параллельно-последовательный п-разрядный аналого-цифровой преобразователь с автоматической коррекцией функции преобразования | 1988 |

|

SU1732471A1 |

| Устройство для измерения линейных перемещений | 1991 |

|

SU1827527A1 |

| Устройство для синусно-косинусного преобразования кода в напяжение | 1982 |

|

SU1089588A1 |

| Устройство для аналого-цифрового преобразователя | 1988 |

|

SU1594687A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| АНАЛОГО-ЦИФРОВАЯ МНОГОПРОЦЕССОРНАЯ СИСТЕМА | 2006 |

|

RU2333533C1 |

Изобретение относится к измерительной технике и может быть использовано в системах ввода аналоговых данных устройств цифровой обработки сигналов. Изобретение позволяет повысить быстродействие. Это достигается тем, что преобразователь содержит масштабирующие операционные усилители 2, 4, 6, аналого-цифровые преобразователи 1, 3, 5, 7, цифроаналоговые преобразователи 8, 9, 10, мультиплексор 11, блок 14 формирования кодов, блок 13 управления, парафазный генератор 12 и сумматор 15. Преобразователь осуществляет преобразования входного аналогового сигнала в последовательный знакоразрядный код по параллельно-последовательному алгоритму с коррекцией результата. При этом совмещаются во времени процедуры кодирования и чтения данных за счет свойства знакоразрядных кодов осуществлять алгебраическое сложение старшими разрядами вперед. Сочетание процедур кодирования и чтения во времени позволяет сократить в 1,5 раза время обращения к аналого-цифровому преобразователю при одноразовом кодировании. 2 з.п. ф-лы, 4 ил.

ключает выходы аналого-цифровых преобразователей соответствующей ступени к первым и вторым входам блока 14 о Сигналы на выходах 30 - 32 блока 13 формируются, как и на выходе 37, из синхросерии на первом выходе парафазЕще в процессе сдвига данных в регистре 17 осуществляется запись реного генератора 12, а сигналы на выходах 36 и 37 блока 13 - из синхросерии лс зультата кодирования второго такта на втором выходе парафазного генерато- преобразования в триггер 18 и регистр ра 12, что позволяет осуществлять занесение данных в триггеры 18 и 27 и регистры 16 и 17 по переднему фронту

16 сигналом по входу блока 13, одновременно потенциалом выхода 42 разрешается прохождение кода с выхода регистра 16 на выходы элементов 21 и 22о Сдвиг данных в регистре 16 осуществляется сигналом с выхода 39 блока 13 о Затем регистры 16 и 17 еще раз меняются местами, т.е. в регистр 17 заносятся результаты кодирования первого и третьего тактов преобразования, а в регистр 16 - результаты второго и четвертого тактов преобразования. При этом, если результатом преобразосигналов.

i

Результат первого такта преобразования, занесенньй в триггер 27 и регистр 17 блока 14, поступает с последовательного выхода регистра 17 на первый выход блока 14 При этом, если результат преобразования отрицательный, то в триггер 27 записана единица и код с выхода регистра 17 поступает на элементы 19, в противном

фазном виде поступают на одноименные выходы сумматора 15.

Сдвиг данных в регистре 17 осуществляется импульсами с выхода 38 блока 13.

Еще в процессе сдвига данных в регистре 17 осуществляется запись результата кодирования второго такта преобразования в триггер 18 и регистр

лс зультата кодирования второго такта преобразования в триггер 18 и регистр

0

5

16 сигналом по входу блока 13, одновременно потенциалом выхода 42 разрешается прохождение кода с выхода регистра 16 на выходы элементов 21 и 22о Сдвиг данных в регистре 16 осуществляется сигналом с выхода 39 блока 13 о Затем регистры 16 и 17 еще раз меняются местами, т.е. в регистр 17 заносятся результаты кодирования первого и третьего тактов преобразования, а в регистр 16 - результаты второго и четвертого тактов преобразования. При этом, если результатом преобразования есть положительное число, то оно в последовательном коде появляется на первом и третьем выходах блока 14, а если результатом преобразования есть отрицательное число, то оно появляется на втором или четвертом выходах блока 14. Знаковый разряд не передается, а началу передачи предшествует посылка сигнала с выхода 42 блока 13 по всем выходам блока 14. Таким образом, если результатом первого преобразования является, например, число H1d did3d4d5, второго - число ,Ь1ЬгЬэЬ4Ь5-5 третьего - число j С ,, С7С3С4С 5, четвертого - число D 3H1d,d d3d4d5-s то на выходах Злока 14 появляются следующие кодовые лоследовательности:

его первом выходе, которым осуществля- А T d d djd dj-OOO С, СгС3С4С50000; ется сброс триггера 45, счетчиков 43

D T40000 b b bsOOO dfd d3d4d

Соответственно единичные позиции чисел A,B,C,D поступают на соответстзууощие выходы блока 14 в зависимости от значений знаковых разрядов в числах А,В,С и т.д.

Сформированные кодовые последовательности А и В по одноименным пара- фазным линиям с выхода блока 14 поступают на вход сумматора 15, в котором происходит суммирование чисел А и В старшими разрядами вперед. Логика работы последовательного сумматора 15 выше. В качестве последовательного сумматора знакоразрядных кодов может быть использована микросхема К1815ВФЗ. Результат сложения является окончательным результатом преоб- азования параллельно-последовательного аналого-цифрового преобразовате- пя.

Выработка всех сигналов управления л синхронизации параллельно-последо- вательного аналого-цифрового преобразователя осуществляется блоком 13 из синхросерии парафазного генератора 12.

Блок 17 управления работает следующим образом. Сдвинутые друг относи- тельн.о друга на 90е тактовые серии Ц, i/4 постоянно поступают на входы 34 и 35 блока 13 от парафазного генератора 12, Сигналом Запуск устанавливается в единичное состояние триггер 45, с выхода которого разрешается заполнение счетчиков 43 и 44 соответствующими тактовыми импульсами. Счетчики,

заполняясь, формируют адреса на входах постоянных запоминающих устройств 46 и 47. Сосчитанные из ПЗУ слова данных записываются в регистры 49 и 50 0 Для исключения влияния эффекта гонок используется двухтактная схема синхронизации устройства. Элементы 53-61 стробируются синхроимпульсом для обеспечения- длительности выходных сигналов не более длительности строба. Постоянное запоминающее устройство 46 генерирует сигналы, стробируемые син- хросерией (f , постоянное запоминающее устройство 47 генерирует сигналы, стробируемые синхросерией д .

При чтении из постоянного запоминающего устройства 46 последнего управляющего слова появляется сигнал на

и 44 через одновибратор 48 регистров 49 и 50„ Схема приходит в исходное состояние до прихода следующего импульса Запуск по входу 33.

Формула изобретения

5

0

5

0

5

0

5

0

5

зации первого регистра сдвига и является третьим входом блока, прямой эы- ход первого триггера соединен с первым входом первого элемента И, инверсный выход соединен с первым вхо-- дом второго элемента И, вторые входы первого и второго элементов И объединены и соединены с выходом первого регистра сдвига, третьи входы первого и второго элементов И объединены и являются седьмым входом блока, выходы первого и второго элементов И соединены соответственно с первыми входаь первого и второго элементов ИЛИ, вторые входы которых объединены с первыми входами третьего и четвертого элементов ИЛИ и являются девятым входом блока, вторые входы третьего и четвертого элементов ИЛИ соединены соответственно с выходами третьего и четвертого элементов И, выходы первого, второго, третьего и четвертого элементов ИЛИ являются соответственно первым, вторым, третьим и четвертым выходами блока, восьмым входом которого являются первые входы третьего и четвертого элементов И, вторые входы которых объединены и соединены с выходом второго регистра сдвига, третьи входы третьего и четвертого элементов И соединены соответственно с прямым и инверсным выходами второго триггера, вход синхронизации которого объединен с входом синхронизации второго регистра сдвига и является четвертым входом блока, адресные входы первого и второго регистров сдвига поразрядно объединены и являются соответствующими вторыми входами блока, счетные входы первого и второго регистров сдвига являются соответственно пятым и шестым входами блока.

3 Преобразователь по п. отличающийся тем, что блок управления выполнен на девяти элементах И, двух регистрах, двух постоянных запоминающих устройствах, одно- вибраторе, двух инверторах,двух счетчиках и триггере, установочный вход которого является третьим входом блока, информационный вход является шиной нулевого потенциала, а вход синхронизации объединен с установочными входа,ми первого и второго счетчиков и соединен с первым выходом первого постоянного запоминающего устройства, прямой выход триггера соединен с входами разрешения первого и

второго счетчиков, инверсный выход через одновибратор соединен с установочными входами первого и второго регистров, вход синхронизации первого ( регистра объединен с первыми входами первого, второго, третьего, четвертого и пятого элементов И, входом первого инвертора и является первым входом блок.3, адресные входы первого регистра соединены с соответствующими вторыми выходами первого постоянного запоминающего устройства, а первый, второй, третий, четвертый и пятый выходы первого регистра соединены соответственно с вторыми входами первого, второго, третьего, четвертого и пятого элементов И, шестые выходы первого регистра являются соответственно двенадцатыми выходами блока, входы перво го постоянного запоминающего устройст ва соединены с соответствующими выходами первого счетчика, счетный вход которого объединен с входом второго инвертора и является вторым входом

10

блока, выход первого инвертора соединен ей счетным входом второго счетчика, выходы которого соединены с соответствующими входами второго постоянного запоминающего устройства, выходы которого соединены с соответствующими адресными входами второго регистра, вход синхронизации которого объединен с первыми входами шестого, седьмого, восьмого и девятого элементов И и соединен с выходом второго инвертора, первый, второй, третий, четвертый выходы второго регистра соединены соответственно с вторыми входами шестого, седьмого, восьмого и девятого элементов И, „.пятый и шестой выходы второго регистра являются соответственно пятым и шестым выходами блока, выходы первого, второго, третьего, четвертого, пятого, шестого, седьмого, восьмого и девятого элементов И являются соответственно восьмым, девятым, десятым, одиннадцатым и четвертым выхо- 25 дами блока

15

20

Фиг.2

ЪМ

Ш h n

ПППППППППППППП

| Состав пенообразователя для тушения пожаров | 1980 |

|

SU899046A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аналого-цифровые преобразователи | |||

| - М0: Советское радио, 1980 , с | |||

| Мяльно-трепальный станок для обработки тресты лубовых растений | 1922 |

|

SU200A1 |

Авторы

Даты

1990-06-07—Публикация

1988-07-15—Подача