Изобретение относится к области импульсной техники и может быть использовано в устройствах вычислительной техники и систем управления.

Известен троичный триггер (см. авторское свидетельство СССР №1317654, МКИ: Н 03 К 3/29, “Троичный триггер Богдановича”, Богданович М.И., опубл. 15.06.87, Бюл. №22), содержащий три входа, два выхода, четыре резистора, два диода и четыре транзистора первого типа проводимости, эмиттеры которых подключены к общей шине, пятый и шестой транзисторы второго типа проводимости, базы и коллекторы которых подключены соответственно к коллекторам и базам первого и второго транзисторов. Коллекторы первого и второго транзисторов подключены соответственно к первому и второму выходам триггера и соответственно через первый и второй резисторы соединены с шиной питания. Анод первого диода соединен с первым входом, катод диода соединен с базой первого транзистора, коллектор третьего транзистора соединен с первым выводом третьего резистора. Анод второго диода подключен ко второму входу, катод - к базе второго транзистора, а второй вывод третьего резистора соединен со вторым выходом триггера. Базы третьего и четвертого транзисторов соединены с третьим входом устройства, а коллекторы подключены к эмиттерам соответственно пятого и шестого транзисторов. Коллектор первого транзистора через четвертый резистор подключен к эмиттеру шестого транзистора.

Недостатком указанного троичного триггера является низкая помехоустойчивость.

Известен троичный триггер (см. авторское свидетельство СССР №1753921 от 05.10.90, МКИ Н 03 К 3/29, Троичный триггер, Егоров Л.Б., Шишкин Г.И., опубл. 10.09.97, Бюл. №25), содержащий первую входную шину, подключенную к первому диоду, первый n-р-n транзистор, эмиттер которого соединен с общей шиной, коллектор - с первой выходной шиной и через первый резистор - с шиной питания, база первого n-р-n транзистора соединена с коллектором первого р-n-р транзистора, эмиттер которого через последовательно соединенные третий и второй резисторы подключены к шине питания, база - к первому выводу четвертого резистора, второй n-р-n транзистор, коллектор которого соединен с базой второго р-n-р транзистора, коллектор которого подключен к катоду второго диода, анод которого соединен со второй входной шиной, и вторую выходную шину. Устройство также содержит четыре резистора и конденсатор, включенный между вторым выводом четвертого резистора и общей шиной. Эмиттер второго n-р-n транзистора подключен к точке соединения второго и третьего резисторов, база - к базе первого р-n-р транзистора, эмиттер которого через пятый резистор соединен с общей шиной. Эмиттер второго р-n-p транзистора подключен к шине питания, коллектор - ко второй выходной шине, через шестой резистор - к общей шине и через последовательно соединенные седьмой и восьмой резисторы - к первой выходной шине и аноду первого диода, катод которого подключен к первой входной шине. Точки соединения четвертого резистора и конденсатора и седьмого и восьмого резисторов объединены.

Троичный триггер является наиболее близким по технической сущности к заявленному устройству и взят в качестве прототипа.

Недостатком прототипа является невозможность работы в счетном режиме.

Задачей, решаемой предлагаемым изобретением, является расширение функциональных возможностей троичного триггера, получившего возможность работы в счетном режиме.

Технический результат достигается тем, что в троичный триггер, содержащий первую и вторую входные шины, подключенные к катоду первого диода и аноду второго диода соответственно, анод первого диода соединен с первой выходной шиной, с первыми выводами первого и второго резисторов и с коллектором первого n-р-n транзистора, эмиттер которого соединен с первым выводом конденсатора, первыми выводами третьего, четвертого резисторов и с общей шиной, второй вывод четвертого резистора соединен с катодом второго диода, со второй выходной шиной, с коллектором первого р-n-р транзистора и через пятый резистор - со вторым выводом первого резистора и с первым выводом шестого резистора, второй вывод которого подключен к базам вторых n-р-n и р-n-р транзисторов соответственно, эмиттеры которых соединены с первым и вторым выводами восьмого и третьего резисторов соответственно и между собой соединены через седьмой резистор, второй вывод восьмого резистора соединен с эмиттером первого р-n-р транзистора, со вторым выводом второго резистора и с шиной питания, базы первых р-n-р и n-р-n транзисторов соединены с коллекторами вторых n-р-n и р-n-р транзисторов соответственно, дополнительно введены мультиплексор, выполненный по КМОП-технологии, девятый и десятый резисторы, инвертор и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй входы которого соединены с первой и второй выходными шинами соответственно, а выход через десятый резистор подключен к первому выводу девятого резистора и к первому входу мультиплексора, второй вход которого соединен с первым выводом шестого резистора, вход управления мультиплексора подключен к счетной шине, а выход - ко второму выводу конденсатора, второй вывод девятого резистора соединен с выходом инвертора, вход которого соединен со второй выходной шиной.

Указанная совокупность признаков позволяет упростить троичный триггер.

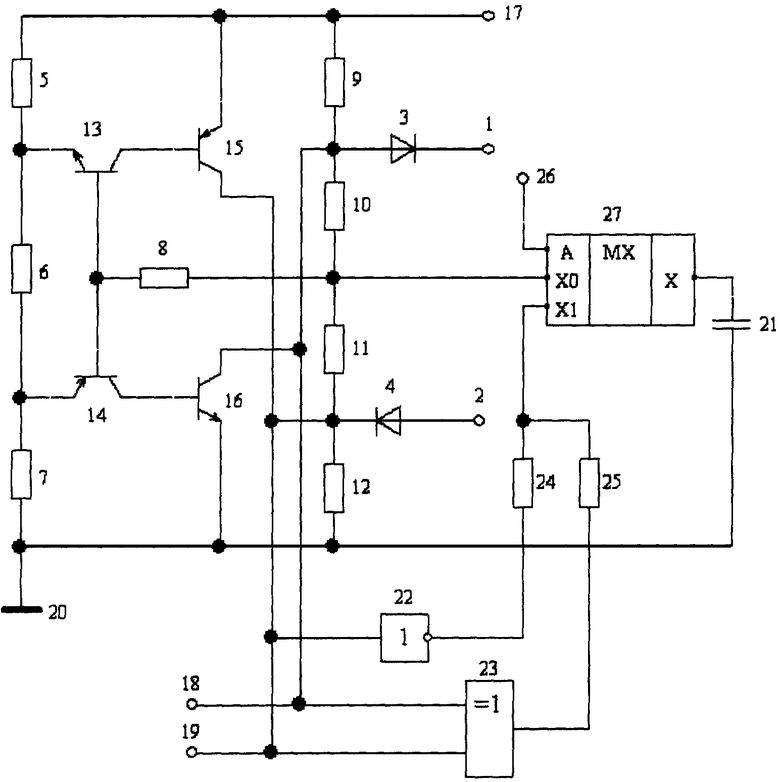

Принципиальная схема троичного триггера приведена на чертеже.

Троичный триггер содержит две входные шины 1, 2, два диода 3,4, десять резисторов 5, 6, 7, 8, 9, 10, 11, 12, 24, 25, два n-p-n транзистора 13 и 16, два р-n-р транзистора 14 и 15, шину питания 17, две выходные шины 18, 19, общую шину 20, конденсатор 21, инвертор 22, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 23, счетную шину 26 и мультиплексор 27, выполненный по КМОП-технологии.

Входная шина 1 соединена с катодом диода 3, анод которого соединен с первыми выводами резисторов 9, 10, с коллектором транзистора 16, с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 23 и с выходной шиной 18. Входная шина 2 соединена с анодом диода 4, катод которого соединен с первыми выводами резисторов 11, 12, с коллектором транзистора 15, с входом инвертора 22, со вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 23 и с выходной шиной 19. Шина питания 17 соединена со вторыми выводами резисторов 9, 5 и с эмиттером транзистора 15, база которого подключена к коллектору транзистора 13. Эмиттер транзистора 13 соединен с первыми выводами резисторов 5 и 6, база - с первым выводом резистора 8 и с базой транзистора 14. Эмиттер транзистора 14 подключен ко вторым выводам резисторов 6 и 7, коллектор - к базе транзистора 16, эмиттер которого соединен с первыми выводами резистора 7 и конденсатора 21, со вторым выводом резистора 12 и с общей шиной 20. Второй вывод резистора 8 соединен со вторыми выводами резисторов 10, 11 и с первым входом мультиплексора 27, выход которого подключен ко второму выводу конденсатора 21. Вход управления мультиплексора 27 соединен со счетной шиной 26, второй вход - с первыми выводами резисторов 24 и 25, вторые выводы которых соединены соответственно с выходом инвертора 22 и с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 23.

Троичный триггер работает следующим образом.

Троичный триггер имеет три устойчивых состояния:

- конденсатор 21 разряжен, при этом транзисторы 16, 14 открыты, транзисторы 13, 15 закрыты, на выходных шинах 18, 19 присутствуют уровни логического “0” (состояние “00”);

- конденсатор 21 заряжен до напряжения, равного примерно половине напряжения питания, транзисторы 13, 14, 15, 16 закрыты, на выходных шинах 18, 19 присутствуют уровни логической “1” и логического “0” соответственно (состояние “10”);

- конденсатор 21 заряжен до напряжения питания, транзисторы 14, 16 закрыты, транзисторы 13, 15 открыты, а на выходных шинах 18, 19 присутствуют уровни логической “1” (состояние “11”).

При наличии уровня логической “1” на выходных шинах 18, 19 присутствует напряжение, практически равное напряжению питания, а при наличии уровня логического “0” - практически равное нулю.

Пороги открывания транзисторов 13 и 14 определяются соотношением сопротивлений делителя напряжения, образованного резисторами 5, 6, 7. При этом порог открывания транзистора 13 равен  а порог открывания транзистора 14 равен

а порог открывания транзистора 14 равен  , где Е - напряжение питания на шине питания 17, Uбэ - падение напряжения на переходе база-эмиттер транзисторов 13, 14.

, где Е - напряжение питания на шине питания 17, Uбэ - падение напряжения на переходе база-эмиттер транзисторов 13, 14.

При подаче питания на шину питания 17 на входной шине 1 присутствует уровень логической “1” (уровень напряжения питания), а на входной шине 2 и на счетной шине 26 - уровень логического “0”. Диоды 3 и 4 смещены в обратном направлении, поэтому состояния на входных шинах 1 и 2 не влияют на уровни напряжения на выходных шинах 18 и 19. Конденсатор 21 разряжен и, поскольку на счетной шине 26 присутствует уровень логического “0”, подключен через мультиплексор 27 к резистору 8. Транзистор 14 открывается током заряда конденсатора 21, протекающим через резистор 8 и мультиплексор 27. Транзистор 16 открывается током коллектора транзистора 14, а транзисторы 13 и 15 закрыты. Устройство устанавливается в состояние “00”. При наличии уровня логической “1” на входной шине 1 и уровня логического “0” на входной шине 2 и счетной шине 26 устройство находится в режиме хранения информации. Ток коллектора транзистора 16 определяется сопротивлением резистора 9, а ток базы транзистора 14 - сопротивлением резисторов 8, 10, 11, 12. Транзистор 16 насыщен, транзистор 14 работает в линейном режиме. Уровни напряжения на конденсаторе 21 и на эмиттере транзистора 14 зависят от коэффициента усиления по току транзистора 14: чем больше коэффициент усиления, тем меньше указанные уровни. На выходе инвертора 22 присутствует уровень логической “1”, а на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 23 - уровень логического “0”. Сопротивления резисторов 24 и 25 равны, поэтому на втором входе мультиплексора 27 присутствует уровень напряжения, равный ≈0,5Е, соответствующий состоянию “10” устройства.

Перевести устройство в состояние “10” можно двумя способами. Первый способ заключается в том, что необходимо подать уровни логического “0” и логической “1” на входные шины 1 и 2 соответственно, а на счетную шину 26 - уровень логического “0”. При этом на выходной шине 18 будет поддерживаться уровень логического “0” независимо от состояния транзистора 16, а на выходной шине 19 установится уровень логической “1”. Конденсатор 21 начнет заряжаться через диод 4, резистор 11 и мультиплексор 27. Напряжение на конденсаторе 21 будет стремится к величине 0,5Е, которое определяется соотношением сопротивлений резисторов 10 и 11, и если за время действия установочных импульсов на входных шинах 1 и 2 оно не достигнет порога открывания транзистора 14, то после окончания установочных импульсов устройство восстановит состояние “00”. Если же за время действия установочных импульсов на входных шинах 1 и 2 напряжение на конденсаторе 21 достигнет порога открывания транзистора 14, то устройство перейдет в состояние “10”.

Для перевода троичного триггера в состояние “10” вторым способом необходимо подать импульс, имеющий уровень логической “1”, на счетную шину 26, после чего конденсатор 21, находящийся в разряженном состоянии, будет подключен ко второму входу мультиплексора 27, на котором присутствует уровень напряжения, равный ≈0,5Е. На входные шины 1 и 2 необходимо подать уровни логической “1” и логического “0” соответственно. Если за время действия импульса на счетной шине 26 напряжение на конденсаторе 21 не достигнет уровня ≈0,5Е, то после окончания импульса на счетной шине 26 устройство восстановит состояние “00”. Если же напряжение на конденсаторе 21 достигнет уровня ≈0,5Е, то троичный триггер перейдет в состояние “10”. После окончания импульса на счетной шине 26 конденсатор 21 подключится к первому входу мультиплексора 27. Напряжение на конденсаторе 21 вызывает закрывание транзистора 14, что приводит к закрыванию транзистора 16, и устройство переходит в режим хранения состояния “10”. На выходе инвертора 22 останется уровень логической “1”, а на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 23 также установится уровень логической “1”. Это приведет к появлению уровня логической “1” на втором входе мультиплексора 27, который соответствует состоянию “11” устройства.

Перевести троичный триггер в состояние “11” также можно двумя способами.

Первый способ заключается в подаче уровня логической “1” на входные шины 1 и 2, сохранив уровень логического “0” на счетной шине 26. При этом на выходных шинах 18 и 19 установятся уровни логической “1”, соответствующие состоянию “11” устройства. Конденсатор 21 начнет заряжаться через диод 4, резистор 11 и мультиплексор 27. Напряжение на конденсаторе 21 начнет нарастать, стремясь к напряжению питания, и если за время действия установочных импульсов на входных шинах 1 и 2 оно не достигнет порога открывания транзистора 13, то после окончания установочных импульсов устройство восстановит состояние “10”. Если же за время действия установочных импульсов на входных шинах 1 и 2 напряжение на конденсаторе 21 достигнет порога открывания транзистора 13, то транзистор 13 откроется. Это приведет к открыванию транзистора 15 и устройство перейдет в состояние “11”.

Для перевода троичного триггера в состояние “11” вторым способом необходимо подать импульс с уровнем логической “1” на счетную шину 26, после чего конденсатор 21 окажется подключенным ко второму входу мультиплексора 27, на котором присутствует уровень напряжения питания. На входные шины 1 и 2 необходимо подать уровни логической “1” и логического “0” соответственно. Если за время действия импульса на счетной шине 26 напряжение на конденсаторе 21 не достигнет уровня напряжения питания, то после окончания импульса на счетной шине 26 устройство восстановит состояние “10”. Если же напряжение на конденсаторе 21 достигнет уровня напряжения питания, то троичный триггер перейдет в состояние “11”. После окончания импульса на счетной шине 26 конденсатор 21 подключается к первому входу мультиплексора 27, что вызывает открывание транзистора 13, а затем и транзистора 15. Устройство переходит в режим хранения состояния “11”. На выходах инвертора 22 и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 23 установятся уровни логического “0”. Это приведет к появлению уровня логического “0” на втором входе мультиплексора 27, который соответствует состоянию “00” устройства.

Дальнейший перевод троичного триггера в состояние “00” происходит аналогичным образом. Следует отметить, что перевод устройства по первому способу (при помощи установочных импульсов на входных шинах 1 и 2) возможен в любое состояние, независимо от предыдущего состояния. Перевод устройства вторым способом (при помощи импульсов на счетной шине 26) возможен только в определенном порядке: из состояния “00” в состояние “10”, далее в состояние “11”, затем в состояние “00”.

Необходимо отметить, что помехоустойчивость заявляемого объекта, по сравнению с прототипом, не изменилась.

Таким образом, заявляемый троичный триггер обладает более широкими по сравнению с прототипом функциональными возможностями, а именно обеспечивает работу в счетном режиме.

В качестве диодов 3, 4 могут быть использованы диоды типа 2Д522, в качестве резисторов 5, 6, 7, 8, 9, 10, 11, 12, 24, 25 - резисторы типа С2-33, в качестве транзисторов 13, 16 - транзисторы 2Т3117, в качестве транзисторов 14, 15 - транзисторы 2Т313, а в качестве конденсатора 21 - конденсатор типа К10-17. Инвертор 22 может быть выполнен на микросхеме 564ЛН2, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ - на микросхеме 564ЛП2, мультиплексор 27 - на микросхеме 564КП2.

Изготовлен лабораторный макет троичного триггера, испытания которого подтвердили осуществимость и практическую ценность заявляемого объекта. Макет был выполнен на микросхемах серии 564.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТРОИЧНЫЙ ТРИГГЕР | 1990 |

|

SU1753921A1 |

| Источник вторичного электропитания для сети постоянного напряжения | 1990 |

|

SU1786476A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ | 2022 |

|

RU2782474C1 |

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1992 |

|

RU2030094C1 |

| СХЕМА ЗАЩИТЫ КЛЮЧЕВОГО ТРАНЗИСТОРА | 2003 |

|

RU2245602C1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ЦИКЛИЧЕСКОЙ ИНВЕРСИИ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ (ВАРИАНТЫ) | 2024 |

|

RU2835664C1 |

| РЕЛЕ ВРЕМЕНИ (С ВЫХОДОМ НА СИМИСТОРЕ) | 1992 |

|

RU2130213C1 |

| ПИКОВЫЙ ДЕТЕКТОР | 2009 |

|

RU2409818C1 |

| Импульсный понижающий стабилизатор постоянного напряжения | 1990 |

|

SU1786477A1 |

| ИМПУЛЬСНЫЙ СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ ПОНИЖАЮЩЕГО ТИПА | 1991 |

|

RU2006062C1 |

Изобретение относится к импульсной технике и может быть использовано в устройствах вычислительной техники и систем управления. Технический результат заключается в получении возможности работы в счетном режиме. Устройство содержит две входные шины (1 и 2), два диода (3 и 4), десять резисторов (5-12, 24 и 25), два n-p-n транзистора (13 и 16), два p-n-p транзистора (14 и 15), шину питания (17), две выходные шины (18 и 19), общую шину (20), конденсатор (21), инвертор (22), элемент ИСКЛЮЧАЮЩЕЕ ИЛИ (23), счетную шину (26) и мультиплексор (27). 1 ил.

Троичный триггер, содержащий первую и вторую входные шины, подключенные к катоду первого диода и аноду второго диода соответственно, анод первого диода соединен с первой выходной шиной, с первыми выводами первого и второго резисторов и с коллектором первого n-p-n транзистора, эмиттер которого соединен с первым выводом конденсатора, первыми выводами третьего, четвертого резисторов и с общей шиной, второй вывод четвертого резистора соединен с катодом второго диода, со второй выходной шиной, с коллектором первого p-n-p транзистора и через пятый резистор - со вторым выводом первого резистора и с первым выводом шестого резистора, второй вывод которого подключен к базам вторых n-p-n и p-n-p транзисторов соответственно, эмиттеры которых соединены с первым и вторым выводами восьмого и третьего резисторов соответственно, и между собой соединены через седьмой резистор, второй вывод восьмого резистора соединен с эмиттером первого p-n-p транзистора, со вторым выводом второго резистора и с шиной питания, базы первых p-n-p и n-p-n транзисторов соединены с коллекторами вторых n-p-n и p-n-p транзисторов соответственно, отличающийся тем, что дополнительно введены мультиплексор, выполненный по КМОП-технологии, девятый и десятый резисторы, инвертор и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй входы которого соединены с первой и второй выходными шинами соответственно, а выход через десятый резистор подключен к первому выводу девятого резистора и к первому входу мультиплексора, второй вход которого соединен с первым выводом шестого резистора, вход управления мультиплексора подключен к счетной шине, а выход - ко второму выводу конденсатора, второй вывод девятого резистора соединен с выходом инвертора, вход которого соединен со второй выходной шиной.

| ТРОИЧНЫЙ ТРИГГЕР | 1990 |

|

SU1753921A1 |

| Троичный триггер Богдановича | 1984 |

|

SU1317654A1 |

| ТРЕХСТАБИЛЬНЫЙ СЧЕТНЫЙ ТРИГГЕР (ВАРИАНТЫ) | 1993 |

|

RU2093955C1 |

| Трехстабильный счетный триггер | 1975 |

|

SU585591A1 |

| US 5391935, 21.02.1995. | |||

Авторы

Даты

2004-10-10—Публикация

2003-04-14—Подача