113544432

Изобретение относится к телевизи-личину -«-U (фиг.2д). Импульсы с вы.онной технике, в частности к телеви-хода второго дифференцирующего блока.

зионной измерительной технике.9, которые имеют противоположную поЦель изобретения - повышение точ-лярность относительно импульсов с выности выделения синхроимпульсов прихода первого дифференцирующего блока

воздействии низкочастотной аддитивной8 (фиг.2г), подаются на неинвертируюпомехи.щий вход четвертого порогового блока

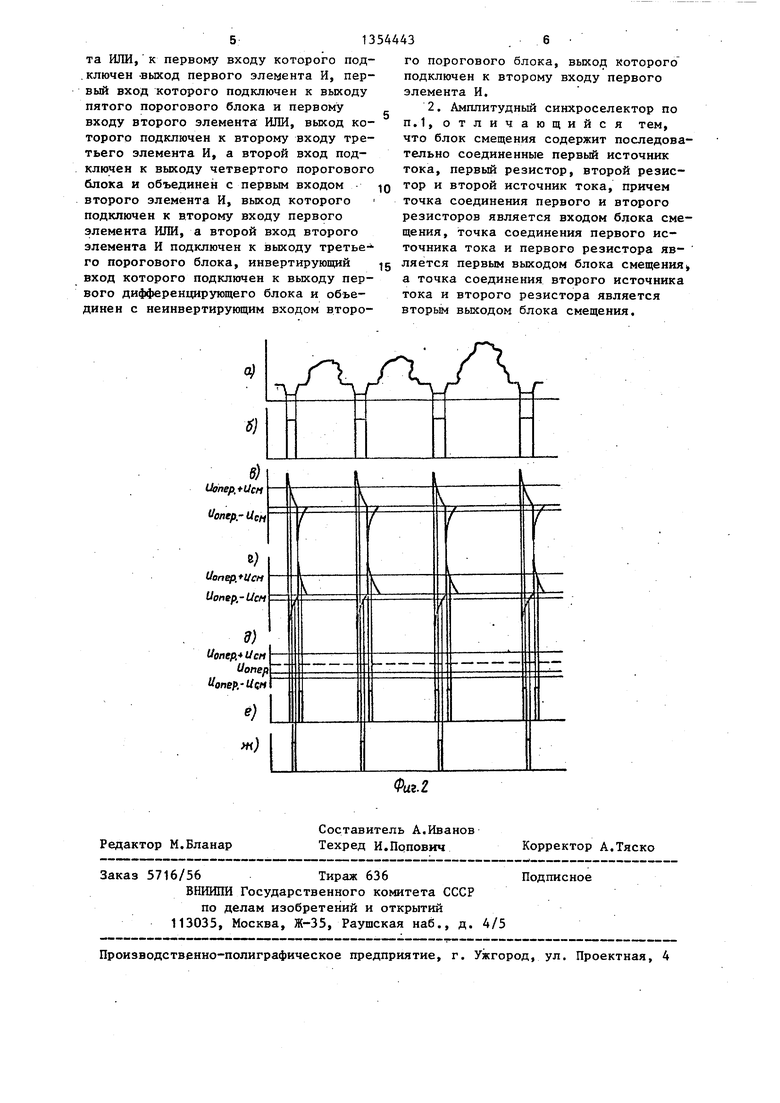

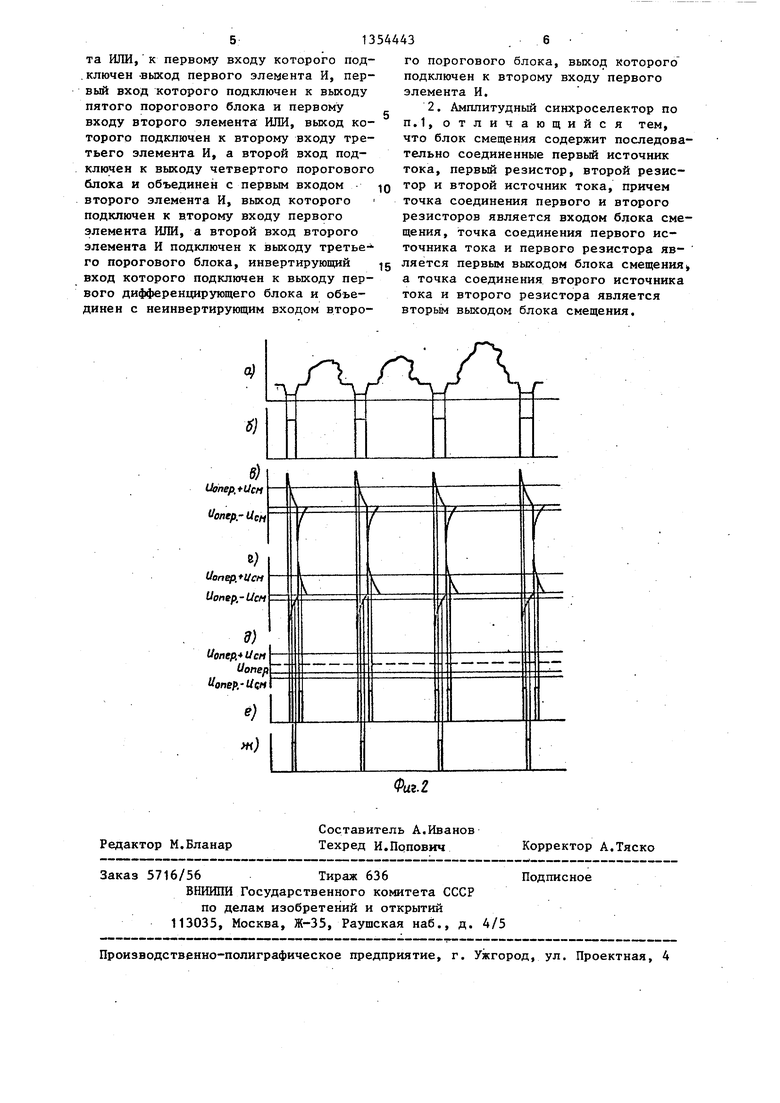

На фиг,1 приведена структурная13 и на инвертирующий вход пятого поэлектрическая схема амплитудного синх-юрогового блока 14, на неинвертирующий

роселектора; на фиг.2 - временныевход которого подается напряжение с

диаграммы, поясняющие работу.выхода операционного усилителя 17,

Амплитудный синхроселектор (фиг.1)смещенное на величину -U, (фиг.2д).

содержит буферньй усилитель 1, первыйНа инвертирующий вход четвертого поконденсатор 2, резистор 3, первьй isрогового блока 13 подается напряжение

ключ 4, источник 5 опорного напряже-с выхода операционного усилителя 17,

кия, первый пороговый блок 6, предва-смещенное на величину +U-., (фиг.2д).

С ЛЛ

рительный синхроселектор 7, два диф- При отсутствии низкочастотной адференцирующих блока 8 и 9, первый ло-дитивной помехи половина размаха

гический инвертор 10, пороговые блоки 2острочных синхроимпульсов на первом

11 - 14, блок 15 смещения, второйвходе порогового блока 6 точно совпаконденсатор 16, операционный усили-дает с напряжением источника 5 опортель 17, второй ключ 18, второй логи-ного напряжения. На выходе операционческий инвертор 19, элементы ИЛИ 20ного усилителя 17 формируется нулевое

и 21, элементы И 22 - 24.25напряжение и длительности всех имБлок 15 смещения содержит первыйпульсов .на выходах пороговых блоков

источник 25 тока, первый 26 и второй11 - 14 равны. Поэтому открьшается

27 резисторы, второй источник 28 тока.только второй ключ 18. При этом заАмплитудньш синхроселектор работа-ряд, накопленный вторым конденсатоет следующим образом. ЗОРОМ 16 во время строчного синхроимВидеосигнал (фиг.2а) подается на .пульса, равен заряду, стекающему с

вход буферного усилителя 1 с малымнего во время гасящего импульса. .За

выходным сопротивлением, что позволя-счет этого напряжение на выходе опеет. исключить влияние импульсов фикса-рационного усилителя 17 не изменяции на входные цепи предварительного ется.

синхроселектора 7. В последнем из ви- При воздействии на видеосигнал

деосигнала вьщеляется синхросмесьнизкочастотной аддитивной помехи за(фиг.2б), которая попадает на входРЯД, накопленный вторым конденсатопервого дифференцирующего блока 8 иром 16, уже не равен заряду, стекаюна вход первого логического инвертора Qщему с него. Напряжение на вькоде

10, где она инвертируется;операционного усилителя 17 начинает

Дифференцирукнцие блоки 8 и 9 выби-изменяться.

раются с равными постоянными времени. Если аддитивная низкочастотная поНа выходе первого дифференцирующегомеха такова, что синхроимпульсы смеблока 8 формируются разнополярные ко- щаются вниз, то на вькоде операционроткие импульсы, соответствующие пе-ного усилителя 17 напряжение увеличиредним и задним фронтам синхроимпуль-вается. Вследствие этого длительность

сов (фиг.2в). Эти импульсы попадаютимпульсов, формируемых вторым порогона неинвертирующий вход второго поро-вын блоком 11 во время прохождения

гового блока 11 и на инвертирующийстрочных синхроимпульсов, уменьшаетвход третьего порогового блока 12,ся, а длительность импульсов, форми-

на неинвертирующий вход которого по-руемых третьим пороговым блоком 12

дается напряжение с выхода операцион-во время прохождения гасящих импульного усилителя 17, смещенное первымсов, увеличивается. В то же время

резистором 26 на величину-U.. (фиг.2д) ,длительность импульсов, формируемых

На инвертирующий вход второго порого-пятым пороговым блоком 14 во время

вого блока 11 подается напряжение спрохождения строчных синхроимпульсов,

выхода операционного усилителя 17-,увеличивается, а длительность импульсмещенное вторым резистором 27 на ве-сов, формируемых четвертым пороговым

3

блоком 13 во время прохождения гасящих импульсов, уменьшается. Выходы пороговых блоков, формирующих импульсы во время прохождения строчных синхроимпульсов, объединены по И первым элементом И 22, а выходы пороговых блоков, формирующих импульсы во время гасящих импульсов, объединены по И с вторым элементом И 23. Поско- льку первьш 8 и второй 9 дифференцирующие блоки имеют одинаковые постоянные времениJ то на выходах элементов И 22 к 23 формируются импульсы

одинаковой длительности во время про- ig также к первому входу первого порогохождения строчных и гасящих импульсов соответственно.

Эти импульсы (фиг.2е) собираются по ИЛИ первым элементом ИЛИ 20 и.открывают второй ключ 18. Эти же им- 20 пульсы через второй логический инвертор 19 запрещают прохождение импульсов с выхода второго элемента ИЖ 21 на управляющий вход первого ключа 4. После прохождения управляющих импуль- 25 ления синхроимпульсов при воздействии сов для второго ключа 18 на управляю- низкочастотной аддитивной помехи, в

вого блока, выход которого является выходом амплитудного синхроселектора, а второй вход подключен к точке соединения резистора и первого конденсатора, к второму выводу которого через предварительный синхроселектор подключен вход первбго дифференцирующего блока, отличающийся тем, что, с целью повышения точности вьде,щий вход ключа 4 через третий элемент И 24 и второй элемент ИЛИ 21 могут проходить импульсы с выходов четвертого 11 и пятого 12 пороговых блоков. И если напряжение на выходе операционного усилителя 17 больше нуля, первый ключ 4 дополнительно открьгоается во время прохождения строчного синхроимпульса (фиг.2ж), что смещает видеосигнал на втором входе первого . порогового блока 6 вверх, т.е. в про- тивофазе с низкочастотной аддитивной помехой.

Соответствующим выбором постоянной времени инвертирующего интегратора, состоящего из резистора 3, второго конденсатора 16 и операционного усилителя 17, можно добиться полной компенсации низкочастотной аддитивной помехи на входе первого порогового блока 6 и соответственно увеличения точности вьщеления синхроимпульсов.

Действительно, на выходе операционного усилителя 17 формируется сигнал, пропорциональный первой производной по времени от сигнала низкочастотной аддитивной помехи. Этот сигнал замешивается в видеосигнал на втором входе первого порогового блока 6 путем дополнительного подключения первого конденсатора 2 через р гзистор 3 и первьй ключ 4 к источнику 5 опорного напряжения. Таким образом, ошибка привязки половины размаха строчного синхроимпульса к потенциалу привязки пропорциональна второй произ-. водной по времени от низкочастотной аддитивной помехи.

Формула изобретения

1. Амплитудньй синхроселектор, содержащий последовательно соединенные буферный усилитель, первый конденсатор, резистор, первый ключ и источник опорного напряжения, подключенные

ления синхроимпульсов при воздействии низкочастотной аддитивной помехи, в

вого блока, выход которого является выходом амплитудного синхроселектора, а второй вход подключен к точке соединения резистора и первого конденсатора, к второму выводу которого через предварительный синхроселектор подключен вход первбго дифференцирующего блока, отличающийся тем, что, с целью повышения точности вьде0

5

0

5

0

5

него введены второй ключ, два логических инвертора, два элемента ИЛИ, с второго по пятьй пороговые блоки, три элемента И, операционный усилитель, второй конденсатор, блок смещения и второй дифференцируюпщй блок, выход которого подключен к выходу предварительного синхроселектора через первый логический инвертор, а выход подключен к неинвертирующему входу четвертого порогового блока и инвертирующему входу пятого порогового блока, неинвертирующий вход которого объединен с неинвертирующим входом третьего порогового блока и подключен к первому выходу блока смещения, к второму выходу которого подключены инвертирующие входы второго и четвертого пороговых блоков, а вход блока смещения подключен к первому вьшоду второго конденсатора и выходу операционного усилителя, неинвертирующий вход которого подключен к источнику опорного напряжения, а инвертирующий вход соединен с вторым выводом конденсатора к через второй ключ подключен к точке соединения резистора и первого ключа, вход управления которого подключен к выходу третьего элемента И, первый вход которого через второй логический инвертор объединен с управ.ляющим входом второго ключа и подключен к выходу первого элемента ИЛИ, к первому входу которого под- , ключей -выход первого элемента И, первый вход которого подключен к выходу пятого порогового блока и первому входу второго элемента ИЖ, выход которого подключен к второму входу третьего элемента И, а второй вход подключен к выходу четвертого порогового блока и объединен с первым входом второго элемента И, выход которого подключен к второму входу первого элемента ИЛИ, а второй вход второго элемента И подключен к выходу третье- го порогового блока, инвертирующий вход которого подключен к выходу первого дифференцирующего блока и объединен с неинвертирующим входом второ

.

)

8)

Uonep.tUcM f onep- UCH

г;

4onep.UcH Uonep,-Ucfi

д)

(Jonep UCH

Uonef)

. UnH

)

«;

Редактор М.Бланар

Составитель А.Иванов Техред И.Прпович

Заказ 5716/56Тираж 636

ВЕШИЛИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раущская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

го порогового блока, выход которого подключен к второму входу первого элемента И.

2. Амплитудньй синхроселектор по П.1, отличающийся тем, что блок смещения содержит последовательно соединенные первый источник тока, первый резистор, второй резистор и второй источник тока, причем точка соединения первого и второго резисторов является входом блока смещения, точка соединения первого источника тока и первого резистора является первым выходом блока смещения а точка соединения второго источника тока и второго резистора является вторьм выходом блока смещения.

Корректор А.Тяско

Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Синхроселектор | 1984 |

|

SU1220138A1 |

| Синхроселектор | 1985 |

|

SU1297257A1 |

| Синхроселектор | 1980 |

|

SU886314A1 |

| Синхроселектор | 1986 |

|

SU1385326A1 |

| Устройство фиксации уровня сигнала | 1981 |

|

SU1030997A2 |

| Синхроселектор | 1984 |

|

SU1197142A1 |

| Устройство для восстановления постоянной составляющей | 1990 |

|

SU1793558A1 |

| Устройство для защиты от однофазных замыканий на землю | 1987 |

|

SU1462445A1 |

| Устройство для контроля низкочастотных помех в сигнале изображения | 1982 |

|

SU1078669A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ПИКОВЫХ ЗНАЧЕНИЙ | 2007 |

|

RU2343429C1 |

Изобретение относится к телевидению и обеспечивает повышение точности вьщеления синхроимпульсов при воздействии низкочастотной аддитивной помехи (НАЛ). Амплитудный синхро- селектор содержит буферный усилитель 1, конденсаторы 2, 16, резистор 3, ключи 4, 18, источник 5 опорного напряжения, пороговые блоки (ПБ) 6,11- 14, предварительный синхроселектор 7, дифференцируклцие блоки 8,9, логические инверторы 10, 19, блок смещения 15, операционный усилитель (ОУ) 17, элементы ИЛИ 20, 21, И 22-24. При отсутствии НАЛ половина размаха строчных синхроимпульсов на первом входе ПВ 6 совпадает с напряжением источника 5. При этом на выходе ОУ 17 формируется нулевое напряжение, на выходах ПБ 11-14 формируются равные по длительности импульсы, и открыт только ключ 18. При воздействии НАП заряд, накопленный конденсатором 16 во время строчного синхроимпульса, не равен заряду, стекающему с него. Пpи этом на выходе ОУ 17 будет-соответственно изменяться напряжение, что приводит к соотв открьшанию .ключей 4, 18 и смещению видеосигнала на входе ПБ 6. Выбором постоянной времени инвертирующего интегратора, : состоящего из резистора 3, конденсатора 16 и ОУ 17, можно добиться полной компенсации НАП на входе порогового блока 6. 1 з.п. ф-лы, 2 ил. с (Л 00 ел 4 ни 4 СО «Я.Г

| Амплитудный синхроселектор | 1977 |

|

SU621125A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-11-23—Публикация

1985-06-05—Подача