Изобретение относится к радиотехнике и .может использоваться в устройствах формирования напряжений прямот угольной формы, фаза которых регулируется в диапазоне 0-360° в широком диапазоне частот входного сигнала.

Цель изобретения - повьшение стабильности сдвига фазы при изменении частоты входного сигнала.

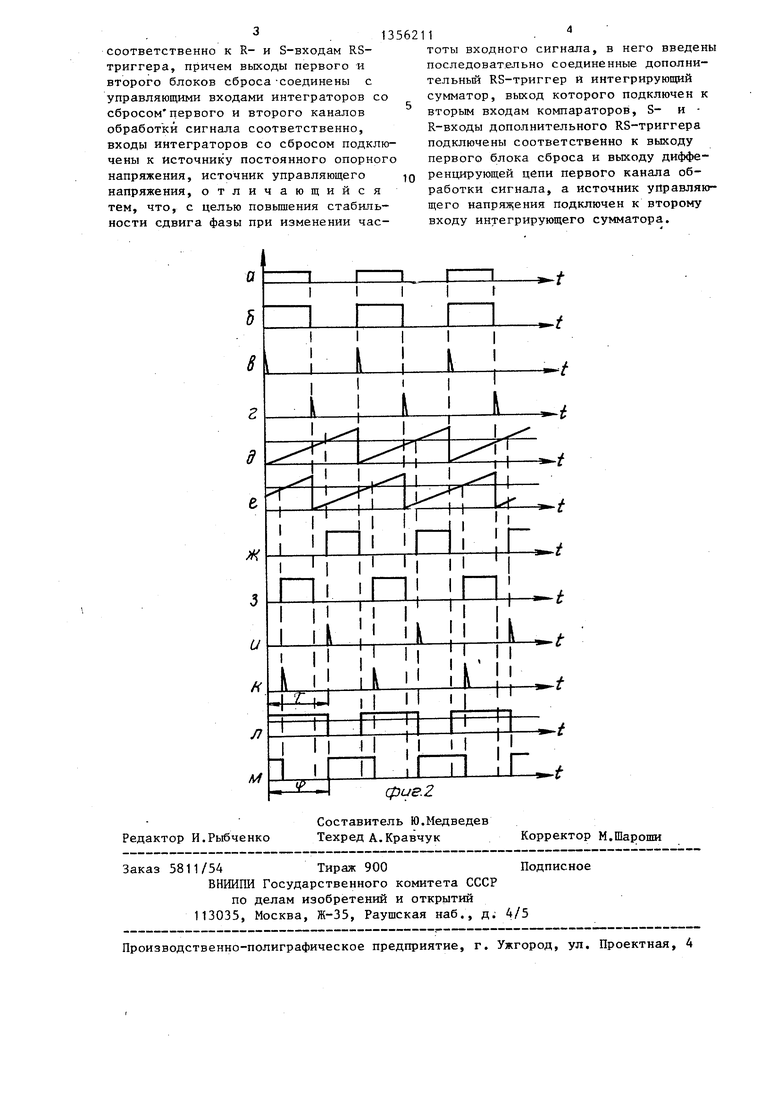

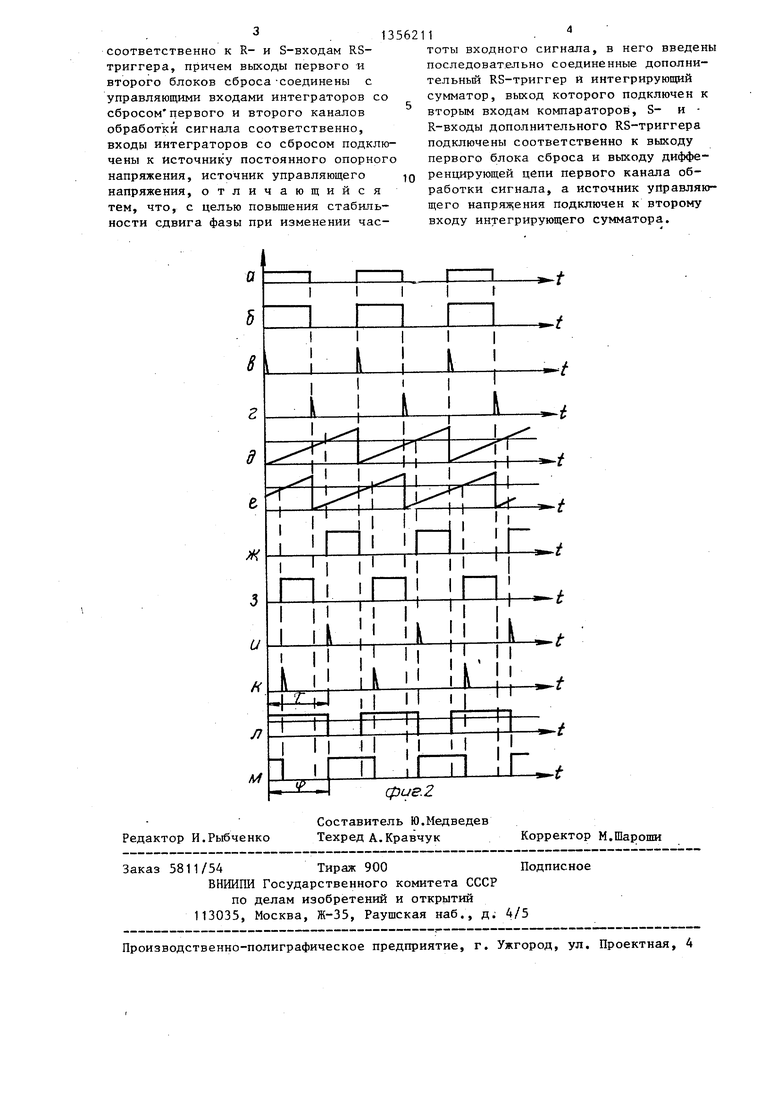

На- фиг.1 представлена структурная электрическая схема управляемого фазовращателя; на фиг.2 - временные диаграммы, поясняющие его работу.

Управляемьй фазовращатель содержит 15 входного сигнала и фазовым сдвигом.

усилитель-ограничитель 1, инвертор 2, первьй и второй блоки 3 и 4 сброса, и интеграторы 5 и 6 со сбросом, компараторы 7 и 8, дифференцирующие цепи 9 и 10, RS-триггер 11, дополнительный RS-триггер 12, источники 13 и 14 постоянного опорного и управляющего напряжения и интегрирукщий сумматор 15.

Управляемьй фазовращатель работает следующим образом.

Поступающее на вход усипителя-ог- раничителя 1 прямоугольное напряжение (фиг.2а) нормируется по амплитуде на его выходе (фиг.26). По передним фронтам прямоугольных импульсов с выхода усилителя-ограничителя 1 блоком 3 сброса формируется импульс сброса (фиг.2в) интегратора 5 со сбросом и одновременно устанавливается в состояние 1 дополнительньй RS-триггер 12. По передним фронтам проинвертирован- ных инвертором 2 прямоугольных импульсов блоком 4 сброса формируется импульс сброса (фиг.2г) интегратора 6 со сбросом. В промежутках между сигналами сброса интеграторы 5 и 6 со сбросом, интегрируя напряжение источника 13 постоянного опорного напряжения, формируют пилообразные напряжения, следующие с периодом входного сигнала, сдвиг фазы между которыми равен длительности импульсов входного сигнала (фиг.). Пилообразные напряжения поступают на первые входы компараторов 7 и 8, на вторые входы которых подается постоянное напряжение с выхода интегрирующего сумматора 15. В моменты совпадения уровня пилообразного напряжения с уровнем напряжения на вторых входах компараторов 7 и 8 на их выходах формируются импульсы прямоугольной формы (фиг.2ж, з), которые поступают на дифференци- рукяцие цепи 9 и 10. Положительные .

импульсы с выхода дифференцирующей цепи 9 (фиг.2и), соответствующие переднему фронту импульса с выхода компаратора 7, устанавливают RS-триггер 11 в состояние 1, а дополнительньй RS-триггер 12 - в состояние О. Положительные импульсы с выхода дифференцирующей цепи 10 (фиг.2к), соответствующие переднему фронту импульса с выхода компаратора 8, устанавливают RS-триггер 11 в состояние О. На выходе RS-триггера 11 формируются прямоугольные импульсы со скважностью

определяемым выходным напряжением интегрирующего сумматора 15 (фиг.2м). На выходе дополнительного RS-триггера 12 формируются прямоугольные импульсы, следующие с частотой входного сигнала и длительностью, равной фазовому сдвигу между входным и выходным сигнала;ми (фиг.2л) „ Импульсы с выхода дополнительного RS-триггера 12 посту- пают на первьй вход интегрирующего сумматора 15, на второй вход которого подается постоянное напряжение с источника 14 управляющего напряжения противоположной полярности импульсам, поступающим на первый вход.

При регулировании уровня постоянного напряжения источника 14 управляющего напряжения от минимального, равного .нулю, до максимального, равного амплитуде импульсов на выходе дополнительного RS-триггера, значений фазовьй сдвиг регулируется в диапазоне 0-360, причем установленньй фазовьй сдвиг поддерживается постоянным при изменении частоты входного сигнала в диапазоне, которьй определяется пороговой чувствительностью компараторов 7 и 8,

Формула изобретения

Управляемый фазовращател, содержащий усилитель-ограничитель, вход которого является входом управляемого фазовращателя, а выход подключен к входу первого блока сброса и через инвертор - к входу второго блока сброса, два канала обработки сигнала, каждьй из которых вьшолнен в виде последовательно соединенных интегратора со сбросом, компаратора и дифференцирующей цепи, выходы дифференцирующих цепей первого и второго каналов обработки сигнала подключены

соответственно к R- и S-входам RS- триггера, причем выходы первого и второго блоков сброса -соединены с управляющими входами интеграторов со сбросом первого и второго каналов обработки сигнала соответственно, входы интеграторов со сбросом подключены к источнику постоянного опорного напряжения, источник управляющего напряжения, отличающийся тем, что, с целью повышения стабильности сдвига фазы при изменении час13

Редактор И.Рыбченко

Составитель Ю.Медведев

Техред А.Кравчук Корректор М.Шароши

Заказ 5811/54Тираж 900Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д; 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

6211.

тоты входного сигнала, в него введены последовательно соединенные дополни- тельньм RS-триггер и интегрирующий сумматор, выход которого подключен к вторым входам компараторов, S- к - R-входы дополнительного RS-триггера подключены соответственно к выходу первого блока сброса и выходу диффе- 10 ренцирующей цепи первого канала обработки сигнала, а источник управляющего напрял1;ения подключен к второму входу интегрирующего сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляемый фазовращатель | 1983 |

|

SU1195419A1 |

| Формирователь импульсов | 1985 |

|

SU1396261A1 |

| Формирователь импульсов | 1985 |

|

SU1358076A1 |

| Формирователь импульсов | 1985 |

|

SU1396260A1 |

| Фазовращатель | 1985 |

|

SU1545325A1 |

| Управляемый фазовращатель | 1985 |

|

SU1529415A1 |

| ЦИФРОАНАЛОГОВЫЙ ФАЗОВРАЩАТЕЛЬ | 1992 |

|

RU2023273C1 |

| Управляемый фазовращатель | 1985 |

|

SU1554109A1 |

| ЦИФРОАНАЛОГОВЫЙ ФАЗОВРАЩАТЕЛЬ | 1992 |

|

RU2021622C1 |

| УСТРОЙСТВО ДЛЯ СНЯТИЯ ФАЗОЧАСТОТНОЙ ХАРАКТЕРИСТИКИ УСИЛИТЕЛЕЙ | 2011 |

|

RU2480775C2 |

Изобретение относится к радиотехнике и обеспечивает повышение стабильности сдвига фазы при изменении частоты входного сигнала. Управляемый фазовращатель содержит усилитель-ограничитель 1, инвертор 2, блоки сброса- 3, 4, два канала обработки сигнала, состоящие из интегратора со сбросом 5(6), компаратора 7(8) и дифференцирующей цепи 9(10), RS-триггеры 11, 12, источник 13 постоянного опорного напряжения, источник 14 управляющего напряжения и интегрирующий сумматор 15. Интеграторы 5,6, интегрируя напряжение источника 13, формируют пилообразные напряжения с периодом входного сигнала. Сдвиг фаз между пилообразными напряжениями интеграторов 5,6 обеспечивается блоками сброса 3, 4 и равен длительности импульсов входного сигнала. При совпадании напряжений интеграторов 5, 6с постоянным напряжением интегрирующего сумматора 15 соотв. компараторы форьшруют импульсы. По ним RS-триггер 11 формирует импульсы с частотой входного сигнала и фазовьм сдвигом, определяемым выходным напряжением интегрирующего сумматора 15. С помощью введенных RS-триггера 12 и интегрирующего сумматора 15 поддерживается постоянным при изменении частоты входного сигнала фазовый сдвиг, устанавливае- мьй регулированием уровня напряжения источника 14. 2 ил. (Л . оо ел О5 to Фие.1

| Управляемый фазовращатель | 1983 |

|

SU1195419A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-11-30—Публикация

1985-06-10—Подача