Изобретение относится к радиотехнике и может быть использовано для формирования меандра с заданной фазовой задержкой относительно входного гармонического сигнала.

Цель изобретения - повышение температурной стабильности скважности выходного сигнала управляемого фазовращателя .

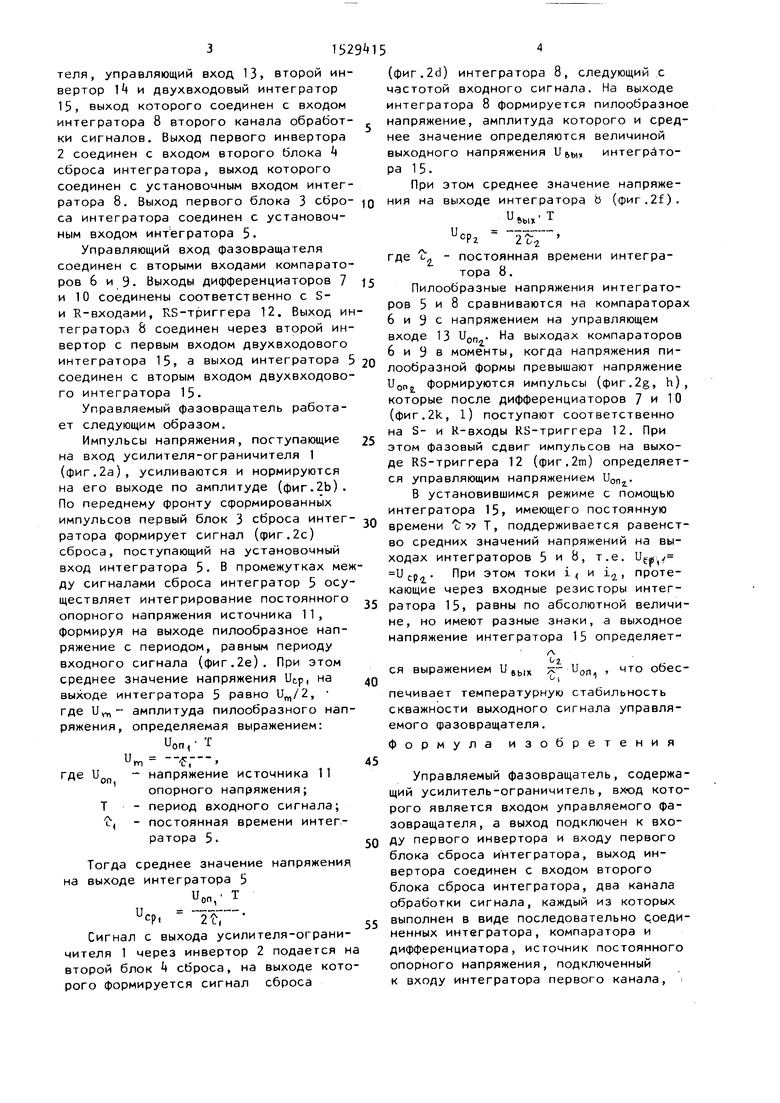

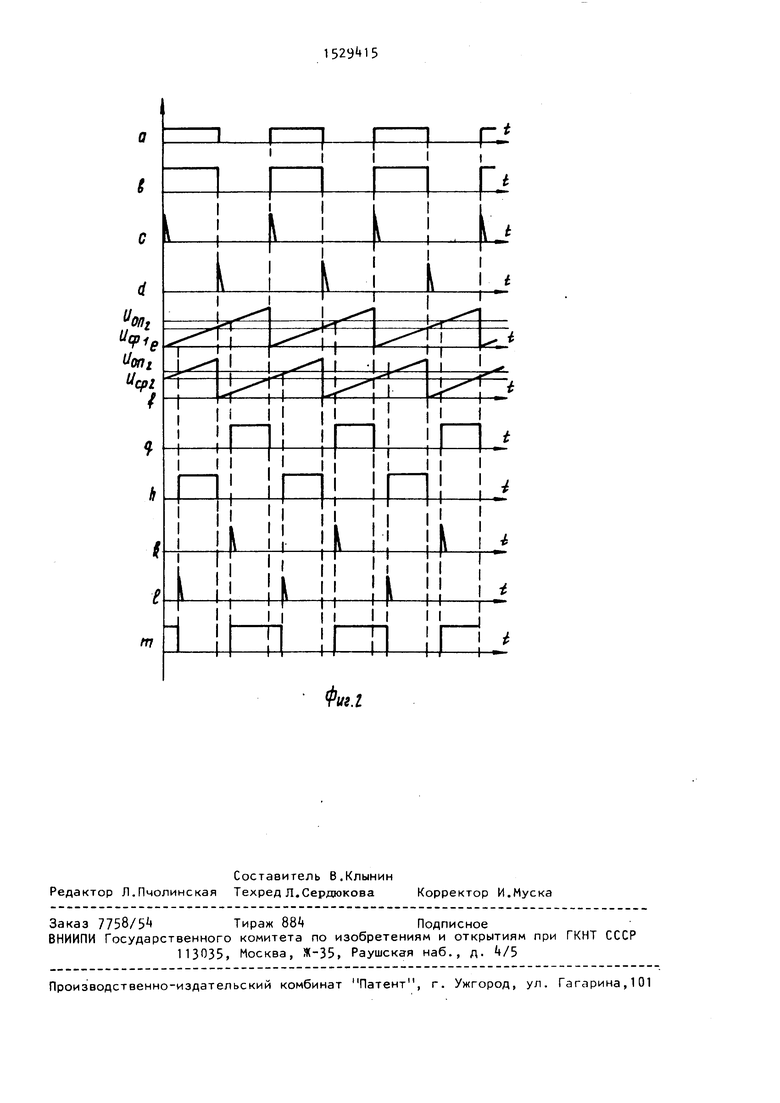

На фиг.1 изображена функ1,иональная схема управляемого фазовращателя; на фиг.2 - эпюры напряжений в различных его цепях.

Управляемый фазовращатель содержит усилитель-ограничитель 1, вход которого соединен с входом управляемого фазовращателя, а выход - с входом первого инвертора 2 и входом первого блока 3 сброса интегратора, второй блок k сброса интегратора, первый канал обработки сигнала, состоящий из соединенных последовательно интегратора 5 компаратора 6 и дифференциатора 7. второй канал обработки сигнала, состоящий из соединенных последовательно интегратора 8, компаратора 9 и дифференциатора 10, источник 11 постоянного опорного напряжения, RS-триггер 12, выход которого соединен с выходом управляемого фазовращаСа N5

СО

СП

теля, управляющий вход 13, второй инвертор и двухвходовый интегратор 15, выход которого соединен с входом интегратора 8 второго канала обработки сигналов. Выход первого инвертора 2 соединен с входом второго блока 4 сброса интегратора, выход которого соединен с установочным входом интегратора 8. Выход первого блока 3 сбро- са интегратора соединен с установочным входом интегратора 5.

Управляющий вход фазовращателя соединен с вторыми входами компараторов 6 и 9. Выходы дифференциаторов 7 и 10 соединены соответственно с S- и R-входами, RS-триггера 12. Выход интегратора 8 соединен через второй инвертор с первым входом двухвходового интегратора 15, а выход интегратора 5 соединен с вторым входом двухвходового интегратора 15.

Управляемый фазовращатель работает следующим образом.

Импульсы напряжения, поступающие на вход усилителя-ограничителя 1 (фиг.2а), усиливаются и нормируются на его выходе по амплитуде (фиг.2Ь). По переднему фронту сформированных импульсов первый блок 3 сброса интег- ратора формирует сигнал (фиг.2с) сброса, поступающий на установочный вход интегратора 5. В промежутках между сигналами сброса интегратор 5 осуществляет интегрирование постоянного опорного напряжения источника 11, формируя на выходе пилообразное напряжение с периодом, равным периоду входного сигнала (фиг.2е). При этом среднее значение напряжения Utp, на выходе интегратора 5 равно , где амплитуда пилообразного напряжения, определяемая выражением:

и

оп,

Т

и

г., -- 5,-

on,

11

напряжение источника опорного напряжения; Т - период входного сигнала; - постоянная времени интегратора 5.

Тогда среднее значение напряжения выходе интегратора 5

и

оп.

и,

ср. - 2t, Сигнал с выхода усилителя-ограничителя 1 через инвертор 2 подается на второй блок k сброса, на выходе которого формируется сигнал сброса

s 0

5 Q Q

5

(фиг.2) интегратора 8, следующий с частотой входного сигнала. На выходе интегратора 8 формируется пилообразное напряжение, амплитуда которого и среднее значение определяются величиной выходного напряжения Uьы, интегрйто- ра 15.

При этом среднее значение напряжения на выходе интегратора Ь (фиг.2).

lL

Р2 Zli

где с. - постоянная времени интегратора 8.

Пилообразные напряжения интеграторов 5 и 8 сравниваются на компараторах 6 и 9 с напряжением на управляющем входе 13 3 выходах компараторов 6 и 9 в моменты, когда напряжения пилообразной формы превышают напряжение UQOJ формируются импульсы (фиг.2g, h) , которые после дифференциаторов 7 и 10 (фиг.2k, 1) поступают соответственно на S- и R-входы RS-триггера 12. При этом фазовый сдвиг импульсов на выходе RS-триггера 12 (фиг.2т) определяется управляющим напряжением Ugp,.

В установившимся режиме с помощью интегратора 15, имеющего постоянную времени Т, поддерживается равенство средних значений напряжений на выходах интеграторов 5 и 8, т.е. Uee,y Uj,prt При этом токи i( и i, протекающие через входные резисторы интегратора 15, равны по абсолютной величине, но имеют разные знаки, а выходное напряжение интегратора 15 определяет

ся выражением U

ых

А

02.

Л- и.

м

что обесг,

печивает температурную стабильность скважности выходного сигнала управляемого фазовращателя.

Формула изобретения

Управляемый фазовращатель, содержащий усилитель-ограничитель, вход которого является входом управляемого фазовращателя, а выход подключен к входу первого инвертора и входу первого блока сброса интегратора, выход инвертора соединен с входом второго блока сброса интегратора, два канала обработки сигнала, каждый из которых выполнен в виде последовательно с.оеди- ненных интегратора, компаратора и дифференциатора, источник постоянного опорного напряжения, подключенный к входу интегратора первого канала.

5152Э

установочные входы интеграторов подключены к выходам соответствующих блоков сброса интеграторов, выходы дифференциаторов первого и второго каналов обработки сигнала подключены соответственно к S- и К-входам RS- триггера, выход которого является выходом управляемого фазовращателя, а управляющий вход фазовращателя, подключен к вторым входам компараторов, отличающийся тем,

Ь6

что, с целью повышения темгературной стабильности скважности выходного сигнала управляемого фазовращателя, введены второй инвертор, вход которого соединен с выходом интегратора второго канала, двухвходовый интегратор, первый вход которого подключен к выходу второго инвертора, второй вход подключен к выходу интегратора первого канала, а выход соединен с входом интегратора второго канала.

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь импульсов | 1985 |

|

SU1396261A1 |

| Управляемый фазовращатель | 1983 |

|

SU1195419A1 |

| Формирователь импульсов | 1985 |

|

SU1396260A1 |

| Управляемый фазовращатель | 1985 |

|

SU1356211A1 |

| Формирователь импульсов | 1985 |

|

SU1358076A1 |

| Управляемый фазовращатель | 1985 |

|

SU1554109A1 |

| ЦИФРОАНАЛОГОВЫЙ ФАЗОВРАЩАТЕЛЬ | 1992 |

|

RU2023273C1 |

| Управляемый фазовращатель | 1980 |

|

SU995278A1 |

| ЦИФРОАНАЛОГОВЫЙ ФАЗОВРАЩАТЕЛЬ | 1992 |

|

RU2021622C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ФАЗОЙ КОЛЕБАНИЙ | 2003 |

|

RU2273950C2 |

Изобретение относится к радиотехнике. Целью изобретения является повышение температурной стабильности скважности выходного сигнала управляемого фазовращателя. Управляемый фазовращатель содержит усилитель-ограничитель, вход которого является входом управляемого фазовращателя, а выход подключен к входу первого инвертора и входу первого блока сброса интегратора, выход первого инвертора соединен с входом второго блока сброса интегратора, два канала обработки сигнала, каждый из которых выполнен в виде последовательно соединенных интегратора, компаратора и дифференциатора, источник постоянного опорного напряжения, подключенный к входу интегратора первого канала, установочные входы интеграторов подключены к выходам соответствующих блоков сброса, выходы дифференциаторов первого и второго каналов обработки сигнала подключены соответственно к S - и R - входам RS - триггера, выход которого является выходом управляемого фазовращателя, управляющий вход, подключенный к вторым входам компараторов, второй инвертор, вход которого соединен с выходом интегратора второго канала, двухвходовый интегратор, первый вход которого подключен к выходу второго инвертора, второй вход подключен к выходу интегратора первого канала, а выход соединен с входом интегратора второго канала. 2 ил.

Аг.

а

LL5::3/ii

Вых.

т

гпл

Физ.1

Фиг.г

Авторы

Даты

1989-12-15—Публикация

1985-06-03—Подача