Изобретение относится к автомати- ке и вычислительной технике и может быть использовано для связи аналоговых источников информации с цифровым вычислительным устройством.

Цель изобретения - расширение об- ласти применения преобразователя путем формирования кода модуля ускорения.

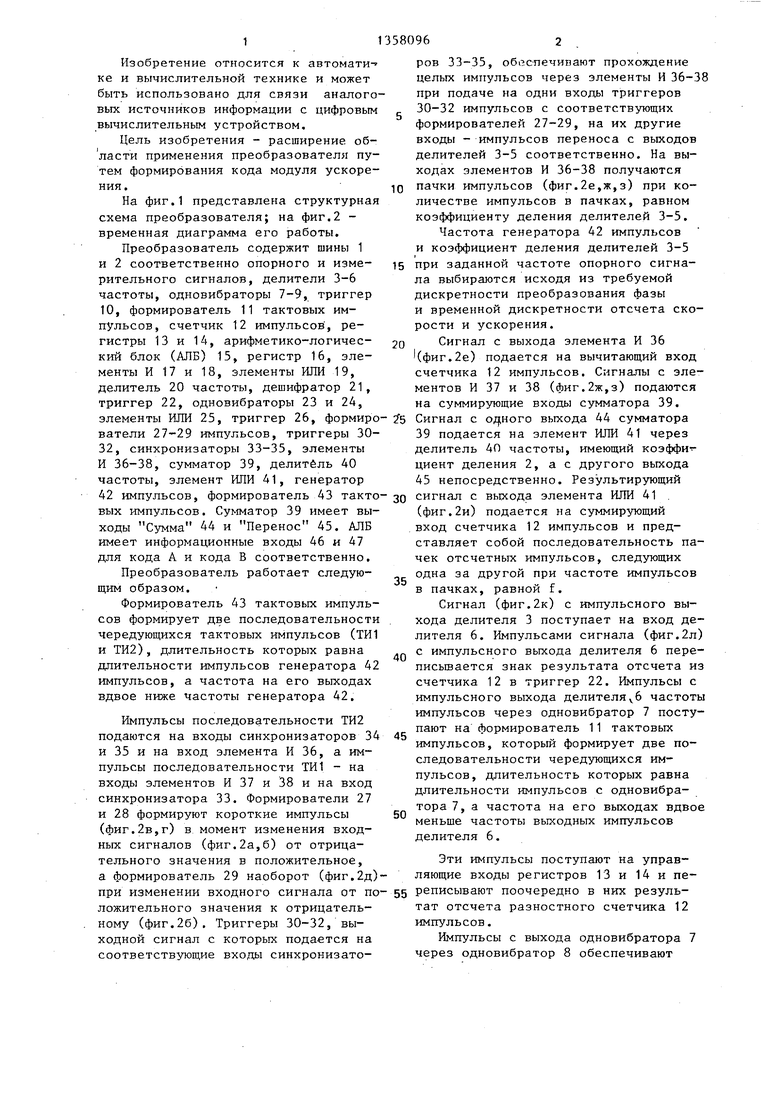

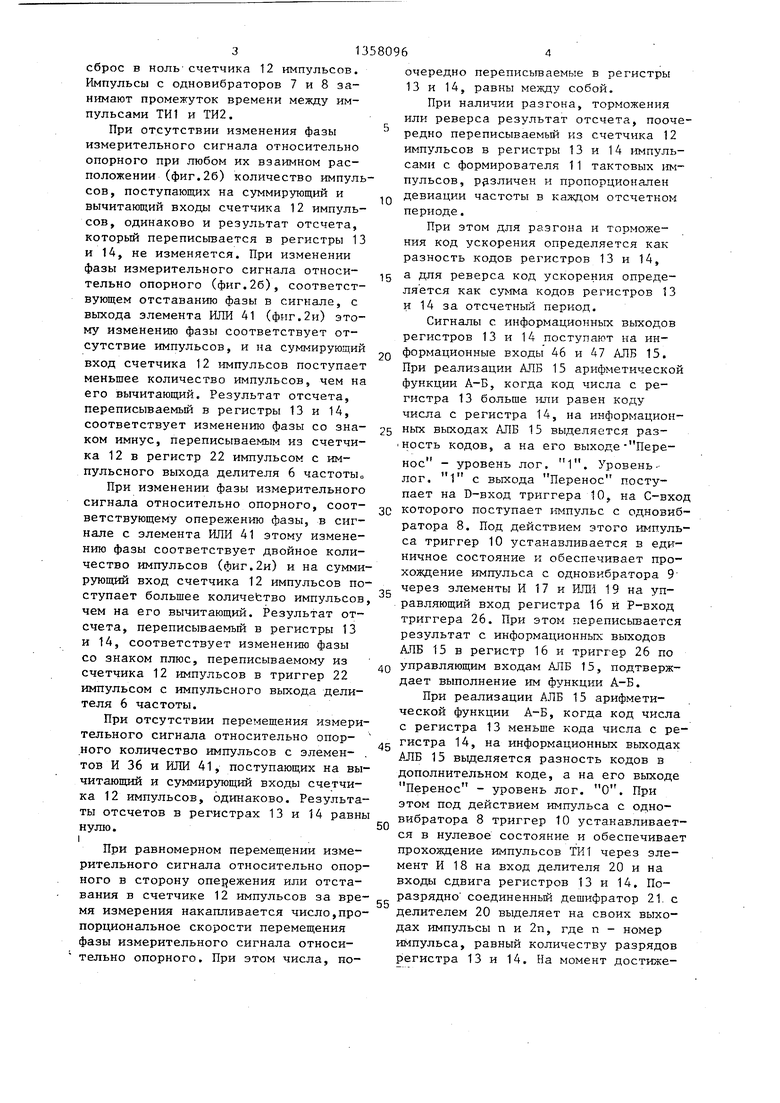

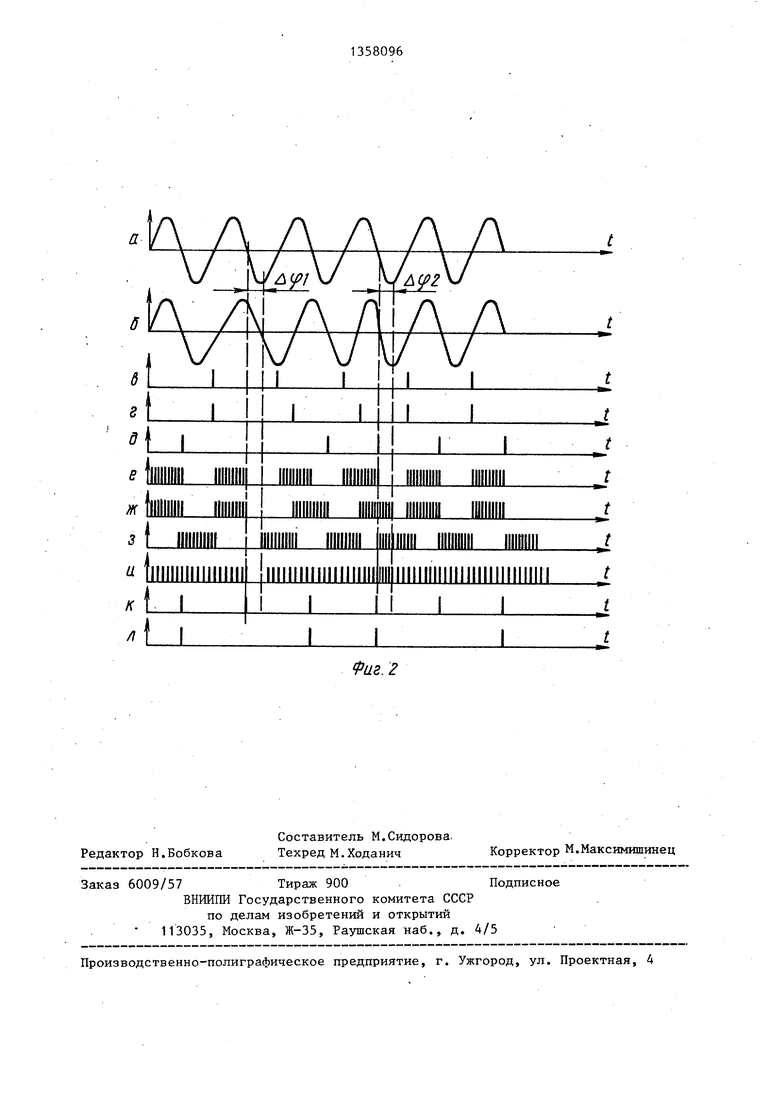

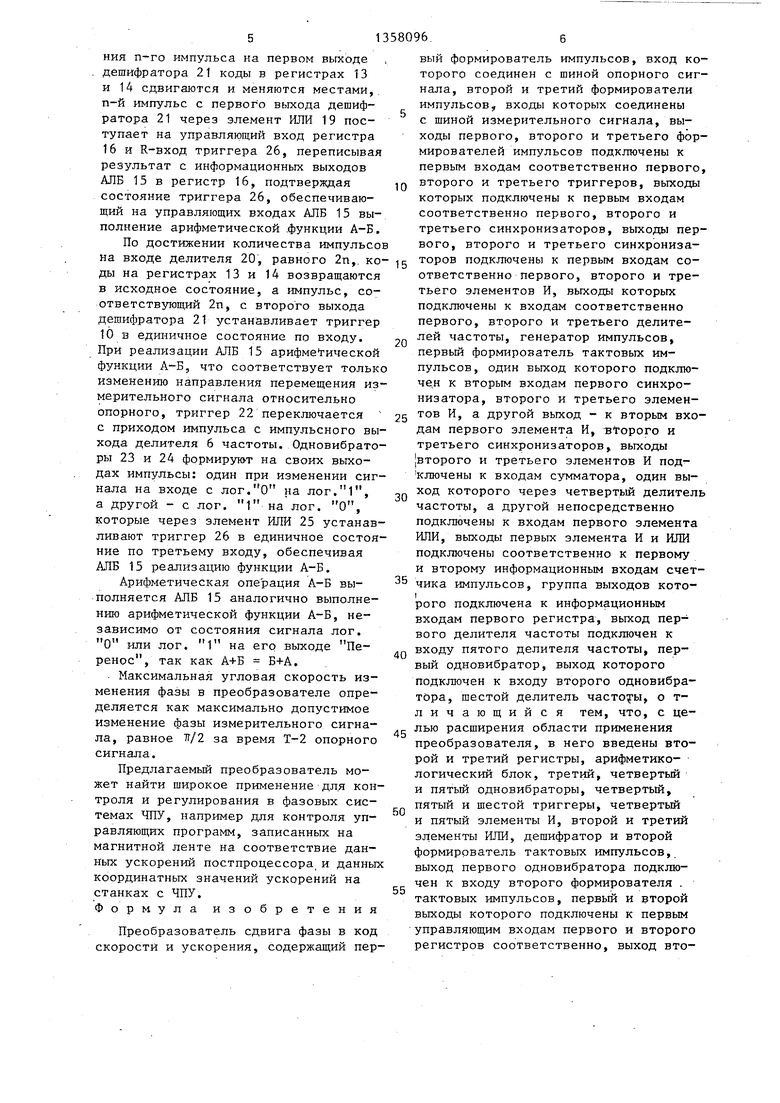

На фиг.1 представлена структурная схема преобразователя; на фиг.2 - временная диаграмма его работы.

Преобразователь содержит шины 1 и 2 соответственно опорного и измерительного сигналов, делители 3-6 частоты, одновибраторы 7-9, триггер 10, формирователь 11 тактовых импульсов, счетчик 12 импульсов , регистры 13 и 14, арифметико-логический блок (АЛБ) 15, регистр 16, элементы И 17 и 18, элементы ИЛИ 19, делитель 20 частоты, дешифратор 21, триггер 22, одновибраторы 23 и 24, элементы ИЛИ 25, триггер 26, формирователи 27-29 импульсов, триггеры 30- 32, синхронизаторы 33-35, элементы И 36-38, сумматор 39, делитель 40 частоты, элемент ИЛИ 41, генератор 42 импульсов, формирователь 43 тактовых импульсов. Сумматор 39 имеет выходы Сумма 44 и Перенос 45. АЛБ имеет информационные входы 46 и 47 для кода А и кода В соответственно.

Преобразователь работает следующим образом.

Формирователь 43 тактовых импульсов формирует две последовательности чередующихся тактовых импульсов (ТИ1 и ТИ2), длительность которых равна длительности импульсов генератора 42 импульсов, а частота на его выходах вдвое ниже частоты генератора 42.

Импульсы последовательности ТИ2 подаются на входы синхронизаторов 34 и 35 и на вход элемента И 36, а импульсы последовательности ТИ1 - на входы элементов И 37 и 38 и на вход синхронизатора 33. Формирователи 27 и 28 формируют короткие импульсы (фиг.2в,г) в момент изменения входных сигналов (фиг.2а,б) от отрицательного значения в положительное, а формирователь 29 наоборот (фиг.2д) при изменении входного сигнала от положительного значения к отрицательному (фиг.2б). Триггеры 30-32, выходной сигнал с которых подается на соответствующие входы синхронизаторов 33-35, обеспечивают прохождение целых импульсов через элементы И 36-38 при подаче на одни входы триггеров 30-32 импульсов с соответствующих формирователей 27-29, на их другие входы - импульсов переноса с выходов делителей 3-5 соответственно. На выходах элементов И 36-38 получаются

пачки импульсов (фиг.2е,ж,з) при количестве импульсов в пачках, равном коэффициенту деления делителей 3-5.

Частота генератора 42 импульсов и коэффициент деления делителей 3-5

5 при заданной частоте опорного сигнала выбираются исходя из требуемой дискретности преобразования фазы и временной дискретности отсчета скорости и ускорения.

0 Сигнал с выхода элемента И 36

(фиг.2е) подается на вычитающий вход счетчика 12 импульсов. Сигналы с элементов И 37 и 38 (фиг.2ж,з) подаются на суммирующие входы сумматора 39.

5 Сигнал с offHoro выхода 44 сумматора 39 подается на элемент ИЛИ 41 через делитель 4П частоты, имеющий коэффициент деления 2, ас другого выхода 45 непосредственно. Результирующий

0 сигнал с выхода элемента ИЛИ 41 . (фиг.2и) подается на суммирующий вход счетчика 12 импульсов и представляет собой последовательность пачек отсчетных импульсов, следующих одна за другой при частоте импульсов в пачках, равной f.

Сигнал (фиг.2к) с импульсного выхода делителя 3 поступает на вход делителя 6. Импульсами сигнала (фиг.2л) с импульсного выхода делителя 6 пере- письшается знак результата отсчета из счетчика 12 в триггер 22. Импульсы с импульсного выхода делителя 6 частоты импульсов через одновибратор 7 поступают на формирователь 11 тактовых импульсов, который формирует две последовательности чередующихся импульсов, длительность которых равна длительности импульсов с одновибра- тора 7, а частота на его выходах вдвое меньше частоты выходных импульсов делителя 6.

5

0

5

0

Эти импульсы поступают на управляющие входы регистров 13 и 14 и пе- 55 реписывают поочередно в них результат отсчета разностного счетчика 12 импульсов.

Импульсы с выхода одновибратора 7 через одновибратор 8 обеспечивают

10

15

31358096

сброс в ноль счетчика 12 импульсов. Импульсы с одновибраторов 7 и 8 занимают промежуток времени между импульсами ТИ1 и ТИ2.

При отсутствии изменения фазы измерительного сигнала относительно опорного при любом их взаимном расположении (фиг. 2б) количество импульсов, поступающих на суммирующий и вычитающий входы счетчика 12 импульсов, одинаково и результат отсчета, который переписьгоается в регистры 13 и 14, не изменяется. При изменении фазы измерительного сигнала относительно опорного (фиг.2б), соответствующем отставанию фазы в сигнале, с выхода элемента ИЛИ 41 (фиг.2и) этому изменению фазы соответствует отсутствие импульсов, и на суммирующий вход счетчика 12 импульсов поступает меньшее количество импульсов, чем на его вычитающий. Результат отсчета, переписываемый в регистры 13 и 14, соответствует изменению фазы со знаком имнус, переписываемым из счетчика 12 в регистр 22 импульсом с импульсного выхода делителя 6 частоты

При изменении фазы измерительного сигнала относительно опорного, соответствующему опережению фазы, в сигнале с элемента ИЛИ 41 этому изменению фазы соответствует двойное количество импульсов (Лиг.2и) и на сумми- рзтощйй вход счетчика 12 импульсов по20

ЗС

очередно переписываемые в регистры 13 и 14, равны между собой.

При наличии разгона, торможения или реверса результат отсчета, пооче редно переписываемый из счетчика 12 импульсов в регистры 13 и 14 импульсами с формирователя 11 тактовых импульсов, различен и пропорционален девиации частоты в каждом отсчетном периоде.

При этом для разгона и торможения код ускорения определяется как разность кодов регистров 13 и 14, а для реверса код ускорения определяется как сумма кодов регистров 13 и 14 за отсчетный период.

Сигналы с информационных выходов регистров 13 и 14 поступают на информационные входы 46 и 47 АЛБ 15. При реализации АЛБ 15 арифметической функции А-Б, когда код числа с регистра 13 больше или равен коду числа с регистра 14, на информацион- 5 ных выходах АЛБ 15 выделяется раз- Ность кодов, а на его выходе- Перенос - уровень лог. 1. Уровень- лог. 1 с выхода Перенос поступает на D-вход триггера lOj на С-вхо которого поступает импульс с однови ратора 8. Под действием этого импуль са триггер 10 устанавливается в единичное состояние и обеспечивает прохождение импульса с одновибратора 9 через элементы И 17 и ИЛИ 19 на упог- Lui jc I / i-i . j net У ступает большее количеЬтво импульсов, - равляющий вход регистра 16 и Р-вход

чем на его вычитающий. Результат отсчета, переписываемый в регистры 13 и 14, соответствует изменению фазы со знаком плюс, переписываемому из счетчика 12 импульсов в триггер 22 импульсом с импульсного выхода делителя 6 частоты.

При отсутствии перемещения измерительного сигнала относительно опор- ного количество импульсов с элемен- . тов И 36 и ИЛИ 41, поступающих на вычитающий и суммирующий входы счетчика 12 импульсов, одинаково. Результаты отсчетов в регистрах 13 и 14 равны

нулю.

I

40

При равномерном перемещении измерительного сигнала относительно опорного в сторону опе1}ежения или отставания в счетчике 12 импульсов за время измерения накапливается число,пропорциональное скорости перемещения фазы измерительного сигнала относительно опорного. При этом числа, потриггера 26. При этом переписьшается результат с информационных выходов А.ПБ 15 в регистр 16 и триггер 26 по управляющим входам АЛБ 15, подтверждает выполнение им функции А-Б.

При реализации АЛБ 15 арифметической функции А-Б, когда код числа с регистра 13 меньше кода числа с ре g гистра 14, на информационных выходах АЛБ 13 вьщеляется разность кодов в дополнительном коде, а на его выходе Перенос - уровень лог. О. При этом под действием импульса с одно- вибратора 8 триггер 10 устанавливает ся в нулевое состояние и обеспечивае прохождение импульсов ТИ1 через элемент И 18 на вход делителя 20 и на входы сдвига регистров 13 и 14. Поразрядно соединенный дешифратор 21. с делителем 20 выделяет на своих выходах импульсы п и 2п, где п - номер импульса, равный количеству разрядов регистра 13 и 14. На момент достиже50

55

5

0

С

очередно переписываемые в регистры 13 и 14, равны между собой.

При наличии разгона, торможения или реверса результат отсчета, поочередно переписываемый из счетчика 12 импульсов в регистры 13 и 14 импульсами с формирователя 11 тактовых импульсов, различен и пропорционален девиации частоты в каждом отсчетном периоде.

При этом для разгона и торможения код ускорения определяется как разность кодов регистров 13 и 14, а для реверса код ускорения определяется как сумма кодов регистров 13 и 14 за отсчетный период.

Сигналы с информационных выходов регистров 13 и 14 поступают на информационные входы 46 и 47 АЛБ 15. При реализации АЛБ 15 арифметической функции А-Б, когда код числа с регистра 13 больше или равен коду числа с регистра 14, на информацион- 5 ных выходах АЛБ 15 выделяется раз- Ность кодов, а на его выходе- Перенос - уровень лог. 1. Уровень- лог. 1 с выхода Перенос поступает на D-вход триггера lOj на С-вход которого поступает импульс с одновиб- ратора 8. Под действием этого импульса триггер 10 устанавливается в единичное состояние и обеспечивает прохождение импульса с одновибратора 9 через элементы И 17 и ИЛИ 19 на упг- Lui jc I / i-i . j net У равляющий вход регистра 16 и Р-вход

0

триггера 26. При этом переписьшается результат с информационных выходов А.ПБ 15 в регистр 16 и триггер 26 по управляющим входам АЛБ 15, подтверждает выполнение им функции А-Б.

При реализации АЛБ 15 арифметической функции А-Б, когда код числа с регистра 13 меньше кода числа с ре- g гистра 14, на информационных выходах АЛБ 13 вьщеляется разность кодов в дополнительном коде, а на его выходе Перенос - уровень лог. О. При этом под действием импульса с одно- вибратора 8 триггер 10 устанавливается в нулевое состояние и обеспечивает прохождение импульсов ТИ1 через элемент И 18 на вход делителя 20 и на входы сдвига регистров 13 и 14. Поразрядно соединенный дешифратор 21. с делителем 20 выделяет на своих выходах импульсы п и 2п, где п - номер импульса, равный количеству разрядов регистра 13 и 14. На момент достиже0

5

ния n-го импульса на первом выходе дешифратора 21 коды в регистрах 13 и 14 сдвигаются и меняются местами,, п-й импульс с первого выхода дешифратора 21 через элемент ИЛИ 19 поступает на управляющий вход регистра 16 и R-вход триггера 26, переписывая результат с информационных выходов АЛБ 15 в регистр 16, подтверждая состояние триггера 26, обеспечивающий на управляющих входах АЛБ 15 выполнение арифметической .функции А-Б, По достижении количества импульсо

на входе делителя 20, равного 2п,. ко- 15 торов подключены к первым входам соды на регистрах 13 и 14 возвращаются в исходное состояние, а импульс, со- ответствз/тощий 2п, с второго выхода дешифратора 21 устанавливает триггер 10 в единичное состояние по входу. При реализации АЛБ 15 арифметической функции А-Б, что соответствует только изменению направления перемещения измерительного сигнала относительно опорного, триггер 22 переключается с приходом импульса с импульсного выхода делителя 6 частоты. Одновибрато- ры 23 и 24 формирзлот на своих выходах импульсы: один при изменении сигнала на входе с лог.О на лог. Ч, а другой - с лог. 1 на лог. О, которые через элемент ИЛИ 25 устанавливают триггер 26 в единичное состояние по третьему входу, обеспечивая АЛБ 15 реализацию функции А-Б.

Арифметическая операция А-Б выполняется АЛБ 15 аналогично выполнению арифметической функции А-Б, независимо от состояния сигнала лог. О или лог. 1 на его выходе Перенос, так как А+Б Б+А.

Максимальная угловая скорость изменения фазы в преобразователе определяется как максимально допустимое изменение фазы измерительного сигнала, равное Tf/2 за время Т-2 опорного сигнала.

Предлагаемьш преобразователь может найти широкое применение для контроля и регулирования в фазовых системах ЧПУ, например для контроля управляющих программ, записанных на магнитной ленте на соответствие данных ускорений постпроцессора и данных координатных значений ускорений на станках с ЧПУ. Формула изобретения

Преобразователь сдвига фазы в код скорости и ускорения, содержащий пер20

25

30

35

40

45

50

55

ответственно первого, второго и третьего элементов И, выходы которых подключены к входам соответственно первого, второго и третьего делителей частоты, генератор импульсов, первый формирователь тактовых импульсов, один выход которого подклю- че,н к вторым входам первого синхронизатора, второго и третьего элементов И, а другой выход - к вторым входам первого элемента И, второго и третьего синхронизаторов, выходы второго и третьего элементов И под ключены к входам сумматора, один выход которого через четвертый делитель частоты, а другой непосредственно подключены к входам первого элемента ИЛИ, выходы первых элемента И и ИЛИ подключены соответственно к первому и второму информационным входам счетчика импульсов, группа выходов которого подключена к информационным входам первого регистра, выход первого делителя частоты подключен к входу пятого делителя частоты, первый одновибратор, выход которого подключен к входу второго одновибра- тора, шестой делитель частоты, о т- личающийся тем, что, с целью расширения области применения преобразователя, в него введены второй и третий регистры, арифметико- логический блок, третий, четвертый и пятый одновибраторы, четвертый, пятый и шестой триггеры, четвертый и пятый элементы И, второй и третий элементы ИЛИ, дешифратор и второй формирователь тактовых импульсов, выход первого одновибратора подключен к входу второго формирователя . тактовых импульсов, первый и второй выходы которого подключены к первым управляющим входам первого и второго регистров соответственно, выход вто

вый формирователь импульсов, вход которого соединен с шиной опорного сигнала, второй и третий формирователи импульсов, входы которых соединены с шиной измерительного сигнала, выходы первого, второго и третьего формирователей импульсов подключены к первым входам соответственно первого, второго и третьего триггеров, выходы которых подключены к первьм входам соответственно первого, второго и третьего синхронизаторов, выходы первого, второго и третьего синхрониза

5

0

5

0

5

0

5

ответственно первого, второго и третьего элементов И, выходы которых подключены к входам соответственно первого, второго и третьего делителей частоты, генератор импульсов, первый формирователь тактовых импульсов, один выход которого подклю- че,н к вторым входам первого синхронизатора, второго и третьего элементов И, а другой выход - к вторым входам первого элемента И, второго и третьего синхронизаторов, выходы второго и третьего элементов И под ключены к входам сумматора, один выход которого через четвертый делитель частоты, а другой непосредственно подключены к входам первого элемента ИЛИ, выходы первых элемента И и ИЛИ подключены соответственно к первому и второму информационным входам счетчика импульсов, группа выходов которого подключена к информационным входам первого регистра, выход первого делителя частоты подключен к входу пятого делителя частоты, первый одновибратор, выход которого подключен к входу второго одновибра- тора, шестой делитель частоты, о т- личающийся тем, что, с целью расширения области применения преобразователя, в него введены второй и третий регистры, арифметико- логический блок, третий, четвертый и пятый одновибраторы, четвертый, пятый и шестой триггеры, четвертый и пятый элементы И, второй и третий элементы ИЛИ, дешифратор и второй формирователь тактовых импульсов, выход первого одновибратора подключен к входу второго формирователя . тактовых импульсов, первый и второй выходы которого подключены к первым управляющим входам первого и второго регистров соответственно, выход второго одновибратора подключен к установочному входу счетчика импульсов, к входу третьего одновибратора и к управляющему входу четвертого триггера, выход третьего одновибратора и первый выход четвертого триггера подключены к входам четвертого элемента И, один выход первого формирователя тактовых импульсов и второй выход четвертого триггера подключены к входам пятого элемента И, выход которого подключен к входу шестого делителя частоты и вторым управляющим входам первого и второго регистров, выходы шестого делителя частоты подключены к входам дешифратора, первый выход которого и выход четвертого элемента И подключены к входам второго элемента ИЛИ, выход которого подключен к управляющему входу третьего регистра и одному входу пятого триггера, выход знакового разряда счетчика импульсов подключен к информационному входу шестого триггера, а группа выходов счетчика импульсов подключена к информационным входам второго регистра, выходы первого и второго регистров подключены к первой и второй группам информационных входов арифметико-логического

блока, первый и второй управляющие входы которого подключены к первому и второму выходам пятого триггера соответственно, информационные выходы подключены к информационным входам третьего регистра, а выход переноса подключен к информационному входу четвертого триггера, второй выход дешифратора подключен к установочному входу четвертого триггера, выход старшего разряда первого регистра подключен к последовательному входу второго регистра, а выход стар5 шего разряда второго регистра подключен к последовательному входу первого регистра, выход пятого делителя частоты подключен к управляющему входу шестого триггера, эыходы которого

0 через четвертый и пятый одновибраторы соответственно подключены к входам третьего элемента ИЛИ, выход третьего элемента ИЛИ подключен к другому входу пятого триггера, выходы первого,

5 второго и третьего делителей частоты подключены к вторым входам со ответст- венно первого, второго и третьего триггеров, выход генератора импульсов соединен с входом первого фор - 30 мирователя тактовых импуль - сов,

| название | год | авторы | номер документа |

|---|---|---|---|

| Фазоимпульсный преобразователь | 1983 |

|

SU1161977A1 |

| Преобразователь угла поворота вала в код | 1985 |

|

SU1272509A1 |

| Фазоимпульсный преобразователь | 1984 |

|

SU1256186A1 |

| Преобразователь угла поворота вала в код | 1983 |

|

SU1108482A2 |

| Преобразователь угла поворота вала в код | 1981 |

|

SU1013998A1 |

| Ячейка однородной вычислительной среды | 1986 |

|

SU1443000A1 |

| МАГНИТОСТРИКЦИОННЫЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕЩЕНИЙ | 1994 |

|

RU2109399C1 |

| Устройство для управления шаговым двигателем | 1989 |

|

SU1646036A2 |

| Устройство для распознавания сигналов объектов | 1989 |

|

SU1674183A1 |

| МАГНИТОСТРИКЦИОННЫЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕЩЕНИЙ | 1994 |

|

RU2090839C1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано для связи аналоговых источников информации с цифровым вычислительным устройством. С целью расширения области применения путем формирования кода модуля ускорения в преобразователь сдвига фазы в код скорости и ускорения, содержащий шины опорного и измерительного сигналов, шесть делителей частоты, два одновибратора, три триггера, три элемента И, элемент ИЛИ, формирователь тактовых импульсов, три формирователя импульсов, три синхронизатора, сумматор , регистр, счетчик, введены два регистра, арифметико-логический блок (АЛБ), три одно- вибратора, четыре триггера, два элемента И, два элемента ИЛИ, дешифратор и второй формирователь тактовых импульсов. При отсутствии перемещения измерительного сигнала относительно опорного количество импульсов, поступающих на суммирующий и вычитающий входы счетчика, одинаково. При равномерном перемещении измерительного сигнала относительно опорного количество импульсов, переписываемых в два регистра, одинаково. При наличии разгона, торможения или реверса количество импульсов, переписываемых из счетчика в регистры, различно и пропорционально изменению частоты в каждом отсчетном периоде. При этом для разгона и торможения код ускоре- ния определяется в АЛБ как разность кодов в регистрах, а для реверса - как сумма кодов регистров за отсчет- ньш период. Максимальная угловая скорость изменения фазы составляет за половину периода опорного сигнала. 2 ил. с (Л 00 СП ро о ю 05

IllililJIII

lllllilLJJUJIilllUi

Illillllllilllin

.Li

Редактор Н.Бобкова

Составитель М.Сидорова. Техред М.Ходанич

Заказ 6009/57Тираж 900Подписное

ВНИИГШ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, А

11

Раг.2

Корректор М.Максимишинец

| Преобразователь угол-код | 1974 |

|

SU488242A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Преобразователь угла поворота вала в код | 1985 |

|

SU1272509A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-12-07—Публикация

1986-04-14—Подача