Изобретение относится к измерительной технике и может быть использовано в системах сбора и обработки информации с фазовым ее представлением.

11,елью изобретения является повышение точности преобразователя путем расширения пределов изменения дискретности определения фазы.

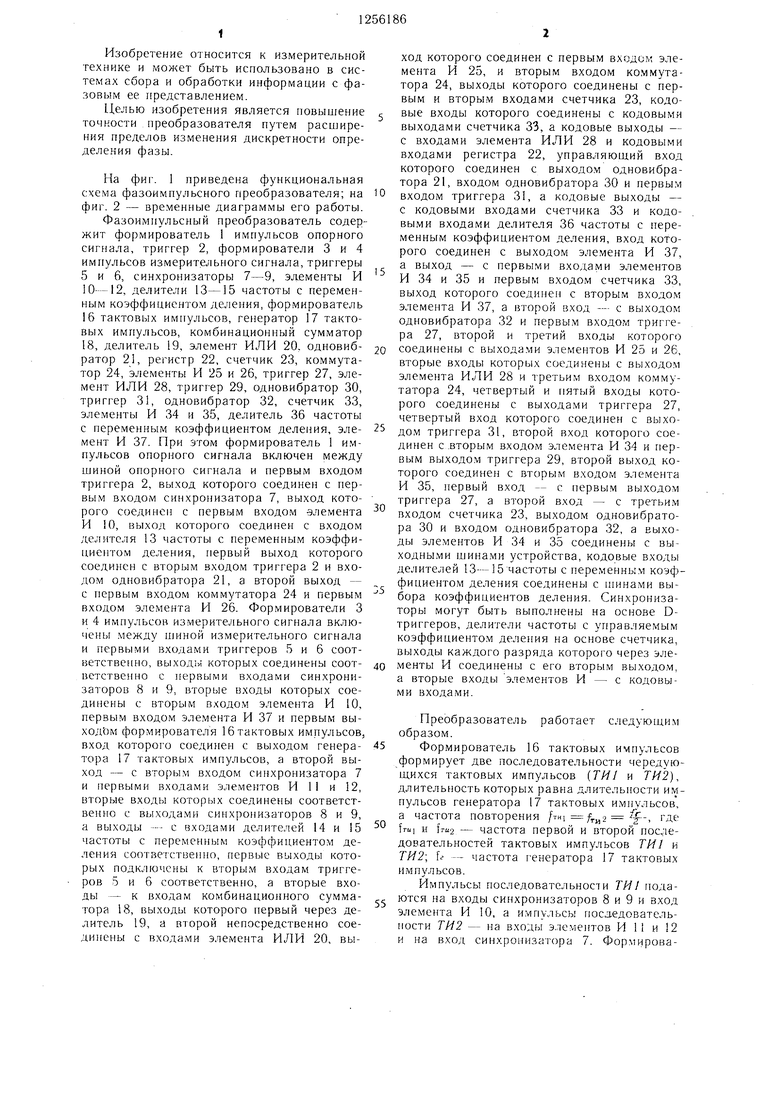

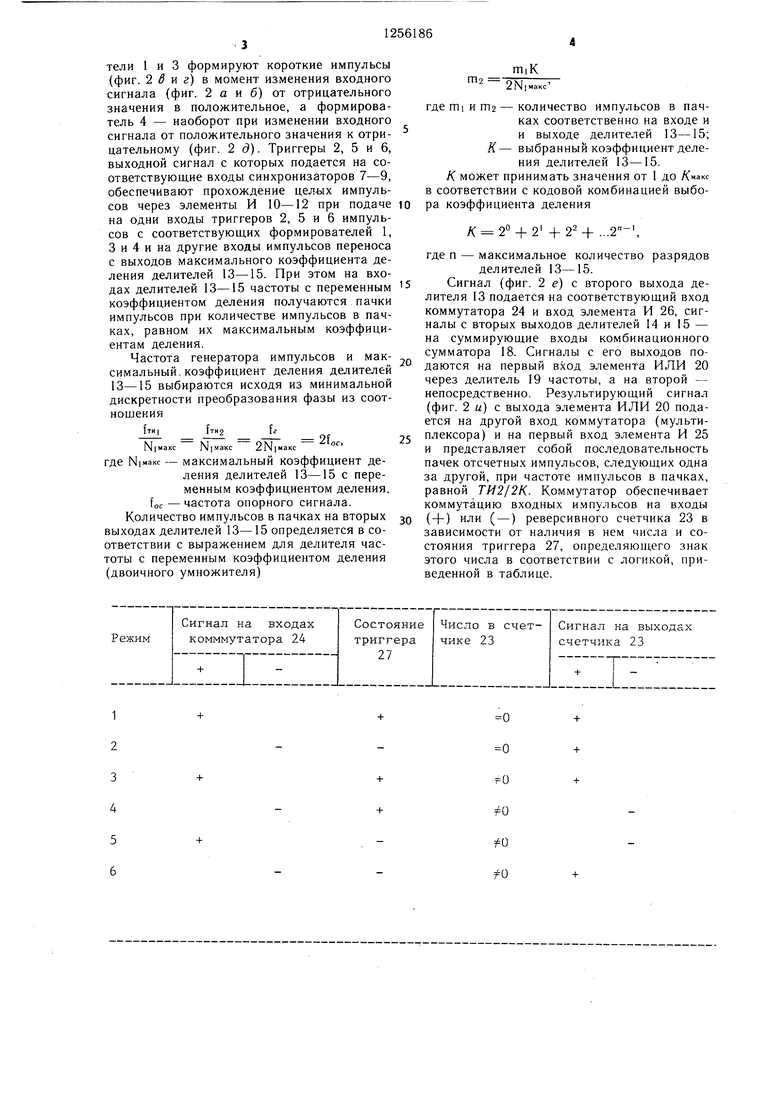

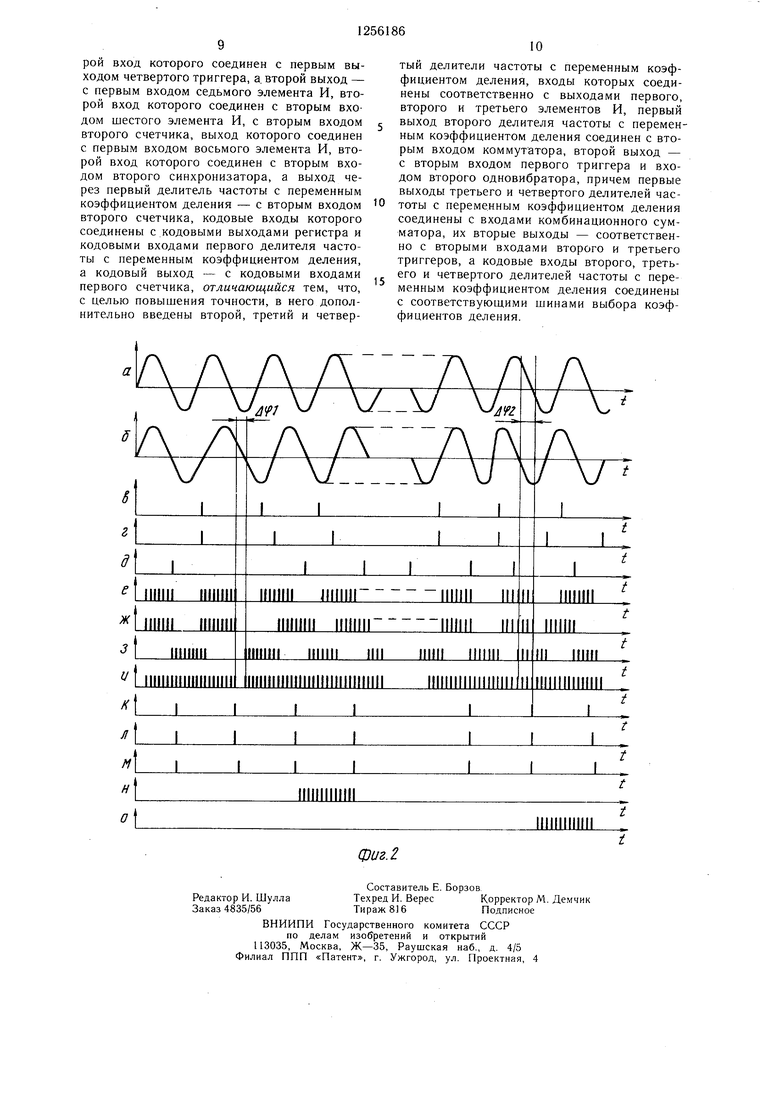

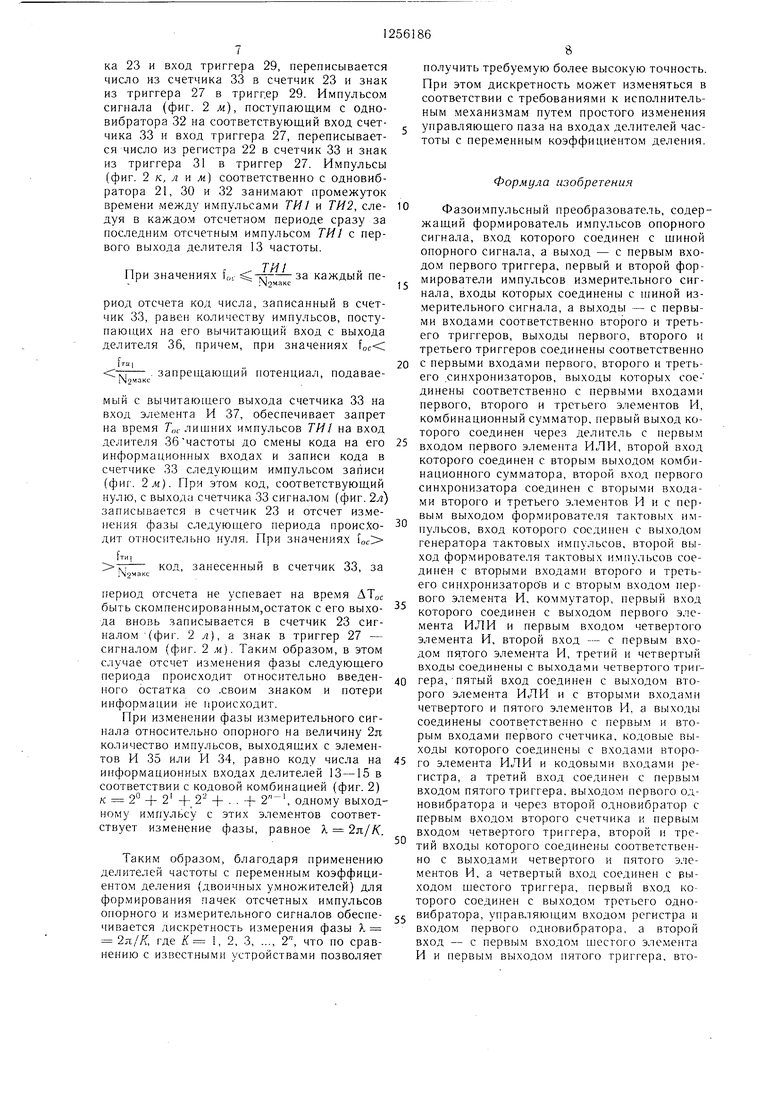

На фиг. 1 приведена функциональная схема фазоимпульсного преобразователя; на фиг. 2 - временные диаграммы его работы.

Фазоимпульсный преобразователь содержит формирователь 1 импульсов опорного сигнала, триггер 2, формирователи 3 и 4 импульсов измерительного сигнала, триггеры 5 и 6, синхронизаторы 7-9, элементы И 10-12, делители 13-15 частоты с переменным коэффициентом деления, формирователь 16 тактовых импульсов, генератор 17 тактовых импульсов, комбинационный сумматор 18, делитель 19, элемент ИЛИ 20. одновиб- ратор 21, регистр 22, счетчик 23, коммутатор 24, элементы И 25 и 26, триггер 27, элемент ИЛИ 28, триггер 29, одновибратор 30, триггер 31, одновибратор 32, счетчик 33, элементы И 34 и 35, делитель 36 частоты с переменным коэффициентом деления, эле- мент И 37. При этом формирователь 1 импульсов опорного сигнала включен между шиной опорного сигнала и первым входом триггера 2, выход которого соединен с первым входом синхронизатора 7, выход которого соединен с первым входом элемента И 0, выход которого соединен с входом делителя 13 частоты с переменным коэффициентом деления, первый выход которого соединен с вторым входом триггера 2 и входом одновибратора 21, а второй выход - с первым входом коммутатора 24 и первым входом элемента И 26. Формирователи 3 и 4 импульсов измерительного сигнала включены .между измерительного сигнала и первыми входами триггеров 5 и 6 соответственно, выходь которых соединены соот- ветственно с первыми входами синхронизаторов 8 и 9, вторые входы которых соединены с вторым входо.м элемента И 10, первым входом элемента И 37 и первым вы- ход ом формирователя 16 тактовых импульсов вход которого соединен с выходом генера- тора 17 тактовых импульсов, а второй выход - с вторым входом синхронизатора 7 и первь ми входами элементов И 11 и 12, вторые входы которых соединены соответственно с выходами синхронизаторов 8 и 9,

а выходы - с входами делителей 14 и 15

частоты с переменным коэ4)фициентом деления соответственно, первые выходы которых подключены к вторым входам триггеров 5 и 6 соответственно, а вторые входы - к входам комбинационного сумматора 18, выходы которого первый через делитель 19, а второй непосредственно соединены с входами элемента ИЛИ 20, вы

0 5 0 5

0

ход которого соединен с первым входом элемента И 25, и вторым входом коммутатора 24, выходы которого соединены с первым и вторым входами счетчика 23, кодовые входы которого соединены с кодовыми выходами счетчика 33, а кодовые выходы - с входами элемента ИЛИ 28 и кодовыми входами регистра 22, управляющий вход которого соединен с выходом одновибратора 21, входом одновибратора 30 и первь 1 входом триггера 31, а кодовые выходы - с кодовыми входами счетчика 33 и кодовыми входами делителя 36 частоты с переменным коэффициентом деления, вход которого соединен с выходом элемента И 37, а выход - с первыми входами элементов И 34 и 35 и первым входом счетчика 33, выход которого соединен с вторым входо.м элемента И 37, а второй вход - с выходом одновибратора 32 и первым входом триггера 27, второй и третий входы которого соединены с .ми элементов И 25 и 26, вторые входы которых соединены с выходом элемента ИЛИ 28 и третьим входом коммутатора 24, четвертый и пятый входы которого соединены с выходами триггера 27, четвертый вход которого соединен с выходом триггера 31, второй вход которого соединен с .вторым входом элемента И 34 и первым выходом триггера 29, второй выход которого соединен с вторым входом элемента И 35, первый вход - с первы.м выходом триггера 27, а второй вход - с третьи.м входом счетчика 23, выходом одновибратора 30 и входом одновибратора 32, а выходы элементов И 34 и 35 соединены с выходными шинами устройства, кодовые входы делителей 13-15 частоты с переменным коэффициентом деления соединены с шинами выбора коэффициентов деления. Синхронизаторы могут быть выполнены на основе D- триггеров, делители частоты с управляемым коэффициентом деления на основе счетчика, выходы каждого разряда которого через элементы И соединены с его вторым выходом, а вторые входы эле.ментов И - с кодовыми в хода .ми.

Преобразователь работает следующим образом.

Формирователь 16 тактовых импульсов формирует две последовательности чередуво- щихся тактовых импульсов (ТИ1 и ТИ2), длительность которых равна длительности импульсов генератора 17 тактовых импульсов, а частота повторения /ти н2 fri/i и fru2 - частота первой и второй последовательностей тактовых импульсов ТИ и ТИ2; г - частота генератора 17 тактовых импульсов.

Импульсы последовательности ТИ подаются на входы синхронизаторов 8 и 9 и вход элемента И 10, а импульсы последовательности ТИ2 - на входы элементов И 11 и 12 и на вход синхронизатора 7. Формирователи 1 и 3 формируют короткие импульсы (фиг. 2 в к г) в момент изменения входного сигнала (фиг. 2 а и б) от отрицательного значения в положительное, а формирователь 4 - наоборот при изменении входного сигнала от положительного значения к отрицательному (фиг. 2 с). Триггеры 2, 5 и 6, выходной сигнал с которых подается на соответствующие входы синхронизаторов 7-9, обеспечивают прохождение целых импулв- сов через элементы И 10-12 при подаче на одни входы триггеров 2, 5 и 6 импульсов с соответствующих формирователей 1, 3 и 4 и на другие входы импульсов переноса с выходов максимального коэффициента деления делителей 13-15. При этом на входах делителей 13-15 частоты с переменным коэффициентом деления получаются пачки импульсов при количестве импульсов в пачках, равном их максимальным коэффициентам деления.

Частота генератора импульсов и мак- симальный. коэффициент деления делителей 13-15 выбираются исходя из минимальной дискретности преобразования фазы из соотношения

Of

Ы|макс NlMaKC 2NlMaKC

где NIMBKC - максимальный коэффициент деления делителей 13-15 с переменным коэффициентом деления. foe - частота опорного сигнала. Количество импульсов в пачках на вторых выходах делителей 13-15 определяется в соответствии с выражением для делителя частоты с переменным коэффициентом деления (двоичного умножителя)

2 3 4 5 6

т2

miK

2NlMaKc

где mi и 012

количество импульсов в пачках соответственно на входе и и выходе делителей 13-15; К- выбранный коэффициент деления делителей 13-15. /С может принимать значения от 1 до /Смаке в соответствии с кодовой комбинацией выбора коэффициента деления

+ 2 +2 + ...,

где п - максимальное количество разрядов

делителей 13-15.

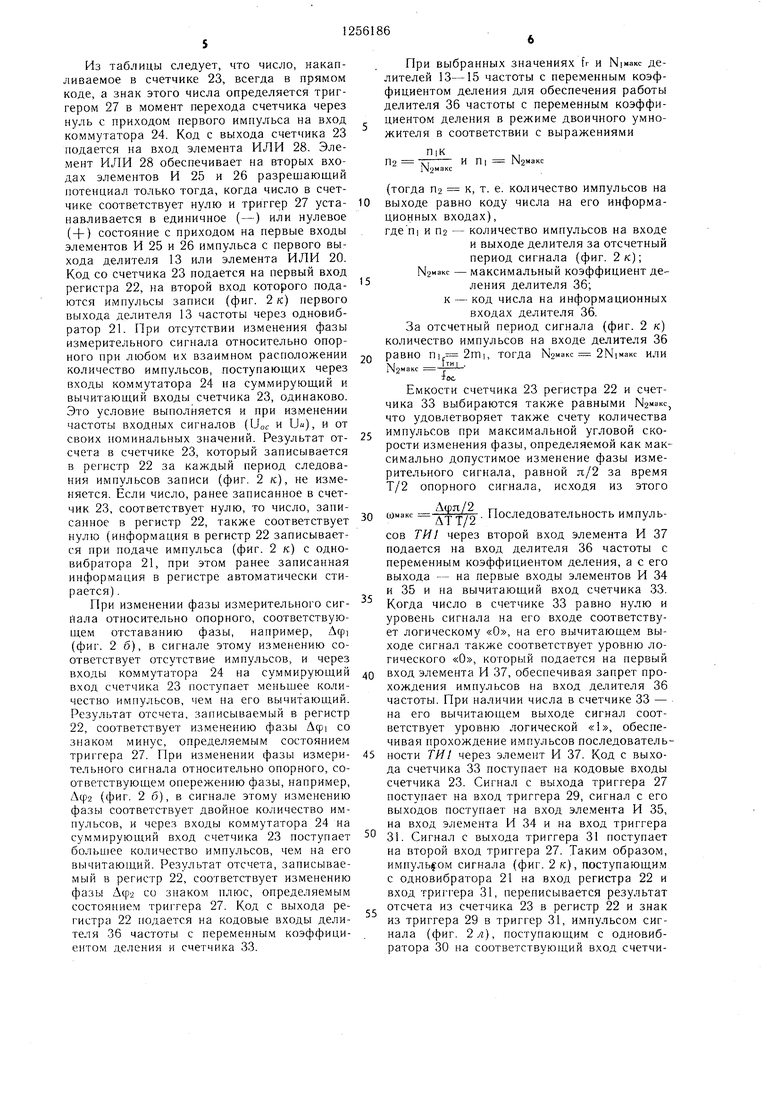

Сигнал (фиг. 2 е) с второго выхода делителя 13 подается на соответствующий вход коммутатора 24 и вход элемента И 26, сигналы с вторых выходов делителей 14 и 15 - на суммирующие входы комбинационного сумматора 18. Сигналы с его выходов подаются на первый вход элемента ИЛИ 20 через делитель 19 частоты, а на второй - непосредственно. Результирующий сигнал (фиг. 2 «) с выхода элемента ИЛИ 20 подается на другой вход коммутатора (мультиплексора) и на первый вход элемента И 25 и представляет собой последовательность пачек отсчетных импульсов, следующих одна за другой, при частоте импульсов в пачках, равной ТИ2/2К.. Коммутатор обеспечивает коммутацию входных и.мпульсов на входы (-|-) или (-) реверсивного счетчика 23 в зависимости от наличия в нем числа и состояния триггера 27, определяюнхего знак этого числа в соответствии с логикой, приведенной в таблице.

0 0

0

fO

Из таблицы следует, что число, накапливаемое в счетчике 23, всегда в прямом коде, а знак этого числа определяется триггером 27 в момент перехода счетчика через нуль с приходом первого импульса на вход коммутатора 24. Код с выхода счетчика 23 подается на вход элемента ИЛИ 28. Элемент ИЛИ 28 обеспечивает на вторых входах элементов И 25 и 26 разрешающий потенциал только тогда, когда число в счетчике соответствует нулю и триггер 27 устанавливается в единичное (-) или нулевое ( + ) состояние с приходом на первые входы элементов И 25 и 26 импульса с первого выхода делителя 13 или элемента ИЛИ 20. Код со счетчика 23 подается на первый вход регистра 22, па второй вход которого подаются импульсы записи (фиг. 2 к) первого выхода делителя 13 частоты через одновиб- ратор 21. При отсутствии изменения фазы измерительного сигнала относительно опорного при любом их взаимном расположении количество импульсов, поступающих через входы коммутатора 24 на суммирующий и вычитающий входы счетчика 23, одинаково. Это условие выполняется и при изменении частоты входных сигналов (IJoc и U), и от своих номинальных значений. Результат отсчета в счетчике 23, который записывается в регистр 22 за каждый период следования импульсов записи (фиг. 2 к), не изменяется. Если число, ранее записанное в счетчик 23, соответствует нулю, то число, записанное в регистр 22, также соответствует нулю (информация в регистр 22 записывается при подаче импульса (фиг. 2 к) с одно- вибратора 21, при этом ранее записанная информация в регистре автоматически стирается) .

При изменении фазы измерительного сигнала относительно опорного, соответствую- пдем отставанию фазы, например. Дер (фиг. 2 б), в сигнале этому из.менению соответствует отсутствие импульсов, и через входы коммутатора 24 на суммирующий вход счетчика 23 поступает меньшее количество импульсов, чем па его вычитающий. Результат отсчета, записываемый в регистр 22, соответствует изменению фазы Дф1 со знаком минус, определяемым состоянием триггера 27. При изменении фазы измерительного сигнала относительно опорного, соответствующем опережению фазы, например, АФ2 (фиг. 2 б), в сигнале этому изменению фазы соответствует двойное количество импульсов, и через входы коммутатора 24 на суммирующий вход счетчика 23 поступает большее количество импульсов, чем на его вычитающий. Результат отсчета, записываемый в регистр 22, соответствует изменению фазы ДФ2 со знаком плюс, определяемым состоянием триггера 27. Код с выхода регистра 22 подается на кодовые входы делителя 36 частоты с переменным коэффициентом деления и счетчика 33.

При выбранных значениях fr и NixaKc делителей 13-15 частоты с переменным коэффициентом деления для обеспечения работы делителя 36 частоты с переменным коэффициентом деления в режиме двоичного умножителя в соответствии с выражениями

niK

Па -ГТ и П| N2MaKC

i 2M3Kc

(тогда П2 к, т. е. количество импульсов на выходе равно коду числа на его информационных входах),

где П| и П2 - количество импульсов на входе и выходе делителя за отсчетный период сигнала (фиг. 2 к); N2MaKc - максимальный коэффициент деления делителя 36; к - код числа на информационных

входах делителя 36.

За отсчетный период сигнала (фиг. 2 к) количество импульсов на входе делителя 36 равно П1.. 2ш1, тогда К 2макс 2Ы|макс или

N2M3KC J

Емкости счетчика 23 регистра 22 и счетчика 33 выбираются также равными NaxaKc что удовлетворяет также счету количества импульсов при максимальной угловой скорости изменения фазы, определяемой как максимально допустимое из.менение фазы измерительного сигнала, равной л/2 за время Т/2 опорного сигнала, исходя из этого

сомакс дХ „/.„ . Последовательность импуль

0

сов ТИ1 через второй вход элемента И 37 подается на вход делителя 36 частоты с переменным коэффициентом деления, а с его выхода - на первые входы элементов И 34 и 35 и на вычитающий вход счетчика 33. Когда число в счетчике 33 равно нулю и уровень сигнала на его входе соответствует логическому «О, на его вычитающем выходе сигнал также соответствует уровню логического «О, который подается на первый вход элемента И 37, обеспечивая запрет прохождения импульсов на вход делителя 36 частоты. При на.тичии числа в счетчике 33 - па его вычитающем выходе сигнал соответствует уровню логической «1, обеспечивая прохождение импульсов последователь5 ности ТИ1 через элемент И 37. Код с выхода счетчика 33 поступает на кодовые входы счетчика 23. Сигнал с выхода триггера 27 поступает на вход триггера 29, сигнал с его выходов поступает на вход элемента И 35, на вход элемента И 34 и на вход триггера

31. Сигнал с выхода триггера 31 поступает на второй вход триггера 27. Таким образом, импульсом сигнала (фиг. 2 к), поступающим с одновибратора 21 на вход регистра 22 и вход триггера 31, переписывается результат отсчета из счетчика 23 в регистр 22 и знак из триггера 29 в триггер 31, импульсом сигнала (фиг. 2л), поступающим с одновибратора 30 на соответствующий вход счетчика 23 и вход триггера 29, переписывается число из счетчика 33 в счетчик 23 и знак из триггера 27 в триггер 29. Импульсом сигнала (фиг. 2 м), поступающим с одно- вибратора 32 на соответствующий вход счетчика 33 и вход триггера 27, переписывается число из регистра 22 в счетчик 33 и знак из триггера 31 в триггер 27. Импульсы (фиг. 2 к, л и м) соответственно с одновиб- ратора 21, 30 и 32 зани.мают промежуток времени между импульсами ТИ и ТИ2, еле- дуя в каждом отсчетном периоде сразу за последним отсчетным импульсом ТИ 1 с первого выхода делителя 13 частоты.

При значениях

ТИ1

за каждый период отсчета код числа, записанный в счетчик 33, равен количеству импульсов, поступающих на его вычитающий вход с выхода делителя 36, причем, при значениях foc

17 I N2

. запрещающий потенциал, подавае

код, занесенный в счетчик 33, за

мый с вычитающего выхода счетчика 33 на вход элемента И 37, обеспечивает запрет на время 7„с лишних импульсов ТИ на вход делителя 36 частоты до смены кода на его информационных входах и записи кода в счетчике 33 следующим импульсом записи (фиг. 2м). При этом код, соответствующий нулю, с выхода счетчика 33 сигналом (фиг. 2л) записывается в счетчик 23 и отсчет изменения фазы сле;1,ующего периода проис со- дит относительно нуля. При значениях ioc

| тИ1

г ериод отсчета не успевает на время АТос быть скомпенсированны.м,остаток с его выхода вновь записывается в счетчик 23 сигналом (фиг. 2 тг), а знак в триггер 27 - сигналом (фиг. 2 м). Таким образом, в этом случае отсчет изменения фазы следующего периода происходит относительно введен- ного остатка со .своим знаком и потери информации не происходит.

При изменении фазы измерительного сигнала относительно опорного на величину 2л количество импульсов, выходящих с элементов И 35 или И 34, равно коду числа на информационных входах делителей 13-15 в соответствии с кодовой комбинацией (фиг. 2) к 2° 4- 2 +,2 + . . + , одному выходному импульсу с этих элементов соответствует изменение фазы, равное Я. 2л/К.

Таким образом, благодаря применению делителей частоты с переменным коэффициентом деления (двоичных умножителей) для формирования пачек отсчетных импульсов опорного и измерительного сигналов обеспе- чивается дискретность измерения фазы К 2л/К, где . 1, 2, 3, ..., 2, что по сравнению с известными устройствами позволяет

получить требуемую более высокую точность. При этом дискретность может изменяться в соответствии с требованиями к исполнительным механизмам путем простого изменения управляющего паза на входах делителей частоты с переменным коэффициентом деления.

10

15

20

5 0

5

Q

5

Формула изобретения

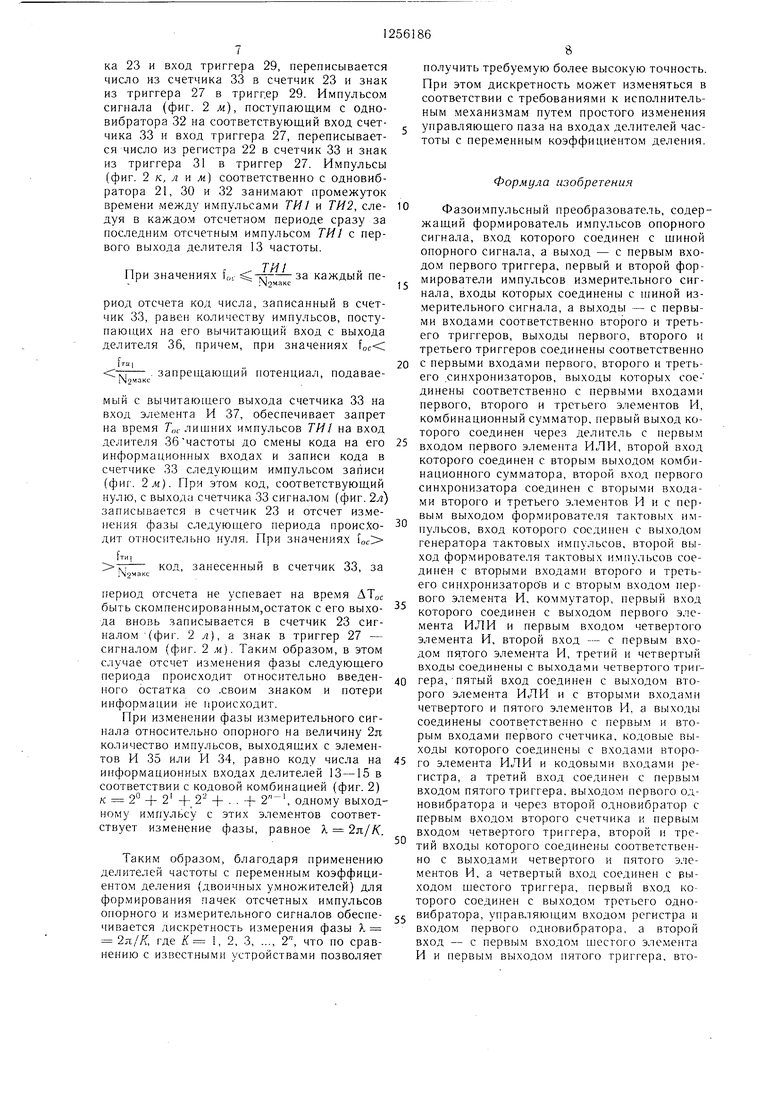

Фазоимпульсный преобразователь, содержащий формирователь импульсов опорного сигнала, вход которого соединен с шиной опорного сигнала, а выход - с первым входом первого триггера, первый и второй формирователи импульсов измерительного сигнала, входы которых соединены с шиной из- .мерительного сигнала, а выходы - с первыми входа.ми соответственно второго и третьего триггеров, выходы первого, второго и третьего триггеров соединены соответственно с первыми входами первого, второго и третьего синхронизаторов, выходы которых сое- динены соответственно с первыми входами первого, второго и третьего элементов И, комбинационный сумматор, первый выход которого соединен через делитель с первым входом первого элемента ИЛИ, второй вход которого соединен с вторым выходом комбинационного сумматора, второй вход первого синхронизатора соединен с вторыми входами второго и третьего элементов И и с первым выходом формирователя тактовых импульсов, вход которого соединен с выходом генератора тактовых импульсов, второй выход формирователя тактовых импульсов соединен с вторыми входами второго и третьего синхронизаторов и с вторым входом первого элемента И, коммутатор, первый вход которого соединен с выходом первого элемента ИЛИ и первым входом четвертого элемента И, второй вход - с первым входом пятого элемента И, третий и четвертый входы соединены с выхода.ми четвертого триггера, пятый вход соединен с выходом второго элемента ИЛИ и с вторыми входами четвертого и пятого элементов И, а выходы соединены соответственно с первы.м и вторым входами первого счетчика, кодовые выходы которого соединены с входами второго элемента ИЛИ и кодовыми входами регистра, а третий вход соединен с первым входом пятого триггера, выходом первого од- новибратора и через второй одновибратор с первым входом второго счетчика и первым входо.м четвертого триггера, второй и третий входы которого соединены соответственно с выходами четвертого и пятого элементов И, а четвертый вход соединен с ры- ходом шестого триггера, первый вход которого соединен с выходом третьего одно- вибратора, уиравляюкцим входом регистра и входом первого одновибратора, а второй вход - с первым входо.м шестого элеме1гга И и первым выходом пятого триггера, второй вход которого соединен с первым выходом четвертого триггера, а. второй выход - с первым входом седьмого элемента И, второй вход которого соединен с вторым входом шестого элемента И, с вторым входом второго счетчика, выход которого соединен с первым входом восьмого элемента И, второй вход которого соединен с вторым входом второго синхронизатора, а выход через первый делитель частоты с переменным коэффициентом деления - с вторым входом второго счетчика, кодовые входы которого соединены с кодовыми выходами регистра и кодовыми входами первого делителя частоты с переменным коэффициентом деления, а кодовый выход - с кодовыми входами первого счетчика, отличающийся тем, что, с целью повышения точности, в него дополнительно введены второй, третий и четвертый делители частоты с переменным коэффициентом деления, входы которых соединены соответственно с выходами первого, второго и третьего элементов И, первый

выход второго делителя частоты с переменным коэффициентом деления соединен с вторым входом коммутатора, второй выход - с вторым входом первого триггера и входом второго одновибратора, причем первые выходы третьего и четвертого делителей частоты с переменным коэффициентом деления соединены с входами комбинационного сумматора, их вторые выходы - соответственно с вторыми входами второго и третьего триггеров, а кодовые входы второго, третьего и четвертого делителей частоты с переменным коэффициентом деления соединены с соответствующими шинами выбора коэффициентов деления.

f

| название | год | авторы | номер документа |

|---|---|---|---|

| Фазоимпульсный преобразователь | 1983 |

|

SU1161977A1 |

| Преобразователь сдвига фазы в код скорости и ускорения | 1986 |

|

SU1358096A1 |

| Преобразователь угла поворота вала в код | 1985 |

|

SU1272509A1 |

| Преобразователь угла поворота вала в код | 1983 |

|

SU1108482A2 |

| Преобразователь угла поворота вала в код | 1981 |

|

SU1013998A1 |

| Умножитель частоты | 1990 |

|

SU1797113A1 |

| Устройство для программного управления | 1981 |

|

SU987579A1 |

| Устройство для программного управления с самоконтролем | 1983 |

|

SU1130832A1 |

| Преобразователь частота-код | 1987 |

|

SU1515368A1 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

Изобретение относится к измерительной технике и может быть использовано в системах сбора и обработки информации с фазовым ее представлением. Цель изобретения - повышение точности преобразователя. Устройство содержит формирователь 1 импульсов опорного сигнала, триггеры 2, 5, 6, 27, 29 и 31, формирователи 3 и 4 импульсов измерительного сигнала, синхронизаторы 7, 8 и 9, элементы И 10, 11, 12, 25, 26, 34, 35 и 37, делитель 36 частоты с переменным коэффициентом деления, формирователь 16 тактовых импульсов, генератор 17 тактовых импульсов, комбинационный сумматор 18, делитель 19, элементы ИЛИ 20 и 28, одно- вибраторы 21, 30 и 32, регистр 22, счетчики 23 и 33 и коммутатор 24. Введение делителей 13, 14 и 15 частоты с переменным коэффициентом деления и образование новых связей между элементами устройства расширяет пределы изменения дискретности определения фазы. 2 ил., 1 табл. S (Л 1C ел о: 00 05 фиг.1

тип ПНИН

ж

IIIHH НННН

1Ш1Н11ШШ1Ш

и

IIHHilHIIHHHIH

11МН1ННННН11ПММ1Н111

Редактор И. Шулла Заказ 4835/56

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП «Патент, г. Ужгород, ул. Проектная, 4

III 1МП1

и

tlllllllMIHII

Составитель Е. Борзов.

Техред И. ВересКорректор М. Демчик

Тираж 8) 6Подписное

| ПРЕОБРАЗОВАТЕЛЬ ФАЗА - ПОСЛЕДОВАТЕЛЬНОСТЬИМПУЛЬСОВ | 1971 |

|

SU416722A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-09-07—Публикация

1984-11-26—Подача