Изобретение относится к вычислительной технике, может быть использовано для контроля состояния контроллера или другого устройства, содержащего микропроцессор, при включении или сбоях питания и является усовершенствованием авт.св. № 11551972,

Целью изобретения является повышение достоверности функционирования устройства при сбоях его напряжения питания.

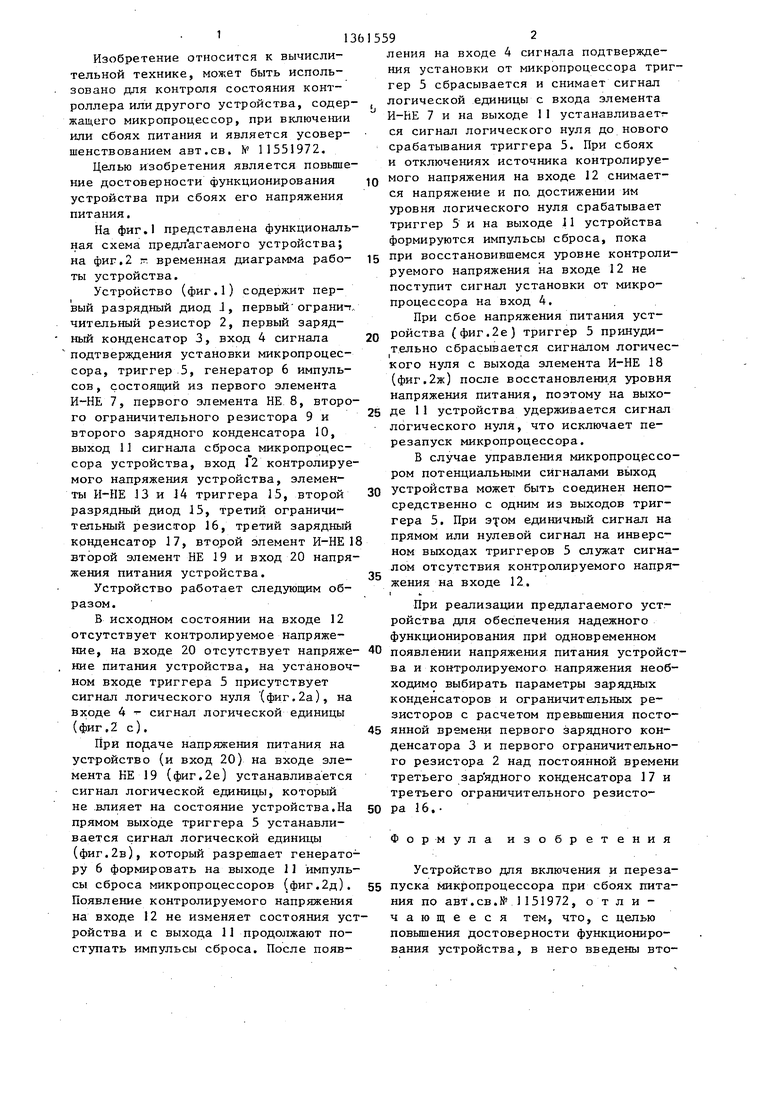

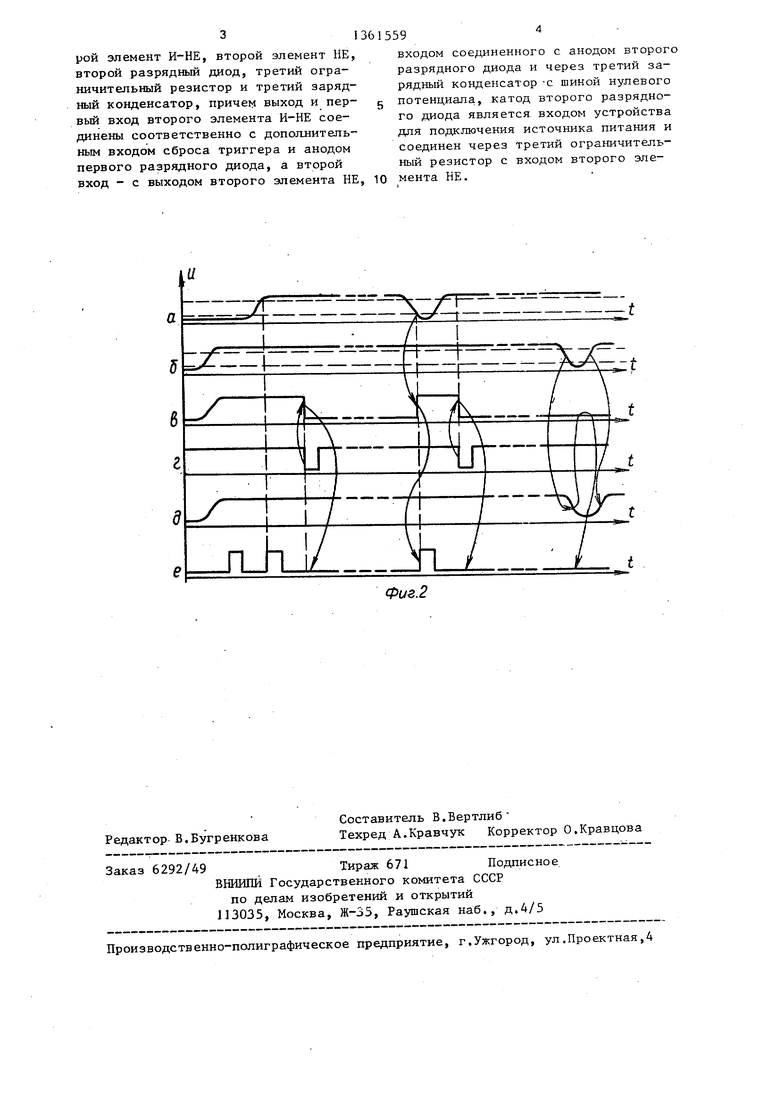

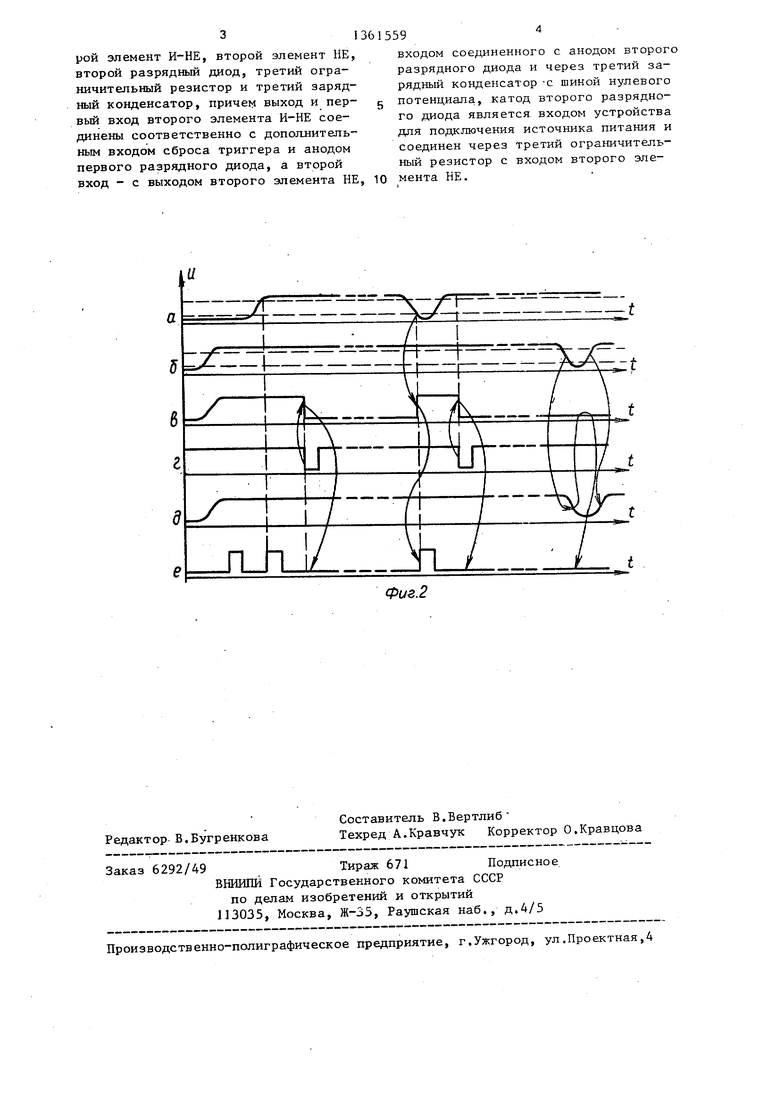

На фиг.1 представлена функциональная схема предл агаемого устройства; на фиг.2 г. временная диаграмма работы устройства.

Устройство (фиг.1) содержит первый разрядный диод J, первый огранит, чительный резистор 2, первый зарядный конденсатор 3, вход 4 сигнала подтверждения установки микропроцессора, триггер 5, генератор 6 импульсов , состоящий из первого элемента И-НЕ 7, первого элемента НЕ 8, второго ограничительного резистора 9 и второго зарядного конденсатора 10, выход П сигнала сброса микропроцессора устройства, вход 12 контролируемого напряжения устройства, элементы И-НЕ 13 и J4 триггера 15, второй разрядный диод 15, третий ограничительный резистор 16, третий зарядный конденсатор 17, второй элемент И-НЕ 1 второй элемент НЕ 19 и вход 20 напряжения питания устройства.

Устройство работает следующим образом.

В исходном состоянии на входе 12 отсутствует контролируемое напряжение, на входе 20 отсутствует напряже- ние питания устройства, на установочном входе триггера 5 присутствует сигнал логического нуля {фиг.2а), на входе 4 сигнал логической единицы (фиг.2 с).

При пораче напряжения питания на устройство (и вход 20) на входе элемента НЕ 19 (фиг.2е) устанавливается сигнал логической единицы, который не .влияет на состояние устройства.На прямом выходе триггера 5 устанавливается сигнал логической единицы (фиг.2в), который разрешает генератору 6 формировать на выходе 11 импульсы сброса микропроцессоров (фиг.2д). Появление контролируемого напряжения на входе 12 не изменяет состояния устройства и с выхода 1 продолжают поступать импульсы сброса. После появ

10

15

20

25

30

, 83615592

ления на входе 4 сигнала подтверждения установки от микропроцессора триггер 5 сбрасывается и снимает сигнал логической единицы с входа элемента И-НЕ 7 и на выходе 1 1 устанавливаетг- ся сигнал логического нуля до нового срабатывания триггера 5. При сбоях и отключениях источника контролируемого напряжения на входе 12 снимается напряжение и по. достижении им уровня логического нуля срабатывает триггер 5 и на выходе J1 устройства формируются импульсы сброса, пока при восстановившемся уровне контролируемого напряжения на входе I2 не поступит сигнал установки от микропроцессора на вход 4.

При сбое напряжения питания устройства (фиг.2е) триггер 5 принудительно сбрасывается сигналом логического нуля с выхода элемента И-НЕ 18 (фиг.2ж) после восстановления уровня напряжения питания, поэтому на выходе 11 устройства удерживается сигнал логического нуля, что исключает перезапуск микропроцессора.

В случае управления микропроцессором потенциальными сигналами выход устройства может быть соединен непосредственно с одним из выходов триггера 5. При единичный сигнал на прямом или нулевой сигнал на инверсном выходах триггеров 5 служат сигналом отсутствия контролируемого напряжения на входе 12.

35

При реализации предлагаемого устройства для обеспечения надежного функционирования при одновременном появлении напряжения питания устройства и контролируемого напряжения необходимо выбирать параметры зарядных конденсаторов и ограничительных резисторов с расчетом превьш1ения посто- янной времени первого зарядного конденсатора 3 и первого ограничительного резистора 2 над постоянной времени третьего зар ядного конденсатора 17 и третьего ограничительного резистора 16,

Формула изобретения

Устройство для включе1шя и перезапуска микропроцессора при сбоях питания по авт.св.№1151972, от л и - чающееся тем, что, с целью повьш1ения достоверности функционирования устройства, в него введены вто31

рой элемент И-НЕ, второй элемент НЕ, второй разрядный диод, третий ограничительный резистор и третий зарядный конденсатор, причеь выход и первый вход второго элемента И-НЕ соединены соответственно с дополлитель- ным входом сброса триггера и анодом первого разрядного диода, а второй вход - с выходом второго элемента НЕ

61559

входом соединенного с анодом второго разрядного диода и через третий зарядный конденсатор -с шиной нулевого с потенциала, катод второго разрядного диода является входом устройства для подключения источника питания и соединен через третий ограничительный резистор с входом второго эле- 10 мента НЕ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для включения и перезапуска микропроцессора при сбоях питания | 1983 |

|

SU1151972A1 |

| Устройство для выключения и перезапуска микропроцессора при сбоях питания | 1986 |

|

SU1352492A1 |

| Устройство для включения и перезапуска микропроцессора при сбоях питания | 1987 |

|

SU1474653A1 |

| Устройство для включения и перезапуска микропроцессора при сбоях питания | 1982 |

|

SU1061147A1 |

| Устройство для выключения и перезапуска микропроцессора при сбоях питания | 1988 |

|

SU1509904A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ФУНКЦИОНИРОВАНИЯ БЛОКА ОБРАБОТКИ ДАННЫХ | 1998 |

|

RU2143727C1 |

| Устройство для перезапуска и контроля электропитания микроЭВМ | 1989 |

|

SU1797122A1 |

| УПРАВЛЯЕМЫЙ ГЕНЕРАТОР ИМПУЛЬСОВ | 2003 |

|

RU2254670C1 |

| УПРАВЛЯЕМЫЙ ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ | 2004 |

|

RU2257003C1 |

| ПИКОВЫЙ ДЕТЕКТОР | 2009 |

|

RU2409818C1 |

Изобретение относится к вычислительной технике и может быть использовано для контроля состояния контроллера или другого устройства, содержащего микропроцессор, при включении или сбоях питания. Целью изобретения является повышение достоверности функционирования устройства. Для этого в устройство, содержащее первый разрядный диод 1, первый ограничительный резистор 2, первый зарядный конденсатор 3, вход 4 сигнала подтверж- . дения установки микропроцессора, триггер 5, генератор 6 импульсов,состоящий из первого элемента И-НЕ 7, первого элемента НЕ 8, второго ограничительного резистора 9 и второго зарядного конденсатора 10, выход 1J сигнала сброса микропроцессора устройства, вход 12 контролируемого напряжения устройства, элементы И-НЕ 13 и 14 триггера 5, введены второй разрядный диод IS, третий зарядный конденсатор 17, третий ограничительный резистор 16, второй элемент И-НЕ 18 и второй элемент НЕ 19. Изобретение исключает возможность лишнего перезапуска микропроцессора путем принудительной установки триггера в нулевое исходное состояние при восстановлении напряжения питания устройства после его сбоя. 2 ил. Ф о:) О: сл ел 1М ФигЛ

Редактор Б.Бугренкова

Составитель В.Вертлиб

Техред А.Кравчук Корректор О.Кравцова

Заказ 6292/49Тираж 671Подписное.

ВНИШ1И Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

«...-. - - - «. -----------

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

Фиг.2

| Устройство для включения и перезапуска микропроцессора при сбоях питания | 1983 |

|

SU1151972A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-12-23—Публикация

1986-07-25—Подача