Изобретение относится к вычислительной технике и может быть использовано для контроля правильности работы системы обработки данных или отдельных ее частей, базирующихся, в основном, на микропроцессорах, микроконтроллерах и т.п.

При работе систем обработки данных, особенно при воздействии источников помех, возможны сбои и отказы системы, приводящие к нарушению ее нормального функционирования. При этом наиболее часто причинами нарушения нормального функционирования являются нарушения корректного выполнения команд, пропуски или основания лишних машинных циклов, нарушения соответствия сигналов на шине адреса и управления текущей командой и т.д. Возможны также нарушения нормального функционирования системы обработки данных вследствие "зависания" процессора при обращении к внешнему устройству, зацикливания отдельного участка выполняемой программы и пр.

В связи с этим возникает необходимость осуществлять проверку блока обработки данных, в частности - микропроцессора, во время его функционирования на отсутствие ошибок и сбоев в ходе выполнения программы.

Одним из путей контроля корректности процесса выполнения программы является использование независимого внешнего устройства, которое регулярно запускается сигналом, формируемым контролируемым блоком обработки данных в определенных местах программы. Если этот сигнал из-за ошибок в аппаратном или программном обеспечении не появляется в определенном временном интервале, то внешнее контролирующее устройство вырабатывает сигнал ошибки. Чаще всего указанный сигнал ошибки используется для возврата контролируемого блока обработки данных к началу реализуемой программы с целью повторного ее выполнения, то есть в качестве сигнала RESET, устанавливающего контролируемый блок в определенное исходное состояние.

Очевидно, что для выполнения указанной функции устройство для контроля функционирования блока обработки данных должно содержать технические средства, обеспечивающие формирование сигналов, следующих через определенные и заранее заданные промежутки времени и задающих границы временного интервала, внутри которого на вход устройства для контроля должен поступить сигнал запуска, устанавливающий его в исходное состояние и вырабатываемый проверяемым блоком при корректном выполнении программы.

Известны устройства для контроля функционирования блока обработки данных, в которых формирователи временных интервалов выполнены в виде пересчетных схем, реализованных на дискретных элементах.

Одно из подобных устройств описано в патенте ФРГ N 4329872, кл. G 06 F 11/30, опубл. 1995. В этом устройстве формирователь временных интервалов выполнен в виде двоичного счетчика, связанного с генератором импульсов, причем входом запуска этого формирователя является вход сброса счетчика.

Данное устройство обеспечивает формирование сигнала запроса ответного сигнала контролируемого микропроцессора, поступающего на вход сброса двоичного счетчика и возвращающего формирователь временных интервалов в исходное состояние, и формирование сигнала RESET при отсутствии ответного сигнала микропроцессора. К недостаткам этого устройства следует отнести, в частности, невозможность выявления случая формирования проверяемым блоком ошибочного ответного сигнала, предшествующего сигналу запроса.

Из патента США N 5542051, кл. G 06 F 11/34 (НКИ 395/185.04) опубл. 1996, известно устройство для контроля блока обработки данных, в котором формирователь временного интервала выполнен в виде пересчетной схемы, реализованной на регистре сдвига. Это устройство обеспечивает выявление случаев как преждевременного формирования контролируемым блоком ответного сигнала, так и отсутствия ответного сигнала в пределах заданного временного интервала, однако требует более тесного взаимодействия с проверяемым блоком, на который возлагается выполнение некоторых сервисных функций.

Общим недостатком указанных выше устройств является и их относительная сложность, обусловленная, в частности, наличием необходимого для обеспечения их работоспособности отдельного генератора тактовых импульсов.

Наиболее близким к заявленному изобретению по технической сущности и достигаемому результату является известное из патента ФРГ N 3335548, кл. G 06 F 11/30, опубл. 1985, устройство для контроля функционирования блока обработки данных, содержащее реализованные на одновибраторах первый и второй формирователи временного интервала, входы запуска которых объединены и являются входом устройства. В этом устройстве прямой выход первого формирователя временного интервала является выходом сигнала запроса, а один из выходов второго формирователя временного интервала - выходом сигнала ошибки.

Недостаток этого устройства заключается в том, что оно не обеспечивает формирование сигнала ошибки в случае появления на соответствующем выходе проверяемого блока обработки данных ошибочного лишнего ответного сигнала, предшествующего очередному сигналу запроса.

Задачей данного изобретения является обеспечение возможности формирования сигнала ошибки как в случае появления на соответствующем выходе контролируемого блока обработки данных ошибочного лишнего ответного сигнала, предшествующего очередному сигналу запроса, так и в случае отсутствия ответного сигнала в пределах заданного временного интервала, при достаточно простой аппаратурной реализации устройства для контроля функционирования блока обработки данных.

Указанный технический результат достигается тем, что в устройство для контроля функционирования блока обработки данных, содержащее первый и второй формирователи временного интервала, входы запуска которых объединены и являются входом устройства, прямой выход первого формирователя временного интервала является выходом сигнала запроса, а один из выходов второго формирователя временного интервала - выходом сигнала ошибки, введены времязадающий элемент и элемент задержки, а каждый из формирователей временного интервала содержит D-триггер и времязадающий элемент, выход которого подключен к R-входу D-триггера, а вход является входом сброса формирователя, прямой и инверсный выходы D-триггера являются прямым и инверсным выходами формирователя, установочным и информационным входами которого являются соответственно S-вход и D-вход D-триггера, C-вход которого является входом запуска формирователя временного интервала, вход сброса и прямой выход первого формирователя временного интервала соединены между собой, а инверсный выход этого формирователя подключен через элемент задержки к информационному входу и непосредственно - к входу сброса второго формирователя временного интервала, инверсный выход которого связан с входом времязадающего элемента, подсоединенного своим выходом к установочным входам первого и второго формирователей временного интервала, причем информационный вход первого формирователя временного интервала подключен к источнику сигнала логической единицы, например к соответствующей шине питания.

С целью повышения надежности работы устройства для контроля функционирования блока обработки данных за счет обеспечения требуемого порядка установки первого и второго формирователей временного интервала в исходное состояние выход времязадющего элемента связан с установочным входом второго формирователя временного интервала через резистор.

При некоторых конкретных реализациях отдельных частей устройства для контроля функционирования блока обработки данных после включения питания возможно появление на R- и S-входах D-триггеров, входящих в состав формирователей временного интервала, сигналов единичного уровня, которые могут привести некоторые типы D-триггеров в запрещенное состояние, характеризуемое наличием сигналов единичного уровня на прямом и инверсном выходах этих триггеров.

Для исключения указанного эффекта в устройство для контроля функционирования блока обработки данных введен дополнительный элемент задержки, вход которого подключен к шине питания, а выход подсоединен к выходу времязадающего элемента через первый развязывающий диод, включенный встречно напряжению питания.

Выше упоминалось, что вырабатываемый устройством для контроля функционирования блока обработки данных сигнал ошибки в большинстве практических случаев используют в качестве сигнала RESET, обеспечивающего установку проверяемого блока в определенное исходное состояние. Наряду с этим необходимость в формировании сигнала RESET возникает и при включении питания блока обработки данных, работающего совместно с устройством для контроля его функционирования.

В данном изобретении обеспечение возможности формирования сигнала RESET не только при появлении сигнала ошибки, но и при включении питания достигается тем, что в устройство для контроля функционирования блока обработки данных введен генератор одиночного импульса, вход которого соединен с шиной питания, а выход является выходом сигнала RESET устройства и связан с инверсным выходом второго формирователя временного интервала через включенный встречно второй развязывающий диод.

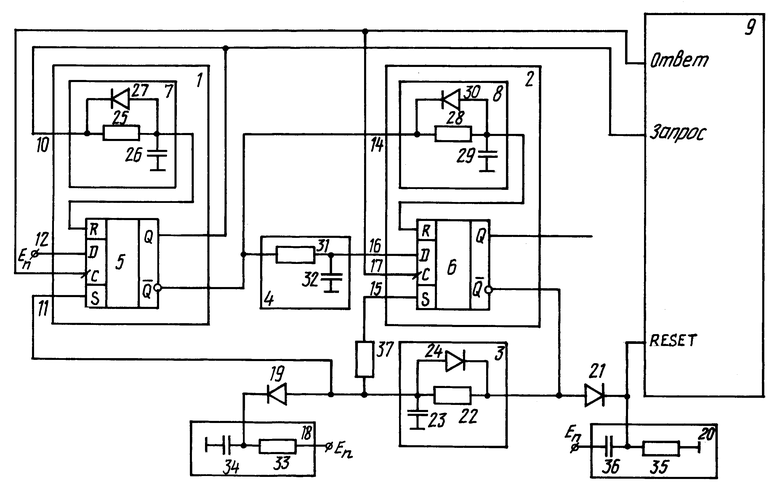

На чертеже представлена схема наиболее экономичного варианта устройства для контроля функционирования блока обработки данных, выполненного согласно данному изобретению.

Устройство для контроля функционирования блока обработки данных содержит первый 1 и второй 2 формирователи временного интервала, времязадающий элемент 3 и элемент 4 задержки. В состав каждого из формирователей 1 и 2 временного интервала входят D-триггер 5 и соответственно 6, а также времязадающий элемент 7 или соответственно 8.

Позицией 9 на чертеже условно показан блок обработки данных, для контроля функционирования которого используется данное изобретение.

На чертеже обозначены вход 10 (14) сброса, установочный вход 11 (15), информационный вход 12 (16) и вход 13 (17) запуска первого (второго) формирователя 7 (8) временного интервала.

Кроме того, на чертеже показаны используемые в частных случаях выполнения устройства дополнительный элемент 18 задержки, первый развязывающий диод 19, генератор 20 одиночного импульса и второй развязывающий диод 21.

Конструкция данного устройства допускает использование различных конкретных реализаций входящих в него частей.

Например, в качестве времязадающих элементов 3, 7 и 8 могут быть использованы одновибраторы с задержкой, в качестве элементов 4 и 18 задержки - цепочки последовательно соединенных инверторов, а в качестве генератора 20 - любой генератор одиночного импульса, формирующий на своем выходе импульс единичного уровня и заданной длительности.

В представленном примере конкретного выполнения устройства для контроля функционирования блока обработки данных, использующего D-триггеры микросхемы 561ТМ2, все остальные части этого устройства реализованы на пассивных элементах.

Времязадающие элементы 3, 7 и 8 выполнены в виде интегрирующих RC-цепочек, представляющих собой последовательно соединенные резистор и конденсатор, общая точка соединения которых является выходом элемента, другой вывод резистора является входом элемента, а другой вывод конденсатора связан с общей шиной устройства, причем резистор зашунтирован диодом, обеспечивающим ускоренный разряд конденсатора при спаде сигнала на входе элемента.

Времязадающий элемент 3 содержит резистор 22, конденсатор 23 и диод 24, времязадающий элемент 7 - резистор 25, конденсатор 26 и диод 27, а времязадающий элемент 8 - резистор 28, конденсатор 29 и диод 30.

Элементы 4 и 18 задержки также выполнены в виде интегрирующих RC-цепочек, реализованных аналогично описанным выше, но без шунтирующих диодов, причем элемент 4 содержит резистор 31 и конденсатор 32, а элемент 18 - резистор 33 и конденсатор 34.

Генератор 20 одиночного импульса представляет собой дифференцирующую RC-цепочку, состоящую из последовательно соединенных резистора 35 и конденсатора 36, общая точка соединения которых является выходом генератора, другой вывод конденсатора является входом генератора, а другой вывод резистора связан с общей шиной устройства.

Обеспечивающий требуемый порядок установки в исходное состояние первого 1 и второго 2 формирователей временного интервала резистор, необходимый при вышеизложенной реализации частей устройства с использованием пассивных элементов, обозначен на чертеже позицией 37.

Подключение данного устройства для контроля к проверяемому блоку обработки данных может быть различным и зависит от конструктивных особенностей проверяемого блока. В частности, это устройство может быть подключено к проверяемому блоку как одно из внешних устройств. При этом выход сигнала запроса может быть подсоединен ко входу сигнала запроса на обслуживание внешнего устройства проверяемым блоком, а вход устройства - к тому выходу проверяемого блока, который предназначен для выдачи сигнала готовности к обслуживанию внешнего устройства.

При использовании данного изобретения для контроля функционирования микропроцессора подключение устройства для контроля к проверяемому блоку может быть таким же, как и у ближайшего аналога, а именно: выход сигнала запроса соединен с входом немаскируемого прерывания микропроцессора, выход сигнала RESET - с входом RESET микропроцессора, а вход запуска устройства для контроля - с выводом строб-сигнала WRITE микропроцессора.

Устройство для контроля функционирования блока обработки данных работает следующим образом.

При нормальном функционировании блока обработки данных нет необходимости в формировании сигнала RESET единичного уровня, устанавливающего контролируемый блок в исходное состояние. Следовательно, на инверсном выходе второго формирователя 2 временного интервала должен быть выставлен сигнал логического нуля, в связи с чем триггер 6 должен находиться в единичном состоянии.

Сигнал запроса формируется путем выставления сигнала логического нуля на прямом выходе первого формирователя 1 временного интервала, для чего триггер 5 должен быть установлен в нулевое состояние. При этом сигнал единичного уровня с инверсного выхода триггера 5 поступает на вход времязадающего элемента 8 и через элемент 4 задержки - на D-вход триггера 6.

При бессбойном выполнении программы проверяемый блок 9 обработки данных должен в течение определенного промежутка времени сформировать на входе запуска устройства для контроля ответный сигнал единичного уровня, поступающий на C-входы триггеров 5 и 6. Поскольку на D-входы этих триггеров подан сигнал логической единицы, то по переднему фронту ответного сигнала подтвердится единичное состояние триггера 6, а состояние триггера 5 изменится с нулевого на единичное.

Как только триггер 5 установится в единичное состояние, что соответствует снятию сигнал запроса, на вход времязадающего элемента 7 с прямого выхода триггера 5 поступит сигнал единичного уровня, и конденсатор 26 начнет заряжаться через резистор 25. Эти два элемента образуют интегрирующую времязадающую цепочку, которая определяет временной интервал между предыдущим и очередным сигналами запроса, поступающими на соответствующий вход проверяемого блока 9. Напряжение с конденсатора 26 поступает на R-вход триггера 5, который по достижении этим напряжением определенного уровня сбросится в нулевое состояние, в результате чего на прямом выходе этого триггера появится сигнал нулевого уровня, являющийся сигналом запроса, а конденсатор 26 быстро разрядится через диод 27.

Если выполнение программы в контролируемом блоке 9 обработки данных происходит без ошибок и сбоев, то контролируемый блок 9 вовремя сформирует ответный сигнал, и описанный выше процесс повторится.

Как только будет сформирован сигнал запроса, то есть триггер 5 перейдет в нулевое состояние, уровень сигнала, поступающего с инверсного выхода этого триггера на вход времязадающего элемента 8, изменится с нулевого на единичный, и конденсатор 29 начнет заряжаться через резистор 28. Элементы 28 и 29 представляют собой интегрирующую времязадающую цепочку, определяющую продолжительность временного интервала, в течение которого ожидается появление ответного сигнала блока 9.

Если в течение этого времени контролируемый блок 9 не сформирует поступающий на вход запуска устройства для контроля ответный сигнал, что свидетельствует о некорректном выполнении программы блоком 9, возрастающее напряжение на конденсаторе 29 достигнет уровня срабатывания триггера 6 по R-входу, в результате чего триггер 6 перейдет в нулевое состояние.

Таким образом, нулевое состояние триггера 6 указывает на возникновение ошибок и сбоев в аппаратном или программном обеспечении контролируемого блока обработки данных, а сигналом ошибки является сигнал логического нуля на прямом выходе триггера 6 или сигнал логической единицы на инверсном выходе этого триггера.

Сигнал единичного уровня с инверсного выхода триггера 6 поступает на вход определяющего длительность сигнала ошибки времязадающего элемента 3, функционирование которого аналогично функционированию времязадающих элементов 7 и 8.

По достижении возрастающим напряжением на выходе времязадающего элемента 3 уровней срабатывания триггеров 5 и 6 по S-входу эти триггеры будут установлены в единичное состояние. Появление сигналов нулевого уровня на инверсных выходах триггеров 5 и 6 приведет к быстрому разряду конденсатора 23 через диод 24 и конденсатора 29 через диод 30.

В связи с тем что до разряда конденсатора 29 на R- и S-входах триггера 6 возникает конфликтная ситуация, заключающаяся в формировании на этих входах сигналов единичного уровня, при использовании в данном изобретении рассмотренного выше конкретного выполнения времязадающих элементов необходимо обеспечить опережающую установку триггера 5 в единичное состояние. Это достигается с помощью резистора 37, обеспечивающего требуемую задержку сигнала установки триггера 6 в единичное состояние.

После установки триггеров 5 и 6 устройство для контроля переходит в исходное состояние, предваряющее формирование сигнала запроса.

Если ответный сигнал единичного уровня будет сформирован проверяемым блоком на входе запуска устройства для контроля до того, как состояние триггера 5 изменится с единичного на нулевое, то есть до момента выставления сигнала запроса, то по переднему фронту ответного сигнала единичное состояние триггера 5 будет подтверждено, а триггер 6 изменит свое состояние с единичного на нулевое в соответствии с поступающим на его D-вход через элемент 4 задержки сигналом логического нуля с инверсного выхода триггера 5.

Использование элемента 4 задержки для передачи сигнала с инверсного выхода триггера 5 на D-вход триггера 6 обусловлено необходимостью предотвращения ложного изменения состояния триггера 6 в тех случаях, когда по переднему фронту ответного сигнала изменяется состояние триггера 5.

Таким образом, при преждевременном формировании проверяемым блоком ответного сигнала будут сформированы сигналы ошибки на выходах триггера 6.

В результате переходных процессов, происходящих при включении питания в данном устройстве для контроля, на R- и S-входах триггеров 5 и 6 могут появиться сигналы, требующие установки этих триггеров в запрещенное состояние.

Возникновение указанной конфликтной ситуации исключается введением в устройство для контроля функционирования блока обработки данных элемента 18 задержки, подключенного своим входом к шине питания, а выходом - к выходу времязадающего элемента 3 через развязывающий диод 19. Благодаря этому при включении питания обеспечивается удержание уровня логического нуля на S-входах триггеров 5 и 6 в течение некоторого промежутка времени, определяемого в данном случае постоянной времени RC-цепочки, состоящей из последовательно соединенных резистора 33 и конденсатора 34.

Данное устройство для контроля функционирования блока обработки данных может быть использовано как источник сигнала RESET, устанавливающего контролируемый блок в определенное исходное состояние для возврата к началу реализуемой программы при обнаружении некорректности ее выполнения.

При этом сигнал RESET снимается с одного из выходов триггера 6, например с его инверсного выхода (активный сигнал - уровень логической единицы).

Для обеспечения формирования сигнала RESET также и при включении питания в устройство для контроля введен генератор 20 одиночного импульса, вход которого подключен к шине питания, а выход является выходом сигнала RESET и соединен с инверсным выходом триггера 6 через встречно включенный развязывающий диод 21.

При включении питания на выходе генератора 20 формируется одиночный импульс единичного уровня, длительность которого определяется в данном случае постоянной времени дифференцирующей RC-цепочки, состоящей из последовательно соединенных резистора 35 и конденсатора 36. Диод 21, не препятствующий передаче сигнала ошибки единичного уровня с инверсного выхода триггера 6 на вход сигнала RESET, предотвращает запуск времязадающего элемента 3 одиночным импульсом с выхода генератора 20 одиночного импульса.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ИМПУЛЬСОВ | 2003 |

|

RU2248089C1 |

| Устройство контроля электропитания процессора | 1984 |

|

SU1188741A1 |

| Устройство для психофизиологических исследований | 1990 |

|

SU1780717A1 |

| Устройство для сопряжения цифровой вычислительной машины | 1987 |

|

SU1444793A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ИМПУЛЬСОВ | 2004 |

|

RU2256288C1 |

| Устройство для программногоупРАВлЕНия | 1979 |

|

SU809066A1 |

| Устройство для защиты трехфазного частотно-регулируемого привода от неполнофазного режима питания | 1985 |

|

SU1377950A1 |

| Устройство контролируемого пункта | 1983 |

|

SU1211784A1 |

| Устройство для контроля логических и временных параметров сигналов | 1990 |

|

SU1777235A1 |

| Измеритель длительности импульсов | 1990 |

|

SU1714535A1 |

Изобретение относится к вычислительной технике и может быть использовано для контроля правильности работы системы обработки данных или отдельных ее частей. Техническим результатом является обеспечение возможности формирования сигнала ошибки в случае появления на выходе контролируемого блока обработки данных ошибочного ответного сигнала и в случае отсутствия ответного сигнала в пределах заданного временного интервала. Для этого заявленное устройство содержит формирователи временного интервала, времязадающий элемент и элемент задержки. 3 з.п. ф-лы, 1 ил.

| DE 3335548 A1, 18.04.85 | |||

| US 5542051 A, 30.07.96 | |||

| DE 4329872 A1, 09.03.95 | |||

| ПЛАСТИНЧАТЫЙ НАСОС | 2000 |

|

RU2184875C1 |

| US 5155846 A, 13.10.92 | |||

| Устройство для сбора и регистрации данных о работе узлов электронной вычислительной машины | 1973 |

|

SU545990A1 |

| Устройство для регистрации сигналов неисправности | 1979 |

|

SU864290A1 |

Авторы

Даты

1999-12-27—Публикация

1998-09-07—Подача