Изобретение относится к цифровой вычислительной, технике и автоматике и может быть использовано при построении устройств защиты микропроцессоров от сбоев питания, или превышении им допустимо возможной величины.

Целью изобретения является расширение области применения устройства.

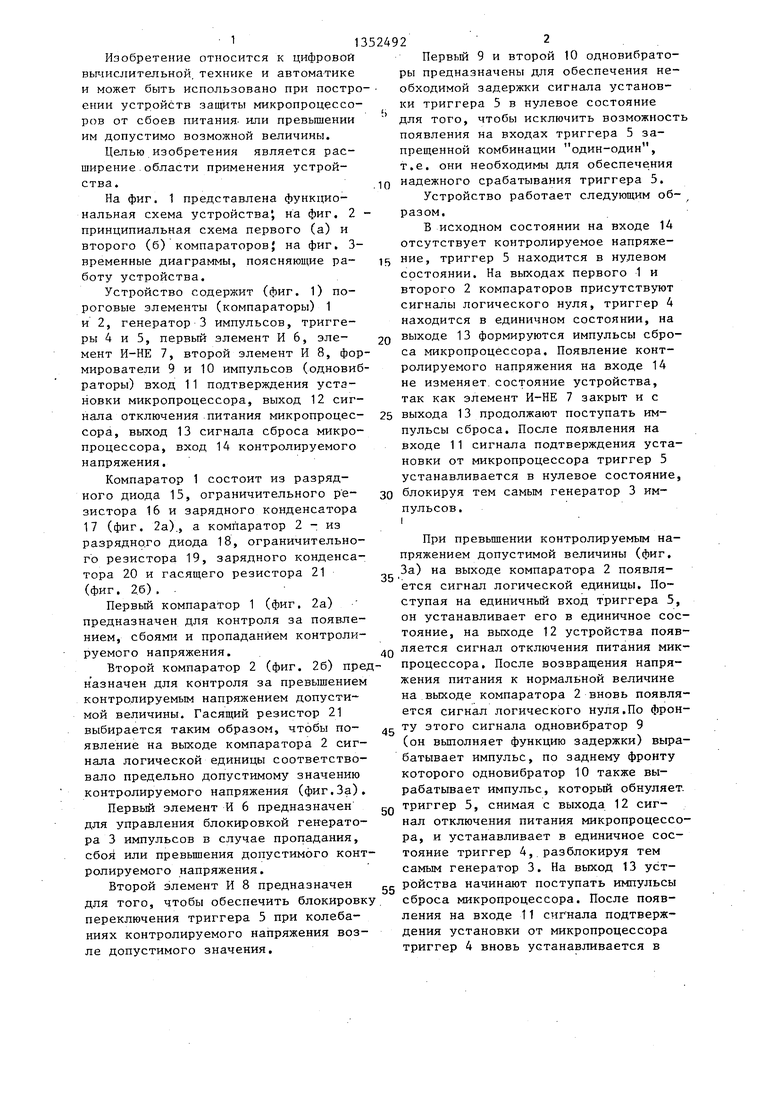

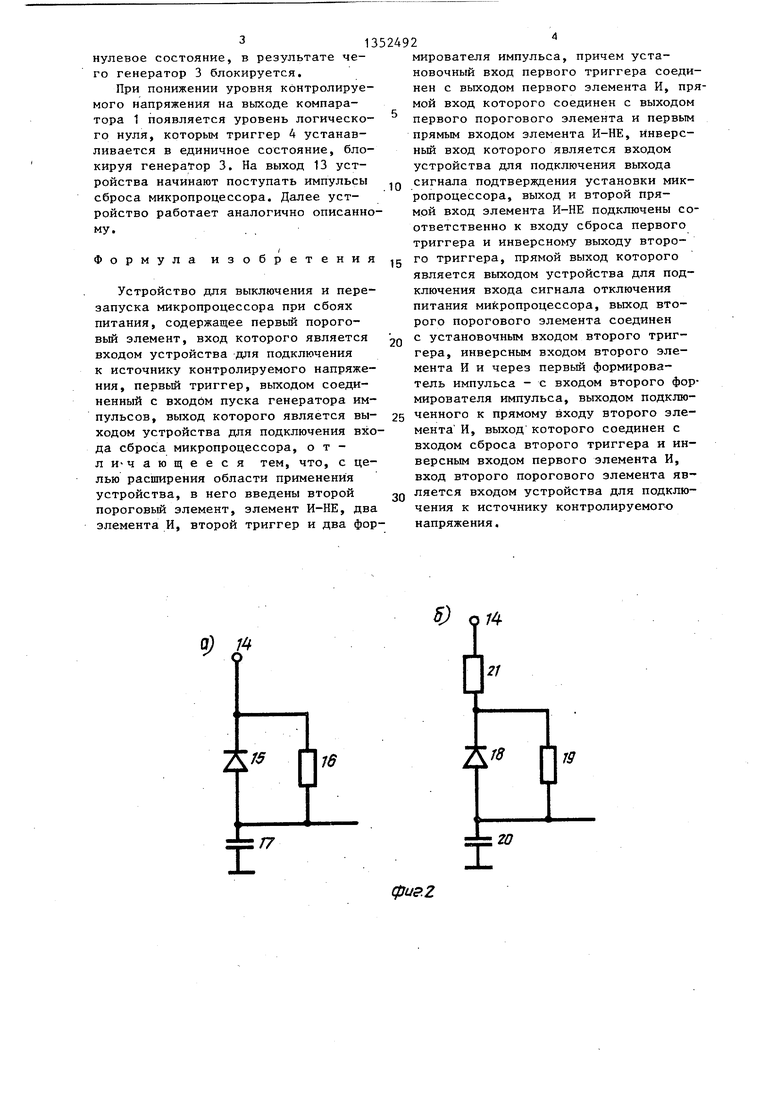

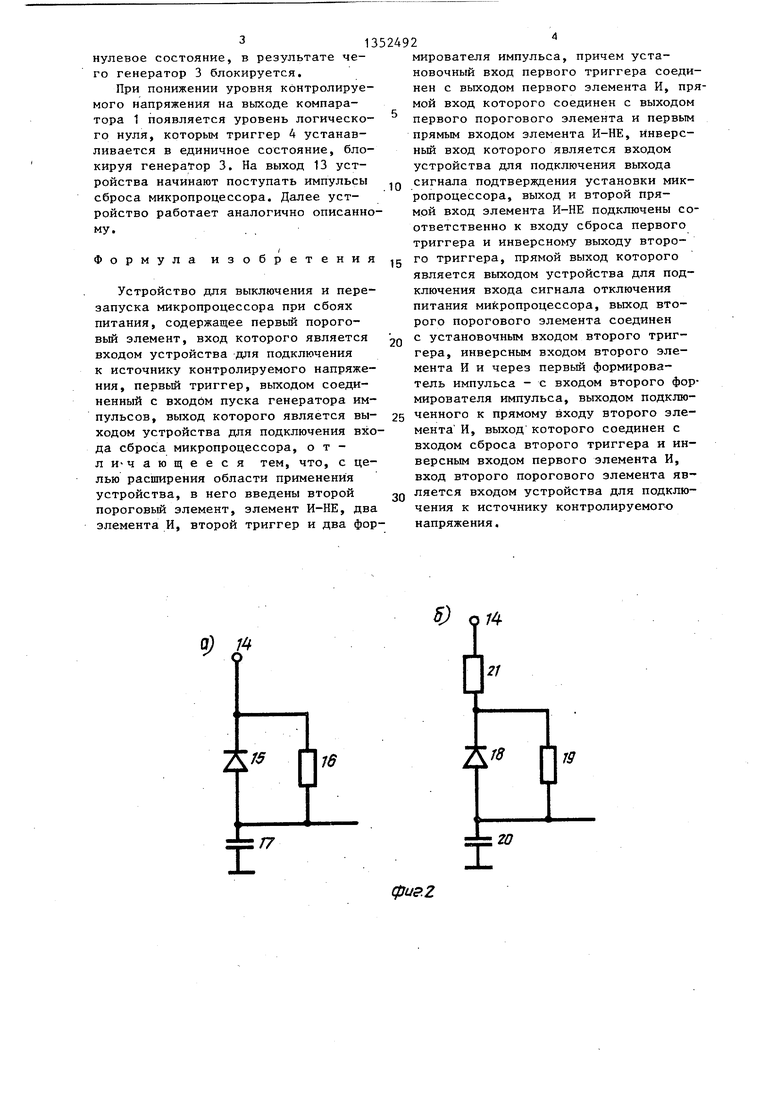

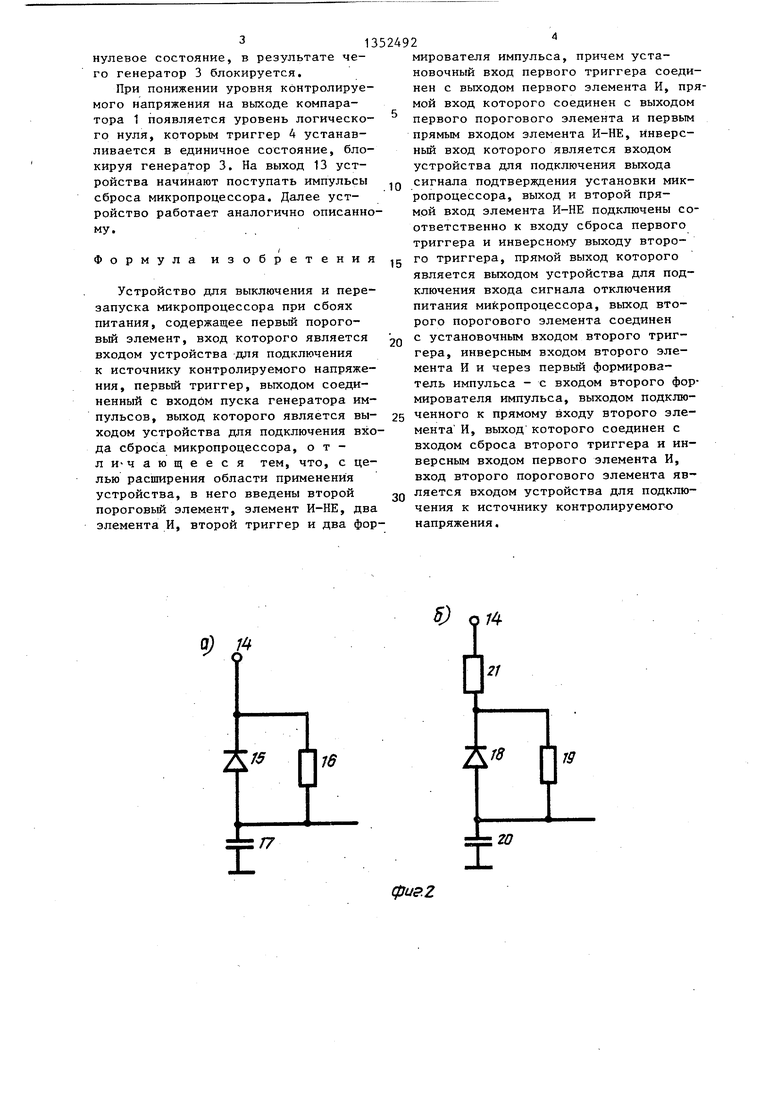

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 принципиальная схема первого (а) и второго (б) компараторов; на фиг. 3- временные диаграммы, поясняющие работу устройства.

Устройство содержит (фиг. 1) пороговые элементы (компараторы) 1 и 2, генератор 3 импульсов, триггеры 4 и 5, первый элемент И 6, элемент И-НЕ 7, второй элемент И 8, формирователи 9 и 10 импульсов (одновиб раторы) вход 11 подтверждения установки микропроцессора, выход 12 сигнала отключения .питания микропроцессора, выход 13 сигнала сброса микропроцессора, вход 14 контролируемого напряжения.

Компаратор 1 состоит из разрядного диода 15, ограничительного р е- зистора 16 и зарядного конденсатора 17 (фиг. 2а)., а компаратор 2 - из разрядного диода 18, ограничительного резистора 19, зарядного конденсатора 20 и гасящего резистора 21 (фиг. 26). .

Первый компаратор 1 (фиг. 2а) предназначен для контроля за появлением, сбоями и пропаданием контролируемого напряжения.

Второй компаратор 2 (фиг. 26) пре н азначен для контроля за превышением контролируемым напряжением допустимой величины. Гасящий резистор 21 выбирается таким образом, чтобы появление на выходе компаратора 2 сигнала логической единицы соответствовало предельно допустимому значению контролируемого напряжения (фиг.За),

Первьм элемент И 6 предназначен для управления блокировкой генератора 3 импульсов в случае пропадания, сбоя или превышения допустимого контролируемого напряжения.

Второй элемент И 8 предназначен для того, чтобы обеспечить блокировк переключения триггера 5 при колебаниях контролируемого напряжения возле допустимого значения.

0

FJ

5

0

5

0

5

0

5

Первый 9 и второй 10 одновибрато- ры предназначены для обеспечения необходимой задержки сигнала установки триггера 5 в нулевое состояние для того, чтобы исключить возможность появления на входах триггера 5 запрещенной комбинации один-один, т.е. они необходимы для обеспечения надежного срабатывания триггера 5.

Устройство работает следующим образом.

В исходном состоянии на входе 1Д отсутствует контролируемое напряжение, триггер 5 находится в нулевом состоянии. На выходах первого 1 и второго 2 компараторов присутствуют сигналы логического нуля, триггер 4 находится в единичном состоянии, на выходе 13 формируются импульсы сброса микропроцессора. Появление контролируемого напряжения на входе 14 не изменяет, состояние устройства, так как элемент И-НЕ 7 закрыт и с выхода 13 продолжают поступать импульсы сброса. После появления на входе 11 сигнала подтверждения установки от микропроцессора триггер 5 устанавливается в нулевое состояние, блокируя тем самым генератор 3 импульсов. I

При превьшгении контролируемым напряжением допустимой величины (фиг. За) на выходе компаратора 2 появляется сигнал логической единицы. Поступая на единичный вход триггера 5, он устанавливает его в единичное состояние, на выходе 12 устройства появляется сигнал отключения питания мик- процессора. После возвращения напряжения питания к нормальной величине на выходе компаратора 2 вновь появляется сигнал логического нуля.По фронту этого сигнала одновибратор 9 (он вьшолняет функцию задержки) вырабатывает импульс, по заднему фронту которого одновибратор 10 также вырабатывает импульс, который обнуляет, триггер 5, снимая с выхода 12 сигнал отключения питания микропроцессора, и устанавливает в единичное состояние триггер 4, разблокируя тем самым генератор 3. На выход 13 устройства начинают поступать импульсы сброса микропроцессора. После появления на входе 11 сигнала подтверждения установки от микропроцессора триггер 4 вновь устанавливается в

нулевое состояние, в результате чего генератор 3 блокируется.

При понижении уровня контролируемого напряжения на выходе компаратора 1 появляется уровень логического нуля, которым триггер 4 устанавливается в единичное состояние, блокируя генератор 3, На выход 13 устройства начинают поступать импульсы сброса микропроцессора. Далее устройство работает аналогично описанному/Формула изобретения

Устройство для выключения и перезапуска микропроцессора при сбоях питания, содержащее первый пороговый элемент, вход которого является входом устройства для подключения к источнику контролируемого напряжения, первый триггер, выходом соединенный с входом пуска генератора импульсов, выход которого является выходом устройства для подключения входа сброса микропроцессора, о т - л и чающееся тем, что, с целью расширения области применения устройства, в него введены второй пороговый элемент, элемент И-НЕ, два элемента И, второй триггер и два фор0} /4

о

2/

16

77

0

5

0

5

0

мирователя импульса, причем установочный вход первого триггера соединен с выходом первого элемента И, прямой вход которого соединен с выходом первого порогового элемента и первым прямым входом элемента И-НЕ, йнверс- ньй вход которого является входом устройства для подключения выхода сигнала подтверждения установки микропроцессора, выход и второй прямой вход элемента И-НЕ подключены соответственно к входу сброса первого триггера и инверсному выходу второго триггера, прямой выход которого является выходом устройства для подключения входа сигнала отключения питания микропроцессора, выход второго порогового элемента соединен с установочным входом второго триггера, инверсным входом второго элемента И и через первый формирователь импульса - с входом второго формирователя импульса, выходом подключенного к прямому входу второго элемента И, выход которого соединен с входом сброса второго триггера и инверсным входом первого элемента И, вход второго порогового элемента является входом устройства для подключения к источнику контролируемого напряжения.

5) 0/4

rff

го

фи.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выключения и перезапуска микропроцессора при сбоях питания | 1988 |

|

SU1509904A1 |

| Устройство для контроля источника питания | 1991 |

|

SU1839251A1 |

| Устройство для включения и перезапуска микропроцессора при сбоях питания | 1986 |

|

SU1361559A2 |

| Устройство для включения и перезапуска микропроцессора при сбоях питания | 1983 |

|

SU1151972A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ФУНКЦИОНИРОВАНИЯ БЛОКА ОБРАБОТКИ ДАННЫХ | 1998 |

|

RU2143727C1 |

| Устройство для контроля сдвига фаз двух сигналов | 1989 |

|

SU1716522A1 |

| Устройство для измерения параметра динамического процесса и управления им с самоконтролем | 1986 |

|

SU1423985A1 |

| Устройство для контроля и восстановления микропроцессорной системы | 1985 |

|

SU1317441A1 |

| Устройство для контроля срабатывания электромагнитов переменного тока | 1983 |

|

SU1160371A1 |

| Устройство для блокировки информации в вычислительной системе при включении и выключении электропитания | 1989 |

|

SU1735853A1 |

Изобретение относится к области цифровой вычислительной техники и автоматики и может быть использовано при построении устройств защиты микропроцессоров от сбоев питания или нарушения области допустимых значений величины напряжения источника питания. Цель изобретения - расширение области применения и повьшение надежности устройства. Цель достигается тем, что в устройство, содержащее первый пороговый элемент (компаратор) 1, первый триггер 4 и генератор 3 импульсов, введены второй пороговый элемент 2, второй триггер 5, первый элемент И 6, второй элемент И 8, элемент И-НЕ 7, первьй 9 и второй 10 формирователи импульса (одно- вибраторы). 3 ил. W С /5

| Устройство для включения и перезапуска микропроцессора при сбоях питания | 1982 |

|

SU1061147A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для включения и перезапуска микропроцессора при сбоях питания | 1983 |

|

SU1151972A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-11-15—Публикация

1986-07-09—Подача