Изобретение относится к технике электрического измерения и регулирования соотношения (относительной разности) скоростей вращения электродвигателей, рабочих органов машин и механизмов, а также соотношения частот электрических сигналов.

Цель изобретения - повышение быстродействия и уменьшение погрешнос- ти измерения и регулирования соотношения скоростей при их изменении в широком диапазоне.

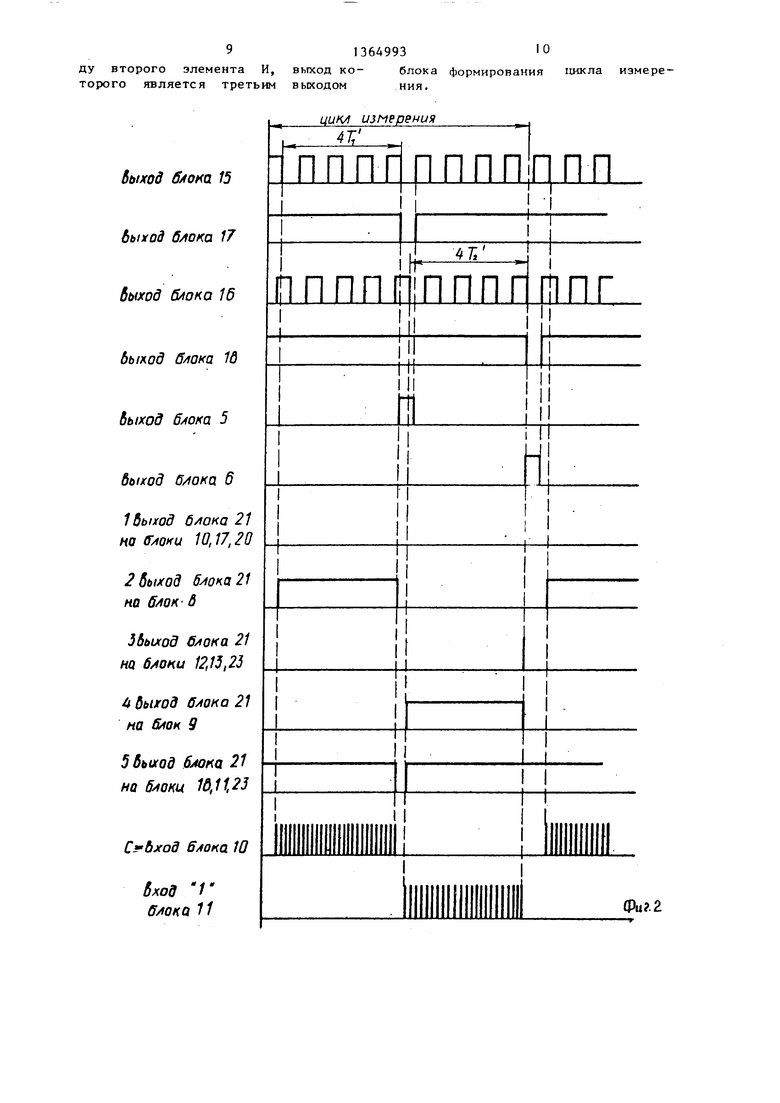

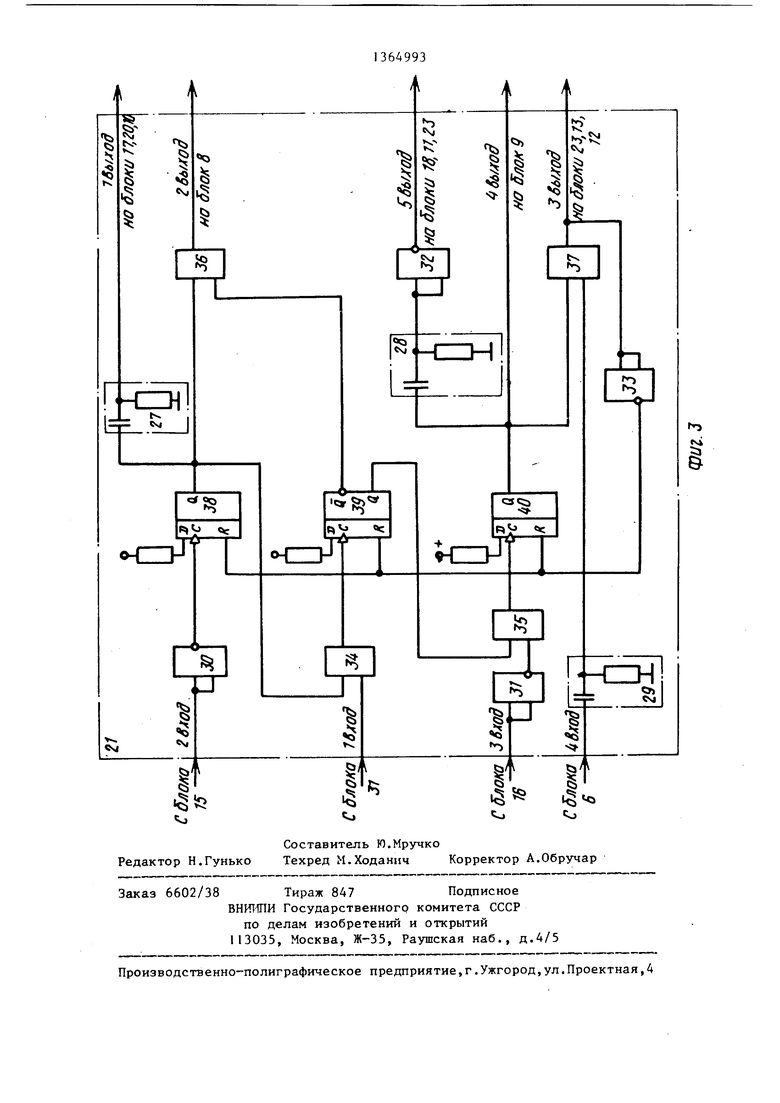

На фиг,1 представлена функциональная схема устройства; на фиг.2 - временная диаграмма его работы, иллюстрирующая изменение состояний информационных шин и шин управления в цикле измерения для случая N 4; на фиг.3 - схемы блока формирования цик- ла измерения.

Устройство содержит источники 1 и 2 импульсных сигналов, входные формирователи 3 и 4, инверторы 5 и 6, генератор 7 эталонной частоты, эле- менты И 8 и 9, подключенные первыми входами к генератору 7, а выходами - к счетным входам соответственно нереверсивного и реверсивного счетчиков 10 и 11, регистры 12 и 13 памяти, пер вый из которых подключен к выходу счетчика 10 непосредственно, а второй - к выходу счетчика 11 через узел инвертирования числа, цифроаналого- вое делительное устройство 14, свя- занное цифровыми входами с выходами регистров памяти, умножители 15 и

16частоты и управляемые делители

17и 18 частоты, попарно включенные

в оба измерительных канала таким об- разом, что входы умножителей 15 и 16 подключены к выходам соответствующих формирователей 3 и 4, а выходы соединены со счетными входами соответственно элементов 5 и 6, неуправляемый делитель 19 частоты, счетным и обнуляющим входами подключенный соответственно к генератору 7 и умножителю 15, узел 20 управления делением частоты, счетным и обнуляющим входами связанньш соответственно с выходами делителя 19 и умножителя 15, блок 21 формирования цикла измерения, подключенный своими четырьмя входами к выходам инверторов 5 и 6 и умножителей 15 и 16, блок 22 инверторов, управляемый блоком 23, реверсивный источник 24 опорного напряжения, формируемого для блока 14. Информационный вход

предзаноса счетчика I1 связан с выходом счетчика 10, управляющие входы делителей 17 и 18 и цифровой вход блока 25 регулирования соотношения скоростей объединены с выходом узла 20, а выходы блока 21 соединены соответственно первый - со стробирующим входом узла 20, обнуляющим входом счетчика 10 и стробирующим входом предзаноса управляемого делителя 17, второй и четвертый - с вторыми входами соответственно элементов И 8 и 9, третьим - со стробирующими входами регистров 12, 13 и блока 23, а пятым - со стробирующими входами предзаноса соответственно счетчика 11, управляемого делителя 18 и с входом сброса блока 23.

Элементы 1,3,15,17,5,8,10,12 образуют первьй измерительный канал, а элементы 2,4,16,18,6,9,11,22,13 - второй измерительный канал. Оба канала в совокупности с элементами 7, 21,14,23,24,19,20 образуют блок измерения соотношения скоростей. На вход блока 25 подключен задатчик 26.

Блоки 15 и 16 представляют собой одинаковые умножители частоты, не вносящие статической погрешности в преобразование частоты. В качестве блоков 15, 16 целесообразно использовать блоки фазовой автоподстройки частоты (ФАПЧ).

Управляемые делители 17 и 18 являются идентичными. Они обеспечивают деление частот f,, f преобразованных сигналов источников 1, 2, поступающих на их счетные входы с выходов блока 15, 16 на один и тот же коэффициент деления N, определяемый цифровым кодом, установленным узлом 20 и несущим информацию о скорости (частоте f, а точнее о периоде Т,): Л, KS7,; f, Kf ,; т; Т ,/К , где К - коэффициент умножения частоты; Я., базовая скорость; f и Т - частота и период сигнала источника 1. При этом информация с шины управления считьшается в каждые из блоков 17, 18 перед началом цикла измерения стробирующими импульсами.

Узел 20 управления делени ем частоты состоит из включенных последовательно счетчика и регистра памяти, причем счетчик своим счетным входом подключен к выходу блока 19 и производит отсчет только в течение импульса на выходе умножит.еля 15, об-

нуляясь и прекращая счет во время паузы сигнала, а регистр памяти счи- тьгоает информацию с выхода счетчика только по команде блока 21.

Функции блока 22 заключаются в том, чтобы на основе информации о преобразованных умножителями и управляемыми делителями частоты сигналах

4993

щей цепочкой 28 и инвертором 32 на пятом выходе блока 21 формируется короткий отрицательный импульс.

В конце рабочего импульса сигнала источника 2, преобразованного элементами 16 и 18, дифференцирующая цепочка 29 и элемент И 37 формируют короткий положительный импульс сброса по

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения и регулирования соотношения скоростей | 1984 |

|

SU1224726A1 |

| Способ контроля состояния кромки режущего инструмента и устройство для его осуществления | 1990 |

|

SU1763890A1 |

| Цифровой электромагнитный толщиномер | 1988 |

|

SU1839228A1 |

| Дифференцирующий счетчик фотонов | 1986 |

|

SU1374063A1 |

| Устройство диагностирования скважинных штанговых насосов | 1984 |

|

SU1224444A1 |

| Умножитель частоты | 1990 |

|

SU1797113A1 |

| Устройство для измерения параметров радиоимпульсов | 1980 |

|

SU938206A1 |

| Цифровой фазометр | 1980 |

|

SU935821A1 |

| Устройство для динамической балансировки роторов | 1984 |

|

SU1173214A1 |

| Устройство для виброакустического диагностирования двигателя внутреннего сгорания | 1990 |

|

SU1702217A1 |

Изобретение относится к измерительной технике. Цель изобретения-- повьшение быстродействия и уменьшение погрешности измерения и регулирования соотношения скоростей при их изменении в широком диапазоне. Устр-во содержит источники I и 2 импульсных сигналов, формирователи 3 и 4, инверторы 5 и 6, генератор 7 эталонной частоты, элементы И 8 и 9, счетчики 10 и 11, регистры 12 и 13 памяти, цифроаналоговое делительное устр-во 14, умножители 15 и 16 частоты, делители 17, 18 и 19, узел 20 управления делением частоты, блок 21 формирования циклов измерения, блок 22 инверторов, управляемый блоком 23, источник 24 опорного напряжения, блок 25 регулирования соотношения скоростей и задатчик 26. Введение новых элементов и образование новых связей между элементами устр-ва позволяют производить перестройку коэффициента деления в функции базовой скорости, что позволяет измерить соотношение скоростей и частот первичных сигналов источников 1 и 2 путем сравнения частот преобразованных сигналов, которые изменяются в более узком диапазоне, чем общий диапазон изменения сравниваемых скоростей. 1 з.п. ф-лы, 3 ил. (Л оо О5 ; со ;о со ф|Уг/

источников 1, 2, поступающих по вход-ю третьему выходу блока 21, по которому ным шинам, сформировать и выдать уп- посредством инвертора 33 происходит

равляющие воздействия по выходным щи нам на другие элементы устройства в цикле измерения в соответствии с диаграммой на фиг.2.

Блок 21 формирования цикла измерения (фиг.З) содержит дифференцирующие цепочки 27 - 29, инверторы 30-33, элементы И 34 - 37, 1-й, 2-и.и 3-й D-триггеры 38 - 40.

Сброс D-триггеров 38, 39 подго- товка блока 21 к работе) осуществляется в конце рабочего импульса сигнала источника 2, преобразованного умножителем 16 и делителем 18, т.е. в конце цикла измерения. При этом на Q-выходах триггеров 38 и 39 устанавливаются уровни логического нуля Переключение триггеров возможно только в последовательности 38, 39, 40.

Первый триггер 38 переключается в конце первого (рабочего) импульса сигнала источника 1, преобразованного умножителем 15. В результате дифференцирующая цепочка 27 формирует короткий положительный импульс на первом выходе блока 21, а на выходе элемента И, т.е. на втором выходе блока 21, появляется уровень логической единицы.

Второй триггер 39 переключается в конце первого (рабочего) импульса сигнала источника 1, преобразованног умножителем 15 и управляемым делителем 17. При этом на выходе элемента И, т.е. на втором выходе блока 21, восстанавливается уровень логическог нуля. Таким образом, на втором выходе блока 21 уровень логической единицы держится в течение времени импульса выходного сигнала делителя 17

Третий триггер 40 переключается по заднему фронту первого импульса сигнала источника 2, преобразованно

го умножителем 16, следующему во вре- gg выхода счетчика 10 в реверсивный мени за рабочим импульсом на выходе счетчик 11, последующего вычитания блока 17. При этом на четвертом выходе блока 21 устанавливается уровень жзгической единицы, а дифференцируюиз содержимого последнего импульсов опорной частоты в течение рабочего импульса на четвертом выходе блока

0

установка блока 21 в исходное сое- - тояние.

Устройство в целом работает следу- 5 ющим образом.

Измерение соотношения скоростей основано на сравнении количества импульсов эталонной частоты fj, проходящих за временные интервалы Т,, Т, одинаково пропорциональные периодам Т, Т импульсных сигналов источников 1, 2, связанных с приводными точками, скорости Я, ниваются:

Я которых срав25

30

(О

35

(2)

Измерение осуществляется циклами. измерения включает три этапа: определение коэффициента деления N, соответствующего базовой скорости Я, ведущего вала, получение информации о периоде Т с требуемой для дальней

шего определения соотношения

точностью путем подсчета числа импульсов эталонной частоты счетчиком 10 в течение рабочего импульса на втором выходе блока 21 продолжительностью N Т,/К, а также определение абсолютной разности периодов (Т , - TIJ) и вычисление соотношения пери - одов (скоростей) посредством пред- заноса информации о величине Т с

выхода счетчика 10 в реверсивный счетчик 11, последующего вычитания

из содержимого последнего импульсов опорной частоты в течение рабочего импульса на четвертом выходе блока

ре-.л 2

Т.)/

21 продолжительностью N - T .j/К и ализации операции деления (т, - /Т цифроаналоговьм делительным устройством 14.

Цикл измерения начинается с приходом первого (рабочего) импульса сигнала источника 1, преобразованного умножителем 15, следующим во времени за коротким импульсом Конец цикла, формируемым блоком 21 на третьем выходе.

В течение рабочего импульса длительностью Т,/2 (сигнала с частотой

10

управляемый делитель 18, с вькода счетчика 10 в реверсивный счетчик 11 а также обеспечивает подготовку к работе блок 23.

Затем в течение N периодов преобразованного умножителем 16 сигнала источника 2 блоком 21 формируется ра решающий сигнал, при котором элемент 9 пропускает сигнал эталонной частоты на вычитающий вход реверсивного счетчика 1I. Таким образом, по истечении разрешающего сигнала в счетчик 11 сформируется число, характеризуциональных периодам первичных сигналов источников 1,2:

4Т т - Т

N .т - И К 1 к

т,.

f , ) блоком 20 осуществляется опреде- 15 ющее абсолютную разность преобразо- ление величины базовой скорости пу- ванных периодов (т - Т ), пропор- тем подсчета количества импульсов эталонной частоты генератора 7, деленной блоком 19.

В конце указанного рабочего им- 2о пульса (фиг.2) блок 21 формирует на первом выходе короткий положительный импульс, инициирующий перевод информации с выхода счетчика блока 20 в регистр памяти этого блока. Таким 25 образом, на кодовой шине управления устанавливается число, характеризующее базовую скорость 57, . В соответствии с этим числом устанавливается коэффициент N деления частоты блока- зо ми 17, 18, а блок 25 устанавливает соответствующий коэффициент усиления в канале регулирования соотношения скоростей. Указанным импульсом на первом выходе блока 21 производится также обнуление счетчика 10 первого канала и (с небольшой задержкой) счи- тьшание информации о базовой скорости в управляемый делитель 17 первого канала.

Затем в течение N периодов преобразованного умножителем 15 сигнала источника 1 блоком 21 формируется разрешающий сигнал, при котором элемент И 8 пропускает сигнал эталонной 45 частоты на счетный вход счетчика 10. Число импульсов, подсчитанное за указанное время счетчиком 10, представляет собой информацию о преобразован35

40

В том случае, если ЛТ 0, переполнение счетчика 11 фиксируется бло ком 23, который формирует команды на инвертирование числа для блока 22 и знака опорного напряжения для блока 24.

В конце цикла измерения, совпадающего с отрицательным фронтом сигнала, блок 21 формирует короткий импульс Конец цикла, который переводит информацию о периоде Т и абсолютной разности йТ соответственно в регистры 12 и 13 памяти, которые сохраняют ее в течение последующего цикла измерения на своих вьшодах,под ключенных к делительному устройству 14. При этом на выходе последнего фо мируется аналоговый сигнал, напряжение и знак которого соответствуют из меряемому соотношению скоростей:

ibix

- и,.

tU,

D

К

т :

f, - Т7 fЭ

JJV, ,,

я,-я. я

tu,

Kj,

где К - коэффициент передачи делительного устройства. Перестройка коэффициента деления N в функции базовой скорости позволяет измерять соотношение скоростей или частот первичных сигналов источников 1, 2 путем сравнения частот f, , f преобразованньгх сигналов, которые изменяются в гораздо более узком диапазоне, чем общий диапазон изменения сравниваемых скоростей.

ном периоде Т,, пропорциональном периоду первичного сигнала источника 1 (т ; NT , NT,/к).

После этого блок 21 переходит в режим ожидания отрицательного фронта импульса сигнала источника 2, преобразованного умножителем 16. По указанному фронту блок 21 выдает короткий импульс на пятом выходе, который инициирует считывание информации в

0

управляемый делитель 18, с вькода счетчика 10 в реверсивный счетчик 11, а также обеспечивает подготовку к работе блок 23.

Затем в течение N периодов преобразованного умножителем 16 сигнала источника 2 блоком 21 формируется разрешающий сигнал, при котором элемент 9 пропускает сигнал эталонной частоты на вычитающий вход реверсивного счетчика 1I. Таким образом, по истечении разрешающего сигнала в счетчике 11 сформируется число, характеризу5 ющее абсолютную разность преобразо- ванных периодов (т - Т ), пропор-

циональных периодам первичных сигналов источников 1,2:

4Т т - Т

N .т - И К 1 к

т,.

ющее абсолютную разность преобразо- ванных периодов (т - Т ), пропор-

В том случае, если ЛТ 0, переполнение счетчика 11 фиксируется блоком 23, который формирует команды на инвертирование числа для блока 22 и знака опорного напряжения для блока 24.

В конце цикла измерения, совпадающего с отрицательным фронтом сигнала, блок 21 формирует короткий импульс Конец цикла, который перево - дит информацию о периоде Т и абсолютной разности йТ соответственно в регистры 12 и 13 памяти, которые сохраняют ее в течение последующего цикла измерения на своих вьшодах,подключенных к делительному устройству 14. При этом на выходе последнего формируется аналоговый сигнал, напряжение и знак которого соответствуют измеряемому соотношению скоростей:

ibix

- и,.

tU,

D

К

т :

f, - Т7 fЭ

JJV, ,,

я,-я. я

tu,

Kj,

45

50

55

где К - коэффициент передачи делительного устройства. Перестройка коэффициента деления N в функции базовой скорости позволяет измерять соотношение скоростей или частот первичных сигналов источников 1, 2 путем сравнения частот f, , f преобразованньгх сигналов, которые изменяются в гораздо более узком диапазоне, чем общий диапазон изменения сравниваемых скоростей.

. 71364993

ормула изобретения

до об ли ле ум вт ва хо ве ег со уп ве вх кл но

Q g 5 Q 0 5 g е

5

дом узла управления делением частоты, обнуляющие входы неуправляемого делителя частоты и узла управления делением частоты подключены к выходу умножителя частоты первого канала, второй и третий входы блока формирования цикла измерения связаны с выходами умножителей частоты соответственно первого и второго каналов, а его первый и пятый выходы соединены со стробирующими входами предзаноса управляемых делителей частоты соответственно первого и второго каналов, входы элементов И обоих каналов подключены к выходу генератора эталонной частоты.

ду второго элемента И, выход ко-блока формирования цикла иэмереторого является третьим выходомния.

| Измеритель соотношения скоростей | 1982 |

|

SU1071961A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для измерения и регулирования соотношения скоростей | 1984 |

|

SU1224726A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1988-01-07—Публикация

1985-07-09—Подача