VJ

чэ

ч|

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты | 1988 |

|

SU1608779A1 |

| Умножитель частоты | 1986 |

|

SU1385230A1 |

| Умножитель частоты | 1979 |

|

SU834697A1 |

| Цифровой фазометр с оптимальным квантованием | 1973 |

|

SU468189A1 |

| Умножитель частоты | 1984 |

|

SU1179334A1 |

| Цифровой следящий умножитель частоты | 1988 |

|

SU1608659A1 |

| ЦИФРОВОЙ ФАЗОМЕТР С ПОСТОЯННЫМ ИЗМЕРИТЕЛЬНЫМ | 1973 |

|

SU366419A1 |

| Умножитель частоты следования импульсов | 1989 |

|

SU1728964A2 |

| Устройство для синхронизации цифровой магнитной записи | 1989 |

|

SU1691888A1 |

| Устройство для измерения кратковременной нестабильности периода | 1990 |

|

SU1774279A1 |

Изобретение относится к вычислительной технике и может быть использовано, например, в синхронизируемых синтезаторах периодических сигналов сложной формы. Цель изобретения - повышение точности умножения частоты. Умножитель частоты содержит формирователь 1 импульсов, источник 2 опорного напряжения, три триггера 3, 4, 13, четыре элемента И 15, 16, 17, 17, фильтр 6 нижних частот, коммутатор 7, управляемый генератор 8 импульсов, два формирователя 9, 19 импульсов сброса, два фазовых детектора 10, 11, элемент ИЛИ-НЕ 12, ключ 14, два делителя 15, 20 частоты, три счетчика 21, 24, 26, дешифратор 22, одновибратор 23 и реверсивный счетчик 25, соединенные между собой функционально.3 ил.

со

Изобретение относится к вычислительной и информационно-измерительной технике, предназначено для умножения частоты .периодических сигналов и может быть использовано, например, в синхрони- зируемых синтезаторах периодических сигналов сложной формы, в фазометрах, фазорегуляторах,

Известен умножитель частоты, содержащий генератор тактовых импульсов, ос- новной делитель частоты, ключи, первый и второй счетчики, две группы элементов И, управляемый делитель частоты, формирова- тель импульсов, управляемой генератор импульсов, фильтр нижних частот, фазовый детектор и дополнительный делитель частоты.

Недостатком данного умножителя является низкая точность умножения в связи с

тем, что погрешность измерения каждого

периода входного сигнала не компенсируется соответствующей подстройкой частоты управляемого генератора вследствие инерционности схемы фазовой автоподстройки частоты.

Известен также умножитель частоты, содержащий блок управления, генератор тактовых импульсов, подключенный выходом к сигнальным входам первого и второго ключей, выходы которых соединены.сосчет- ными входами первого и второго счетчиков соответственно, и коммутатор, подключенный выходом к установочному входу третьего счетчика, соединенного выходом с выходной шиной умножителя частоты, вхо- дом управления установкой кода третьего счетчика и входом делителя частоты, подключенного выходом к первому входу фазового детектора, соединенного вторым входом с выходом формирователя импуль- сов, а выходом - с входом фильтра нижних частот, подключенного выходом через управляемый генератор импульсов к счетному входу третьего счетчика, причем вход формирователя импульсов .соединен с шиной ввода умножаемой частоты, два регистра, при этом блок управления содержит три триггера, два элемента И и два формирователя импульсов сброса, подключенные выходами к входам обнуления первого и второго счетчиков соответственно вход первого формирователя импульсов сброса соединен с выходом первого элемента И, с входом разрешения записи первого регистра и с входом обнуления первого триггера, подключенного входом установки в единицу к выходу второго элемента И, к входу разрешения записи второго регистра и к входу второго формирователя импульсов сброса, а выходом - к управляющему входу комму

0 5

0

5

0 5 0 5 0 5

татора, соединенного информационными входами с выходами первого и второго регистров, информационные входы которых подключены к выходам первого и второго счетчиков соответственно, причем первый элемент И соединен первым входом с выходом второго триггера и с первым входом .второго элемента И, а вторым входом - с управляющим входом второго ключа и с инверсным выходом и информационным входом третьего триггера, подключенного прямым выходом к второму входу второго элемента И и к управляющему входу первого ключа, а синхронизирующим входом - к выходу формирователя импульсов и к информационному входу второго триггера, соединенного синхронизирующим входом с выходом третьего счетчика,

Недостатком этого умножителя является низкая точность умножения частоты. Причина этого недостатка заключается в следующем.

В данном умножителе частоты длительность периода выходного сигнала равна Твых Nxi Туг, где Nxi - результат измерения i-ro периода входного сигнала Тх; Туг - значение длительности периода сигнала управляемого генератора (УГ).

При изменении значения Nxi происходит скачкообразное изменение длительности периода выходного сигнала умножителя и, следовательно, возникает ошибка умножения. Эта ошибка устраняется соответствующим изменением длительности периода колебаний, генерируемых УГ, что осуществляется схемой фазовой автоподстройки частоты (ФАПЧ) УГ. .

Вследствие инерционности схемы ФАПЧ, которая характеризуется временем установления туст частоты сигнала УГ при известной начальной расстройке Afp, погрешность умножения устраняется только по истечении времени t tyct. Инерционность схемы ФАПЧ в значительной мере определяется постоянной времени фильтра нижних частот, входящего в ее состав. Обычно .

. Вместе с тем, при непрерывном квантовании входного сигнала число квантующих импульсов Nxi в пределах каждого .1-го периода Txi Тх не остается постоянным, а изменяется вследствие погрешности квантования,

Погрешность квантования определяется следующим образом: at Ткв NXi-TXi AtHp- Atki, где Ткв -период квантующих импульсов; AtHi - временной интервал, равный части первого периода квантующего сигнала, находящийся вне измеряемого интервала Txi; Atki - интервал времени между последним квантующим импульсов и концом измеряемого периода Txi (Ермолов Р.С. Цифровые частотомеры. Л.: Энергия, 1973, с. 36}. Значения AtHi и Atki изменяются в пределах интервала 0; Ткв и могут быть равны между собой только тогда, когда значения периодов Тх и Ткв кратны. При этом погрешность квантования at 0. В этом же случае возможно, что ДтН| 0, а Atki Тка, или наоборот, Д tHi Ткв, а Atki 0. Тогда погрешность квантования о t будет максимальной и равной ± Ткв.

При отрицательной погрешности квантования ff. ее значение определяется дробной частью отношения TXJ и Ткв и равно {Тх/Ткв}-Ткв, где {Тх/Ткв} дробная часть отношения Тх/Ткв, Если значение. A tHi увели - чивается, то соответственно увеличивается и; значение Atki. Когда Atki достигает значения Atki Ткв и продолжает увеличиваться, число квагнтующих импульсов Nxi, находящихся в пределах измеряемого периода Тхь увеличивается на 1, а погрешность fft становится положительной и равной 7t+- Ткв - at-. Само значение A tk(i-H) становится ;равным Atk(M-t) - Д tki-ТКв.

Поскольку входной и квантующий сигналы независимы, то при непрерывном квантовании входного сигнала для первого измерения интервал AtHi будет случайным, а все последующие значения Ды и Д tki, включая значение Д tki, определяются соотношением Тх и Ткв и изменяются вместе с номером измеряемого периода . Так, для i 2 значение AtH2 будет равно Atki и т.д.

Таким образом, значения cf изменяются вместе с номером измеряемого периода I, и это является причиной разброса значений Nxi даже при ТХ| Тх. Диапазон разброса значений NXi зависит от соотношения Тх и Ткв, и его максимальное значение равно ± 1. Если результаты измерения смежных периодов Nxi и NX(H-I) имеют крайние значения, то Nxt- Nx(hM) 12 f . .

При монотонном изменении частоты входного сигнала изменяется cootHouieHjie ТХ) и Ткв, а также ati. В этом случае максимальное значение погрешности квантования (Jtmax будет равНО tmax ± 1. ПОЭТОМУ

результаты измерения двух смежных периодов Nxi и Nxp-и) только за счет погрешности квантования могут отличаться на 2.

Период чередования отличающихся значений Nxi зависит от дробной части соотношения Тх и Ткв и имеет максимальное значение 2ТХ, например при {Тх/ТКв} 0,5

иДГн О.бТкв.

В рассматриваемом умножителе частоты разброс, значений результатов измерения каждого i-ro периода сигнала Тх приводит к возникновению погрешности умножения. В связи с тем, что минимальный период чередования отличающихся значений меньше времени установления частоты УГ схемой ФАПЧ, устранения погрешности умножения не происходит. В данном уст0 ройстве работа схемы ФАПЧ оказывается весьма неэффективной, что и является причиной низкой точности умножения частоты. Целью изобретения является повышение точности умножения частоты.

5Указанная цель достигается тем, что в умножитель частоты, содержащий входной формирователь импульсов, первый фазовый детектор, первый делитель частоты, фильтр нижних частот, коммутатор, управляемый

0 генератор импульсов, первый, второй и третий счетчики, первый, второй и третий триггеры, первый и второй формирователи импульсов сброса, ключ и первый и второй элементы И, причем информационный вход

5 умножителя частоты через входной формирователь импульсов соединен с первым входом первого фазового детектора и с входом установки в единицу первого триггера, выход которого соединен с управляющим вхо0 дом ключа, выход первого делителя частоты соединен с вторым входом первого фазового детектора, выход которого соединен с входом фильтра нижних частот, выход третьего триггера соединен с управляющим

5 входом коммутатора, выход первого элемента И соединен с входом первого формирователя импульсов сброса, выход которого соединен с входом установки в ноль первого счетчика, выход управляемого генератора

0 импульсов соединен со счетным входом второго счетчика, выход которого соединен с информационным выходом умножителя частоты, дополнительно введены второй делитель частоты, реверсивный счетчик, второй

5 фазовый детектор, источник опорного напряжения, дешифратор, элемент ИЛИ-НЕ одновибратор и третий и четвертый элементы И, причем разрядные выходы первого счетчика соединены соответственно с уста0 ПОБОЧНЫМИ входами реверсивного счетчика, вход вычитания которого соединен с выходом второго элемента И, выход третьего элемента И соединен с входом сложения реверсивного счетчика, разрядные выходы

5 которого соединены соответственно с установочными входами второго счетчика, выход которого соединен со счетным входом третьего счетчика, выход которого соединен с входом первого делителя частоты, выход которого соединен со старшим входным

разрядом дешифратора, остальные входные разряды которого соединены соответственно с разрядными выходами третьего счетчика, старший разрядный выход которого соединен с первым входом второго фа- зового детектора, второй вход которого соединен с выходом первого фазового детектора, выход второго фазового детектора соединен с первым входом элемента ИЛИНЕ, второй вход которого соединен с выхо- дом третьего триггера, выход элемента ИЛИ-НЕ соединен с первыми входами первого, второго и третьего элементов И, вторые входы которых соединены соответственно с первым, вторым и третьим выхо- дами дешифратора, выход второго формирователя импульсов сброса соединен с входом одновибратора и входами установки в ноль реверсивного счетчика и третьего триггера, вход установки в единицу которо- го соединен с входом установки в единицу второго триггера, входом установки в ноль второго делителя частоты и выходом первого формирователя импульсов сброса, выход одновибратора соединен с входом строби- рования дешифратора, выход управляемого генератора импульсов соединен с информационным входом ключа, выход которого соединен с входом второго делителя частоты, выход которого соединен со счетным вхо- дом первого счетчика, выход фильтра нижних частот соединен с первым информационным входом коммутатора, второй информационный вход которого соединен с выходом источника опорного напряжения выход коммутатора соединен с входом управляемого генератора импульсов, выход входного формирователя импульсов соединен с первым входом четвертого элемента И, второй вход которо- го соединен с выходом первого триггера и входом второго формирователя импульсов сброса, а выход четвертого элемента И соединен с входом установки в ноль второго триггера, выход которого соединен с входом установки в ноль первого триггера.

Повышение точности умножения частоты в предлагаемом устройстве достигается за счет того, что дискретное регулирование частоты выходного сигнала умножителя осу- ществляется при помощи цепи пороговой обратной связи по отклонению частоты УГ от номинального значения. Если частота входного сигнала постоянна или изменяется в пределах полосы удержания схемы ФАПЧ, коэффициент деления второго счетчика, выход которого является выходом умножителя частоты, остается неизменным, а соответствующее изменение частоты выходного сигнала осуществляется только путем изменения частоты сигнала УГ. При изменении частоты входного сигнала в диапазоне, превышающем полосу удержания схемы ФАПЧ (диапазона возможной автоматической перестройки частоты УГ). осуществляется коррекция текущего значения коэффициента деления, т.е. его увеличение или уменьшение, с тем чтобы уменьшить отклонение частоты УГ от номинального значения и предотвратить тем самым срыв синхронизации ФАПЧ. В процессе осуществления коррекции текущее значение коэффициента деления второго счетчика изменяется последовательно на единицу младшего разряда.

Цикл измерения длительности периода входного сигнала осуществляется только при отсутствии синхронизации ФАПЧ, например после подключения к входу умножения частоты источника сигнала.

Таким образом,у предлагаемого умножителя частоты при постоянной или изменяющейся в пределах полосы удержания ФАПЧ частоте входного сигнала погрешность умножения отсутствует. У прототипа в этом случае максимальная абсолютная погрешность умножения (скачок значения периода выходного сигнала) равна 2Туг. Если диапазон изменения частоты входного сигнала превышает полосу удержания ФАПЧ, то вследствие осуществления коррекции текущего значения коэффициента деления второго счетчика возникает погрешность умножения, максимальное значение, которой равно Туг. что в два раза меньше, чем в аналогичной ситуации у прототипа. Кроме того, период осуществления коррекции определяется только скоростью изменения частоты входного сигнала, в то время как у прототипа изменение коэффициента деления определяется еще и погрешностью квантования. Поэтому скачкообразное изменение частоты выходного сигнала у предлагаемого умножителя происходит реже, чем у прототипа.

Сравнение свойств предлагаемого умножителя частоты и прототипа свидетельствует о наличии положительного эффекта - повышения точности умножения.

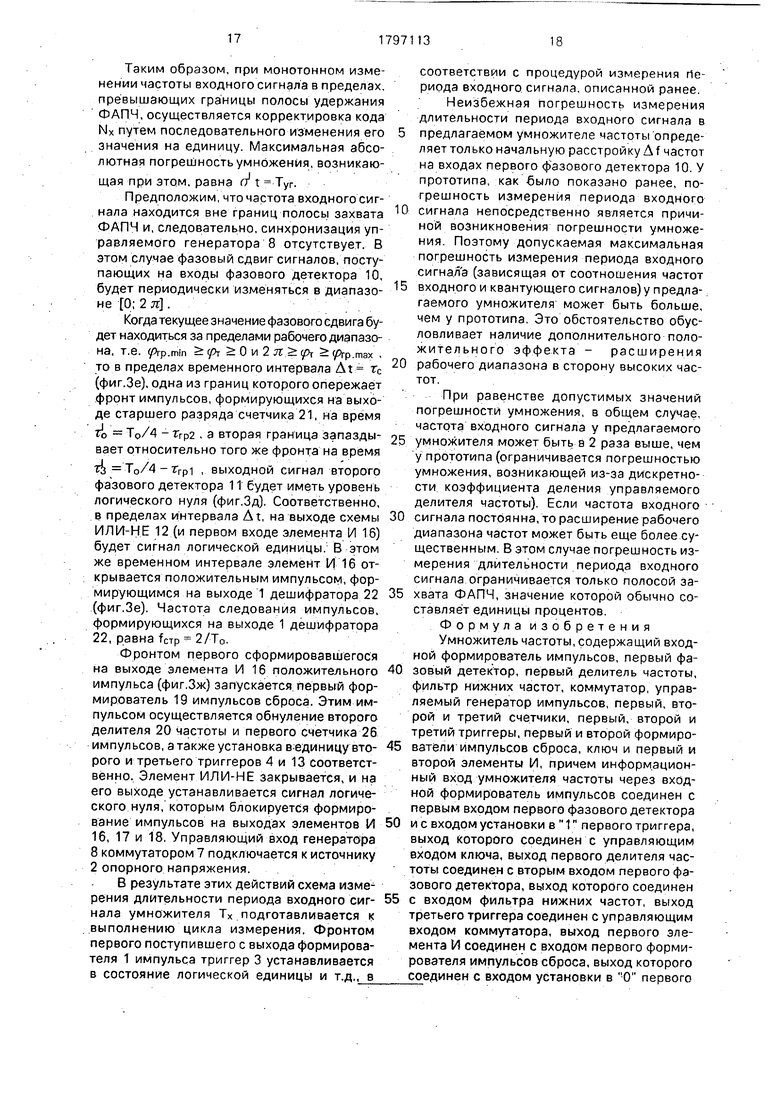

На фиг.1 изображена блок-схема умножителя частоты; на фиг.2, 3 - временные диаграммы сигналов, поясняющие его работу.

Умножитель частоты содержит входной формирователь 1 импульсов, источник 2 опорного напряжения, первый и второй триггеры 3 и 4 соответственно, четвертый элемент И 5, фильтр 6 нижних частот, коммутатор 7, управляемый генератор 8 им- пульсов. второй формирователь 9

импульсов сброса, первый и второй фазовые детекторы 10 и 11 соответственно, элемент ИЛИ-НЕ 12, третий триггер 13. ключ 14, первый делитель 15 частоты, первый, второй и третий элементы И 16. 17 и 18 соответственно, первый формирователь 19 импульсов сброса, второй делитель 20 частоты, третий счетчик 21, дешифратор 22, од- новибратор 23, второй счетчик 24, реверсивный счетчик 25 и первый счетчик 2:6. Информационный вход умножителя частоты через входной формирователь 1 импульсов соединен с первым.входом первого фазового детектора 10 и с входом установки в единицу первого триггера 3. Выход первого триггера 3 соединен с управляющим входом ключа 14. Выход первого делителя 15 частоты соединен с вторым входом первого фазового детектора 10, выход которого соединен с входом фильтра 6 нижних частот. Выход третьего триггера 13 соединен с управляющим входом коммутатора 7. Выход первого элемента И 16 соединен с входом первого формирователя 19 импульсов сброса, выход которого соединен с входом установки в ноль первого счетчика 26. Выход управляемого генератора 8 импульсов соединен со счетным входом второго счетчика 24, выход которого соединен с информационным выходом умножителя частоты. Разрядные выходы первого счетчика 26 соединены соответственно с установочными входами реверсивного счетчика 25, вход вычитания которого соединен с выходом второго элемента И 17. Выход третьего элемента, И 18 соединен с входом сложения реверсивного счетчика 25, разрядные выходы которого соединены соответственно с установочными входами второго счетчика 24. Выход второго счетчика 24 соединен со счетным входом третьего счетчика 21, выход которого соединен с входом первого делителя 15 частоты. Выход делителя 15 соединен со старшим входным разрядом дешифратора 22, остальные входные разряды которого соединены соответственно с разрядными выходами третьего счетчика 21. Старший разрядный выход третьего счетчика 21 соединен с первым входом второго фазового детектора 11, второй вход которого соединен с выходом первого фазового детектора 10. Выход второго фазового детектора 11 соединен с первым входом элемента ИЛИ-НЕ 12, второй вход которого соединен с выходом третьего триггера 13. Выход элемента ИЛ И-Н Е 12 соединен с первыми входами первого, второго и третьего элементов И 16, 17 и 18 соответственно, вторые входы которых соединены соответственно с первым, вторым и третьим выходами дешифратора 22. Выход вгерого формирователя 9 импульсов сброса соединен с входом одновибратора 23 и входами установки в ноль реверсивного счетчика 25 и 5 третьего триггера 13, вход установки в единицу которого соединен с входом установки в единицу второго триггера 4, входом установки в ноль второго делителя 20 частоты и выходом первого формирователя 19 им0 пульсов сброса. Выход одновибратора 23 соединен с входом стробирования дешифратора 22. Выход управляемого генератора 8 импульсов соединен с информационным входом ключа 14, выход которого соединен

5 с входом второго делителя 20 частоты, выходом соединенного со счетным входом первого счетчика 26. Выход фильтра б нижних частот соединен с первым информационным входом коммутатора 7, второй инфор0 мационный вход которого соединен с выходом источника опорного напряжения 2. Выход коммутатора 7 соединен с входом управляемого генератора 8 импульсов. Выход входного формирователя 1 импульсов

5 соединен с первым входом четвертого элемента И 5, второй вход которого соединен с выходом первого триггера 3 и входом второго формирователя 9 импульсов сброса. Выход четвертого элемента И 5 соединен с

0 входом установки в ноль второго триггера 4, выход которого соединен с входом установки в ноль первого триггера 3.;

Умножитель частоты работает следующим образом.

5 Входной формирователь 1 импульсов преобразует входной сигнал в последовательность прямоугольных импульсов (фиг.26) с нормированными значениями уровня и длительности перепада. Эти им0 пульсы поступают на второй вход первого фазового детектора 10, а также на тактовый вход первого триггера 3 и второй вход четвертого элемента И.5.

Пусть в исходном состоянии, до поступ5 ления импульсов с выхода формирователя 1, первый триггер 3 находится в состоянии логического нуля, а второй триггер 4 и третий триггер 13 - в состоянии логической единицы. При этом ключ 14 будет закрыт, на выхо0 де элемента ИЛИ-НЕ 12 формируется сигнал логического нуля, источник 2 опорного напряжения подключен коммутатором 7 к входу управляемого генератора (УГ) 8. Напряжение источника 2 равно такому значе5 нию, при котором частота сигнала управляемого генератора 8 равна номинальному значению (среднему значению частоты рабочего диапазона).

Предположим, что запись информации в первый триггер 3 и установка в ноль второго триггера 4. осуществляется положительным перепадом уровня (фронтом) соответствующего сигнала.

С поступлением первого импульса с выхода формирователя 1 положительным пе- репадом в первый триггер 3 осуществляется запись логической единицы. Формирующимся на выходе триггера 3 положительным перепадом уровня сигнала, через Открытый четвертый элемент И 5, осуществ- ляется обнуление второго триггера 4. Ключ 14 открывается, и импульсы с выхода управляемого генератора 8 через второй делитель 20 частоты поступают на счетный вход первого счетчика 26 импульсов.

С поступлением второго импульса с выхода формирователя 1 в первый триггер 3 осуществляется запись логического нуля. Отрицательным перепадом уровня сигнала (спадом), формирующимся при этом на вы- ходе триггера 3, запускается второй формирователь 9 импульсов сброса, на выходе которого через интервал времени Т3 , равный времени задержки установки кода на установочных входах реверсивного счетчи- ка 25 после того, как ключ 14 будет закрыт, формируется импульс сброса. Этим импульсом осуществляется перепись кода измеренного периода входного сигнала Nx из первого счетчика 26 в реверсивный счетчик 25, обнуление третьего триггера 13 и запуск одновибратора 23. После обнуления триггера 13 вход управляемого генератора 8 коммутатором 7 подключается к выходу фильтра 6 нижних частот. Элемент ИЛИ-НЕ 12 открывается, и далее сигнал на его выходе будет определяться выходным сигналом второго фазового детектора 11.

После запуска одновибратора 23 на его выходе формируется импульс, блокирую- щий дешифратор 22. Длительность блокирующего импульса Гбл определяется постоянной времени схемы ФАПЧ и равна времени установления частоты сигнала управляемого генератора 8 при максимально возмож- ной начальной разности частот сигналов на входах первого фазового детектора 10, обусловленной погрешностью измерения периода входного сигнала.

Число импульсов NX, поступившее на вход первого счетчика 26 за период входного сигнала Тх. равно

Nx jtAtH-Atk) КУмн Тх/То КуМН, где То - номинальное значение период колебаний, формируемых управляемым гене- ратором 8; AtH часть периода квантующего сигнала, находящегося вне измеряемого интервала Тх: At - часть периода квантующего сигнала, находящегося между последним квантующим импульсом в

пределах интервала Тх и концом этого интервала; Кумн - коэффициент умножения частоты, равный коэффициенту деления второго делителя 20,

После записи кода Nx в реверсивный счетчик 25 коэффициент деления счетчика 24 становится равным Nx. На его выходе, который является выходом умножителя частоты, формируется сигнал с периодом ТВых, равным Твых Т0 Nx Тх/Кумн. Таким образом, данное устройство осуществляет деление периода входного сигнала или, что то же самое, умножение частоты.

Так как код N является приближенным значением аналоговой величины Тх, то значение Твых будет формироваться с погрешностью .Оумн , равной Оумн Твых Тх/КумнУстранение погрешности умножения Оумн осуществляется соответствующей подстройкой частоты управляемого генератора 8, т.е. изменением значения Туг, относительно номинального Т0 до достижения точного равенства ТВых Тх/Кумн ТУг Nx, где Туг - текущее значение частоты сигнала управляемого генератора 8.

Подстройка частоты управляемого генератора 8 выполняется схемой фазовой автоподстройки частоты (ФАПЧ), в состав которой входят третий счетчик 21, первый делитель 15 частоты, первый фазовый детектор 10 и фильтр 6 нижних частот. Счетчик 21 имеет коэффициент деления КуМц/2, а делитель 15 частоты - 2.

Процесс подстройки частоты управляемого генератора 8 осществляется следующим образом. На первый и второй.входы фазового детектора 10 поступают сигналы соответственно с выхода делителя 15 (фиг.2а), частота которого равна fBbix/KyMH, и с выхода формирователя 1, частота которого равна fx (фиг.2б). На выходе фазового детектора ТО, при условии, что схема ФАПЧ работает в режиме установившегося захвата частоты, формируется последовательность однополярНых импульсов с частотой 2f (фиг.2в). Скважность этих импульсов $г зависит от сдвига фаз входных сигналов ft и однозначно определяет уровень постоянной составляющей выходного сигнала фазового детектора 10. Постоянная составляющая выделяется фильтром б нижних частот и через коммутатор 7 поступает на управляющий вход генератора 8. Всякое изменение частоты входного сигнала fx вызы- eaiBT соответствующее изменение уровня постоянной составляющей и соответствующее изменение частоты сигнала генератора 8.

Если частота входного сигнала fx при текущем значении кода Nx не равна

fx твых/Кумн, но находится в пределах полосы захвата, схема ФАПЧ обеспечивает синхронизацию управляемого генератора 8 входным сигналом умножителя и тем самым установление равенства частот на входах первого фазового детектора 10. В процессе работы схема ФАПЧ отслеживает изменения частоты входного сигнала умножителя в пределах полосы удержания; При этом код NX не изменяется и погрешность умножения не возникает.

При плавном изменении частоты входного сигнала fx в диапазоне, превышающем полосу удержания схемы ФАПЧ, для предотвращения срыва синхронизации осуществляется коррекция текущего значения кода NX. Коррекция выполняется путем увеличения или уменьшения числа Nx последова-. тельно на единицу младшего разряда так, чтобы отклонение Af частоты сигнала генератора 8 от номинал ьного значения fo 1 /То уменьшалось и не превышало границ полосы удержания..

Коррекция значения кода NX осуществляется схемой, содержащей второй фазовый детектор 11, стробируемый дешифратор 22, элементы И 17 и 18, элемент ИЛИ-НЕ 12.: . ;

Осуществление коррекции кода Nx основано на том, что граничным значениям полосы удержания (или полосы захвата) соответствуют определенные граничные значения скважности импульсов вгр.тах и вгр. , формирующихся на выходе фазового детектора 10, а также на том, что временное положение этих импульсов.связано с временным положением импульсов, формирующихся на выходе старшего разряда счетчика 21. Взаимное положение данных импульсов определяется как режимом работы схемы ФАПЧ, так и свойствами первого, делителя 15 и генератора 8.

Предположим, что перепад уровня сигнала на выходе первого делителя 15(фиг.2а) формируется при положительном перепаде уровня сигнала на его входе (фиг.2г), а частота управляемого генератора 8 имеет такую зависимость от управляющего напряжения, при которой знак приращения частоты совпадает со знаком приращения управляющего напряжения (таким свойством обладает, например, LC-генератор с ва- рикапом в контуре).

Синхронизация управляемого генератора 8 входным сигналом умножителя осуществляется схемой ФАПЧ только при однозначной связи сдвига фаз входных сигналов фазового детектора 10с постоянной составляющей сигнала на его выходе.

У обычного фазового детектора (пер-е- множителя сигналов) такая связь имеет место в ограниченном интервале значений фазовых сдвигов - 0; я или тг; 2 л . В диапазоне фазовых сдвигов 0: 2 л результат фазового детектирования неоднозначен. Например, у фазового детектора, выполненного на логической схеме ИСКЛЮЧАЮЩЕЕ ИЛИ, зависимость постоянной составляющей выходного сигнала от сдвига фаз входных сигналов имеет вид треугольника с максимумами в точках 0 и 2 я и минимумом в точке п. Поэтому рабочий диапазон фазовых сдвигов входных сигналов

фазового детектора в режиме установившегося захвата частоты может располагаться только внутри одного из интервалов. - 0; я или щ 2 л , который определяется зависимостью частоты сигнала управляемого генератора от управляющего напряжения. В данном устройстве, при указанной выше зависимости, диапазон фазовых сдвигов сигнала на втором входе фазового детектора 10 (фиг.26) относительно сигнала, поступающего на его первый вход (фиг,2а), будет располагаться внутри интервала л; 1 л. При этом положительные перепады уровней сигналов, формирущихся на выходе фазового детектора 10 и на выходе старшего разряда

счетчика 21, будут совпадать во времени.

Определение временного положения импульсов, формирующихся на выходе фазового детектора 10, относительно сигнала, формирующегося на выходе старшего разряда счетчика 21, осуществляется вторым фазовым детектором 11. На его выходе формируется последовательность импульсов (фиг,2д), временное положение которых относительно имлудьсов, формирующихся на

выходе старшего разряда счетчика 21 (фиг,2г), зависит от выходного сигнала фазового детектора 10, т.е. от сдвига фаз его входных сигналов.

Предположим, что сдвиг фазы сигнала, поступающего на второй вход фазового детектора ТО (входного сигнала умножителя), относительно сигнала, поступающего на его первый вход, равен 3 nil. В этом случае

на выходе фазового детектора 1.0 формируются импульсы со скважностью $г 2, которые синфазны импульсам, формирующимся на выходе старшего разряда счетчика 21. При этом на выходе второго фазового детектора 11 устанавливается сигнал логической единицы, а на выходе элемента ИЛИ-НЕ будет сигнал логического нуля, которым элементы И 16, 17 и 18 удерживаются в закрытом состоянии,

При плавном уменьшении частоты входного сигнала fx (фиг.26) фазовый сдвиг ун увеличивается. Это приводит к уменьшению скважности (увеличению длительности гИ1) импульсов на выходе фазового детектора 10 (фиг.2в) и появлению отрицательных импульсов на выходе второго фазового детектора 11 (фиг.2д). Спад этих импульсов совпадает с отрицательным перепадом уровня выходного сигнала старшего разряда счетчика 21, а временное положение фронта зависит от скважности импульсов 0т поступающих с выхода фазового детектора 10. Длительность .ТИ2 этих импульсов равна тИ2 ТИ1 - Тном То (1 /2 0т - 0,25), где ГИ1 - длительность импульсов, поступающих с выхода первого фазового детектора 10; тном - длительность импульсов ТИ1 при 0г 2.

На выходе 3 дешифратора 22, с периодом Т0, формируются стробирующие импульсы (фиг.2ж), фронт которых опережает фронт импульсов, поступающих с выхода второго фазового детектора (фиг.2д), на время не менее tpпри Ти2 тф2 То (1 /2 Ap.rnin -0,25). Значение tp определяется быстродействием цифровых элементов умножителя (длительностью импульсов, при которой обеспечивается нормальная работа этих элементов). Спад стробирующйх импульсов запаздывает относительно спада импульсов, поступающих с выхода старшего разряда счетчика 21, на время trp2 тгр2 .

Когда скважность импульсов на выходе первого фазового детектора 10 достигает граничного значения 0г 0rp.min , длитель-; ность импульсов на выходе второго фазового детектора 11 становится равной и2 - Тгр.2 и они начинают перекрываться во времени со стробирующими импульсами, поступающими с выхода 3 дешифратора 22. На выходе элемента И 18 начинают формироваться корректирующие импульсы (фиг.2и), которые поступают на суммирующий вход реверсивного счетчика 25. После прихода первого импульса текущее значение кода NX, содержащегося в реверсивном счетчике 25, увеличивается на единицу. В результате период следования импульсов на выходе счетчика 24 (выходе умножителя) ТВых увеличивается на ДТ Туг. Период следования импульсов на выходе делителя 15 также увеличивается, и фазовый сдвиг входных сигналов fh первого фазового детектора 10 уменьшается. На выходе второго фазового детектора 11 скважность импульсов увеличивается (длительность тИ2 уменьшается). Если значение скважности импульсов на выходе фазового детектора 10 0т становится больше граничного значения

0

5

0

5

0

5

0

5

0

5

0т 0rp.minTO импульсы, поступающие с выхода 3 дешифратора 22, не будут перекрываться во времени с импульсами, формирующимися на выходе второго фазового детектора. Формирование корректируй ющих импульсов прекращается, и на выходе элемента И 18 устанавливается уровень логического нуля.

Предположим, что частота входного сигнала умножителя fx плавно увеличивается (период Тх уменьшается). В этом случае фазовый сдвиг сигналов г, поступающих на входы фазового детектора 10, уменьшается. При fn 3 ж/2 на выходе фазового детектора 11 формируются отрицательные импульсы, фронт которых совпадает со спадом импульсов, поступающих с выхода старшего разряда счетчика 21, а временное положение спада определяется скважностью выходных импульсов первого фазового детектора 10. Длительность ТИ2 этих импульсов в данном случае будет равна

Ги2 Гнрм - Т„1 Т0 (0,25-1 /2 0т).

На выходе 2 дешифратора 22, с периодом То, формируется последовательность стробирующйх импульсов (фиг.2е), спад которых запаздывает относительно спада импульсов, поступающих со второго фазового детектора 11 (фиг.2д), на время не менее tp (как и в предыдущем случае) при

ГИ2 :Ј ГГР2 Т0 (0,25 - 1/2 ftp.max). Ф РОНТ

стробирующйх импульсов опережает спад импульсов, формирующихся на выходе старшего разряда счетчика 21, на время trpl 5:%,1 .. .

Когда скважность импульсов на выходе первого фазового детектора 10 достигает граничного значения 0гр.тах , длительность импульсов Ти2 , поступающих с выхода второго фазового детектора, становится равной . Ги2 - TVpi и они перекрываются во времени с импульсами, поступающими с выхода 2 дешифратора 22, На выходе элемента И 17 формируются корректирующие импульсы, поступающие на вычитающий вход реверсивного счетчика 25.

После поступления корректирующего импульса текущее значение кода NX уменьшается на единицу, вследствие чего период .следования импульсов на выходе второго счетчика 24 (выходе, умножителя) уменьша-. ется на AT Туг. Соответственно уменьшается период следования импульсов на выходе первого делителя 15, и фазовый сдвиг сигналов на входах фазового детектора 10 увеличивается. Если значение.скважности 0т становится меньше граничного значения .тах , то формирование корректирующих импульсов прекращается.

Таким образом, при монотонном изменении частоты входного сигнала в пределах, превышающих границы полосы удержания ФАПЧ, осуществляется корректировка кода NX путем последовательного изменения его значения на единицу. Максимальная абсолютная погрешность умножения, возникающая при этом, равна гУ t Туг.

Предположим, что частота входного сигнала находится вне границ полосы захвата ФАПЧ и, следовательно, синхронизация управляемого генератора 8 отсутствует. В этом случае фазовый сдвиг сигналов, поступающих на входы фазового детектора 10, будет периодически изменяться в диапазоне 0; 2 л.

Когда текущее значение фазового сдвига будет находиться за пределами рабочего диапазона, Т.е. rp.min О И 2 П (fh rp.max ,

то в пределах временного интервала At гс (фиг.Зе), одна из границ которого опережает фронт импульсов, формирующихся на выходе старшего разряда счетчика 21, на время

TO Тр/4 - тгр2 , а вторая граница запаздывает относительно того же фронта на время

тз То/4 - Ггр1 , выходной сигнал второго фазового детектора 11 будет иметь уровень логического нуля (фиг.Зд). Соответственно, в пределах интервала At, на выходе схемы ИЛИ-НЕ 12 (и первом входе элемента И 1.6) будет сигнал логической единицы. В этом же временном интервале элемент И 16 открывается положительным импульсом, формирующимся на выходе 1 дешифратора 22 (фиг.Зе). Частота следования импульсов, формирующихся на выходе 1 дешифратора 22, равна тСтр 2/Т0.

Фронтом первого сформировавшегося на выходе элемента И 16 положительного импульса (фиг.Зж) запускается.первый формирователь 19 импульсов сброса. Этим импульсом осуществляется обнуление второго делителя 20 частоты и первого счетчика 26 импульсов, а также установка в-единицу второго и третьего триггеров 4 и 13 соответственно. Элемент ИЛИ-НЕ закрывается, и на его выходе устанавливается сигнал логического нуля, которым блокируется формирование импульсов на выходах элементов И 16, 17 и 18. Управляющий вход генератора 8 коммутатором 7 подключается к источнику 2 опорного напряжения.

В результате этих действий схема изме рения длительности периода входного сигнала умножителя Тх подготавливается к выполнению цикла измерения. Фронтом первого поступившего с выхода формирователя 1 импульса триггер 3 устанавливается в состояние логической единицы и т.д., в

соответствии с процедурой измерения Периода входного, сигнала, описанной ранее. Неизбежная погрешность измерения длительности периода входного сигнала в 5 предлагаемом умножителе частоты определяет только начальную расстройкуAfчастот на входах первого фазового детектора 10. У прототипа, как было показано ранее, погрешность измерения периода входного

0 сигнала непосредственно является причиной возникновения погрешности умножения. Поэтому допускаемая максимальная погрешность измерения периода входного сигнал а (зависящая от соотношения частот

5 входного и квантующего сигналов)у предлагаемого умножителя может быть больше, чем у прототипа. Это обстоятельство обусловливает наличие дополнительного положительного эффекта - расширения

0 рабочего диапазона в сторону высоких частот.

При равенстве допустимых значений погрешности умножения, в общем случае, частота входного сигнала у предлагаемого

5 умножителя может быть в 2 раза выше, чем у прототипа (ограничивается погрешностью умножения, возникающей из-за дискретности коэффициента деления управляемого делителя частоты). Если частота входного

0 сигнала постоянна, то расширение рабочего диапазона частот может быть еще более существенным. В этом случае погрешность измерения длительности периода входного сигнала ограничивается только полосой за.5 хвата ФАПЧ, значение которой обычно составляет единицы процентов.

Формула изобретения Умножитель частоты, содержащий входной формирователь импульсов, первый фа0 зовый детектор, первый делитель частоты, фильтр нижних частот, коммутатор, управляемый генератор импульсов, первый, второй и третий счетчики, первый, второй и третий триггеры, первый и второй формиро5 ватели импульсов сброса, ключ и первый и второй элементы И, причем информационный вход умножителя частоты через входной формирователь импульсов соединен с первым входом первого фазового детектора

0 и с входом установки в 1 первого триггера, выход которого соединен с управляющим входом ключа, выход первого делителя частоты соединен с вторым входом первого фазового детектора, выход которого соединен

5 с входом фильтра нижних частот, выход третьего триггера соединен с управляющим входом коммутатора, выход первого элемента И соединен с входом первого формирователя импульсов сброса, выход которого соединен с входом установки в О первого

счетчика, выход управляемого генератора импульсов соединен со счетным входом второго счетчика, выход которого соединен с информационным выходом умножителя частоты, о т л и ч а ю щ и и с я тем, что, с целью повышения точности умножения частоты, в него введены второй делитель частоты, реверсивный счетчик, второй фазовый детектор, источник опорного напряжения, дешифратор, элемент ИЛИ-НЕ, одновибра- тор и третий и четвертый элементы И, причем разрядные выходы первого счетчика соединены соответственно с установочными входами реверсивного счетчика, вход вычитания которого соединен с выходом второго элемента И, выход третьего элемента И соединен с входом сложения реверсивного счетчика, разрядные выходы которого соединены соответственно с установочными входами второго счетчика, выход которо- то соединен со счетным входом третьего счетчика, выход которого соединен с входом первого делителя частоты, выход которого соединен со старшим входным разрядом дешифратора, остальные входные, разряды которого соединены соответственно с разрядными выходами третьего счетчика, старший разрядный выход которого соединен с первым входом второго фазового детектора, второй вход которого соединен с выхо- дом первого фазового детектора, выход второго фазового детектора соединён с первым входом элемента ИЛИ-НЕ, второй вход которого соединен с выходом третьего триггера, выход элемента ИЛИ-НЕ соединен с

первыми входами первого, второго и третьего элементов И, вторые входы которых соединены соответственно с первым, вторым и третьим выходами дешифратора, выход второго формирователя импульсов сброса соединен с входом одновибратора и входами установки в О реверсивного счетчика и третьего триггера, вход установки в Г которого соединен с входом установки в 1 второго триггера, входом установки в О второго делителя частоты и выходом первого формирователя импульсов сброса, выход одновибратора соединен с входом строби- рования дешифратора, выход управляемого генератора импульсов соединен с информационным входом ключа, выход которого соединен с входом второго делителя частоты, выход которого соединен со счетным входом первого счетчика, выход фильтра нижних частот соединен с первым информационным входом коммутатора, второй ин; формационный вход которого соединен с выходом источника опорного напряжения, а выход коммутатора соединен с входом управляемого генератора импульсов, выход входного формирователя импульсов соединён с первым входом четвертого элемента И, второй вход которого соединен с выходом первого триггера и входом второго формирователя импульсов сброса, а выход четвертого элемента И соединен с входом установки в 6 второго триггера, выход которого соединен с входом установки в О первого триггера.

ФИГ. 2. .

| Умножитель частоты | 1979 |

|

SU834697A1 |

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

| Умножитель частоты | 1984 |

|

SU1179334A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-02-23—Публикация

1990-11-21—Подача