00 О) 00 СХ)

Изобретение относится к электротехнике и может быть использовано в источниках электропитания устройств автоматики и вычислительной техники.

Цель изобретения - снижение потерь и повышение надежности устройства.

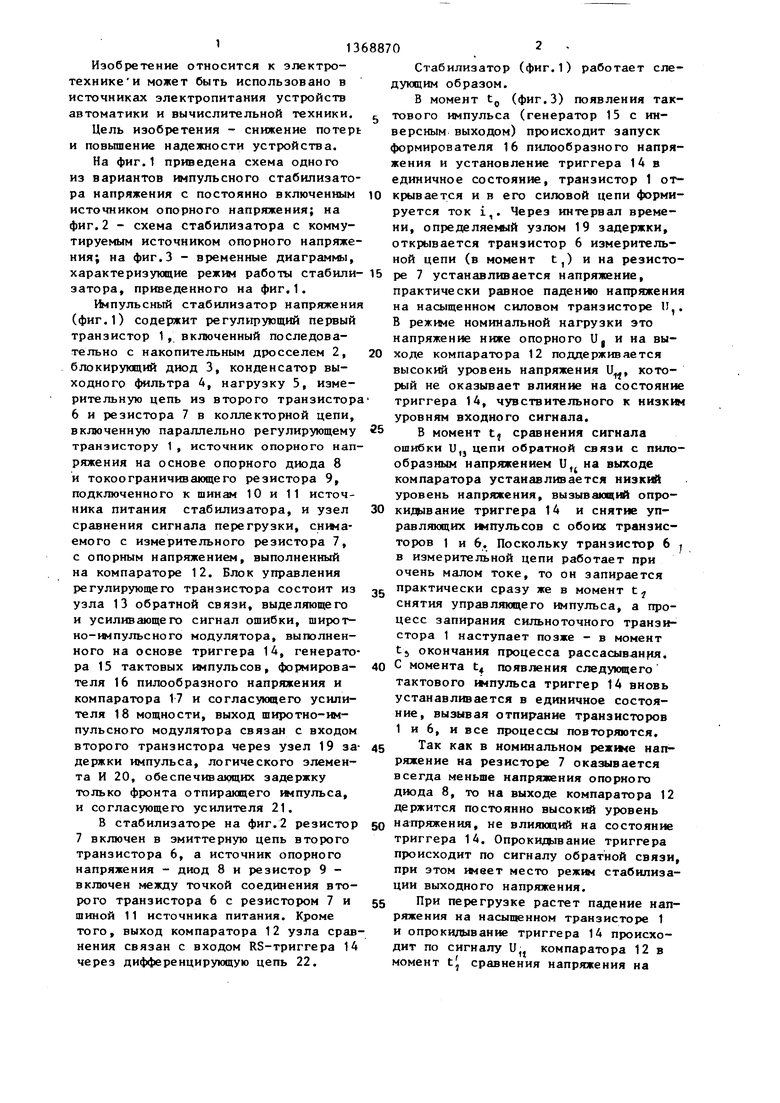

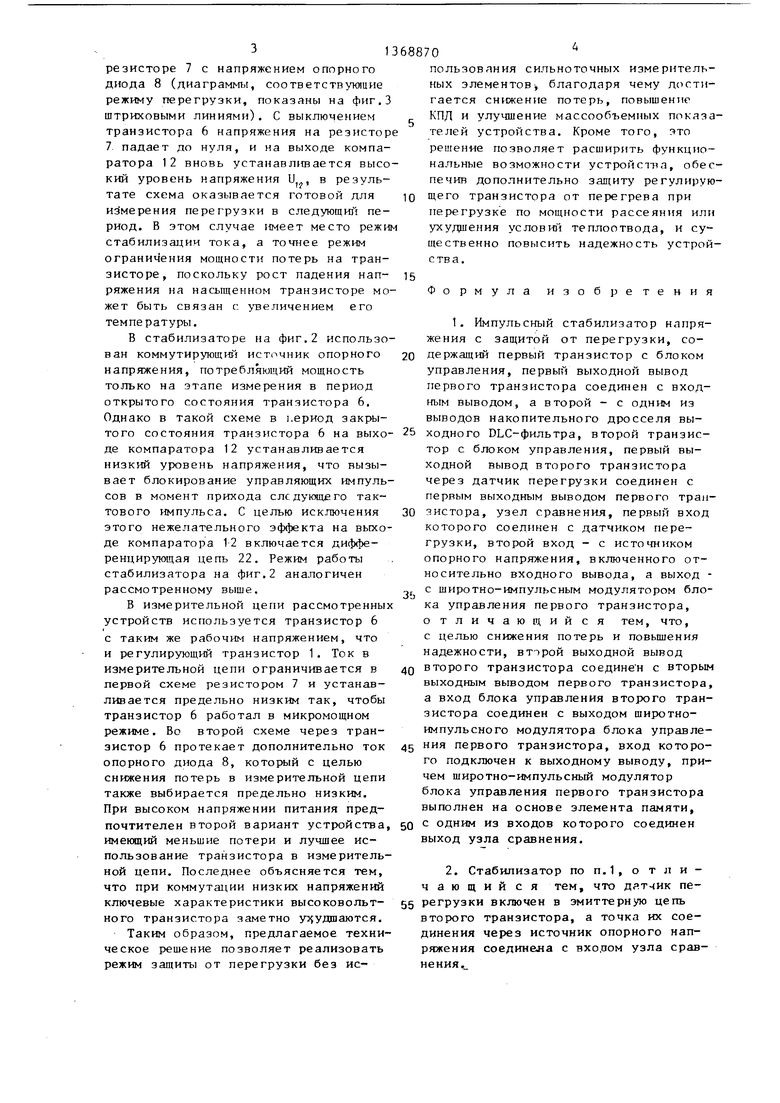

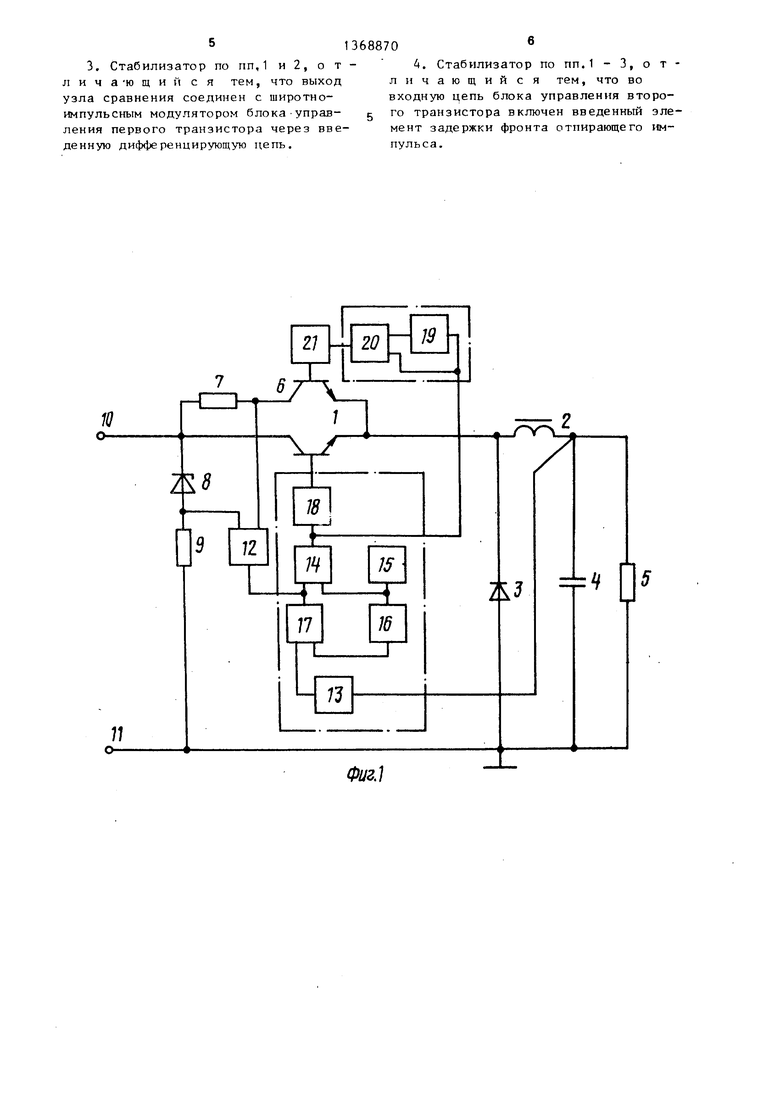

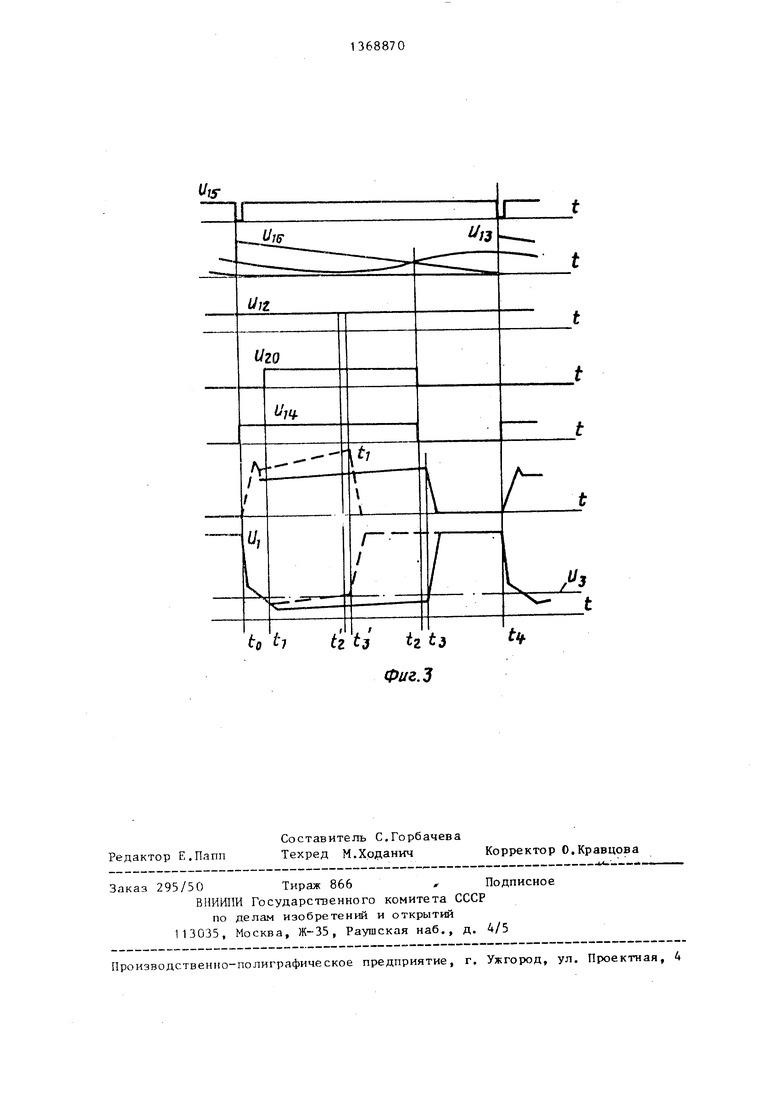

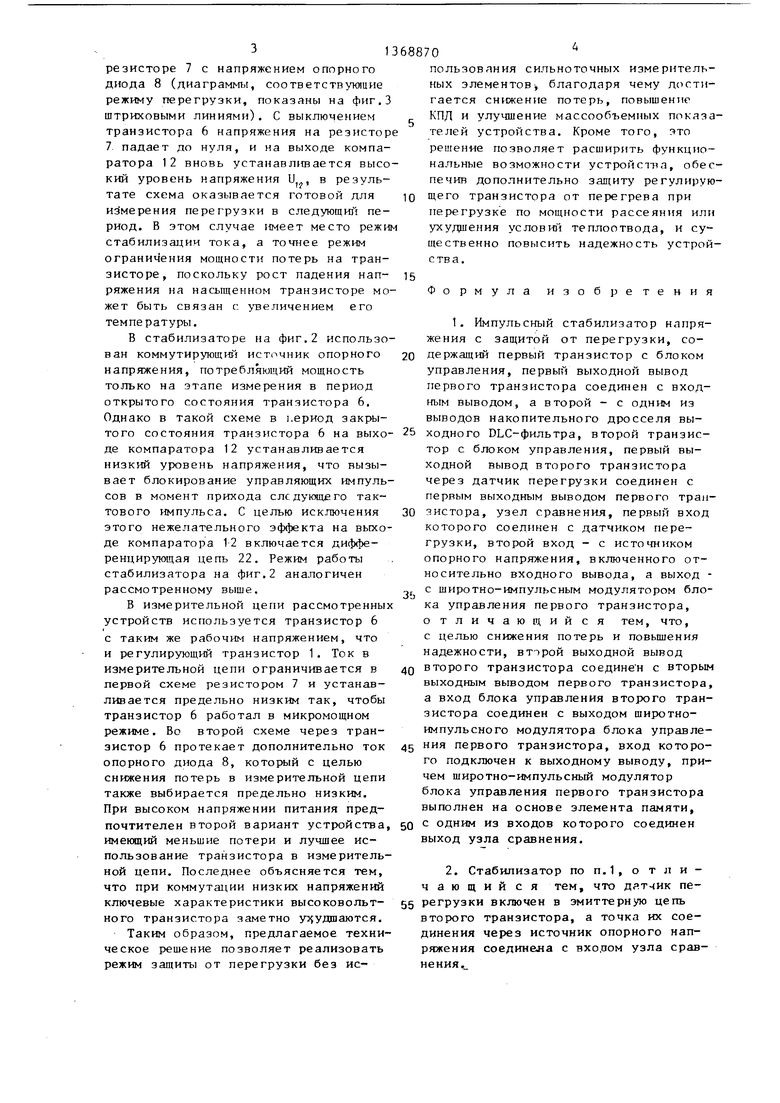

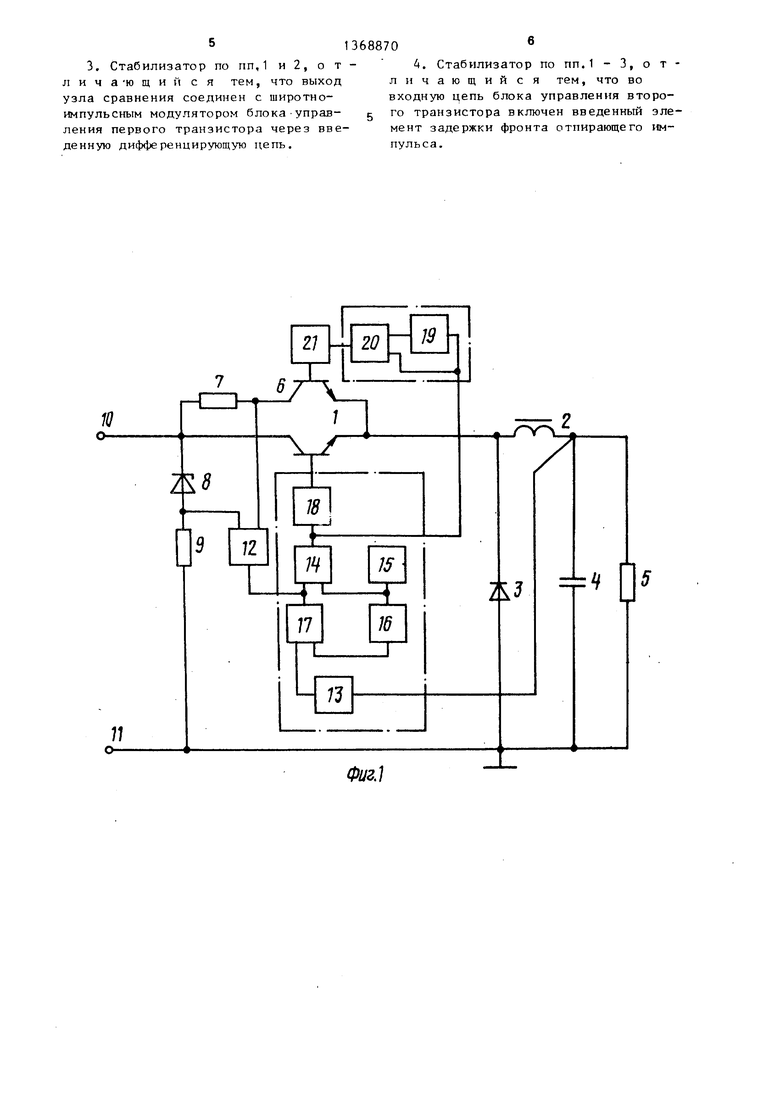

На фиг.1 приведена схема одного из вариантов импульсного стабилизатора напряжения с постоянно включенным источником опорного напряжения; на фиг.2 - схема стабилизатора с коммутируемым источником опорного напряжения; на фиг.З - временные диаграммы,

В момент tp (фиг.З) появления тового импульса (генератор 15 с и версным выходом) происходит запус формирователя 16 пилообразного на жения и установление триггера 1А единичное состояние, транзистор 1 крывается и в его силовой цепи фо руется ток i,. Через интервал вре ни, определяемый узлом 19 задержк открывается транзистор 6 измерите ной цепи (в момент t,) и на рези

характеризующие режим работы стабили- 15 ре 7 устанавливается напряжение.

Стабилизатор (фиг.1) работает следующим образом.

В момент tp (фиг.З) появления тактового импульса (генератор 15 с инверсным выходом) происходит запуск формирователя 16 пилообразного напряжения и установление триггера 1А в единичное состояние, транзистор 1 открывается и в его силовой цепи формируется ток i,. Через интервал времени, определяемый узлом 19 задержки, открывается транзистор 6 измерительной цепи (в момент t,) и на резисторе 7 устанавливается напряжение.

| название | год | авторы | номер документа |

|---|---|---|---|

| Стабилизированный конвертор | 1978 |

|

SU748721A1 |

| ИМПУЛЬСНЫЙ СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ ПОНИЖАЮЩЕГО ТИПА | 1991 |

|

RU2006062C1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ | 1992 |

|

RU2036510C1 |

| Ключевой стабилизатор постоянного напряжения | 1990 |

|

SU1728854A1 |

| Устройство для управления и защиты преобразователя | 1985 |

|

SU1336171A1 |

| Импульсный стабилизатор напряжения | 1983 |

|

SU1121659A1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ | 2003 |

|

RU2260833C1 |

| Импульсный понижающий стабилизатор постоянного напряжения | 1990 |

|

SU1786477A1 |

| Преобразователь постоянного напряжения в постоянное | 1986 |

|

SU1420636A2 |

| ИСТОЧНИК ПИТАНИЯ ДЛЯ ЭЛЕКТРОЛЮМИНЕСЦЕНТНОЙ ПАНЕЛИ | 2001 |

|

RU2210120C1 |

Изобретение относится к электротехнике и может быть использовано в источниках электропитгния устройств ) автоматики и вычислительной техники. Цель изобретения - снижение потерь и повьшение надежности. В устр-ве использована маломощная измерительная цепь последовательно соединенных второго ключевого транзистора и рези- стивного датчика, включенного параллельно регулирующему ключевому транзистору, которая позволяет фиксировать перегрузку как по току, так и по мощности рассеивания регулирующего транзистора. Кроме того,в устр-ве использован коммутирующий источник опорного напряжения, имеющий меньшие потери. В результате достигается повьшение КПД и надежности устр-ва. 3 з.п. ф-лы, 3 ил. с в и

затора, приведенного на фиг.1.

Импульсный стабилизатор напряжения (фиг.1) содержит регул фующий первый транзистор 1, включенный последовательно с накопительным дросселем 2, блокирующий диод 3, конденсатор выходного фильтра А, нагрузку 5, измерительную цепь из второго транзистор 6 и резистора 7 в коллекторной цепи, включенную параллельно регулирующему транзистору 1, источник опорного напряжения на основе опорного диода 8 и токоограничивающего резистора 9, подключенного к шинам 10 и 11 источника питания стабилизатора, и узел сравнения сигнала перегрузки, снша- емого с измерительного резистора 7, с опорным напряжением, выполненный на компараторе 12. Блок управления регулирующего транзистора состоит из узла 13 обратной связи, выделяющего и усиливающего сигнал ошибки, широт- но-импульсного модулятора, выполненного на основе триггера 14, генератора 15 тактовых импульсов, формирователя 16 пилообразного напряжения и компаратора 17 и согласующего усилителя 18 мощности, выход широтно-им- пульсного модулятора связан с входом второго транзистора через узел 19 задержки импульса, логического элемента И 20, обеспечивающих задержку только фронта отпирающего импульса, и согласующего усилителя 21.

В стабилизаторе на фиг.2 резистор 7 включен в эмиттерную цепь второго транзистора 6, а источник опорного напряжения - диод 8 и резистор 9 - включен между точкой соединения второго транзистора 6 с резистором 7 и шиной 11 источника питания. Кроме того, выход компаратора 12 узла сравнения связан с входом RS-триггера 14 через дифференцирующую цепь 22.

0

0

5

5

практически равное падению напряжения на насыщенном силовом транзисторе U,. В режиме номинальной нагрузки это напряжение ниже опорного U, и на выходе компаратора 12 поддерживается высокий уровень напряжения U, который не оказывает влияние на состояние триггера 14, чувствительного к низким уровням входного сигнала.

Б момент tj сравнения сигнала ошибки U,j цепи обратной связи с пилообразным напряжением U, на выходе компаратора устанавливается низкий уровень напряжения, вызывающий опро- кидавание триггера 14 и снятие управляющих 4Пульсов с обоих транзисторов 1 и 6. Поскольку транзистор 6 j в измерительной цепи работает при очень малом токе, то он запирается практически сразу же в момент t снятия управляющего импульса, а процесс запирания сильноточного транзистора 1 наступает позже - в момент tj окончания процесса рассасывания. 40 С момента t4 появ;юния следующего тактового (мпульса триггер 14 вновь устанавливается в единичное состояние, вызывая отпирание транзисторов 1 и 6, и все процессы повторяются.

Так как в номинальном режиме напряжение на резисторе 7 оказывается всегда меньше напряжения опорного диода 8, то на выходе компаратора 12 держится постоянно высокий уровень напряжения, не влияющий на состояние триггера 14. Опрокидывание триггера происходит по сигналу обратной связи, при этом имеет место режим стабилизации выходного напряжения.

При перегрузке растет падение напряжения на насыщенном транзисторе 1 и опрокидывание триггера 14 происходит по сигналу Ujj компаратора 12 в момент tj сравнения напряжения на

45

50

55

резисторе 7 с напряжением опорного диода 8 (диаграммы, соответствующие режиму перегрузки, показаны на фиг.3 штриховыми линиями). с выключением транзистора 6 напряжения на резистор 7 падает до нуля, и на выходе компаратора 12 вновь устанавл1шается высокий уровень напряжения U , в результате схема оказывается готовой для измерения перегрузки в следующий период. В этом случае имеет место режи стабилизшдии тока, а точнее режим ограничения мощности потерь на транзисторе, поскольку рост падения напряжения на насыщенном транзисторе может быть связан с величением его температуры.

В стабилизаторе на фиг.2 использован коммутирующий источник опорного напряжения, потребляющий мощность только на этапе измерения в период открытого состояния транзистора 6, Однако в такой схеме в ьериод закрытого состояния транзистора 6 на выходе компаратора 12 устанавливается низкий уровень напряжения, что вызывает блокирование управляющих импульсов в момент прихода следующего тактового импульса. С целью исключения этого нежелательного эффекта на выходе компаратора 12 включается дифференцирующая цепь 22. Режим работы стабилизатора на фиг.2 аналогичен рассмотренному выше.

В измерительной цепи рассмотренны устройств используется транзистор 6 с таким же рабочим напряжением, что и регулирующий транзистор 1. Ток в измерительной цепи ограничивается в первой схеме резистором 7 и устанавливается предельно низким так, чтобы транзистор 6 работал в микромощном режиме. Во второй схеме через транзистор 6 протекает дополнительно ток опорного диода 8, который с целью снижения потерь в измерительной цепи также выбирается предельно низким. При высоком напряжении питания предпочтителен второй вариант устройства имеющий меньшие потери и лучщее использование транзистора в измерительной цепи. Последнее объясняется тем, что при коммутации низких напряжений ключевые характеристики высоковольтного транзистора заметно ут удшаются.

Таким образом, предлагаемое техническое решение позволяет реализовать режим защиты от перегрузки без ис

пользования сильноточных измерительных элементовi благодаря чему достигается снижение потерь, повышенно КПД и улучшение массообъемных показателей устройства. Кроме того, это решение позволяет расширить функциональные возможности устройстаа, обеспечив дополнительно зап(иту регулирующего транзистора от перегрева при перегрузке по мощности рассеяния или ухудшения условий теплоотвода, и существенно повысить надежность устройства.

Формула изобретения

5

6

19

го

HI

6 7

Фиг. 2

to i 1

| Импульсный стабилизатор напряжения постоянного тока | 1983 |

|

SU1116419A2 |

| Непрерывно-ключевой стабилизатор напряжения | 1984 |

|

SU1179300A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1988-01-23—Публикация

1986-07-14—Подача