Изобретение относится к импульсной технике и может быть использовано в микромощных интегральных схемах

Целью изобретения является уменьшение потребляемой мощности.

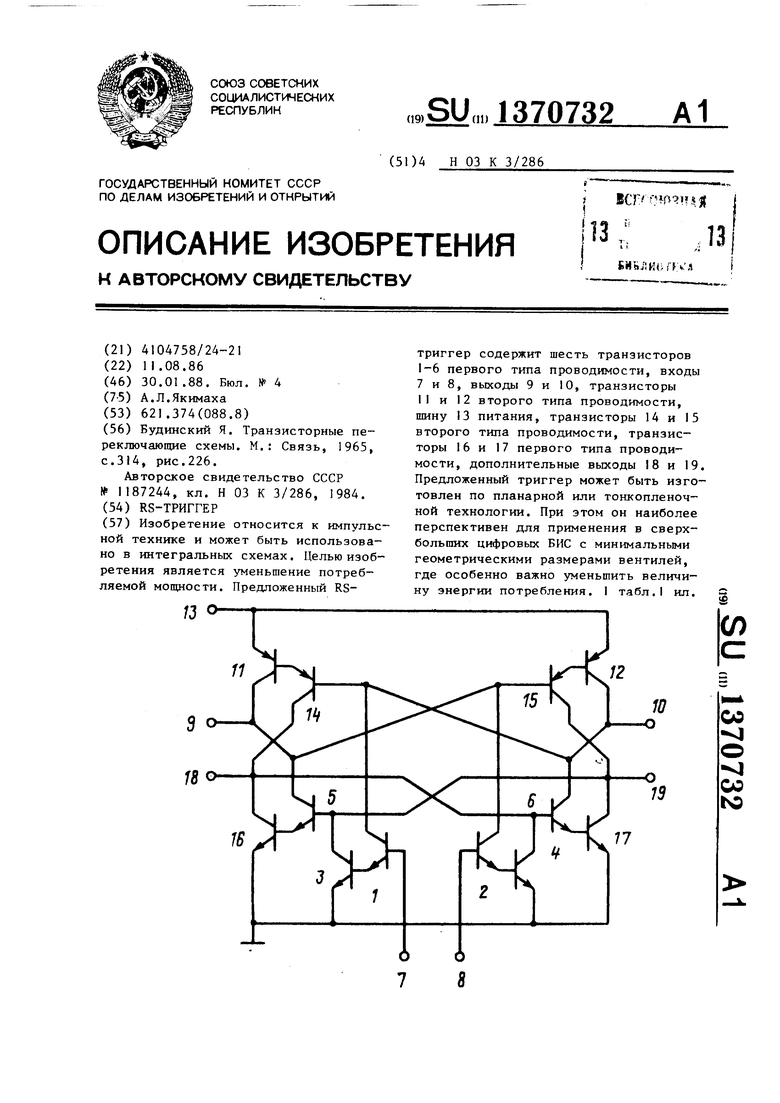

На чертеже изображена электрическая схема устройства.

RS-триггер содержит шесть транзисторов 1 - 6 первого типа проводимое- ти, базы транзисторов 1 и 2 соединены соответственно с первым 7 и вторым 8 входами, эмиттеры - соответственно с базами транзисторов 3 и 4, эмиттеры которых соединены с общей Ш1ШОЙ, а коллекторы подключены соответственно к базам транзисторов 5 и 6, коллекторы которых соединены соответственно с первым 9 и вторым 10 выходами и подключены соответственно к коллекторам седьмого 11 и восьмого 12 транзисторов второго типа проводимости, эмиттеры которых соединены с шиной 13 питания, коллекторы транзисторов 1 и 2 соединены соответст- венно с базами девятого 14 и десятог 15 тра1нзисторов второго типа проводимости, эмиттеры одиннадцатого 16 и двенадцатого 17 транзисторов первого типа проводимости соединены с общей шиной, базы подключены соответственно к эмиттерам транзисторов 5 и 6, коллекторы соединены соответственно с первым 18 и вторым 19 дополнительными выходами и подключены соответственно с коллектором транзисторов 14 и 15, эмиттеры которых соединены соответственно с базами транзисторов II и 12, а базы подключены соответственно к коллекторам транзисторов 6 и 5, базы которых соединены соответственно с коллекторами транзисторов 16 и 17.

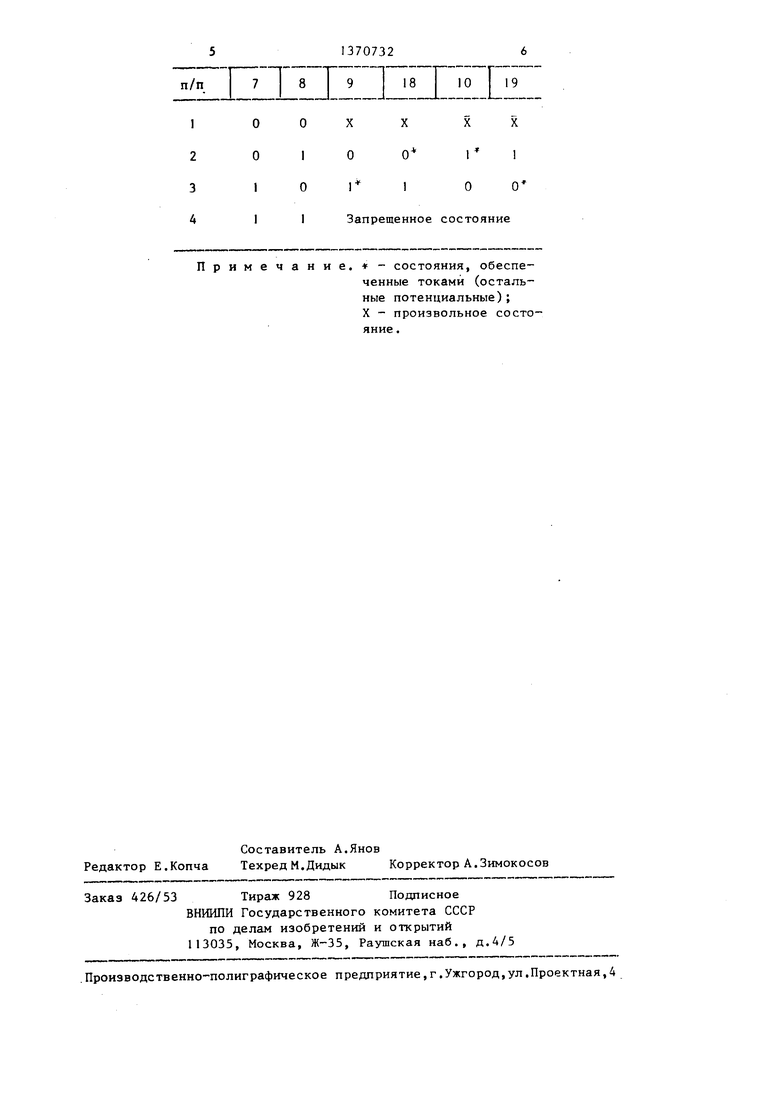

В таблице представлены возможные логические состояния на входах и вы- ходах устройства.

RS-триггер работает следующим образом.

Пусть на входы 7 и В поступают низкие уровни напряжения лог,О (см. таблицу). Тогда транзисторы 1, 3 и 2, 4 будут находиться в закрытом состоянии, а значит не будут влиять на состояния остальных транзисторов 5,6, 11,12,14,15,16 и 17, Таким образом, на выходах 9 и 18 будет произвольное состояние и иьгаерсное ему - X - на выходах 10 и 19,

5 0 5 0 з 0

5

0

5

Если на вход 7 поступает уровень лог. 1 , а на вход В - уровень лог,О, то независимо от предыдущего состояния RS-триггера на выходах 9 и 18 установится высокий уровень лог.1, а на выходах 10 и 19 - низкий уровень лог.О напряжения. При этом транзисторы 1,3,14,11,6 и 17 будут открыты, а транзисторы 15,16,2,4,15 и 12 - закрыты. Состояние лог.1 на выходе 9 обеспечивается током открытого транзистора 11, в то время как состояние ЛОГ.1 на выходе 18 является потенциальным, поскольку ток коллектора транзистора 14 значительно меньше тока коллектора транзистора 11, Аналогично состояние лог.О на выходе 19 также обеспечивается током коллектора транзистора 17, в то время как состояние лог.О на выходе 10 током не обеспечивается, поскольку ток коллектора транзистора 6 значительно меньше тока коллектора транзистора 17.

Если на вход 7 поступает уровень лог,О, а на вход 8 - уровень лог,I, тогда независимо от предыдущего состояния RS-триггера на выходах 9 и 18 будет низкий уровень напряжения лог,О, а на выходах 10 и 19 - высокий уровень напряжения лог,1. При этом транзисторы 5, 16, 2, 4, 15 и 12 будут открыты, а транзисторы 1, 3, 14, 11, 6 и 17- закрыты. Состояние лог.О на выходе 18 обеспечивается током транзистора 16, а состояние лог,О на выходе 9 не обеспечивается током. Аналогично состояние лог,1 на выходе 10 также обеспечивается током открытого транзистора 12, а состояние лог,1 на выходе 19 является потенциальным.

При поступлении на оба входа 7 и 8 высоких уровней напряжения лог,I открьшаются все транзисторы, входящие в схему устройства. На выходах 9, 18 и 10, 19 взаимно противоположные состояния, тогда как на выходах 18 и 19, а также 9 и 10 состояния совпадают. Такое состояние для RS- триггера должно быть запрещенным, поскольку после его снятия на всех выходах устанавливается неопределенное и непредсказуемое состояние.

В режиме переключения из одного логического состояния в другое исключена ситуация прохождения сквозного тока как через мощные транзисторы 16, 11 или 17, 12, а также при принудительном переключении через транзисторы 3, 12 и 4, 11. Это в значительной мере уменьшает потребление энергии устройством при переключении. Предлагаемое устройство имеет минимальное потребление энергии по своим управляющим входам 7 и 8, поскольку все дополнительные транзисторы включены по схеме Дарлингтона, т.е. по существу инверторы управляются практически потенциалами, как и МДП-транзисторы, только величина пороговых напряжений здесь жестко стабилизирована. К напряжению питания V(шина 13) предъявляется

С L.

требование, чтобы оно находилось в диапазоне

(V,,+V,p) - V,,. 4 ,84В,

де V

, р

лор

пороговые напряжения транзисторов, разделяющие экспоненциальные и полиномиальные участки БАХ; ширина запрещенной зоны в полупроводнике, из которого изготовлены все

(cf

ДОР

4,21 В

транзисторы для Si).

В предлагаемом устройстве реализована функция расщепления выходных напряжений, которые могут обеспечиваться токами открытых транзисторов или нет. Например, к выходам 9 и 10 можно подключать базы транзисторов первого типа проводимости, а к выходам 18 и 19 можно подключать базы транзисторов с вторым типом проводимости.

RS-триггер предназначен для изготовления по планарной или тонкопленочной технологиям. Топология изготовления транзисторов - гребенчатая Геометрические размеры транзисторов 16, 17, 11 и 12 могут быть равны друг другу или отличаться в зависимости от концентрации легирующих примесей в полупроводнике областей баз, а геометрические размеры транзисторов 1,2,3,4,14 и 15 могут быть в

10

15

0

.

30

35

40

45

50

5-10 раз меньше размеров указанных транзисторов.

Предлагаемое устройство наиболее перспективно для применения в сверхбольших цифровых БИС с минимальными геометрическими размерами вентилей, где особенно важно уменьшить величину энергии потребления.

Формула изобретения

RS-триггер, содержащий шесть транзисторов первого типа проводимости, базы первого и второго транзисторов соединены соответственно с первым и вторым входами, эмиттеры - соответственно с базами третьего и четвертого транзисторов, эмиттеры которых соединены с общей шиной, а коллекторы подключения соответственно к базам пятого и шестого транзисторов, коллекторы которых соединены соответственно с первым и вторым выходами и подключены соответственно к коллекторам седьмого и восьмого транзисторов второго типа проводимости, эмиттеры которых соединены с шиной питания, коллекторы первого и второго транзисторов соединены соответственно с базами девятого и десятого транзисторов второго типа проводимости, отличающийся тем, что, с целью уменьшения потребляемой мощности, введены одиннадцатый и двенадцатый транзисторы первого типа проводимости, эмиттеры которых соединены с общей шиной, базы подключены соответственно к эмиттерам пятого и шестого транзисторов, коллекторы соединены соответственно с первым и вторым дополнительными выходами и подключены соответственно к коллекторам девятого и десятого транзисторов, эмиттеры которых соединены соответственно с базами седьмого и восьмого транзисторов, а базы подключены соответственно к коллекторам шестого и пятого транзисторов, базы которых соединены соответственно с коллекторами одиннадцатого и двенадцатого транзисторов.

римечание.- состояния, обеспеченные токами (остальные потенциальные); X - произвольное состояние .

| название | год | авторы | номер документа |

|---|---|---|---|

| Триггер | 1989 |

|

SU1691931A1 |

| Устройство реверсирования тока | 1988 |

|

SU1598154A2 |

| Триггер | 1989 |

|

SU1690176A1 |

| Триггер с предварительной установкой | 1988 |

|

SU1598125A1 |

| ИМПУЛЬСНЫЙ СТАБИЛИЗАТОР НАПРЯЖЕНИЯ | 2001 |

|

RU2216765C2 |

| Силовой RS-триггер | 2023 |

|

RU2813798C1 |

| Источник вторичного электропитания для сети постоянного напряжения | 1990 |

|

SU1786476A1 |

| Счетный разряд | 1989 |

|

SU1684926A1 |

| Устройство для управления двухфазным асинхронным электродвигателем | 1990 |

|

SU1777225A1 |

| ИМПУЛЬСНЫЙ СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ ПОНИЖАЮЩЕГО ТИПА | 1991 |

|

RU2006062C1 |

Изобретение относится к импульсной технике и может быть использовано в интегральных схемах. Целью изобретения является уменьшение потребляемой мощности. Предложенный RS/3 триггер содержит шесть транзисторов 1-6 первого типа проводимости, входы 7 и 8, выходы 9 и 10, транзисторы II и 12 второго типа проводимости, щину 13 питания, транзисторы 14 и 15 второго типа проводимости, транзисторы 16 и 17 первого типа проводимости, дополнительные вькоды 18 и 19. Предложенный триггер может быть изготовлен по планарной или тонкопленоч- ной технологии. При этом он наиболее перспективен для применения в сверхбольших цифровых БИС с минимальными геометрическими размерами вентилей, где особенно важно уменьшить величину энергии потребления. 1 табл.1 ил. (Л W со о -vj OQ 1C

| Будинский Я | |||

| Транзисторные переключающие схемы | |||

| М.: Связь, 1965, с.314, рис.226 | |||

| Авторское свидетельство СССР № 1187244, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-01-30—Публикация

1986-08-11—Подача