tinum логически злементой

(Due.f

Изобретение относится к электротехнике, конкретно к источникам вторичного электропитания с импульсным регулированием для радиоэлектронных средств.

Наиболее предпочтительная область использования - устройства вычислительной техники и аппаратура, работающие от батареи (аккумулятора) при предъявлении к ним повышенных требований в отношении массо-габаритных характеристик и КПД.

Известен стабилизатор постоянного напряжения, работающий в режиме широтно- импульсной модуляции, содержащий регулирующий транзистор, DLC-фильтр и схему управления, основу которой составляет микросхема К142ЕП1 (см., например, Справочник Микросхемы для бытовой аппаратуры, М.: Радио и связь, 1989, с.50). Эта микросхема содержит дифференциальный усилитель, формирователь пилообразного напряжения, работающий с внешней емкостью от внешнего генератора прямоугольного напряжения, широтно-импульс- ный модулятор, согласующие транзисторы и источник опорного напряжения. Выход ширртно-импульсного модулятора связан с общей базой первого согласующего транзистора, эмиттер второго согласующего транзистора подключен к общему проводу схемы, а коллекторы обоих согласующих транзисторов через промежуточный транзистор связан с базой регулирующего транзистора. Дифференциальный усилитель сравнивает выходное напряжение с опорным, а широтно-импульсный модулятор выдает импульсы, скважность которых пропорциональна разности между входным и выходным напряжением стабилизатора при определенном токе нагрузки.

Недостатком стабилизатора является то, что он способен работать лишь при входных напряжениях 10...40 В. Тем не менее в технике электропитания радиоэлектронной аппаратуры часто возникает потребность в получении сравнительно низких напряжений (наиболее часто 5 В) при уровнях входного напряжения, максимально близко приближающихся к требуемым выходным. К недостаткам микросхемы К142ЕП1 относятся также большое количество внешних навесных элементов и необходимость подключения к ней внешнего источника напряжения модуляции, к тому же изолированного.

Наиболее близок к предлагаемому источник вторичного электропитания для сети постоянного напряжения, содержащий генератор, компаратор, первый логический элемент 2И, входы которого подключены к выходам генератора и компаратора, RS- триггер, вход S которого соединен с выходом первого логического элемента 2И, первый транзистор n-p-n-типа, база которого подключена к выходу RS-триггера, второй транзистор n-p-n-типа, базой соединенный

с эмиттером первого транзистора, рези- стивный делитель, включенный между выходным выводом и общей шиной, а выходом подключенный к инвертирующему входу компаратора, неинвертирующий вход которого соединен с выходом источника опорного напряжения, DLC-фильтр, конденсатбр которого включен между выходным выводом и общей шиной, и входной вывод - универсальная подсистема для построения

импульсных источников питания фирмы Fairchild (микросхема ju. A76S40): см. книгу Л.Фолкенберри Применение операционных усилителей и линейных ИС, М.: Мир, 1985, § 10.3.3 на с.311.,.320. У микросхемы

/г A78S40 появился отечественный аналог КР1156ЕУ1.

В понижающем стабилизаторе постоянного напряжения, с.315 книги Л.Фолкенберри, рис.10.17а, коллекторы обоих

выходных транзисторов соединены меж|цу собой и подключены вместе с выводом питания микросхемы к входу, а между эмиттером второго выходного транзистора и выходом устройства включен дроссель, который вместе с конденсатором и внутрйн- ним диодом микросхемы образует DLC-фильтр. В схеме управления выход Ы- нератора и инверсный вход R RS-триггера соединены между собой.

Недостаток микросхем /гА78540 (КР1156ЕУ1) заключается в том, что стабилизация срывается при понижении напряжения первичной сети до величины Unp, равной сумме выходного напряжения и остаточного напряжения, которое может достигать 2,8 В. Столь значительная величина остаточного напряжения объясняется, во- первых, включением выходных транзисторов по схеме Дарлингтона, что было

вызвано необходимостью сопряжения управляющего входа силового ключа с триггером, а во-вторых, наличием естественной паузы модулятора, а значит и ключа, ; Целью изобретения является снижение

нижнего предела входного напряжения (при котором сохраняется стабилизация выходного напряжения).

Поставленная цель достигается тем, в источнике вторичного электропитания Для

сети постоянного напряжения, содержащем генератор, компаратор, первый логический элемент 2И, входы которого подключен4 к выходам генератора и компаратора, RS- триггер, вход S которого соединен с выходом первого логического элемента 2И, первый транзистор n-p-n-типа, база которого подключена к выходу RS-триггера, второй транзистор n-p-n-типа, базой соединенный с эмиттером первого транзистора, рези- стивный делитель, включенный между выходным выводом и общей шиной, а выходом подключенный к инвертирующему входу компаратора, неинвертирующий вход которого соединен с выходом источника опорно- го напряжения, DLC-фильтр, конденсатор которого включен между выходным выводом и общей шиной, и входной вывод, введены третий и четвертый транзисторы p-n-p-типа и пятый транзистор п-р-п-типа, первый, второй, третий и четвертый резисторы, диод, второй и третий логические элементы 2И, первая и вторая интегрирующие RC-цепи, логический элемент 2ИЛИ, инвертор, первый и второй D-триггеры и логический узел, причем эмиттеры третьего и четвертого транзисторов соединены с входным выводом, коллектор третьего транзистора подключен к входу DLC-фильтра, база третьего транзистора подключена кто- козадающей цепи и к коллектору четвертого транзистора, между точкой соединения эмиттеров третьего и четвертого транзисторов и коллектором пятого транзистора включены последовательно соединенные первый и второй резисторы, общая точка которых соединена с базой четвертого транзистора, эмиттер второго транзистора подключен к общей шине, к которой через диод подключен и эмиттер пятого транзистора, база которого соединена с коллектором первого транзистора и через третий резистор - с выводом для подключения источника вспомогательного питания, первая интегрирующая RC-цепь входом подключе- на к выходу генератора, а выходом - к первому входу логического элемента 2 ИЛ И, второй вход которого соединен с выходом компаратора, второй логический элемент 2И входами подключен к выходам генератора и логического элемента 2ИЛИ, а выходом - к инверсному входу R RS-триггера, коллектор второго транзистора подключен к одному из входов третьего логического элемента 2И, через последовательно соеди- ненные инвертор и вторую интегрирующую RC-цепь - к его другому входу, а через четвертый резистор - к выводу для подключения источника питания логических элементов, выход третьего логического эле- мента 2И подключен к счетному входу первого D-триггера, выход инвертора - к счетному входу второго D-триггера, информационные входы первого и второго D-триггеров подключены соответственно к

инверсному выходу второго D-триггера и к прямому выходу первого D-триггера, первый и второй входы логического узла подключены соответственно к прямым выходам обоих D-триггеров, третий и четвертый входы - к их инверсным выходам, а первый и второй выходы - соответственно к в ыходу резистивного делителя и к базе пятого транзистора, при этом логический узел, обеспечивающий на первом и втором выходах следующую логическую функцию:

TX-I yi) (ха yi),

где XL yi, X2, уа - сигналы соответственно на первом, втором, третьем и четвертом входах,

выполнен на четырех логических элементах совпадения, причем входы первого и второго логических элементов совпадения использованы в качестве соответственно первого, второго,третьего и четвертого входов логического узла, в качестве первого и второго выходов которого использованы выходы третьего и четвертого логических элементов совпадения с открытыми коллекторами. Кроме того, в источник введен преобразователь постоянного напряжения в переменное, содержащий первый и второй буферные элементы с инверсией и открытыми коллекторами, шестой и седьмой транзисторы, пятый и шестой резисторы, трансформатор, первичная обмотка которого выполнена с отводом от средней точки, подключенным к выводу для подключения источника питания преобразователя, а вторичные обмотки использованы в качестве дополнительных выходов, при этом входы первого и второго буферных элементов подключены соответственно к выходам первого и второго логических элементов совпадения, а выходы буферных элементов соединены с базами шестого и седьмого транзисторов, подключенных соответственно через пятый и шестой резисторы к выводу для подключения источника питания логических элементов, коллекторы шестого, седьмого транзисторов соединены с крайними выводами первичной обмотки трансформатора, а эмиттеры - с общей шиной.

Сущность изобретения заключается в том, что управление состоянием внешнего регулирующего транзистора, эмиттером подключенным к входному выводу положительной полярности, осуществляется через промежуточный транзистор от коллектора выходного транзистора схемы управления, базой подключенного к RS-триггеру этой схемы и в том, что база промежуточного транзистора, к которой кроме указанного

выходного транзистора схемы управления подключена токозадающая цепь, как и выход резистивного делителя, шунтируются логическими элементами с открытыми коллекторами на время естественной паузы схемы управления, что позволяет избавиться от этой паузы в работе регулирующего транзистора. Определение границ этой паузы, на время которой регулирующий транзистор включается принудительно, ведется путем исследования состояния второго транзистора схемы управления посредством логической части, включающей в себя указанные логические элементы, два D- триггера, схему для формирования импульсов для их счетных входов и два логических элемента совпадения, обрабатывающих сигналы D-триггеров и управляющих логическими элементами с открытыми коллекторами.

Выявление границы регулируемой паузы осуществляется введенными в схему управления интегрирующей цепью и логическими элементами (2ИЛИ и вторым 2И) и основано на возврате RS-триггера этой схемы в положение, соответствующее закрытому состоянию транзисторов, подключенных к триггеру, после выявления естественной паузы.

На фиг. 1 представлена схема источника вторичного электропитания; на фиг. 2 - ее развитие для получения нескольких дополнительных выходов; на фиг. 3 даны эпюры в характерных точках схемы.

Источник вторичного электропитания для сети постоянного напряжения состоит из генератора 1, компаратора 2, источника опорного напряжения 3, первого 4, второго 5 и третьего 6 логических элементов 2И, логического элемента 2ИЛИ 7, RS-триггера 8 с инверсным входом первого D-триггера 9, второго D-триггера 10, инвертора 11, первого 14 и второго 15 транзисторов типа проводимости n-p-п, третьего 16 и четвертого 17 транзисторов, имеющих тип проводимости p-n-р, пятого транзистора 18 типа n-p-п, из диода 19, первого 20, второго 21, третьего 22 и четвертого 23 резисторов, резистивного делителя 24, LCD-фильтра 25 и из логиче- ского узла 26 с четырьмя входами, выполненного на первом 27, втором 28, третьем 29 и четвертом 30 логических элементах совпадения в виде логических элементов 2И-НЕ, причем элементы 29, 30 использованы с открытым коллектором.

Между входом источника вторичного электропитания и его выходом включены последовательно соединенные транзистор 16 и DLC-фильтр 25, причем эмиттер упомянутого транзистора подключен ко входному

выводу положительной полярности. Чбрез резистивный делитель 24 выход источника соединен с инвертирующим входом койпа- ратора 2, неинвертирующий вход которого

соединен с выходом источника опорного напряжения 3. Входы первого элемента 2И 4 подключены к выходам генератора 1 и компаратора 2. Выход компаратора 2 подключен также к первому входу логического

0 элемента 2ИЛИ 7, а выход генератора 1 подключен к первому входу второго логического элемента 2Й 5 и через интегрирующую цепь 12 ко второму входу логического элемфнта 2ИЛИ 7, при этом выходы первого 4 и вто5 рого 5 логических элементов 2И подключены ко входам S и R RS-триггера 8, Выход триггера 8 подключен к базе транзистора 14, эмиттер которого соединен с базой транзистора 15. Эмиттер транзистора 15 гюд0 ключей к общему проводу схемы устройства (в том числе схемы управления). Коллектор транзистора 14 соединен с базой транзистора 18, а через резистор 22 - одновременно с цепью питания схемы управления. К обще5 му проводу схемы через диод 19 подключен эмиттер транзистора 18. Между входным выводом положительной полярности, К которому подключен и эмиттер транзистора 17, и коллектором транзистора 18 включены

0 последовательно соединенные резисторы 20, 21, общая точка которых подключена к базе транзистора 17. Коллектор транзистора 15 подключен к одному из входов логического элемента 2И 6, через последовательно

5 соединенные инвертор 11 и интегрирующую RC-цепь 13 ко второму входу логич ско- го элемента 2И 6, а через резистор 23| - к цепи питания логических элементов. В ыхо- ды логического элемента 2И 6 и инвертора

0 11 подключены соответственно к счетным входам первого 9 и второго 10 D-триггйров, D-входы первого и второго 0-триггеров;под- ключены соответственно к выходу Q втфого D-триггера и к выходу Q первого D-триггера,

5 Выходы Q D-триггера 9 и D-триггера подключены соответственно к первому и второ; му входам логического узла 26, а выхсфы Q этих триггеров - соответственно к третьему и четвертому входам узла 26. Первый и вто0 рой выход этого узла подключены соответственно к выходу резистивного делителя 24 и к базе транзистора 18, Первый и второй выходы логического узла 26 являются вводами логического элемента 2И-НЕ 27, а тр)етий

5 и четвертый входы этого узла - входами логического элемента 2И-НЕ 28. Выхо}ц логического элемента 27 подключен к первым входам логических элементов 29,30, а вЫход логического элемента 28 подключен кс| вторым входам логических элементов 29, 30.

Выходы этих логических элементов являются первым и вторым выходами логического узла.

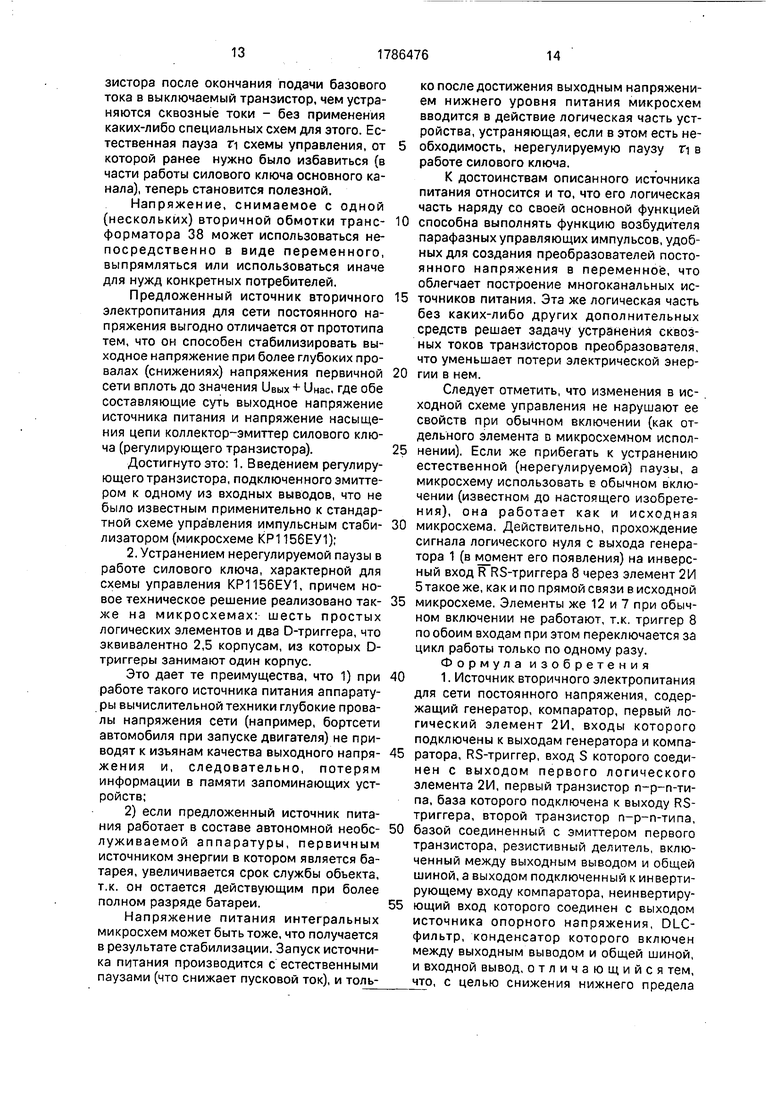

В источнике вторичного электропитания, снабженном одним или несколькими дополнительными каналами выходного напряжения (фиг. 2) имеется также преобразователь 31 постоянного напряжения в переменное, включающий в себя буферные элементы 32, 33 с инверсией и открытыми коллекторами, шестой 34 и седьмой 35 транзисторы, пятый и шестой резисторы 36,37 и трансформатор 38 с первичной обмоткой 39 и вторичной 40, причем таковых может быть по числу требуемых дополнительных каналов. Входы буферных усилителей подключены к выходам первого 27 и второго 28 логических элементов совпадения, а выходы - к базам транзисторов 34, 35, подключенных кроме того через резисторы 36, 37 к цепи питания логических элементов. Коллекторы транзисторов 34, 35 подключены к крайним выводам первичной обмотки 39 трансформатора 38, а средняя точка этой обмотки и эмиттеры транзисторов 34, 35 подключены соответственно к цепи питания преобразователя и к общему проводу схемы источника.

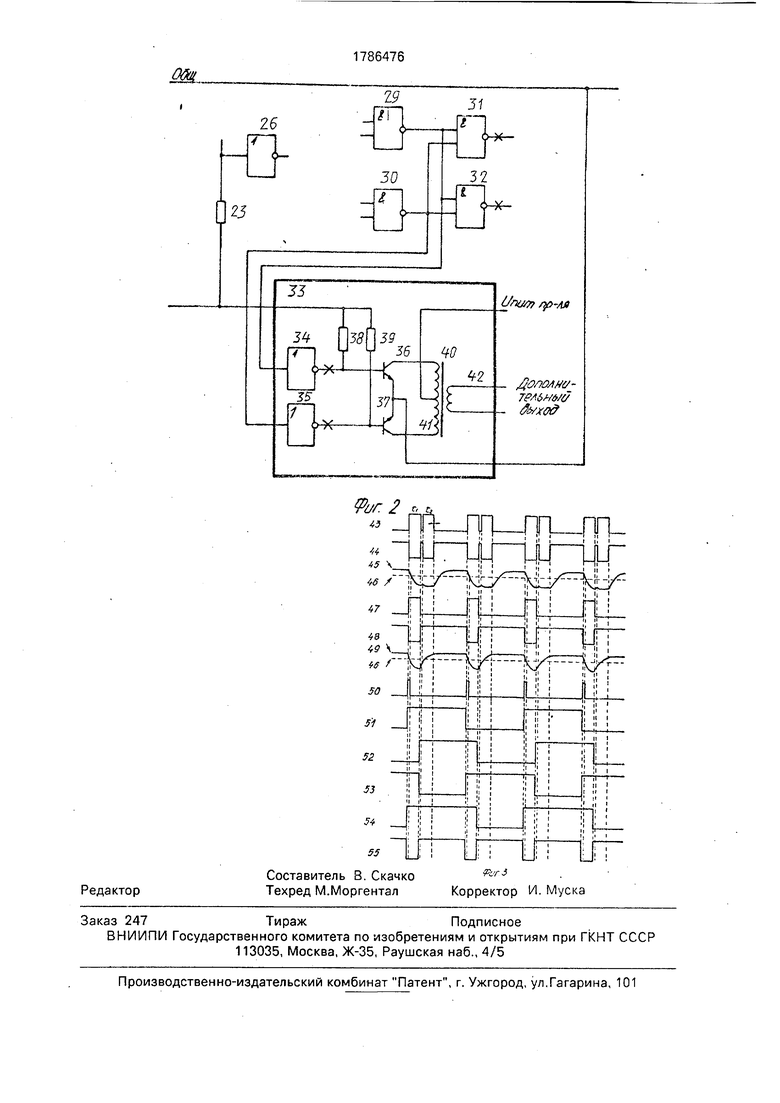

Эпюры на фиг. 3 показывают напряжения:

41 - на коллекторе транзистора 15 (временные интервалы TI и Т2 являют собой естественную и регулируемую паузы схемы управления);

42 - на выходе инвертора 11;

43 - на выходе интегрирующей НС-цепи 13 (на эпюру 43 наложен уровень 44 логической единицы логического элемента 6); 45-47 - видоизменение эпюр 41-43 при предельно пониженном входном напряжении, когда регулируемая пауза исчезает (г2 0);

48 - на выходе логического элемента 2И 6;

49 - на выходе Q первого D-триггера 9;

50 - на выходе Q второго D-триггера 10;

51 - на выходе первого логического элемента совпадения 27;

52 - на выходе второго логического элемента совпадения 28;

53 - выделенный временной интервал п , во время которого производится шунтирование выхода делителя 24 и базы транзистора 18.

Ниже приводится описание работы источника вторичного электропитания для сети постоянного напряжения.

Транзисторы 14, 15 открываются с частотой генератора 1 на время, которое может изменяться от как угодно малого значения

до величины, большей чем время закрытого состояния транзистора примерно в 8 раз. Соотношение времени открытого и закрытого состояния (широтно-импульсная модуляция) зависит от разности между входным и выходным напряжениями, а также от величины тока нагрузки, причем ко времени закрытого состояния добавляется еще постоянно присутствующая естественная

пауза на время релаксации генератора 1.

Чтобы достичь цель изобретения несмотря на указанную особенность схемы уп- равления, нужно обеспечить открытое

состояние силового ключа (регулирующего транзистора 16) во время естественной паузы, т.е. реализовать такой алгоритм управления силовым ключом, чтобы он работал в той же фазе, что и транзисторы 14, 15, только на этапах формирования регулируемой паузы. На этапе же прохождения нерегулируемой (естественной) паузы фазы работы транзисторов 14, 15 и силового ключа должны быть противоположными. Однако сделать это известными средствами нельзя, так как естественная и регулируемая паузы сливаются, и граница между ними неразличима. В настоящем изобретении эта задача решается следующим образом.

Сигнал с коллектора транзистора 14 используется для управления силовым ключом, а сигнал с коллектора транзистора 15 - для управления D-триггерами 9, 10. Во время открытого состояния транзистора 14

транзисторы 18 и 17 закрыты. Следовательно, будет открыт транзистор 16. И наоборот, в закрытом состоянии транзистора 14 надлежит быть открытым транзистору 18 (ток его базы проходит через резистор 22), его

коллекторный ток составит ток базы транзистора 17 и последний станет шунтировать база-эмиттер транзистора 16, который закрывается. По цепи обратной связи через резистивный делитель 24 выходное

напряжение поступает на компаратор 2,

где сравнивается с опорным. Компаратор

2 совместно со схемой 2И 4 и триггером 8

формируют управляющий широтно-модулированный сигнал для транзисторов 14 и 15.

Дальнейшее взаимодействие транзисторов 14,18, 17 и 16 образуют обычную цепь автоматического регулирования, характеризующуюся синфазным состоянием транзистора 14 и транзистора 16. Излом фазы регулирования (обеспечение противоположных состояний транзисторов 14 и 16) достигается воздействием на базу транзистора 18 со стороны открытого коллекторного второго выхода логического узла 26.

Во время возникновения паузы (которая начинается с нерегулируемой ее части) появляется положительный перепад напряжения на указанном втором выходе схемы управления (резистор 23 выступает коллекторной нагрузкой транзистора 14) - см. эпюру 41 на фиг. 3. Импульс, представленный на этой эпюре, создается всей логической частью заявленного устройства в том числе введенными элементами, однако начальная часть - положительный перепад и примыкающая к нему плоская вершина обусловлены только релаксацией генератора. Из этой части вырезается импульс 48 для синхронизации первого D-триггера 9. Происходят та кие процессы: импульс 41 инвертируется (инвертор 11), интегрируется RC-цепью 13, а затем над полученным после этой цепи напряжением 43 и иеходным импульсом 41 выполняется операция конъюнкции (элемент 2И 6). Регулирующий импульс 48 имеет один и тот же вид независимо от того, будет ли регулируемая пауза в работе транзистора 15 схемы управления после естественной (номинальной) паузы, или ее не будет (тг 0). Под воздействием синхронизирующего импульса 48 D-триггер 9 перейдет в состояние, противоположное состоянию второго D- триггера 10 (сравните эпюры 49, 50). От первого же положительного перепада внутри импульса 42 (при Г2 О этот перепад за время между импульсами 48 единственный) D-триггер 10 примет то же состояние, в котором уже находится первый D-триггер (эпюра 50). Процесс переключения обоих D-триггеров будет непрерывным и характеризоваться постоянным запаздыванием перехода D-тр.иггера 10 в состояние, тождественное состоянию D-триггера 9 на номинальную паузу схемы управления (ri).

Во время устанавливающихся взаимно противоположных состояний D-триггеров 9 и 10 на выходах первой и второй схем совпадения 27 и 28 установятся одинаковые состояния: а именно логические единицы (или логические нули, если первый и второй логические элементы применяются в виде 2И или 2ИЛИ-НЕ). По совпадению логических единиц на выходах первого и второго логических элементов 27, 28 (см. эпюры 51 и 52) станут шунтироваться открытыми коллекторами третьего и четвертого логических элементов напряжение обратной связи и широтно-модулированный сигнал на коллекторе транзистора 14 (на время п). Шунтирование базы транзистора 18 приведет к принудительному открыванию транзистора 16, а шунтирование выхода резистивного делителя 23, что равносильно отключению обратной связи, обусловит переключение

RS-триггера 8 по входу S сразу же по окончании процесса релаксации генератор 1 и формирование минимальной длительности паузы, т.е. в размере лишь ri и таким образом скажется выделенной ее естественная длина (эпюра 53). В момент окончания первой половины импульса 41 на коллекторе транзистора 15 возникает положительный перепад на выходе инвертора 11, которым

0 переключается второй D-триггер 10. Сигналы на выходах логических элементов 27, 28 становятся взаимно инверсными, и шунтирование логическими элементами 29, 30 выходов делителя 23 и базы транзистору 18

5 прекратится. Если пауза в работе силового ключа должна быть больше, чем естественная пауза т схемы управления, то на выходе компаратора напряжение примет вид логического нуля, а поскольку напряжение

0 на выходе интегрирующей цепи 12 ещё не стало логической единицей (после появления логической единицы на выходе генератора 1), будет получен импульс логического нуля на выходе элемента 2ИЛИ 7 и, т.к.

5 появление логического нуля на любом входе второго логического элемента 2И 5 вызывает логический нуль на его выходе, триггер 8 снова переключится по входу R и начнётся вторая половина импульса 41 (регулируемая

0 пауза). Силовой ключ (транзистор 16) с э|ого момента будет управляться по обычной цепи обратной связи.

В многоканальном варианте исполнения источника с дополнительным преобра5 зователем 31 постоянного напряжения в переменное (фиг. 2) на входы буферных Јле- ментов 32, 33 этого преобразователя поступают напряжения 51, 52 (см. фиг. 3), вырабатываемые первым 27 и вторым 28

0 логическими элементами совпадения. Во время овпадения логических единиц на выходах Q триггеров 9, 10 закрывается выводной транзистор буферного элемента 3;2 и откроется транзистор 34, базовый ток кбто5 рого будет протекать через резистор 3$. В буферном элементе 33 выходной транзистор в это время будет открытым, и он будет шунтировать переход база-эмиттер транзистора 35. Затем при совпадении логи чес|ких

0 единиц на инверсный выходах Q триггеров 9, 10 откроется транзистор 35 и т.д., в обычных двухтактных преобразователях. Вся предшествующая схема основной чфти устройства представляеттаким образом для

5 преобразователя 31 источник парафазйого сигнала, а возбудителем колебаний выступает генератор 1.

Примечательно, что естественная пауза П этой схемы в преобразователе 31 явится задержкой включения очередного его транзистора после окончания подачи базового тока в выключаемый транзистор, чем устраняются сквозные токи - без применения каких-либо специальных схем для этого. Естественная пауза ri схемы управления, от которой ранее нужно было избавиться (в части работы силового ключа основного канала), теперь становится полезной.

Напряжение, снимаемое с одной (нескольких) вторичной обмотки трансформатора 38 может использоваться непосредственно в виде переменного, выпрямляться или использоваться иначе для нужд конкретных потребителей.

Предложенный источник вторичного электропитания для сети постоянного напряжения выгодно отличается от прототипа тем, что он способен стабилизировать выходное напряжение при более глубоких провалах (снижениях) напряжения первичной сети вплоть до значения 1)вых + Унас, где обе составляющие суть выходное напряжение источника питания и напряжение насыщения цепи коллектор-эмиттер силового ключа (регулирующего транзистора).

Достигнуто это: 1. Введением регулирующего транзистора, подключенного эмиттером к одному из входных выводов, что не было известным применительно к стандартной схеме управления импульсным стабилизатором (микросхеме КР1156ЕУ1);

2. Устранением нерегулируемой паузы в работе силового ключа, характерной для схемы управления КР1156ЕУ1, причем новое техническое решение реализовано также на микросхемах: шесть простых логических элементов и два D-триггера, что эквивалентно 2,5 корпусам, из которых D- триггеры занимают один корпус.

Это дает те преимущества, что 1) при работе такого источника питания аппаратуры вычислительной техники глубокие провалы напряжения сети (например, бортсети автомобиля при запуске двигателя) не приводят к изъянам качества выходного напряжения и, следовательно, потерям информации в памяти запоминающих устройств;

2) если предложенный источник питания работает в составе автономной необслуживаемой аппаратуры, первичным источником энергии в котором является батарея, увеличивается срок службы объекта, т.к. он остается действующим при более полном разряде батареи.

Напряжение питания интегральных микросхем может быть тоже, что получается в результате стабилизации. Запуск источника питания производится с естественными паузами (что снижает пусковой ток), и только после достижения выходным напряжением нижнего уровня питания микросхем вводится в действие логическая часть устройства, устраняющая, если в этом есть необходимость, нерегулируемую паузу Г в работе силового ключа.

К достоинствам описанного источника питания относится и то, что его логическая часть наряду со своей основной функцией

0 способна выполнять функцию возбудителя парафазных управляющих импульсов, удобных для создания преобразователей постоянного напряжения в переменное, что облегчает построение многоканальных ис5 точников питания. Эта же логическая часть без каких-либо других дополнительных средств решает задачу устранения сквозных токов транзисторов преобразователя, что уменьшает потери электрической энер0 гии в нем.

Следует отметить, что изменения в ис- . ходной схеме управления не нарушают ее свойств при обычном включении (как отдельного элемента в микросхемном испол5 нении), Если же прибегать к устранению естественной (нерегулируемой) паузы, а микросхему использовать в обычном включении (известном до настоящего изобретения), она работает как и исходная

0 микросхема. Действительно, прохождение сигнала логического нуля с выхода генератора 1 (в момент его появления) на инверсный вход R RS-триггера 8 через элемент 2И 5 такое же, как и по прямой связи в исходной

5 микросхеме. Элементы же 12 и 7 при обычном включении не работают, т.к. триггер 8 по обоим входам при этом переключается за цикл работы только по одному разу. Формула изобретения

0 1. Источник вторичного электропитания для сети постоянного напряжения, содержащий генератор, компаратор, первый логический элемент 2И, входы которого подключены к выходам генератора и компа5 ратора, RS-триггер, вход S которого соединен с выходом первого логического элемента 2И, первый транзистор п-р-п-ти- па, база которого подключена к выходу RS- триггера, второй транзистор п-р-п-типа,

0 базой соединенный с эмиттером первого транзистора, резистивный делитель, включенный между выходным выводом и общей шиной, а выходом подключенный к инвертирующему входу компаратора, неинвертиру5 ющий вход которого соединен с выходом источника опорного напряжения, DLC- фильтр, конденсатор которого включен между выходным выводом и общей шиной, и входной вывод, отличающийся тем, что, с целью снижения нижнего предела

входного напряжения, в него введены третий и четвертый транзисторы р-п-р-ти- па и пятый транзистор п-р-п-типа, первый, второй, третий и четвертый резисторы, диод, второй и третий логические элементы 2И, первая и вторая интегрирующие RC-цепи, логический элемент 2ЙЛИ, инвертор, первый и второй D-триггеры и логический узел, причем эмиттеры третьего и четвертого транзисторов соединены с входным выводом, коллектор третьего транзистора подключен к входу DLC-фильтра, база третьего транзистора подключена кто- козадающей цепи и к коллектору четвертого транзистора, между точкой соединения эмиттеров третьего и четверто го транзисторов и коллектором пятого транзистора включены последовательно соединенные первый и второй резисторы, общая точка которых соединена с базой четвертого транзистора, эмиттер второго транзистора подключен к общей шине, к которой через диод подключен и эмиттер пятого транзистора, база которого соединена с коллектором первого транзистора и. через третий резистор - с выводом для подключения источника вспомогательного питания, первая интегрирующая RC-цепь входом подключена к выходу генератора, а выходом - к первому входу логического элемента 2ИЛИ, второй вход которого соединен с выходом компаратора, второй логический элемент 2И входами подключен к выходам генератора и логического элемента 2ИЛ И, а выходом

- к инверсному входу RRS-триггера, коллектор второго транзистора подключен к одному из входов третьего логического элемента 2И, через последовательно соединенные инвертор и вторую интегрирующую RC-цепь

- к его другому входу, а через четвертый резистор- к выводу для подключения источника питания логических элементов, выход третьего логического элемента 2И подключен к счетному входу первого D-триггера, а выход инвертора - к счетному входу второго D-триггера, информационные входы первого и второго D-триггеров подключены соответственно к инверсному выходу второго D-триггера и к прямому выходу первого D- триггера, первый и второй входы логического узла подключены соответственно к прямым выходам обоих D-триггеров, третий и четвертый входы - к их инверсным выходам, а первый и второй выходы - соответственно к выходу резистивного делителя и к безе пятого транзисторов, при этом логический узел, обеспечивающий на первом и втором выходах следующую логическую функцию:

(ХГ yi) (Х2 У2),

где xi, yi, X2, У2 - сигналы соответственно;на первом, втором, третьем и четвертом входах, выполнен на четырех логических элемен|ах совпадения, причем входы первого и второго логических элементов совпадения использованы в качестве соответственно первого, второго, третьего и четвертого вХо- дов логического узла, в качестве первого и второго выходов которого использованы выходы третьего и четвертого логических элементов совпадения с открытыми коллекторами.

2, Источник поп. 1,отличающи и с я

тем, что, с целью получения по меньщей мере одного дополнительного выхода, в него введен преобразователь постоянного напряжения в переменное, содержащий первый и второй буферные элементы с йнверсией и открытыми коллекторами, шестой и седьмой транзисторы, пятый и шестой резисторы, трансформатор, первичная обмотка которого выполнена с отводом от средней точки, подключенным к выводу Для

подключения источника питания преобразователя, а вторичные обмотки использованы в качестве дополнительных выходов, при этом входы первого и второго буферных элементов подключены соответственно к выходам первого и второго логических элементов совпадения, а выходы буферйых элементов соединены с базами шестогЬ и седьмого транзисторов, подключенных соответственно через пятый и шестой р зисторы к выводу для подключения источника питания логических элементов, коллекторы шестого, седьмого транзисторов соединены с крайними выводами первичной ки трансформатора, а эмиттеры - с общей

шиной.

| название | год | авторы | номер документа |

|---|---|---|---|

| Импульсный понижающий стабилизатор постоянного напряжения | 1990 |

|

SU1786477A1 |

| ИМПУЛЬСНЫЙ СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ ПОНИЖАЮЩЕГО ТИПА | 1991 |

|

RU2006062C1 |

| ДВУХТАКТНЫЙ ТРАНЗИСТОРНЫЙ ИНВЕРТОР | 1993 |

|

RU2046527C1 |

| Многофазный импульсный стабилизатор напряжения | 1986 |

|

SU1408425A1 |

| Транзисторный инвертор | 1991 |

|

SU1815775A1 |

| СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ С ИМПУЛЬСНЫМ РЕГУЛИРОВАНИЕМ | 1991 |

|

RU2014646C1 |

| Переносной шахтный сигнализатор метана | 1990 |

|

SU1800064A1 |

| УСТРОЙСТВО ДЛЯ БЕСКОНТАКТНОГО ИЗМЕРЕНИЯ ИМПУЛЬСНЫХ ТОКОВ | 1990 |

|

RU2024025C1 |

| Транзисторный инвертор | 1990 |

|

SU1757069A1 |

| БЕСКОНТАКТНЫЙ ЭЛЕКТРОДВИГАТЕЛЬ ПОСТОЯННОГО ТОКА | 2009 |

|

RU2408127C1 |

Использование: в источниках вторичного электропитания с импульсным регулированием для радиоэлектронных средств. Сущность изобретения: устройство содержит генератор 1, компаратор 2, источник опорного напряжения 3, логические элементы 2И 4-6, логический элемент 2 ИЛИ 7, RC-триггер 8, два D-триггера 9,10, инвертор 11, две интегрирующих цепи 12, 13, транзисторы 14-18, диод 19, резисторы 20-23, ре- зистивный делитель 24, LCD-фильтр 25, логический узел 26, выполненный на логических элементах совпадения. Устройство способно стабилизировать выходное напряжение при глубоких провалах напряжения первичной сети. 1 з.п. ф-лы, 3 ил,

| Микросхемы для бытовой аппаратуры | |||

| Справочник, М,: Радио и связь, 1989, с.50 | |||

| Фолкенберри Л | |||

| Применение операционных усилителей и линейных интегральных схем, М,: Мир, 1985, с.315, рис.10.17а. |

Авторы

Даты

1993-01-07—Публикация

1990-11-20—Подача