(Л

со о

00

Изобретение относится к импульсной технике и может быть использовано в качестве коммутатора аналоговых сигналов, в частности при построении устройств выборки и запоминания, пш- роко используемых в линейных системах.

Цель изобретения - повышение точности коммутации.

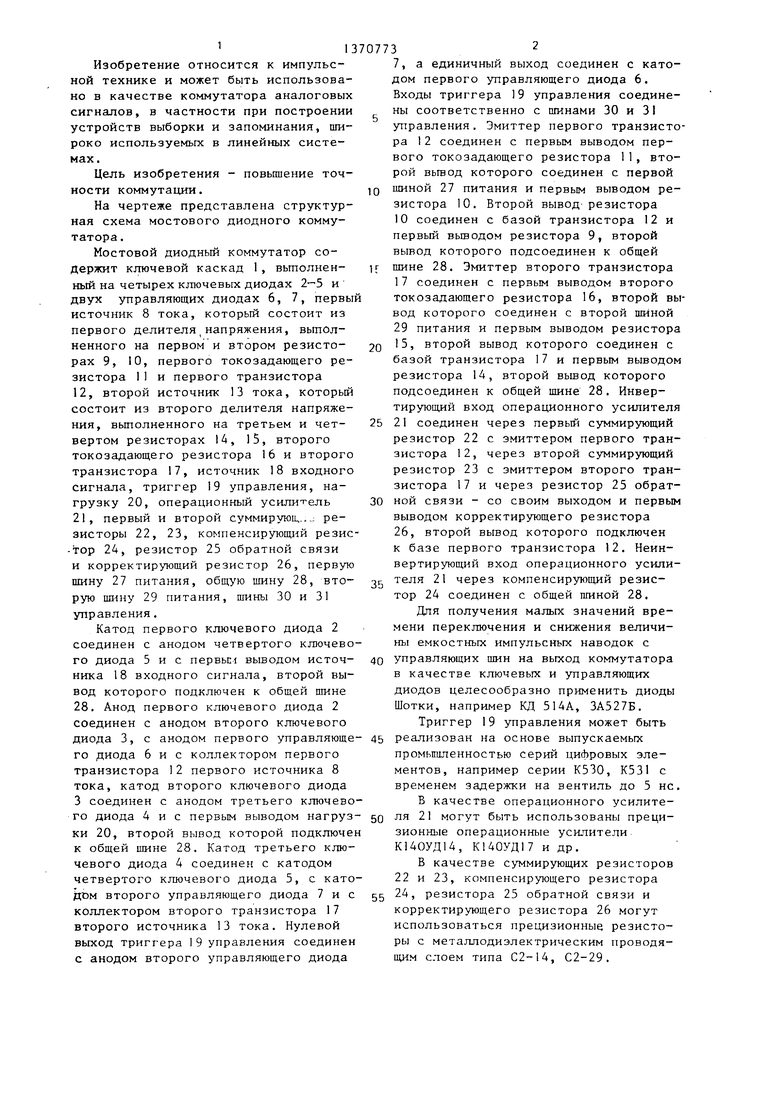

На чертеже представлена структурная схема мостового диодного коммутатора .

Мостовой диодный коммутатор содержит ключевой каскад 1, вьтолнен- ный на четырех ключевых диодах и двух управляющих диодах 6, 7, первы источник 8 тока, которьш состоит из первого делителя напряжения, выполненного на первом и втором резисто- pax 9, 10, первого токозадающего резистора 11 и первого транзистора 12, второй источник 13 тока, который состоит из второго делителя напряжения, выполненного на третьем и чет- вертом резисторах 14, 15, второго токозадающего резистора 16 и второго транзистора 17, источник 18 входного сигнала, триггер 19 управления, нагрузку 20, операционный усилитель 21, первый и второй суммируюи,.,,; резисторы 22, 23, компенсирующий резис -тор 24, резистор 25 обратной связи и корректирующий резистор 26, первую шину 27 питания, общую шину 28, вто- рую шину 29 питания, шины 30 и 31 управления.

Катод первого ключевого диода 2 соединен с анодом четвертого ключевого диода 5 и с первьп выводом источ- ника 18 входного сигнала, второй вывод которого подключен к общей шине 28. Анод первого ключевого диода 2 соединен с анодом второго ключевого диода 3, с анодом первого управляюще го диода бис коллектором первого транзистора 12 первого источника 8 тока, катод второго ключевого диода 3 соединен с анодом третьего ключевого диода 4 и с первым выводом нагруз ки 20, второй вывод которой подключе к общей шине 28. Катод третьего ключевого диода 4 соединен с катодом четвертого ключевого диода 5, с катодом второго управляющего диода 7 и с коллектором второго транзистора 17 второго источника 13 тока. Нулевой выход триггера 1 9 управления соединен с анодом второго управляющего диода

7, а единичный выход соединен с катодом первого управляющего диода 6. Входы триггера 19 управления соединены соответственно с шинами 30 и 3I управления. Эмиттер первого транзистора 12 соединен с первым выводом первого токозадающего резистора 11, второй вьгаод которого соединен с первой шиной 27 питания и первым выводом резистора 10. Второй вывод-резистора 10 соединен с базой транзистора 12 и первый вьшодом резистора 9, второй вывод которого подсоединен к общей шине 28. Эмиттер второго транзистора 17 соединен с первым выводом второго токозадающего резистора 16, второй вывод которого соединен с второй шиной 29 питания и первым выводом резистора 15, второй вывод которого соединен с базой транзистора 17 и первым выводом резистора 14, второй вьшод которого подсоединен к общей шине 28. Инвертирующий вход операционного усилителя

21соединен через первый суммирующий резистор 22 с эмиттером первого транзистора 12, через второй суммирующий резистор 23 с эмиттером второго транзистора 17 и через резистор 25 обратной связи - со своим выходом и первым выводом корректирующего резистора

26, второй вывод которого подключен к базе первого транзистора 12. Неинвертирующий вход операционного усилителя 21 через компенсирующий резистор 24 соединен с общей шиной 28.

Для получения малых значений времени переключения и снижения величины емкостных импульсных наводок с управляющих шин на выход коммутатора в качестве ключевых и управляющих диодов целесообразно применить диоды Шотки, например КД 514А, ЗА527Б.

Триггер 19 управления может быть реализован на основе выпускаемых промышленностью серий цифровых элементов, например серии К530, К531 с временем задержки на вентиль до 5 не

В качестве операционного усилителя 21 могут быть использованы прецизионные операционные усилители К140УД14, К140УД17 и др.

В качестве суммирующих резисторов

22и 23, компенсирующего резистора 24, резистора 25 обратной связи и корректирующего резистора 26 могут использоваться прецизионные резисторы с металлодиэлектрическим проводящим слоем типа С2-14, С2-29.

Принцип работы мостового диодного коммутатора заключается в следующем .

Реэистивные делители, выполненные с на резисторах 9, 10 и 14, 15 создают смещение в базах транзисторов 12 и 17. Через токозадающие резисторы 11 и 16 соответственно создается положительный и отрицательный ток стабили- ю зации. Управл пощие напряжения с нулевого и единичного выходов триггера 19 управления подаются на ключевой каскад в противсфазе через управляющие диоды 6 и 7.15

При положительном управляющем напряжении на катоде диода 6 и отрицательном управляющем напряжении на аноде диода 7 эти диоды заперты, а диоды 2-5 диодной мостовой схемы от- 20 перты, и через оба плеча схемы течет постоянный ток от одного источника тока к другому. Одно плечо диодной мостовой схемы образуют диоды 2 и 5, а другое - диоды 3 и 4. Таким обра- 25 зом, сигнал источника 18 входного сигнала прикладывается к нагрузке 20, При отрицательном управляющем напряжении на катоде диода 6 и положительном управляющем напряжении ЗО на аноде диода 7 эти диоды отперты, а диоды 2-5 диодной мостовой схемы заперты, и источник 18 входного сигнала отключается от нагрузки. ПадеС выхода операционного усилителя 21 сигнал разбаланса, пропорциональный разности токов источников 8 и 13 тока, через корректирующий резистор 26 поступает в базу транзистора 12. Таким образом осуществляется компенсация токов первого и второго источников до их равенства.

Формула изобретения

Мостовой диодный коммутатор, содержащий ключевой каскад, выполненный на четырех ключевых диодах и двух управляющих диодах, первый и второй источники тока, каждый из которых выполнен на делителе напряжения из двух резисторов, токозадающем резисторе и транзисторе, источник входного сигнала, нагрузку, триггер управления, первую и вторую шины питания, общую шину, первую и вторую шины управления, катод первого ключевого диода соединен с анодом четвертого ключевого диода и с первым выводом источника входного сигнала, второй вывод которого подключен к общей пшне, анод первого ключевого диода соединен с анодом второго ключевого диода, с анодом первого управляющего

40

диода и коллектором первого транзистора первого источника тока, катод второго ключевого диода соединен с ния напряжений с первого токозадающе- ,r анодом третьего ключевого диода и с

первым выводом нагрузки, второй вывод которой подключен к общей шине, катод третьего ключевого диода соединен с катодом четвертого ключевого диода, катодом второго управляющего диода и коллектором второго транзистора второго источника тока, первый и второй входы триггера управления соединены соответственно с первой и второй шинами управления, нулевой выход триггера управления соединен с анодом второго управляющего диода, а единичный выход - с катодом первого управляющего диода, первая шина питания через токозадающий резистор

JW

где напряжение на выходе операционного усилителя 21;

го резистора 11 первого источника 8 тока и второго токозадающего резистора 16 второго источника 13 тока через суммирующие резисторы 22 и 23 соответственно подаются на инвертирующий вход операционного усилителя 21, неинвертирующий вход которого через компенсирующий резистор 24 соединен с общей шиной 28. Таким образом, операционный усилитель 2 включен по схеме инвертирующего сумматора. Сигнал разбаланса равен

45

-(U

ОУ 21

) (R55/R

25

) и

22

)U

KM)

50

первого источника тока соединена с эмиттером транзистора первого источника тока, база которого подключена к средней точке делителя напряжения первого источника тока,один из резисторов которого соединен с первой ошной питания, а другой резистор соединен с общей шиной, вторая шина питания через токозадающий резистор

Up - падение напряжений на резисторах 16 и 11 соот- ветственно;

, значения сопротив 22

лений резистора обратной связи и суммирующих резисторов соответственно.

С выхода операционного усилителя 21 сигнал разбаланса, пропорциональный разности токов источников 8 и 13 тока, через корректирующий резистор 26 поступает в базу транзистора 12. Таким образом осуществляется компенсация токов первого и второго источников до их равенства.

Формула изобретения

Мостовой диодный коммутатор, содержащий ключевой каскад, выполненный на четырех ключевых диодах и двух управляющих диодах, первый и второй источники тока, каждый из которых выполнен на делителе напряжения из двух резисторов, токозадающем резисторе и транзисторе, источник входного сигнала, нагрузку, триггер управления, первую и вторую шины питания, общую шину, первую и вторую шины управления, катод первого ключевого диода соединен с анодом четвертого ключевого диода и с первым выводом источника входного сигнала, второй вывод которого подключен к общей пшне, анод первого ключевого диода соединен с анодом второго ключевого диода, с анодом первого управляющего

40

45

первым выводом нагрузки, второй вывод которой подключен к общей шине, катод третьего ключевого диода соединен с катодом четвертого ключевого диода, катодом второго управляющего диода и коллектором второго транзистора второго источника тока, первый и второй входы триггера управления соединены соответственно с первой и второй шинами управления, нулевой выход триггера управления соединен с анодом второго управляющего диода, а единичный выход - с катодом первого управляющего диода, первая шина питания через токозадающий резистор

JW

M)

50

55

первого источника тока соединена с эмиттером транзистора первого источника тока, база которого подключена к средней точке делителя напряжения первого источника тока,один из резисторов которого соединен с первой ошной питания, а другой резистор соединен с общей шиной, вторая шина питания через токозадающий резистор

второго источника тока соединена с эмиттером транзистора второго источника тока, база которого подключена к средней точке делителя напряжения второго источника тока, один из резисторов которого соединен с второй шииой питания, а другой резистор соединен с общей шииой, отличающийся тем, что, с целью повьше- иия точности коммутации, введены операционный усилитель, первый и второй суммирующие резисторы, компенсирую

рующий вход операционного усилителя соединен через первый суммирующий резистор с эмиттером транзистора первого источника тока, через второй суммирующий резистор с эмиттером ; зистора второго источника тока и через резистор обратной связи - со своим выходом и первым вьшодом корректирующего резистора, .второй вывод которого подключен к базе транзистора первого источника тока, неинвер- тирующий вход операционного усилите

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1989 |

|

SU1691895A1 |

| Устройство для пожарной сигнализации | 1990 |

|

SU1836706A3 |

| Операционный усилитель | 1982 |

|

SU1072060A1 |

| Близостный переключатель | 1988 |

|

SU1539855A1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| Трехканальный мажоритарный элемент | 1987 |

|

SU1584101A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ СТЕКЛООМЫВАТЕЛЕМ ТРАНСПОРТНОГО СРЕДСТВА | 1992 |

|

RU2089416C1 |

| Устройство для импульсно-фазового управления трехфазным тиристорным преобразователем | 1987 |

|

SU1631682A1 |

| ПИКОВЫЙ ДЕТЕКТОР | 2009 |

|

RU2409818C1 |

| Умножитель постоянного напряжения | 1982 |

|

SU1072217A1 |

Изобретение относится к импульсной технике. Мостовой диодный коммутатор содержит ключевой каскад 1 на ключевых диодах 2-5 и управляющих диодах 6-7, источник тока (ИТ) 8, включающий резисторы (Р) 9, 10, то- козадающий Р 11 и транзистор 12, ИТ 13, включаю1ций Р 14, 15, токозадающий Р 16 и транзистор 17, источник 18 входного сигнала, триггер 19 управления, нагрузку 20, операционный усилитель 21, суммируюпще Р 22, 23, ком- пенсируклций Р 24, корректирующий Р 26, шины 27, 29 питания, Р 25 обратной связи, общую шину 28, шины 30, 31 управления. Изобретение повьш1ает точность коммутации. 1 ил.

щий резистор, резистор обратной связи ля через компенсирующий резистор и корректирующий резистор, инверти- 15 соединен с общей шиной.

| Титце У., Шенк К | |||

| Полупроводниковая схемотехника | |||

| М.: Мир, 1982, с | |||

| ПАРОВАЯ ИЛИ ГАЗОВАЯ ТУРБИНА | 1914 |

|

SU278A1 |

| ДИОДНЫЙ КОММУТАТОР | 0 |

|

SU240014A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-01-30—Публикация

1986-08-27—Подача