П

00

00

оо

4;:

СО

Изобретение относится к импульс- ;ной технике и может быть использова- НО в системах обработки импульсных сигналов.

Цель изобретения - расширение функциональных возможностей за счет обеспечения возможности преобразования входных серий с изменяющимся периодом следования импульсов от серии к серии.

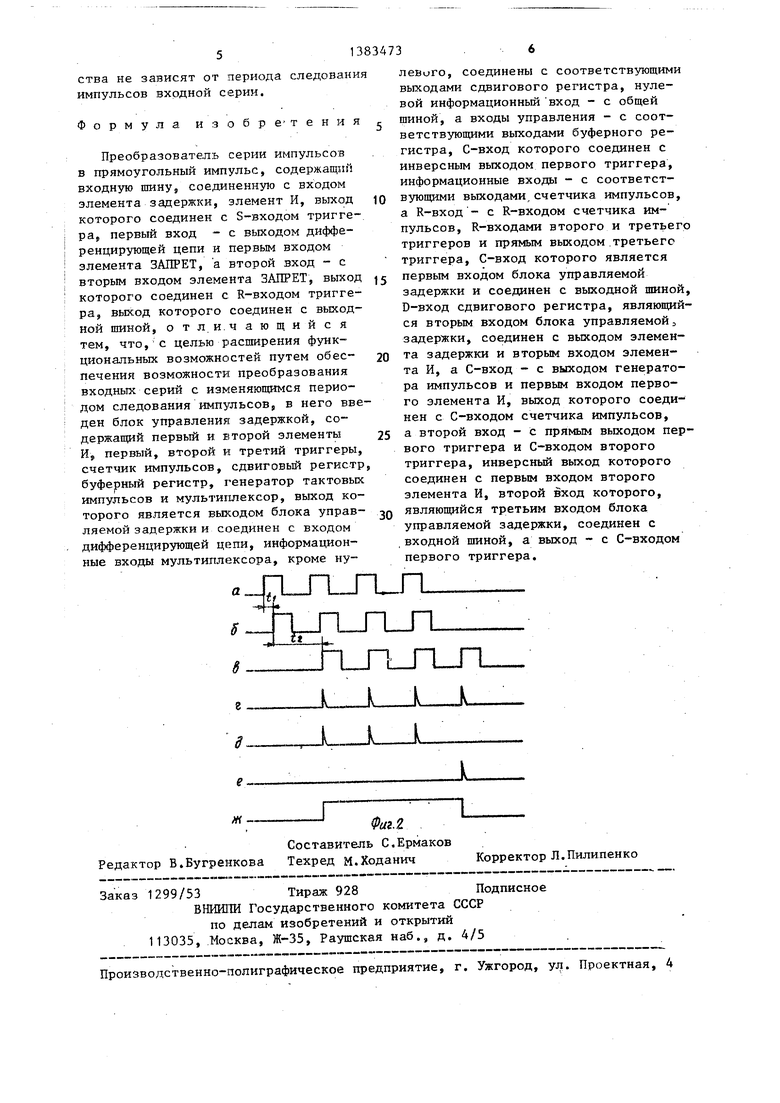

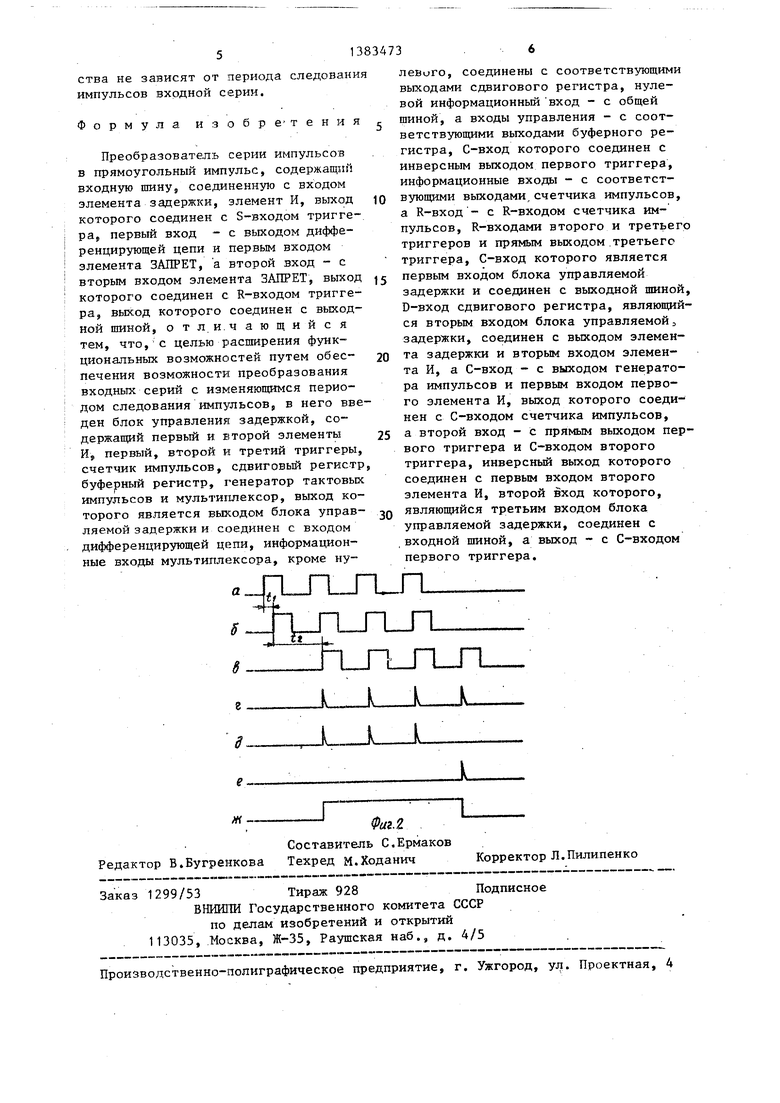

На фиг. 1 представлена электрическая функциональная схема устройства} на фиг. 2 - временные диаграм- |мы, поясняющие его работу.

Преобразователь серии импульсов I в прямоугольный импульс содержит . . Iвходную шину 1, элемент 2 задержки, I дифференцирующую цепь 3, три элемен- Iта И 4-6,четыре триггера 7-10,элемент запрет 11,счетчик 12 импульсов, генератор 13 импульсов, буферный регистр 14, регистр 15 сдвига, мультиплексор 16 и выходную шину 17, причем входная шина 1 соединена с первым входом элемента И 5 и через элемент 2 задержки - с первыми входами элемент 1 ЗАПРЕТ 11 и элемента И 4, второй вход которого соединен с вторьм входом элемента ЗАПРЕТ 11 и выходом дифференцирующей цепи 3, а выход - с :5-входом триггера 7,R -вход которого соединен с выходом элемента ЗАПРЕТ 11, а выход - с выходной шиной 17 и С-входом триггера 10, R-вход кото рого соединен с его же прямым выходом и R-входами счетчика 12, буферного регистра 14 и триггера 9, С-вход которого соединен с прямым выходом триггера 8 и первым входом элемента И 6, а инверсный выход - с вторым входом элемента И 5, выход которого соединен с С-входом триггера 8, инверсный выход которого соединен с С-входом буферного регистра 14, информационные входы которого соединены с соответствующими выходами счетчика 12 импульсов, а выходы - с со- ответств: тощими входш ш управления мультиплексора 16, выход которого соединен с входом дисйеренцирующей цепи 3, нулевой информационный вход соединен с нулевой шиной, а остальные информационные входы - с соответствующими выходами сдвигового регистра 15, С-вход которого соединен с выходом генератора 13 импульсов и вторым входом элемента И 6, выход

которого соединен с С-входом счетчика 12 импульсов.

Элементы И 5 и 6, генератор 13 импульсов, триггеры 8-10, счетчик 12 импульсов, буферный регистр 14, сдвиговый регистр 15 и мультиплексор 16 с соответствующими связями составляют блок управления задержкой.

Q Преобразователь работает следую- шим образом.

В исходном состоянии триггер 7 и блок yпpaвлeн я задержкой находятся в нулевом состоянии. Серия импуль5 сов, поступающая на входную шину 1 устройства (фиг.2а), через время t,, определяемое задержкой в элементе 2 задержки, поступает на вход элемента И 4 и на D-вход регистра 15 сдви0 га блока управления задержкой

(фиг.26). Кроме того, входная серия импульсов поступает на вход элемента И 5 блока управления задержкой. Серия импульсов, поступающая с выхо5 да элемента 2 задержки (фиг.26), задерживается в блоке управления задержкой на время tj и поступает на вход дифференцирующей цепи 3 (фиг.2в) на выходе которой формируются ко0 роткие импульсы, совпадающие по времени с передними фронтами задержанных импульсов серии (фиг.2г).

Время задержки в блоке управления задержкой должно быть таким, чтобы вьшолнялось условие

5

Ти.Ч т, +г, ,

0

t.

5

где Тц - период следования импульсов в серии; и бу - длительность импульсов

серии.

Это условие обеспечивается за v счет того, что блок управления задержкой измеряет интервал времени между первым и вторым импульсами входной серии и сохраняет его значение в цифровом коде до окончания

входной серии импульсов.

I

В этом случае на выход элемента f. И 4 проходят все короткие импульсы серии с выхода дифференцирующей цепи 3, за исключением последнего, соответствующего последнему импульсу в серии (фиг.2д). Первый импульс с t выхода элемента И 4 переключает триггер 7 в единичное состояние (фиг.2ж). Последний импульс с выхода дифференцирующей цепи 3 проходит на выход элемента ЗАПРЕТ 11 (фиг.2е) и, поступая на второй вход триггера 7, сбрасывает последний в нулевое состояние (фиг;2ж).

Работа блока управления задержкой состоит в определении периода следования импульсов входной серии и задержке серии импульсов, поступающей с выхода элемента 2 задержки на вход элемента И 5 блока, на период и про- исходит следующим образом,

R исходном состоянии прямые выходы триггеров 8-10 имеют нулевой логический уровень, счетчик 12 и буферный регистр 14 - обнулены.

Первый импульс входной серии (фиг.2а), поступающий на вход элемента И 5, на другой вход которого поступает единичный логический уровень с инверсного выхода триггера 9, вы- зывает появление единичного логического уровня на выходе элемента И 5 и взводит первый триггер 8, единичный логический уровень с прямого выхода которого разрешает прохождение импульсов с выхода задающего генератора 13 через элемент И 6 на счетный вход счетчика 12 импульсов.

Второй импульс входной серии (фиг.2а) проходит через элемент И 5 и своим фронтом сбрасывает триггер 8 в исходное состояние, тем самым вьщеляя период следования импульсов входной серии. Срез импульса, поступающего с прямого выхода триггера 8 на вход триггера 9, взводит его. Нулевой логический уровень с его инверсного выхода блокирует элемент И 5. Импульсы задающего генератора 13, прошедшие через элемент И 6, за- письгоаются в счетчик 12. Таким образом период серии импульсов преобразо вьгаается в двоичный код, который по фронту импульса с инверсного выхода триггера 8 записывается в буферный регистр 14. Выходы буферного регистра 14 подключены к управляющим входам мультиплексора 16, код на входе которого управляет подключением соответствующего информационного входа мультиплексора 16 к его выходу, который является выходом блока управления задержкой.

На D-вход сдвигового регистра 15 поступает серия импульсов, задержанная по отношению к входной в элемен- те 2 задержки на время t, . Сдвиг импульсов, поступающих на D-вход сдвигового регистра 15, осуществляется

импульсами задающего генератора 13. Когда импульс, сдвигаясь по регистру 15, достигает выхода, подключенного к тому входу мультиплексора 16, который в соответствии с входным управляющим кодом подключен к его выходу, на выходе блока управления задержкой появляется импульс единичного уровня, длительность которого равна длительности импульса, поступающего на входную шину 1 устройства.

Так как работа схемы преобразования периода в двоичный управляющий код и сдвиг входных импульсов в сдвиговом регистре 15 происходят параллельно во время, то должны выполняться условия

0 5

0

5

0

5

0

зг

4,6t, 2Т

Тз. 48+ t,g+ t,,+ t,,,+ t,,,

где ty - время задержки элемента 2

задержки; Tj - период следования импульсов

генератора 13} tjg- время задержки переключения

элемента И 5; время задержки переключения

триггера 8; время задержки переключения

элемента И 6j время задержки переключения

счетчика 12;

время задержки переключения буферного регистра 14, время задержки переключения мультиплексора 16. Таким образом, каждый импульс, поступающий с выхода элемента 2 задержки, оказывается задержанным на период на выходе блока управления задержкой.

Пер ёход блока управления задержкой в исходное состояние происходит по срезу выходного прямоугольного импульса, поступающего с выходной шины 16 устройства на С-вход триггера 10. Триггер 10 взводится и сразу же сбрасывается, так как его прямой выход связан с его R-входом, формируя короткий единичный импульс, который переводит в исходное состояние триггер 9,хсчетчик 12 и буферный регистр 14.

Таким образом, предлагаемое устройство позволяет преобразовывать в прямоугольные импульсы серии импульсов с различным периодом следования импульсов, так как параметры устройства не зависят от периода следовани импульсов входной серии.

Формула из обр 6 тени я

Преобразователь серии импульсов в прямоугольный импульс, содержащий входную шину, соединенную с входом элемента задержки, элемент И, выход которого соединен с S-входом триггера, первый вход - с выходом дифференцирующей цепи и первым входом элемента ЗАПРЕТ, а второй вход - с вторым входом элемента ЗАПРЕТ, выход которого соединен с R-входом триггера, вькод которого соединен с выходной шиной, о тл.и.чающий с я тем, что, С целью расширения функциональных возможностей путем обес- печения возможности преобразования входных серий с изменяющимся периодом следования импульсов, в него введен блок управления задержкой, содержащий первый и: второй элементы И, первый, второй и третий триггеры, счетчик импульсов, сдвиговьй регистр буферный регистр, генератор тактовых импульсов и мультиплексор, выход которого является вькодом блока управ- ляемой задержки и соединен с входом дифференцирующей цепи, информационные входы мультиплексора, кроме нулевого, соединены с соответствующими выходами сдвигового регистра, нулевой информационный вход - с общей щиной, а входы управления - с соответствующими выходами буферного регистра, С-вход которого соединен с инверсным выходом первого триггера, информационные входы - с соответствующими выходами,счетчика импульсов, а R-вход - с R-входом счетчика импульсов, R-входами второго и третьего триггеров и прямым выходом .третьего триггера, С-вход которого является первым входом блока управляемой задержки и соединен с выходной шиной, D-вход сдвигового регистра, являющийся вторым входом блока управляемой задержки, соединен с выходом элемента задержки и вторым входом элемента И, а С-вход - с выходом генератора импульсов и первым входом первого элемента И, выход которого соединен с С-входом счетчика импульсов, а второй вход - с прямым выходом первого триггера и С-входом второго триггера, инверсный выход которого соединен с первым входом второго элемента И, второй вход которого, являющийся третьим входом блока управляемой задержки, соединен с ходной шиной, а выход - с С-входом первого триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляемый генератор импульсов | 1985 |

|

SU1267594A1 |

| Устройство для формирования импульсов | 1984 |

|

SU1239848A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Устройство для выделения первого и последнего импульсов в серии | 1990 |

|

SU1739492A1 |

| Формирователь импульсов | 1988 |

|

SU1614107A1 |

| Преобразователь активной мощностиВ КОличЕСТВО иМпульСОВ | 1979 |

|

SU845109A1 |

| Программируемый многоканальный формирователь серий импульсов | 1991 |

|

SU1775846A1 |

| Устройство для контроля счетчиков импульсов | 1985 |

|

SU1248061A1 |

| Преобразователь серии импульсов в прямоугольный импульс | 1985 |

|

SU1324096A1 |

| Умножитель частоты следования импульсов | 1991 |

|

SU1803970A1 |

Изобретение относится к импульсной технике и может быть использовано в системах обработки импульсных сигналов. Изобретение позволяет расширить функциональные возможности преобразователя серии импульсов, что достигается преобразованием входных серий с изменяющимся периодом следо-« вания импульсов от серии к серии. Преобразователь содержит входную шину 1, элемент 2 задержки, дифференцирующую -цепь 3, элементы И 4, 5 и 6, триггеры 7, 8, 9 и 10, элемент 11 ЗАПРЕТ, счетчик 12 импульсов, генератор 13 импульсов-, буферный регистр 14, сдвиговый регистр 15, мультиплексор 16 и выходную шину 17. Элементы И 5 и 6, генератор 13 импульсов, триггеры 8, 9 и 10, счетчик 12 импульсов, буферный регистр 14, сдвиговый регистр 15 и мультиплексор 16 с соответствующими связями составляют введенный, в соответствии с данным изобретением, блок управления задержкой, обеспечивдюпщй расширение функциональных возможностей устройства. 2 ил. . (Л

| Устройство для преобразования серии импульсов | 1976 |

|

SU594580A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для преобразования серии импульсов в прямоугольный импульс | 1982 |

|

SU1084980A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-03-23—Публикация

1986-07-07—Подача