t-fj

ff

Ё

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СИНТЕЗА РЕЧЕВЫХ СИГНАЛОВ | 1991 |

|

RU2020608C1 |

| Программируемый генератор импульсов | 1985 |

|

SU1575295A1 |

| Устройство для ввода - вывода информации | 1989 |

|

SU1672430A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| УСТРОЙСТВО СОПРЯЖЕНИЯ МАГИСТРАЛЕЙ | 1990 |

|

RU2017210C1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU1035604A1 |

| Устройство предварительной выборки команд | 1987 |

|

SU1561073A1 |

| МИКРОПРОЦЕССОРНАЯ СИСТЕМА УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМИ ПРОЦЕССАМИ | 1991 |

|

RU2012035C1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Устройство для ввода информации | 1987 |

|

SU1509914A1 |

Изобретение относится к импульсной технике и может быть использовано в схемах устройств автоматики и управления, контроля и диагностики для формирования серий импульсов в однократном или циклическом режимах с синхронизированной во времени организацией адресных переходов

1 Ч

сл

00

N О

адресам, формируемым программно или задаваемым внешним управляющим устройством и программных переходов с одной частоты следования импульсов на другую. Устройство содержит шины управления, адреса и данных, блок интерфейсный, 3 мульИзобретение относится к импульсной технике и может быть использовано в устройствах автоматики и управления, контроля и диагностики.

Известен программируемый генератор импульсов, содержащий основной и дополнительный блоки памяти, интерфейсный блок, шины адреса и данных, буферные регистры, блок управления, блок формирования импульсов, адресный счетчик, таймер, программный счетчик, счетчик циклов, блок пуска, генератор импульсов и элементы И и ИЛИ. Это устройство не изменяет частоты следования импульсов, имеет низкое быстродействие, сложное построение и малый функциональный объем памяти формируемых информационных импульсных последовательностей.

Известно устройство для формирования серий импульсов, содержащее генератор опорной частоты, управляемый делитель частоты, два счетчика импульсов, реверсивный счетчик импульсов, три элемента И, элемент ИЛИ, четыре блока памяти, образующие ПЗУ, компаратор. Устройство имеет неэффективную организацию памяти при формировании больших информационных непериодических серий импульсов и не реализует циклический режим работы.

Наиболее близким по технической сущности к заяявляемому объекту является устройство для формирования импульсов, содержащее задающий генератор, выход которого соединен со счетным входом счетчика, блок памяти, младшие разряды адреса которого соединены с выходами счетчика, а старшие разряды адреса соединены с выходами первого регистра, информационные входы которого соединены с выходами второго регистра, выходные триггеры, информационные входы которых соединены с выходами, кроме первого, блока памяти, стробирующие входы выходных триггеров соединены с выходом задающего генератора и первым входом элемента И, второй вход которого соединен с первым выходом

типлексора, 2 блока памяти, блок программируемого ввода-вывода, 4 счетчика, 3 регистра, N выходных триггеров, выходную шину, дополнительные триггеры, задающий генератор, 7 элементов И, 2 элемента ИЛИ. 1 з.п. ф-лы, 3 ил.

блока памяти, а выход подключен к входу обнуления счетчика и синхронизирующему входу первого регистра. Недостатком известного устройства является отсутствие программно-аппаратных средств изменения частоты следования импульсов, что уменьшает полезную информационную емкость памяти устройства. Так, необходимость формировать в определенные моменты импульсы с меньшей длительностью, но кратной длительности импульсов основной частоты, вызывает уменьшение полезной информационной емкости памяти устройства во столько же раз. Устройство не имеет

программно-аппаратных средств синхронизации при переходе с одной последовательности импульсов на другую, а также при останове, что может привести к искажению формируемой импульсной последовательности.

Целью изобретения является расширение функциональных возможностей и надежности устройства за счет формирования серий импульсов в однократном или циклическом режимах с синхонизированной во времени организацией адресных переходов в ОЗУ во время смены серий импульсов по адресам формируемым программно или задаваемым внешним управляющим устройством и программных переходов с одной частоты следования импульсов на другую, а также при останове устройства.

Поставленная цель достигается тем, что в известное устройство, содержащее задающий генератор, выход которого соединен с счетным входом счетчика, первый и второй регистры, элемент И, первый вход которого соединен с первым входом-выходом блока памяти, N старших входов-выходов, с второго no N+1, которого соединены с информационными входами N выходных триггеров, выходы которых соединены с выходной шиной устройства, дополнительно введены второй блок памяти, шины данных, адреса и

управления, блок интерфейсный, блок программируемый ввода-вывода (ПВВ), второй, третий и четвертый счетчики, третий сдвигающий регистр, первый и второй элементы ИЛИ, второй, третий, четвертый, пятый, шестой и седьмой элементы И, N+1, N+2, N+3, N+4 триггеры, первый, второй и третий мультиплексоры, информационные входы первого из которых соединены с выходами первого счетчика, входы выбора информации - с выходами первого регистра, а выход соединен с счетным входом второго счетчика, вход обнуления которого соединен с вы- ходом второго элемента И и первым входом первого элемента ИЛИ, первый выход - со счетным входом третьего счетчика, первыми инверсными входами третьего и чевтвер- того, первым входом пятого и первым инверсным входом шестого элементов И, второй выход-сстробируемым входом N+1 триггера, вторыми инверсными входами третьего, четвертого и вторыми входами пятого, шестого элементов И, а третий выход - со стробирующим входом N+2 триггера, третьими инверсными входами третьего, четвертого, пятого, шестого и первым входом седьмого элементов И, второй вход которого соединен с выходом N+3 триггера, а выход - с счетным входом четвертого счетчика, первый 2о и второй 22 выходы которого соединены с входами второго элемента И, а вход обнуления - с входами обнуления N+3 триггера, первого счетчика и инверс- ным выходом N-f-4 триггера, информацией- ный вход которого соединен с J-входом N+1 триггера и первой линией логического сигнала Н-уровня шиныуправления, вход обнуления - с выходом первого элемента ИЛИ, а стробирующий вход с первым входом-выходом порта С блока ПВВ, е инверсными входами обнуления N выходных, а также N+1. N+2 триггеров, К-вход N+1-ro из которых соединен с второй линией логического сигнала L-уровня шины управления, а прямой и инверсный выходы - с К-входом и J-входом, соответственно, N+2 триггера, выход которого соединен с первым входом второго элемента ИЛИ, второй вход которо- го соединен с выходом шестого элемента И , а выход- с входом записи третьего счетчика, инверсный вход обнуления которого соединен с третьей линией шины управления устройства, инверсными входами обнуле- ния блока ПВВ, второго регистра и вторым инверсным входом первого элемента ИЛИ, установочные входы соединены с выходами второго мультиплексора, а выходы - с информационными входами второго регистра, стробирующий вход которого соединен с выходом пятого элемента И, а выходы - с первыми информационными входами третьего мультиплексора, выходы которого соединены с адресными входами первого и

второго блоков памяти, вторые информационные входы - с линиями младших разрядов шины адреса, кроме того, два младшие из них дополнительно соединены с адресными входами блока ПВВ, а вход выбора информации-с первым выходом блока интерфейсного, второй, третий, четвертый, пятый и шестой выходы которогоо соединены, соответственно, с входами чтения-записи первого и второго блоков памяти, с входом чтения, входом записи, входом выбора блока ПВВ и четвертой линией шины управления, первый, второй, третий и четвертый входы соединены, соответственно, с пятой, шестой, седьмой и восьмой линиями шины управления, адресные входы - со старшими разрядными линиями шины адреса, первые К входов-выходов - с шиной данных, кроме того К/2 младших из них дополнительно соединены с информационными входами-выходами блока ПВВ, а вторые К, с K+1-ro по 2К-ый, входов-выходов блока интерфейсного соединены с входами-выходами первого и второго блоков памяти, кроме того, дополнительно соединены из них: К+М+5-ый - со вторым входом-выходом порта С блока ПВВ и четвертым входом шестого элемента И, с К+5-го по К+М+4-ый - с информационными входами первого регистра, К+4-ый - с четвертым входом третьего элемента И, К+3-ий -с информационным входом третьего сдви- гающегоо регистра, К+2-ой - с третьим входом-выходом порта С блока ПВВ, К+1-ый - с четвертым входом четвертого элемента И, выход которого соединен со стробирующим входом третьего сдвигающегоо регистра, выходы которого соединены с первыми информационными входами второго мультиплексора, вторые информационные .входы которого соединены с выходами портов А и В блока ПВВ, пятый вход-выход порта С которого соединен с вторым входом первого элемента И, выход которого соединен с установочным входом N+3 триггера. Кроме того выход третьего элемента И соединен с стробирующими входами первого регистра и N выходных триггеров.

Наличие у заявляемого решения отличительных от прототипа признаков обуславливает соответствие этого решения критерию новизна. Исследование описанных выше отличительных признаков заявленного технического, решения устройства, а именно введенных блоков и элементов с присущими им связями показало, что решений со сходной совокупностью признаков, позволяющих получить аналогичный положительный эффект, который отражен в цели изобретения, а науке и технике не обнаружено, а это обстоятельство позволяет утверждать о соответствии решения критерию существенные отличия.

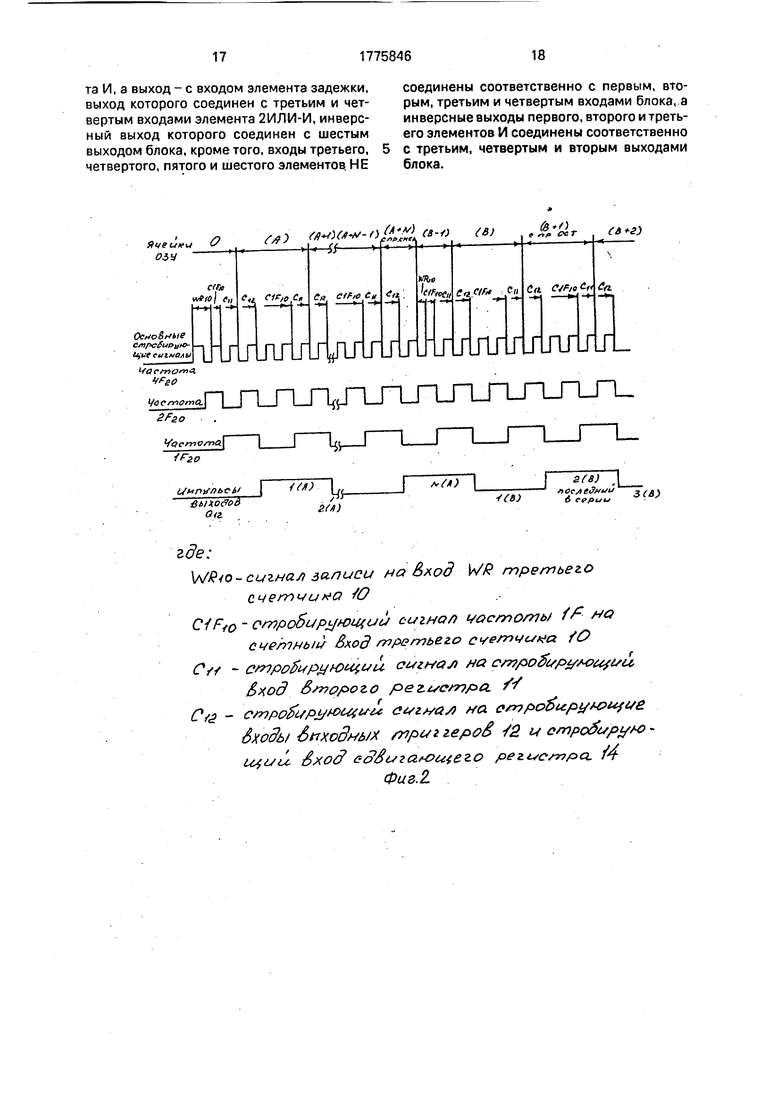

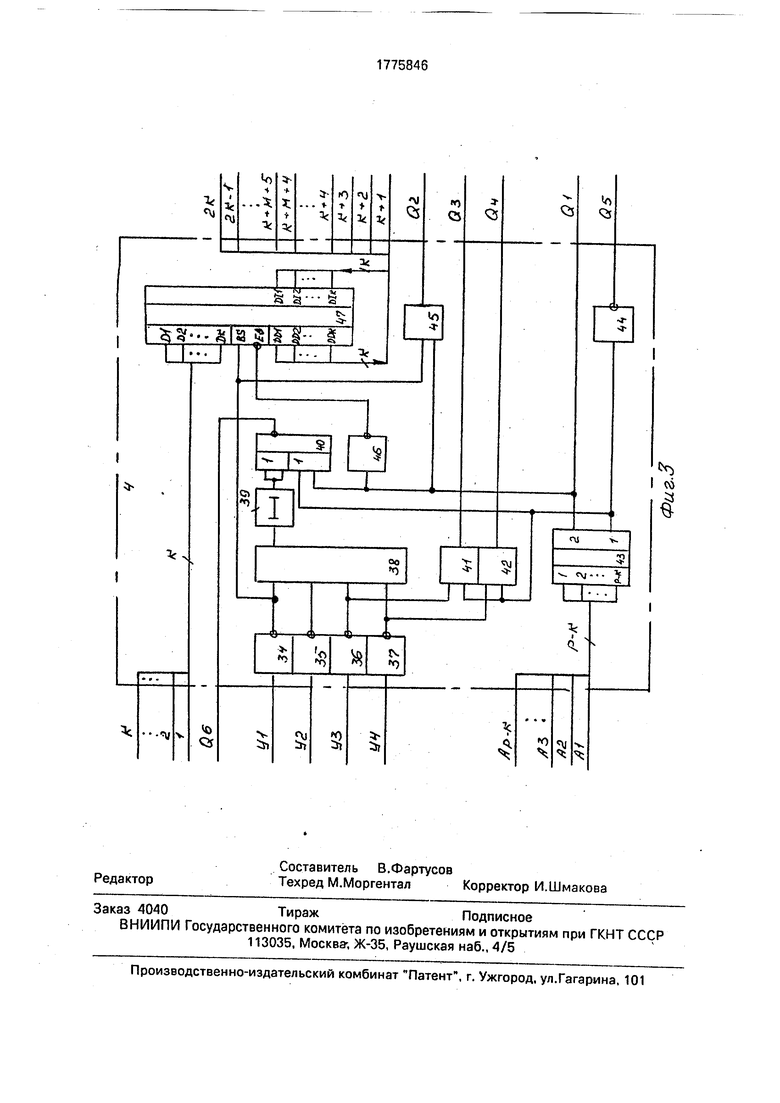

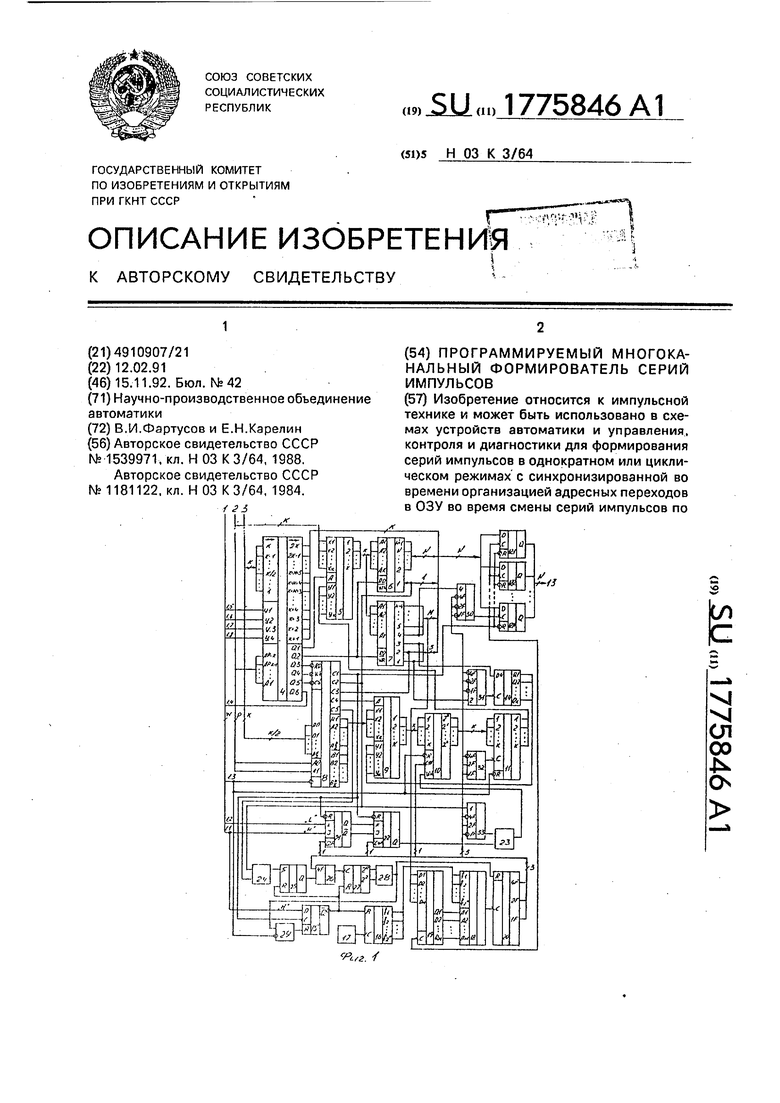

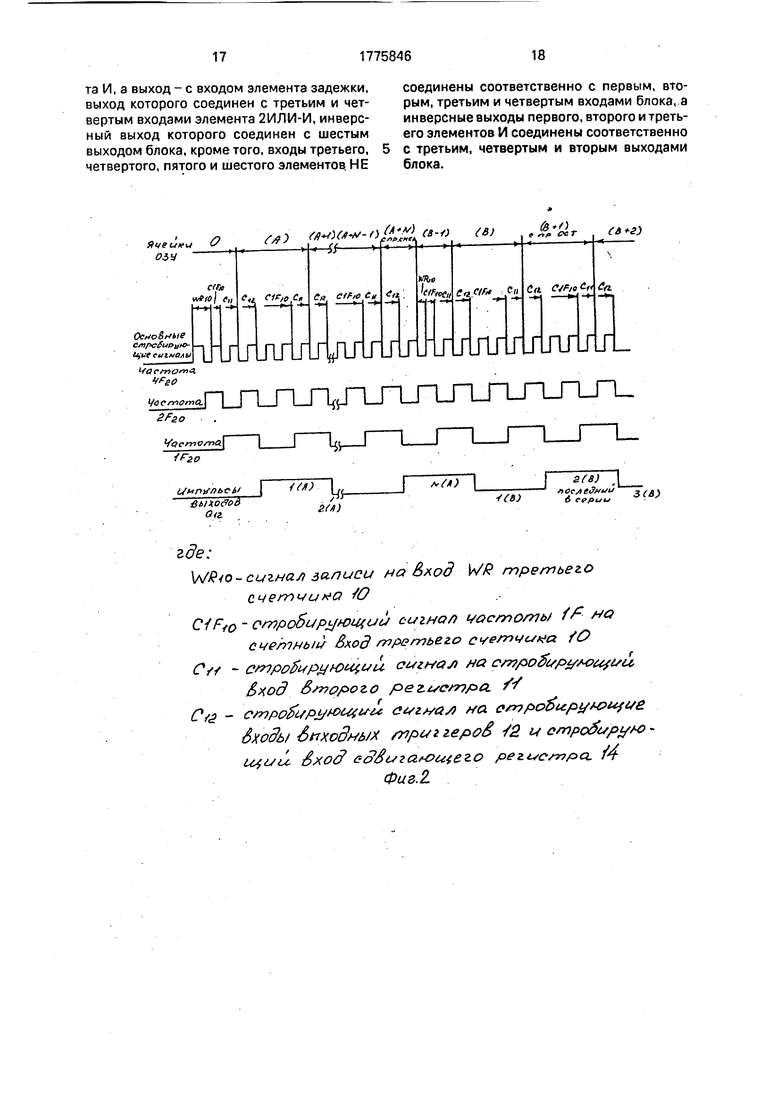

На фиг. 1 представлена функциональная схема программируемого многоканального формирователя серий импульсов; на фиг. 2 - временная диаграмма его работы; на фиг. 3 - функциональная схема блока интерфейсного.

Программируемый многоканальный формирователь серий импульсов содержит шины 1 управления, 2 адреса и 3 данных, блок А интерфейсный, входы которого соединены с шиной управления, первые К входов-выходов с шиной данных, адресные входы-с Р-К старшими адресными линиями шины 2 адреса, К младших адресных линий которой соединены с вторыми информационными входами третьего мультиплексора 5, шесть выходов блока 4 интерфейсного соединены, соответственно, с входом выбора информации мультиплексора 5, входами записи-чтения первого б и второго 7 блоков памяти, входами чтения, записи и выбора блока 8 программируемого ввода-вывода (ПВВ) и четвертой линией шины 1 управления, информационные входы блока 8 ПВВ соединены с К/2 линиями младших разрядов шины 3 данных, два егоо адресных входа соединены с двумя линиями младших разрядов шины 2 адреса, выходы портов А и В - с вторыми информационными входами второго мультиплексора 9, выходы которого соединены с установочными входами третьего счетчика 10, выходы которого соединены с информационными входами второго регистра 11. выходы которого соединены с первыми информационными входами третьего мультиплексора 5, выходы которого соединены с адресными входами первого блока 6 и второго блока 7 памяти, N старших входов-выходов первого блока 6 памяти соединены с информационными входами N выходных триггеров 12, выходы которых соединены с выходной шиной 13, третий вход- выход второго блока 7 памяти соединен с информационным входом третьего регистра 14, выходы которого соединены с первыми информационными входами второго мультипалексора 9, вход выбора информации которого соединен с четвертым входом- выходом порта С блока 8 ПВВ, третий вход-выход порта С которого соединен с вторым входом-выходом второго блока 7 памяти, первый вход-выход порта С - с инверсными входами обнуления N выходных триггеров 12, со стробирующим входом N+4 триггера 15, информационный вход которого соединен с первой линией логического сигнала Н-уровня шины 1 управления, а выход - с входом обнуления первого счетчика

16, счетный вход которого соединен с выходом задающего генератора 17, а выходы соединены с информационными входами первого мультиплексора 18, адресные входы которого соединены с выходами первого регистра 19, а выход - со счетным входом второго счетчика 20, первый 1F выход которого соединен с стробирующим входом третьего счетчика 10, второй 2F выход - с

0 стробирующим входом N+1 триггера 21, J- вход и К-вход которого соединены, соответственно, с первой и второй линиями логического сигнала, соответственно, Н- уровня и L-уровня шины 1 управления, а

5 инверсный вход обнуления соединен с инверсным входом обнуления N+2 триггера 22 и первым входом-выходом порта С блока 8 ПВВ, а прямой и инверсный выходы соединены, соответственно, с К-входом и J-BXO0 дом N+2 триггера 22, стробирующий вход которого соединен с третьим 4F выходом второго счетчика 20, а выход - с первым входом второго элемента 23 ИЛИ, выход которого соединен с входом записи третье5 го счетчика 10. Второй вход-выход порта С- блока 8 ПВВ соединен с первым входом-выходом первого блока 6 памяти и с первым входом первого элемента 24 И, второй вход которого соединен с пятым входом-выходом

0 порта С блока 8 ПВВ, а выход-с установочным входом N+3 триггера 25, выход которого соединен с вторым входом седьмого элемента 26 И, первый вход которого соединен с третьим 4F выходом второго счетчика

5 20, а выход - с счетным входом четвертого счетчика 27, вход обнуления которого соединен с входом обнуления N+3 триггера 25 и инверсным выходом N+4 триггера 15, а выходы - с входами второго элемента 28 И,

0 выход которого соединен с входом обнуления второго счетчика 20 и с первым входом первого элемента 29 ИЛИ, выход которого соединен со входом обнуления N+4 триггера 15, а второй инверсный вход - с третьей

5 линией шины 1 управления, инверсными входами обнуления блока 8 ПВВ, третьего счетчика 10 и второго регистра 11. Кроме того, третий 4F выход второго счетчика 20 соединен с инверсными входами третьего

0 30, четвертого 31. пятого 32 и шестого 33 элеметов И, второй 2F выход - с инверсными входами третьего 30, четвертого 31 и входами пятого 32, шестого 33 элементов И, а первый 1F выход - с инверсными входами

5 третьего 30,-четвертого 31, шестого 33 и вхоодм пятого 32 элементов И. Четвертый вход третьего элемента 30 И соединен с четвертым входом-выходом блока 7 памяти, а выход - со стробирующими входами N выходных триггеров 12 и первого регистра

19, четвертый вход четвертого элемента 31 И соединен с первым входом-выходом блока 7 памяти, а выход - с стробирующим входом третьего сдвигающего регистра 14, выход пятого элемента 32 И соединен с стробирующим входом второго регистра 11, выход шестого элемента 33 И соединен с вторым входом второго элемента 23 ИЛИ, а четвертый вход-с первым входом-выходом первого блока 6 памяти. Причем входы-выходы блоков 6, 7 памяти дополнительно соединены с вторыми К входами-выходами блока 4 интерфейсного.

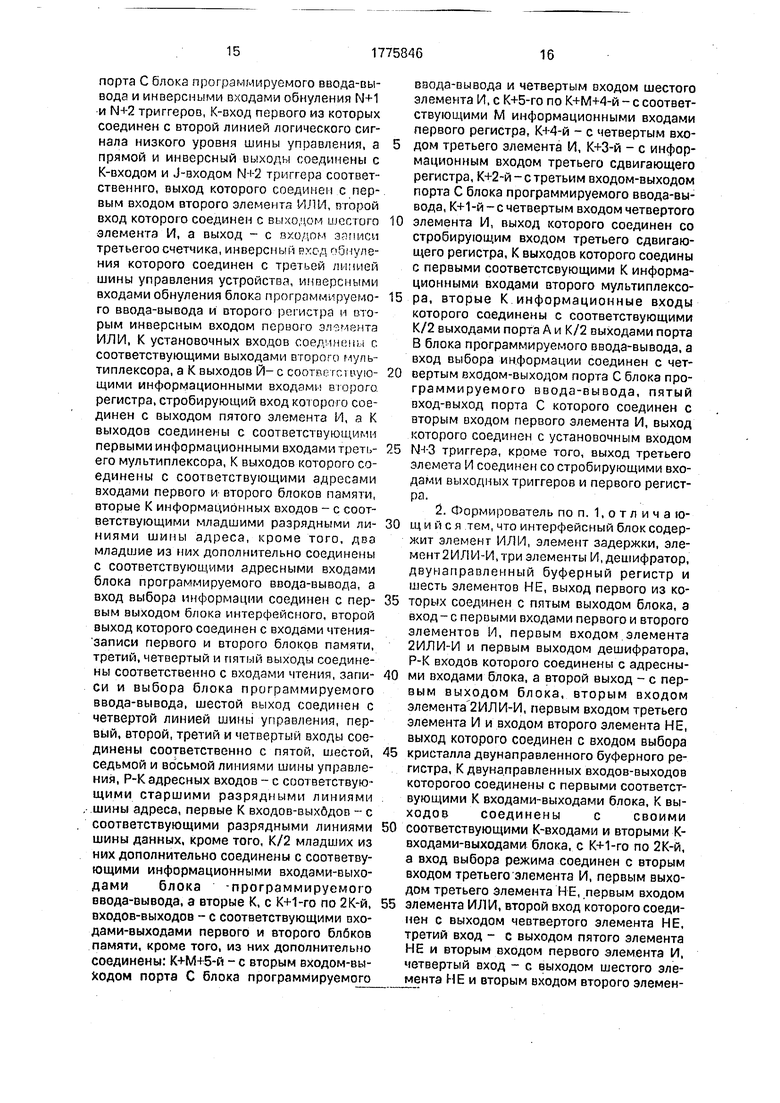

Кроме того, блок 4 интерфейсный содержит третий 34, четвертый 35, пятый 36 и шестой 37 элементы НЕ, входы которых соединены, соответственно, с первым, вторым, третьим и четвертым входами блока, а выходы, соответственно, с первым, вторым, третьим и четвертым входами элемента 38 ИЛИ, выход которого через элемент 39 задержки соединен с третьим и четвертым входами элемента 40 2ИЛИ-И, инверсный выход которого соединен с шестым выходом блока. Выход пятого элемента 36 НЕ дополнительно соединен с вторым входом первого элемента 41 И. Выход шестого элемента 37 НЕ дополнительно соединен с вторым входом второго элемента 42 И, первый вход которого соединен с первым ходом элемента 40 2ИЛИ-И, с первым входом первого элемента 41 И, с первым выходом дешифратора 43 и с входом первого элемента 44 НЕ. Входы дешифратора 43 соединены с адресными входами блока, а его второй выход соединен с первым входом блока, вторым входом элемента40 2ИЛИ-И, первым входом третьего элемента 45 И и входом второго элемента 45 НЕ, выход которого соединен с входом выбора кристалла двунаправленного буферного регистра 47, дву- направленные входы-выходы которого соединены с первыми К входами-выходами блока, выходы соединены с его соответствующими входами и вторыми К входами-выходами блока, а вход выбора режима соединен с выходом третьегоо элемента 34 НЕ, первым входом элемента 38 ИЛИ и вторым входом третьего элемента 45 И, инверсный выход которого соединен с вторым выходом блока. Кроме того, инверсные выходы первого элемента 41 И и второго элемента 42 И соединены, соответственно, с третьим и четвертым выходами блока, а выход первого элемента 44 НЕ соединен с пятым выходом блока.

Устройство работает следующим образом.

Внешнее управляющее устройство (ВУУ) по шинам 1 управления, 2 адреса, 3

данных взаимодействует с устройством. Линии 1.1 и 1.2 шины 1 управления обеспечивают устройство логическими сигналами, соответственно, Н-уровня и L-уровня. Сигнал INIT по линии 1.3 шины 1 управления устанавливает устройство в исходное состояние. С шины 3 данных и шины 2 адреса по сигналам ХАСК и MWTC, соответственно, линий 1.4 и 1.5 шины 1 управления, через

0 блок 4 интерфейсный и третий мультиплексор 5 данные и адрес поступают на первый блок 6 памяти и второй блок 7 памяти и по сигналам первого и второго выходов блока 4 интерфейсного данные записываются в

5 соответствующие ячейки блоков 6,7 памяти. Аналогично по всем адресам в блоки 6,7 памяти записывается вся информация формируемой последовательности серий импульсов.

0

Контрольное считывание информации блоков 6, 7 памяти осуществляется через блок 4 интерфейсный по сигналам ХАСК и MRDC с линий, соответственно, 1.4 и 1.6

5 шины 1 управления.

Старшие N входов-выходов первого блока 6 памяти определяют информационные данные серий импульсов по каждому из выходных каналов, а первый младший вход0 выход - признак смены адреса (СА), согласованный по времени с окончанием каждой серии. Старшие М входов-выходов второго блока 7 памяти определяют выбор основной тактовой частоты устройства, его четвертый

5 вход-выход определяет признак разрешения записи информации N старших входов- выходов первого блока 6 памяти; третий вход-выход содержит в последовательном коде адрес перехода (АП) на следующую се0 рию, второй вход-выход определяет признак разрешения смены адреса перехода (РСАП) внешним управляющим устройством, первый вход-выход-признак разрешения записи адреса перехода (РЗАП).

5 Блок 8 ПВВ выполнен на микросхеме 580 ВВ55. Его программирование осущесу- вляется по К/2 младшим разрядным линиям шины 3 данных по адресу, поступающему с двух младших разрядных линий шины 2 ад0 реса, с помощью управляющих сигналов, вырабатываемых блоком 4 интерфейсным по адресу, получаемому с Р-К старших разрядных линий шины 2 адреса и сигналам IORC, iOWC и ХАСК, соответственно, линий

5 1.7, 1.8 и 1.4 шины 1 управления. Выходы портов Аи В блока 8 ПВВ определяют адрес первой серии импульсов или адрес последующей серии импульсов в режиме РСАП. Режим работы формирователя и его взаимодействие с ВУУ определяется входами-выходами порта С блока 8 ПВВ. Первый из которых выдает сигнал ПУСК устройства, второй принимает сигнал признака СА, третий - сигнал признака РСАП, четвертый выдает сигнал признака выбора АП на следующую серию импульсов от ВУУ или с третьего входа-выхода блока 7 памяти, пятый - признак однократного/многократного режима работы.

По сигналу ПУСК с первого входа-выхода порта С блока 8 ПВВ адрес первой формируемой последовательности с выходов порта А и В блока 8 РВВ поступает через второй мультиплексор 9 по логическому сигналу L-уровня с четвертого входа-выхода порта С блока 8 ПВВ на установочные входы третьего счетчика 10, с выходов которого адрес переписывается на второй регистр 11, с выходов которого через третий мультиплексор 5 адрес поступает на адресные входы блоков 6, 7 памяти.

Сигналом ПУСК снимается обнуление с N выходных триггеров 12, на информационные входы которых по стробам записи записывается информация с N старших входов-выходов блока 6 памяти, а с выходов - информация поступает на N разрядную выходную шину 13 устройства, определяя выходные коды первой серии импульсов.

Программный адрес перехода в последовательном коде поступает в процессе работы формирователя с третьего входа-выхода второго блока 7 памяти на стробируемый сдвигающий регистр t4, с выходов которого адрес перехода через второй мультиплексор 9 по CHI налу Н-уровня с четвертого входа-выхода порта С блока 8 ПВВ поступает на третий счетчик 10. Установка в Н-уровень четвертого входа-выхода порта С блока 8 ПВВ осуществляется, при необходимости, во втором и всех последующих, циклах программирования блока 8 ПВВ, после первого цикла, программирующего сигнал ПУСК.

Сигнал ПУСК через N+4 триггер 15 снимает сигнал обнуления с входа обнуления первого счетчика 16, разрешая его работу по тактовой частоте с задающего генератора 17,2м тактовых частот с выходов первого счетчика 16 поступают на информационные входы первого мультиплексора 18. Выбор тактовой частоты устройства определяется кодом, поступащим с М старших выходов второго блока 7 памяти на адресные входы первого мультиплексора 18 через стробируемый первый регистр 19. Тактовая частота устройства поступает на вход второго бчет- чика 20, на выходах которого формируются синхронизирующие частоты 1F, 2F, 4F.

По сигналу ПУСК снимается сигнал обнуления с N+1 и N+2 триггеров 21 и 22, которые формируют через второй элемент 23 ИЛИ сигнал записи на третий счетчик 10.

Синхронизирующая частота 1F, поступающая на стробирующий вход третьего счетчика 10, последовательно наращивают его выходной код, через второй регистр 11 и третий мультиплексор 5 поступающий на

адресные входы блоков 6, 7 памяти.

Последовательно изменяя коды адреса устройство формирует серию импульсов, информационные и частотные параметры которой по каждому из выходов выходной

шины 13 устройства определяются содержимым ячеек входов-выходов блоков 6, 7 памяти. По достижению конца заданной серии на первом входе-выходе блока 6 памяти появляется в виде Н-уровня логический сигнал признака СА.

Признак однократного режима работы в виде Н-уровня логического сигнала с пятого входа-выхода порта С блока 8 ПВВ разрешает прохождение сигнала признака СА через

первый элемент 24 И на установочный вход N+3 триггера 25, выходной сигнал Н-уровня которого разрешает прохождение тактовой частоты 4F через седьмой элемент 26 И и на счетный вход четвертого счетчика 27. Работа N+3 триггера 25 и четвертого счетчика 27 разрешается сигналом L-уровня с инверсного выхода N+4 триггера 15 одновременно с разрешением работы первого счетчика 16. 2о и 22 выходы четвертого счетчика 27 разрешают по спаду пятого строба частоты 4F прохождение обнуляющего сигнала Н-уровня через второй элемент 28 И на вход обнуления второго счетчика 20 и через первый элемент 29 ИЛИ на вход обнуления N+4

триггера 15, сигнал Н-уровня с инверсного выхода которого запрещает работу первого счетчика 16, точно синхронизируя таким образом, момент окончания формируемой серии импульсов. В случае циклического

режима работы порталу L-уровня с пятого входа-выхода порта С блока 8 ПВВ запрещается останов работы формирователя, а сигнал Н-уровня признака СА через шестой элемент 33 И по синхронизирующим частотам 1F, 2F, 4F и через второй элемент 23 ИЛИ формирует сигнал записи третьего счетчика 10, на выходах которого устанавливается код В-1 адреса следующей серии импульсов. По очередному спаду сигнала

тактовой частоты 4F на счетном входе третьего счетчика 10 на его выходе код адреса увеличивается до В, то есть адреса начала следующей серии. Работа устройства продолжается.

Синхронизация во времени стробов N выходных регистров 12, сдвигающего регистра 14 и второго регистра 11 относительно третьего счетчика 10 осуществляется с помощью третьего 30, четвертого 31 и пятого 32 элементов И.

Синхронизация перехода с одной тактовой частоты устройства на другую с L-уров- нем сигналов синхронизирующих частот 1F, 2F, 4F на выходах второго счетчика 20 позволяет формировать с переменной частотой серии импульсов без их искажения.

Останов устройства осуществляется перепрограммированием пятого входа-выхода порта С блока 8 ПВВ, сигнал Н-уровня с которого является признаком однократного режима работы. По этому сигналу устройство заканчивает работу по окончанию формирования текущей серии импульсов.

Блок 4 интерфейсный взаимодействует с шинами интерфейса И-41. Сигналы MWTC, MRDC, IORC, IOWC поступают с линий, соответственно, 1.5,1.6,1,7,1.8 шины 1 управления на входы элементов, соответственно 34, 35, 36, 37 НЕ блока 4 интерфейсного, которые через элемент 38 ИЛИ, элемент 39 задержки, элемент 40 2ИЛИ-И блока 4 ин- герфейсногоо формируют сигнал ХАСК на его шестой выход. Сигнал ХАСК формируется по сигналам MWTC и MRDC при адресации к блокам 6, 7 памяти или сигналами IORC и IOWC при адресации к блоку 8 ПВВ, когда код с Р-К старших адресных линий шины 2 адреса определяет сигнал Н-уровня на втором или первом выходах дешифратора 43, который стробирует прохождение сигнала ХАСК через элемент 40 2ИЛИ-И блока 4 интерфейсного. Сигнал Н-уровня второго выхода дешифратора 43 через элемент 46 Н Е блока 4 интерфейсного и сигнал MWTC разрешают прохождение информации через двунаправленный буферный регистр 47 блока 4 интерфейсного с шины 3 данных на входы-выходы блоков 6,7 памяти и формируют сигнал записи на второй выход блока 4 интерфейсногоо для блоков 6, 7 памяти. При отсутствии сигнала МТ Л/Сблок 4 интерфейсный считывает информацию из блоков 6, 7 памяти по заданому адресу и сигналу MRDC в обратном направлении. Сигнал Н-уровня на первом выходе дешифратора 43 блока 4 интерфейсногоо стробирует прохождение сигналов IORC и IOWC через элементы 41, 42 И блока 4 интерфейсного на его третий и четвертый выходы, а через элемент 44 НЕ формирует сигнал на пятый выход блока 4 интерфейсного, задавая таким образом сигналы, соответственно, чтения, записи и выбора при программировании блока 8 ПВВ.

Формула изобретения 1. Программируемый многоканальный формирователь серий импульсов, содержащий задающий генератор, выход которого

соединен со счетным входом счетчика, первый и второй регистры, элемент И, первый вход которого соединен с первым выходом блока памяти, N старших выходов, с второго по N+1-й, которого соединены с соответст0 вующими информационными входами выходных триггеров, выходы которых соединены с выходной шиной устройства, отличающийся тем, что, с целью расширения функциональных возможно5 стей и повышения точности формирования импульсов, в него введены второй блок памяти, шины данных, адреса и управления, интерфейсный блок, программируемый блок ввода-вывода, второй, третий и четвер0 тый счетчики, третий сдвигающий регистр, первый и второй элементы ИЛИ, второй, третий, четвертый, пятый, шестой и седьмой элементы И, N+1, N+2, N+3, N+4 триггеры, первый, второй и третий мультиплексоры,

5 два информационных входа первого из которых соединены с соответствующими выходами первого счетчика, М входов выбора информации - с соответствующими выходами первого регистра, а выход соединен со

0 счетным вввходом второго счетчика, вход обнуления которого соединен с выходом второго элемента И и первым входом первого элемента ИЛИ, первый выход - со счетным входом третьего счетчика, первыми

5 инверсными входами третьего и четвертого, первым входом пятого и первым инверсным входом шестого элементов И, второй выход- со стробирующим входом N+1 триггера, вторыми инверсными входами третьего

0 и четвертого элеметов И, вторыми входами пятого и шестого элементов И, а третий выход - со стробирующим входом N+2 триггера, третьими инверсными входами третьего, четвертого, пятого, шестого элементов И и

5 первым входом седьмого элемента И, второй вход которого соединен с выходом N+3 триггера, а выход - со счетным входом четвертого счетчика, первый и второй выходы которого соединены с соответствующими

0 входами второго элемента И, а вход обнуления соединен с входом обнуления N+3 триггера, входом обнуления первого счетчика и инверсным выходом N+4 триггера, информационный вход которого соединен с пер5 вой линией логического си гнала высокого уровня шины управления и J-входом N+1 триггера, вход обнуления - с выходом первого элемента ИЛИ, а стробирующий вход с инверсными входами обнуления N выходных триггеров, первым входом-выходом

орта С блока программируемого ввода-выода и инверсными входами обнуления N+1 N+2 триггеров, К-вход первого из которых оединен с второй линией логического сигнала низкого уровня ашны управления, а прямой и инверсный выходы соединены с К-входом и J-входом N+2 триггера соответ- твеннго, выход которого соединен с перым входом второго олементй ИЛИ, второй вход которого соединен с выходом шестого лемента И, а выход - с входом зямиси ретьегоо счетчика, инверсиыи РХОД jny/ie- ния которого соединен с третьей линией шины управления устройства, инверсными входами обнуления блока программируемого ввода-вывода и второго регистра и вторым инверсным входом первою элемента ИЛИ, К установочных входов соедмнечм г, соответствующими выходами вгорого мультиплексора, а К выходов Й- с COOTFU го вую- щими информационными входами второго регистра, стробирующий вход которого соединен с выходом пятого элемента И, а К выходов соединены с соответствующими первыми информационными входами третьего мультиплексора, К выходов которого соединены с соответствующими адресами входами первого и второго блоков памяти, вторые К информационных входов - с соответствующими младшими разрядными линиями шины адреса, кроме того, два младшие из них дополнительно соединены с соответствующими адресными входами блока программируемого ввода-вывода, а вход выбора информации соединен с первым выходом блока интерфейсного, второй выход которого соединен с входами чтения- записи первого и второго блоков памяти, третий, четвертый и пятый выходы соединены соответственно с входами чтения, записи и выбора блока программируемого ввода-вывода, шестой выход соединен с четвертой линией шины управления, первый, второй, третий и четвертый входы соединены соответственно с пятой, шестой, седьмой и восьмой линиями шины управления, Р-Кадресных входов - с соответствующими старшими разрядными линиями шины адреса, первые К входов-выхбдов - с соответствующими разрядными линиями шины данных, кроме того, К/2 младших из них дополнительно соединены с соответву- ющими информационными входами-выходами блока -программируемого ввода-вывода, а вторые К, с К+1-го по 2К-й, входов-выходов - с соответствующими входами-выходами первого и второго блбков памяти, кроме того, из них дополнительно соединены: К+М-(5-й - с вторым входом-выходом порта С блока программируемого

ввода-вывода и четвертым входом шестого элемента И, с К+5-го по К+М+4-й - с соответствующими М информационными входами первого регистра, К+4-й - с четвертым входом третьего элемента И, К+3-й - с информационным входом третьего сдвигающего регистра, К+2-й- с третьим входом-выходом порта С блока программируемого ввода-вывода, К+1-й - с четвертым входом четвертого

0 элемента И, выход которого соединен со пробирующим входом третьего сдвигающего регистра, К выходов которого соедины с первыми соответствующими К информационными входами второго мультиплексо5 ра, вторые К информационные входы которого соединены с соответствующими К/2 выходами портя А и К/2 выходами порта В блока программируемого ввода-вывода, а вход выбора информации соединен с чет0 вертым входом-выходом пор га С блока программируемого ввода-вывода, пятый вход-выход порта С которого соединен с вторым входом первого элемента И, выход которого соединен с установочным входом

5 триггера, кроме того, выход третьего элемета И соединен со стробирующими входами выходных триггеров и первого регистра.

5 кристалла двунаправленного буферного регистра, К двунаправленных входов-выходов которогоо соединены с первыми соответствующими К входами-выходами блока, К выходов соединены с своими

0 соответствующими К-входами и вторыми К- входами-выходами блока, с К+1-го по 2К-й, а вход выбора режима соединен с вторым входом третьего элемента И, первым выходом третьего элемента НЕ, первым входом

5 элемента ИЛИ, второй вход которого соединен с выходом чевтвертого элемента НЕ, третий вход - с выходом пятого элемента НЕ и вторым входом первого элемента И, четвертый вход - с выходом шестого элемента НЕ и вторым входом второго элемента И, а выход - с входом элемента задежки, выход которого соединен с третьим и четвертым входами элемента 2ИЛИ-И, инверсный выход которого соединен с шестым

соединены соответственно с первым, вторым, третьим и четвертым входами блока, а инверсные выходы первого, второго и третьего элементов И соединены соответственно

„,,„.. к „- w..wi-i«nn/e п иснппспы ответственно

выходом блока, кроме того, входы третьего, 5 с третьим, четвертым и вторым выходами четвертого, пятого и шестого элементов. НЕ блока.выходами

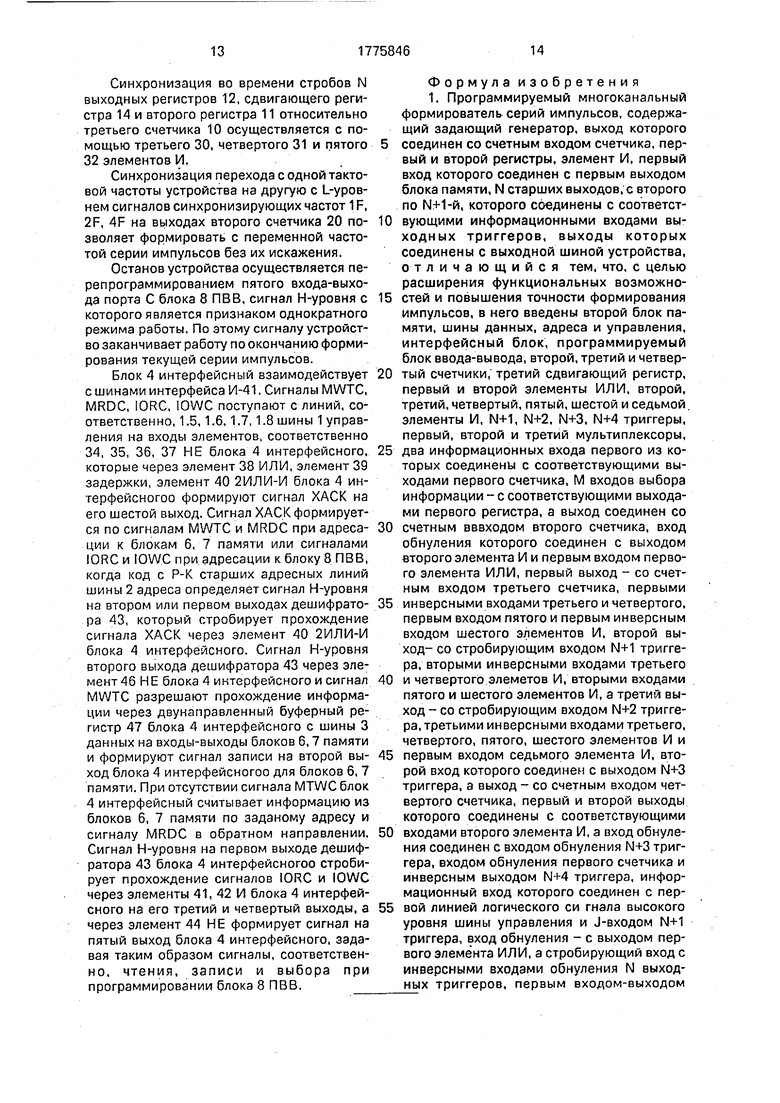

ГА) +(-(;Ј (-л (&) ffrЈr ca+s)

Частот ffS0

Частота. 2Рго

riJTJ jTfljanj JTJTJTjn-rL.

lfQcrnafr ci

fT

где:

A/f io-сигнал записи на Вход V/R третьего счетчихо /О

CSFfO отробирующим сигнол частогпь/ ff &Q

счегпныи Вход третьего cvemvc/xa fO C/s - строёирующии сигнал на сгя/зо$#Ј Ј// ощии

Ssnopozo pezucrrjpa. // - cmpofapytcitfuze ) но. c/r poЈtcpi/t€ ujt/e

бходы бпходмых snpuz геро& /ё t/ отроЈирую и$ии, 6xotf ес Јс/га 0и е.о pezisc/npo. 14 Фиг.2.

соединены соответственно с первым, вторым, третьим и четвертым входами блока, а инверсные выходы первого, второго и третьего элементов И соединены соответственно

- w..wi-i«nn/e п иснппспы ответственно

с третьим, четвертым и вторым выходами блока.выходами

W

I

| Устройство для формирования серий импульсов | 1988 |

|

SU1539971A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Авторское свидетельство СССР № 1181122 | |||

| кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-11-15—Публикация

1991-02-12—Подача