Изобретение относится к электронной технике, в частности к способам форсированных и ускоренных испытаний цифровых интегральных микросхем на надежность.

Целью изобретения является повышение величины форсированной нагрузки и ее однородности для элементов цифровой микросхемы в процессе испытаний на надежность, т.е. повышение эффективности испытаний.

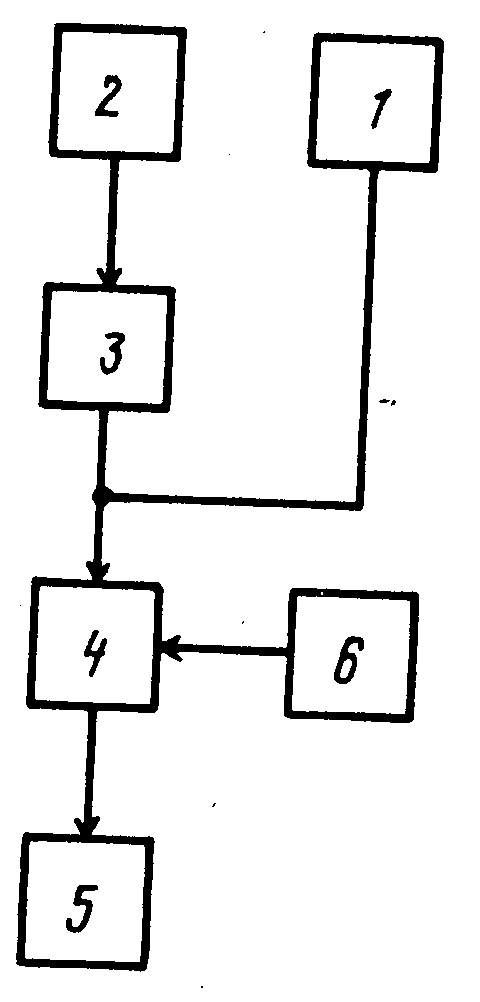

На чертеже приведена блок-схема установки для реализации предлагаемого способа испытаний.

Электрическое смещение с источника 1 и переменные сигналы с генератора 2 через фазовращатель 3 подают на входы микросхемы 4, выходные сигналы с которой поступают на нагрузку 5. Источник питания 6 обеспечивает режим работы микросхемы 4 по постоянному току или напряжению. Величина постоянного смещения с источника 1 и переменные входные сигналы с генератора 2 задают динамический режим работы элементов цифровой микросхемы в пределах переходного участка ее выходной переключательной характеристики.

Сущность способа заключается в одновременном введении всех элементов цифровой микросхемы в динамический режим работы на переходном участке выходной переключательной характеристики на частотах, на которых отсутствует формирование логических сигналов внутри и на выходах микросхемы. Для этого на входы цифровой интегральной микросхемы подают электрическое смещение и переменные сигналы с амплитудами в пределах переходного участка входной переключательной характеристики при различных сочетаниях фазы переменных сигналов и с частотой, на которой амплитуды соответствующих переменных сигналов на выходах микросхемы остаются в пределах переходного участка ее переключательной характеристики.

Частота входных переменных сигналов соответствует частоте, при которой в элементах и на выходах микросхемы исключается формирование логических сигналов (согласно результатам испытаний для КМОП цифровых микросхем, частота входных переменных сигналов на порядок превышает максимальную рабочую частоту изделия). Для исключения фиксации состояния элементов микросхемы в определенной рабочей точке в пределах переходного участка входной переключательной характеристики изменяют соответствие фаз входных переменных сигналов с помощью фазовращателя 3. В качестве нагрузки 5 могут быть применены пассивные цепи или входы однотипных испытываемых микросхем при объединении их в параллельно-последовательные цепочки.

Способ позволяет повысить величину и однородность форсированной нагрузки при испытаниях цифровых интегральных микросхем на надежность и таким образом сократить длительность испытаний, повысить достоверность их результатов. В зависимости от степени интеграции и логической структуры испытываемых цифровых микросхем величина форсированной нагрузки может измеряться от 10 до 104 раз и увеличивается с ростом степени интеграции цифровых микросхем.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ КОНТРОЛЯ ЦИФРОВЫХ ИНТЕГРАЛЬНЫХ МИКРОСХЕМ | 1986 |

|

SU1417613A1 |

| СПОСОБ ИЗМЕРЕНИЯ ПЕРЕХОДНОЙ ХАРАКТЕРИСТИКИ ЦИФРОВЫХ ИНТЕГРАЛЬНЫХ МИКРОСХЕМ | 2020 |

|

RU2766066C1 |

| СПОСОБ ОПРЕДЕЛЕНИЯ ТЕПЛОВОГО ИМПЕДАНСА КМОП ЦИФРОВЫХ ИНТЕГРАЛЬНЫХ МИКРОСХЕМ | 2011 |

|

RU2463618C1 |

| СПОСОБ ОПРЕДЕЛЕНИЯ ТЕПЛОВОГО ИМПЕДАНСА ЦИФРОВЫХ КМОП ИНТЕГРАЛЬНЫХ МИКРОСХЕМ | 2012 |

|

RU2504793C1 |

| СПОСОБ КОНТРОЛЯ ИДЕНТИЧНОСТИ ИЗДЕЛИЙ В ПАРТИИ ОДНОТИПНЫХ МИКРОСХЕМ | 2014 |

|

RU2554675C1 |

| Способ электротермотренировки интегральных микросхем | 1986 |

|

SU1449950A1 |

| ВСЕНАПРАВЛЕННЫЙ РАДИОПЕЛЕНГАТОР | 1996 |

|

RU2126978C1 |

| ДЕТЕКТОР УРОВНЯ И СПОСОБ ДЕТЕКТИРОВАНИЯ УРОВНЯ ВХОДНОГО СИГНАЛА | 1994 |

|

RU2171007C2 |

| СПОСОБ ОПРЕДЕЛЕНИЯ ТЕПЛОВОГО ИМПЕДАНСА СВЕРХБОЛЬШИХ ИНТЕГРАЛЬНЫХ СХЕМ - МИКРОПРОЦЕССОРОВ И МИКРОКОНТРОЛЛЕРОВ | 2012 |

|

RU2521789C2 |

| МАГНИТОМЕТР СО СВЕРХПРОВОДЯЩИМ КВАНТОВЫМ ИНТЕРФЕРОМЕТРИЧЕСКИМ ДАТЧИКОМ | 2011 |

|

RU2481591C1 |

Изобретение может быть использовано для форсированного и ускоренного испытания цифровых интегральных микросхем (М) на надежность. Цель изобретения - повышение величины форсированной нагрузки и ее однородности. Для этого осуществляется одновременное введение всех элементов М в динамический режим работы на переходном участке выходной переключательной характеристики на частотах, на которых отсутствует формирование логических сигналов внутри и на выходах М. При этом на входы М подают электрическое смещение и переменные сигналы. Амплитуды последних - в пределах переходного участка входной переключательной характеристики при различных сочетаниях фазы переменных сигналов. Частота поддерживается таковой, что амплитуды соответствующих переменных сигналов на выходах М остаются в пределах переходного участка ее переключательной характеристики. 1 ил.

СПОСОБ ИСПЫТАНИЙ ЦИФРОВЫХ ИНТЕГРАЛЬНЫХ МИКРОСХЕМ, предусматривающий создание форсированной нагрузки испытуемой интегральной микросхемы, путем подачи на ее выводы переменного электрического напряжения и контроля правильности ее функционирования, отличающийся тем, что, с целью повышения эффективности испытаний, на входы испытуемой интегральной микросхемы подают постоянное электрическое смещение и устанавливают амплитуду переменного электрического напряжения в пределах переходного участка входной переключательной характеристики интегральной микросхемы, контролируют амплитуду выходного сигнала микросхемы, увеличивают частоту до значения, при котором амплитуда выходных сигналов микросхемы находилась в пределах переходного участка выходной переключательной характеристики интегральной микросхемы, после чего проводят контроль функционирования интегральной микросхемы.

| Устройство для охлаждения водою паров жидкостей, кипящих выше воды, в применении к разделению смесей жидкостей при перегонке с дефлегматором | 1915 |

|

SU59A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1994-12-15—Публикация

1986-06-24—Подача