Изобретение относится к радиоэлектронной промьшшенности и может быть использовано как на предприятиях-изготовителях интегральных микро- схем, так и на предприятиях, использующих микросхемы в разнообразной аппаратуре повьшенной надежности.

Цель изобретения - повьшение эффективности электротермотренировки интегральных микросхем.

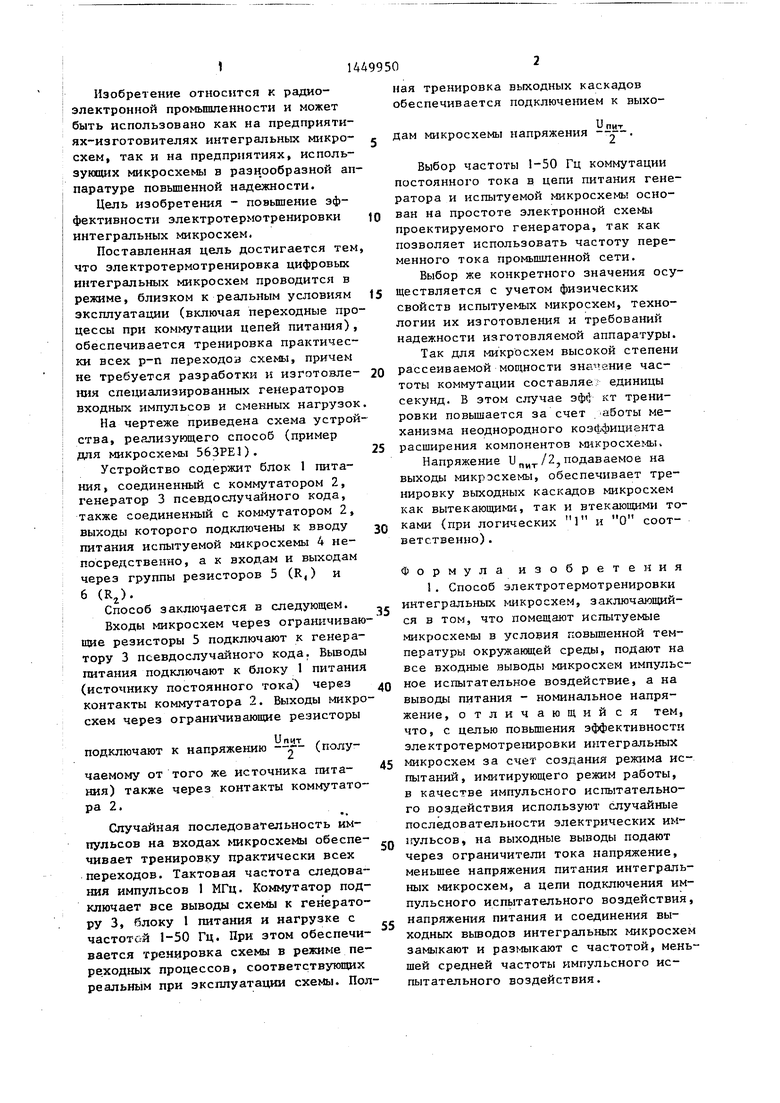

Поставленная цель достигается тем, что электротермотренировка цифровых интегральных микросхем проводится в режиме, близком к реальным условиям эксплуатации (включая переходные процессы при коммутации цепей питания), обеспечивается тренировка практически всех р-п переходов схемы, причем не требуется разработки и изготовле- 1ШЯ спетдаализированных генераторов входных импульсов и сменных нагрузок. На чертеже приведена схема устройства, реализующего способ (пример для микросхемы 563РЕ1).

Устройство содержит блок 1 питания, соединенный с коммутатором 2, генератор 3 псевдослучайного кода, также соединенный с коммутатором 2, выходы которого подключены к вводу питания испытуемой микросхемы 4 непосредственно, а к входам и выходам через группы резисторов 5 (R,) и

6 (кр.

Способ заключается в следующем. Входы микросхем через ограничиваю щие резисторы 5 подключают к генератору 3 псевдослучайного кода. Выводы питания подключают к блоку 1 питания (источнику постоянного тока) через контакты коммутатора 2. Выходы микросхем через ограничивающие резисторы

UnHT ..

подключают к напряжению -.j- (полу

чаемому от того же источника питания) также через контакты коммутатора 2.

Случайная последовательность импульсов на входах микросхемы обеспечивает тренировку практически всех переходов. Тактовая частота следования импульсов 1 МГц. Коммутатор подключает все выводы схемы к генератору 3, блоку 1 питания и нагрузке с частотой 1-50 Гц. При этом обеспечи вается тренировка схемы в режиме переходных процессов, соответствующих реальным при эксплуатации схемы. Пол

,-

j

10

15 20 25

30

Q 45

50

55

ная тренировка выходных каскадов обеспечивается подключением к выхои пит дам микросхемы напряжения --2

Выбор частоты 1-50 Гц коммутации постоянного тока в цепи питания генератора и испытуемой микросхемы основан на простоте электронной cxeMbi проектируемого генератора, так как позволяет использовать частоту переменного тока промьшшенной сети.

Выбор же конкретного значения осуществляется с учетом физических свойств испытуемых микросхем, технологии их изготовления и требований надежности изготовляемой аппаратуры. Так для 1 шкросхем высокой степени рассеиваемой мосщости значение частоты коммутации составляв единицы секунд. В этом случае эфф кт тренировки повышается за счет -аботы механизма неоднородного коэффициента расширения компонентов микросхемы Напряжение ,подаваемое на выходы микросхемы, обеспечивает тренировку выходных каскадов микросхем как вытекающими, так и втекающими токами (при логических 1 и О соответственно) .

Формула изобретения

1, Способ электротермотренировки интегральных микросхем, заключающийся в том, что помещают испытуемые микросхемы в условия повышенной температуры окружаняцей среды, подают на все входные выводы микросхем импульсное испытательное воздействие, а на выводы питания - номинальное напряжение, отличающийся тем, что, с целью повьш1ения эффективности злектротермотренировки интегральных микросхем за счет создания режима испытаний, имитирующего режим работы, в качестве импульсного испытательного воздействия используют случайные последовательности электрических им- 11ульсов, на выходные выводы подают через ограничители тока напряжение, меньщее напряжения питания интегральных микросхем, а цепи подключения импульсного испытательного воздействия, напряжения питания и соединения выходных вьшодов интегральных микросхем замыкают и размыкают с частотой, меньшей средней частоты импульсного испытательного воздействия.

1449950

2. Способ по II.I, отличаю-ности, на выходные выводы микрос.хем

щ и и с я тем, что, с целью увеличе- через ограничители тока подают иапря- ния эффективности электротермотрени- жение, равное половине напряжете ровки интегральных микросхем за счетпитания,

увеличения средней рассеиваемой мощ

Изобретение относится к радио- элгктронной промышленности, в частности к способам контроля интегральных схем. Цель изобретения - повышение эффективности электротермотрени- ровки интегральнык схем. Входы микро схем через ограничивающие резисторы П Г 5 подключают к генератору 3 псевдослучайного кода. Выводы питения подключают к блоку 1 питания через контакты коммутатора 2. Выходы микросхем через ограничивающие резисторы подключают к половине напряжения питания через контакты коммутатора 2. Тактовая частота следования импульсов выбирается высокой, например 1 МГц. Коммутатор подключает все выводы интегральной схемы к генератору 3 псевдослучайного кода и блоку 1 питания с частотой 1-50 Гц. При этом обеспечивается тренировка в режиме переходных процессов. Полная тренировка выходных каскадов обеспечивается подключением к выходам микросхемы половинного напряжения питания. 1з.п. ф-лы, 1 ил. и, Hutn/г m

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Нивелир для отсчетов без перемещения наблюдателя при нивелировании из средины | 1921 |

|

SU34A1 |

| Верхний многокамерный кессонный шлюз | 1919 |

|

SU347A1 |

| Способ очищения сернокислого глинозема от железа | 1920 |

|

SU47A1 |

Авторы

Даты

1989-01-07—Публикация

1986-10-08—Подача