Изобретение относится к электротехнике и может быть использовано для управления полупроводниковыми преобразователями со слежением за кривой выходного напряжения.

Целью изобретения является расширение области использования за счет применения для управления Преобразователями с многоуровневым выходным напряжением, формируемым из импульсов неодинаковых амплитуд, количество которых равно п.

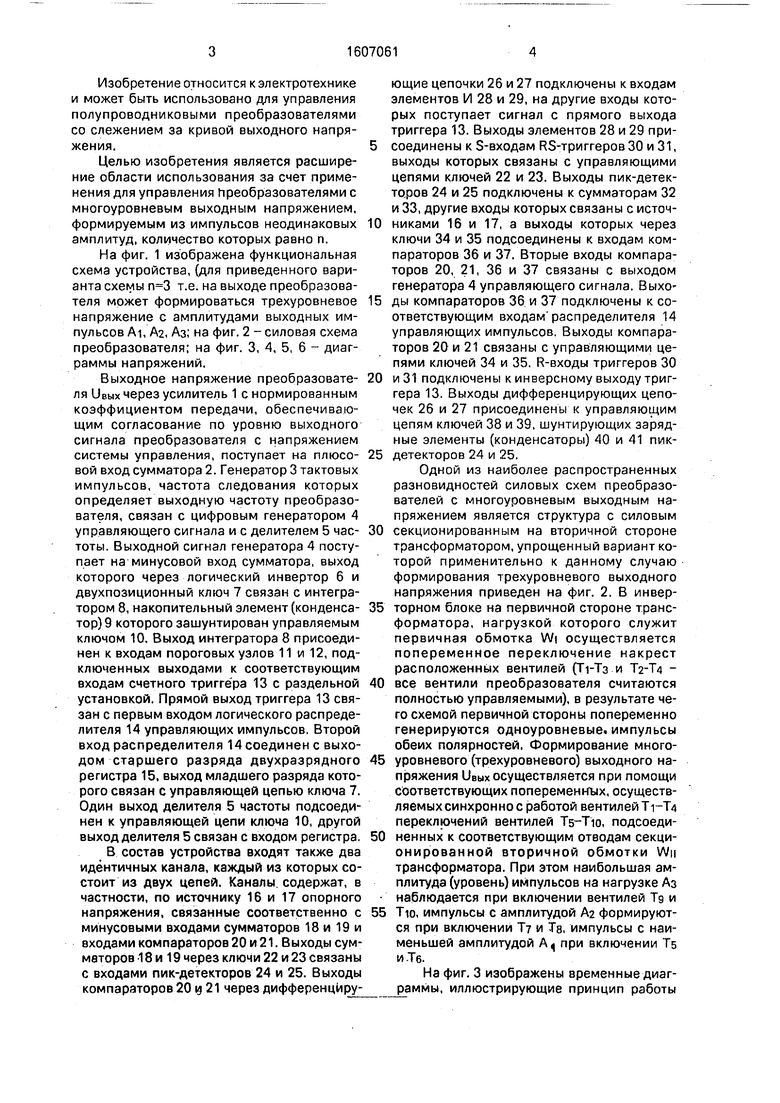

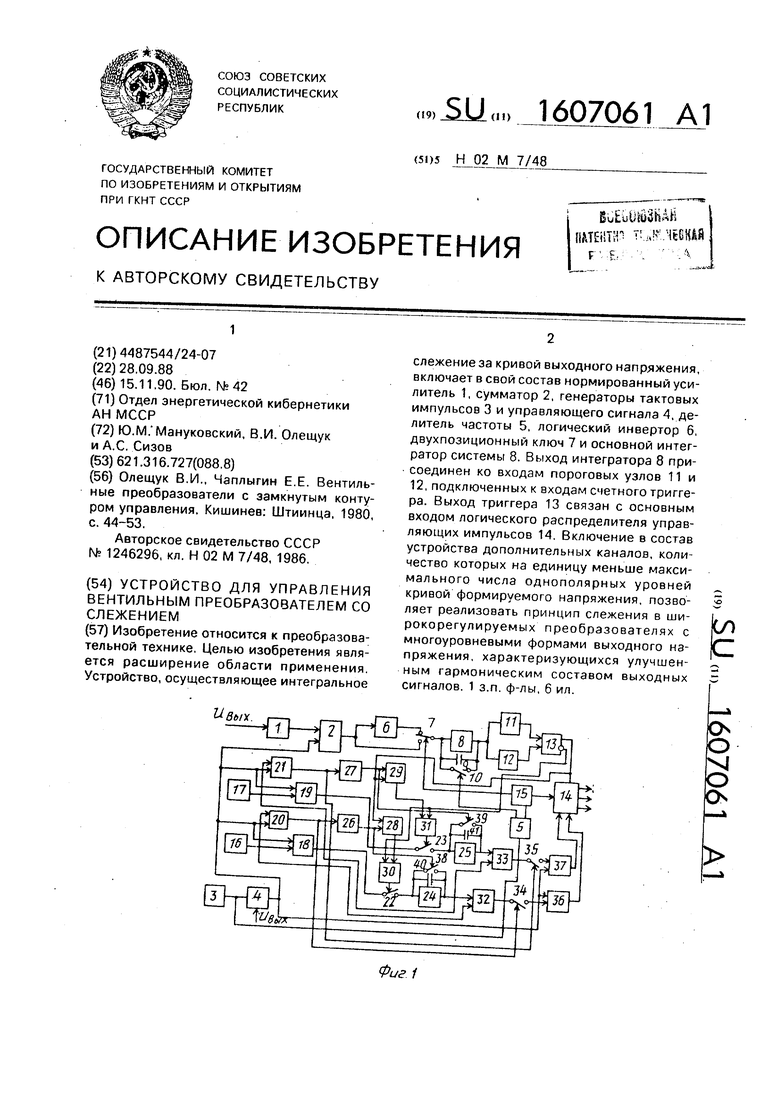

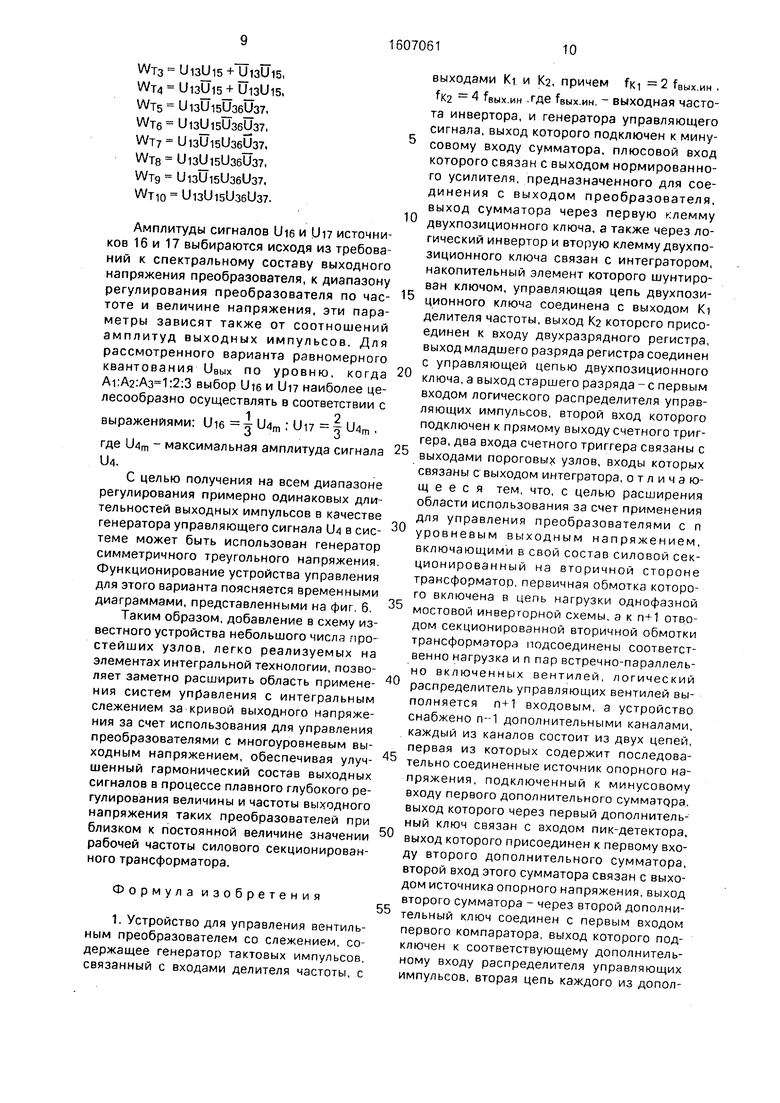

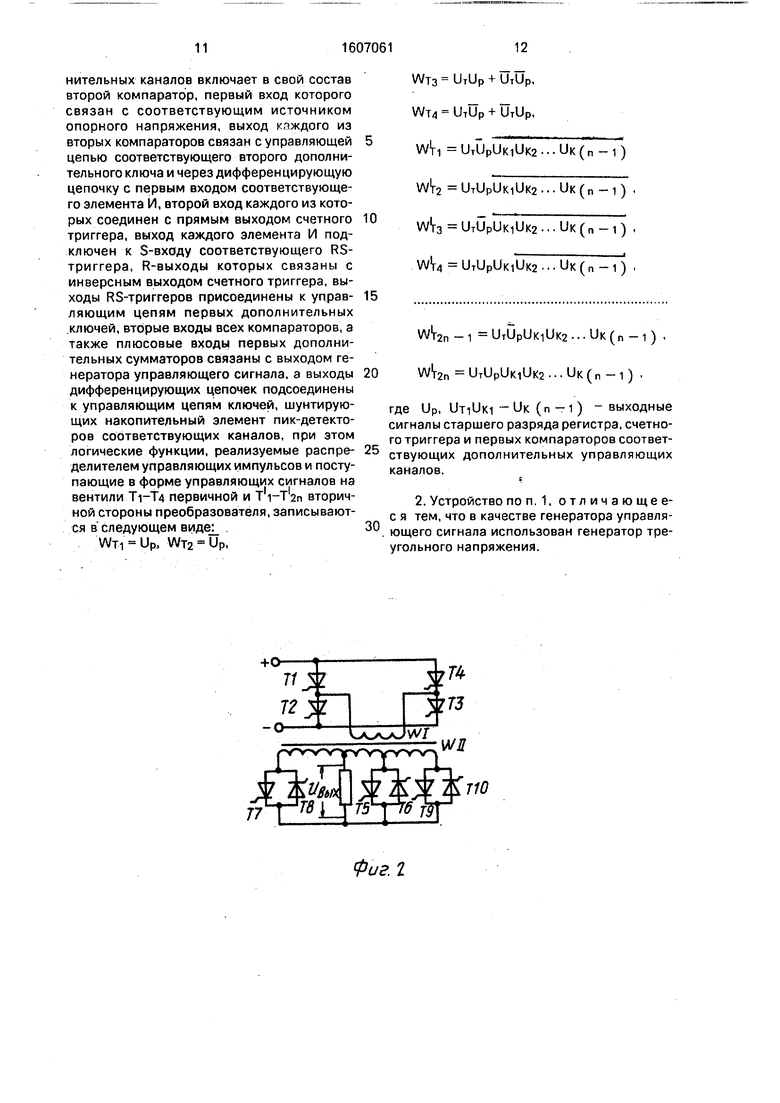

На фиг. 1 изображена функциональная схема устройства, (для приведенного варианта схемы т.е. на выходе преобразователя может формироваться трехуровневое напряжение с амплитудами выходных импульсов Ai, А2, АЗ; на фиг. 2 - силовая схема преобразователя: на фиг. 3, 4, 5, 6 - диаграммы напряжений.

Выходное напряжение преобразователя УВЫХ через усилитель 1 с нормированным коэффициентом передачи, обеспечивающим согласование по уровню выходного сигнала преобразователя с напряжением системы управления, поступает на плюсовой вход сумматора 2. Генератор 3 тактовых импульсов, частота следования которых определяет выходную частоту преобразователя, связан с цифровым генератором 4 управляющего сигнала и с делителем 5 частоты. Выходной сигнал генератора 4 поступает на минусовой вход сумматора, выход которого через логический инвертор 6 и двухпозиционный ключ 7 связан с интегратором 8, накопительный элемент (конденсатор) 9 которого зашунтирован управляемым ключом 10. Выход интегратора 8 присоединен к входам пороговых узлов 11 и 12, подключенных выходами к соответствующим входам счетного тригге ра 13 с раздельной установкой. Прямой выход триггера 13 связан с первым входом логического распределителя 14 управляющих импульсов. Второй вход распределителя 14 соединен с выходом старшего разряда двухразрядного регистра 15, выход младшего разряда которого связан с управляющей цепью ключа 7. Один выход делителя 5 частоты подсоединен к управляющей цепи ключа 10, другой выход делителя 5 связан с входом регистра. В состав устройства входят также два идентичных канала, каждый из которых состоит из двух цепей. Каналы содержат, в частности, по источнику 16 и 17 опорного напряжения, связанные соответственно с минусовыми входами сумматоров 18 и 19 и входами компараторов 20 и 21. Выходы сумматоров -18 и 19 через ключи 22 и 23 связан1 1 с входами пик-детекторов 24 и 25. Выходы компараторов 20 ц 21 через дифференцирующие цепочки 26 и 27 подключены к входам элементов И 28 и 29, на другие входы которых поступает сигнал с прямого выхода триггера 13. Выходы элементов 28 и 29 присоединены к S-входам RS-триггеров 30 и 31, выходы которых связаны с управляющими цепями ключей 22 и 23. Выходы пик-детекторов 24 и 25 подключены к сумматорам 32 и 33, другие входы которых связаны с источ0 никами 16 и 17, а выходы которых через ключи 34 и 35 подсоединены к входам компараторов 36 и 37. Вторые входы компараторов 20, 21, 36 и 37 связаны с выходом генератора 4 управляющего сигнала. Выхо5 ды компараторов 36 и 37 подключены к соответствующим входам распределителя 14 управляющих импульсов. Выходы компараторов 20 и 21 связаны с управляющими цепями ключей 34 и 35. R-входы триггеров 30

0 и 31 подключены к инверсному выходу триггера 13. Выходы дифференцирующих цепочек 26 и 27 присоединены к управляю1-цим цепям ключей 38 и 39, шунтирующих зарядные элементы (конденсаторы) 40 и 41 пик5 детекторов 24 и 25.

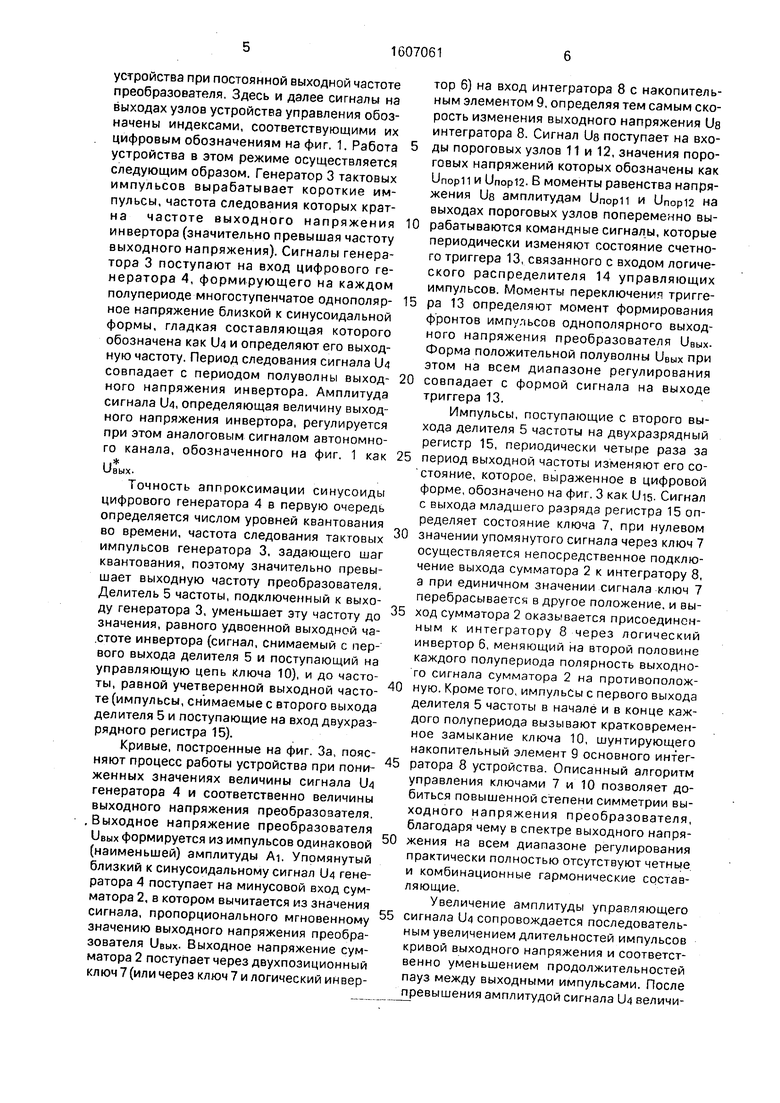

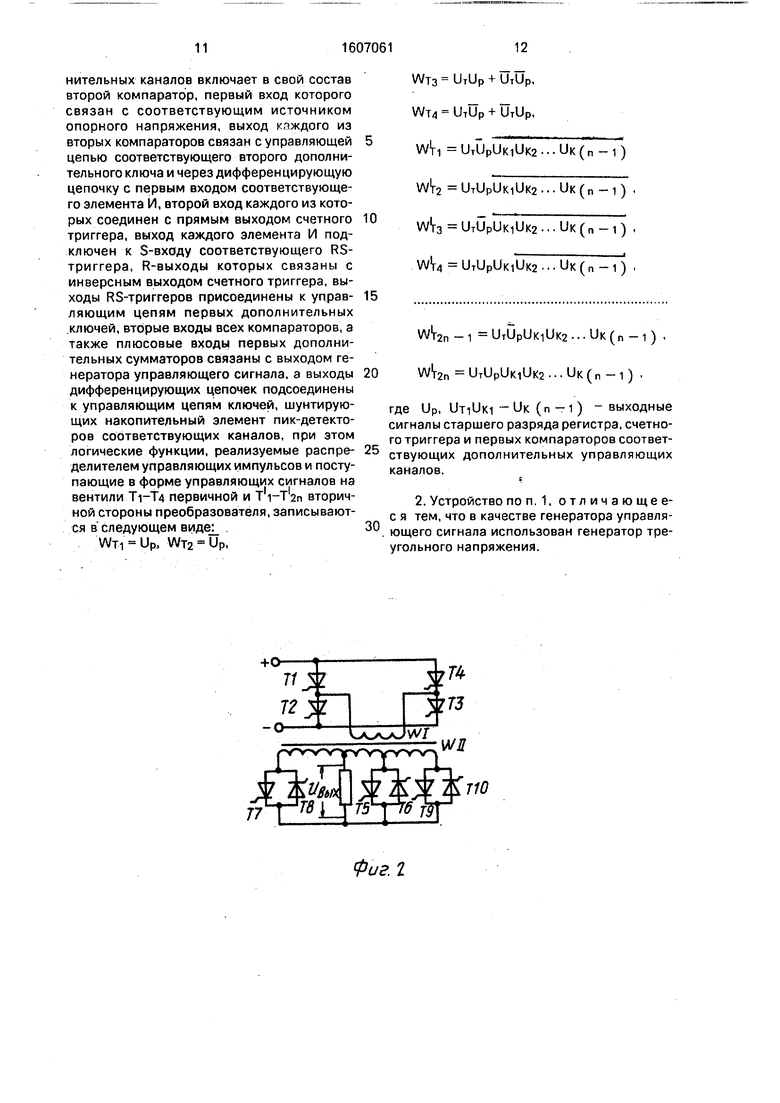

Одной из наиболее распространенных разновидностей силовых схем преобразователей с многоуровневым выходным напряжением является структура с силовым

0 секционированным на вторичной стороне трансформатором, упрощенный вариант которой применительно к данному случаю формирования трехуровневого выходного напряжения приведен на фиг. 2. В инвер5 торном блоке на первичной стороне трансформатора, нагрузкой которого служит первичная обмотка Wi осуществляется попеременное переключение накрест расположенных вентилей (Tl-Тз и Т2-Т4 0 все вентили преобразователя считаются полностью управляемыми), в результате чего схемой первичной стороны попеременно генерируются одноуровневые, импульсы обеих полярностей. Формирование много5 уровневого (трехуровневого) выходного напряжения Увых осуществляется при помощи соответствующих попеременигых, осуществляемых синхронно с работой вентилей TI-ТА переключений вентилей Ts-Tio, подсоеди0 ненных к соответствующим отводам секционированной вторичной обмотки Wii трансформатора. При этом наибольшая амплитуда (уровень) импульсов на нагрузке Аз - наблюдается при включении вентилей Тд и

5 Тю, импульсы с амплитудой Аа формируются при включении Ту и Та, импульсы с наименьшей амплитудой А при включении ТБ и Те.

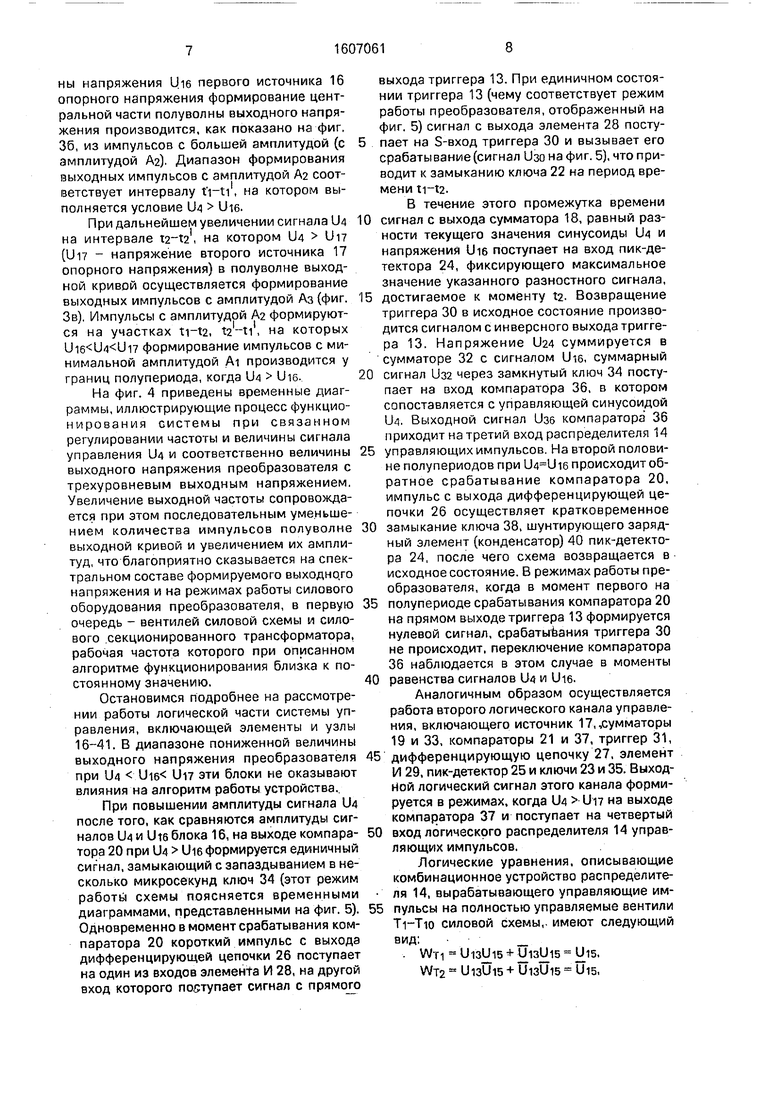

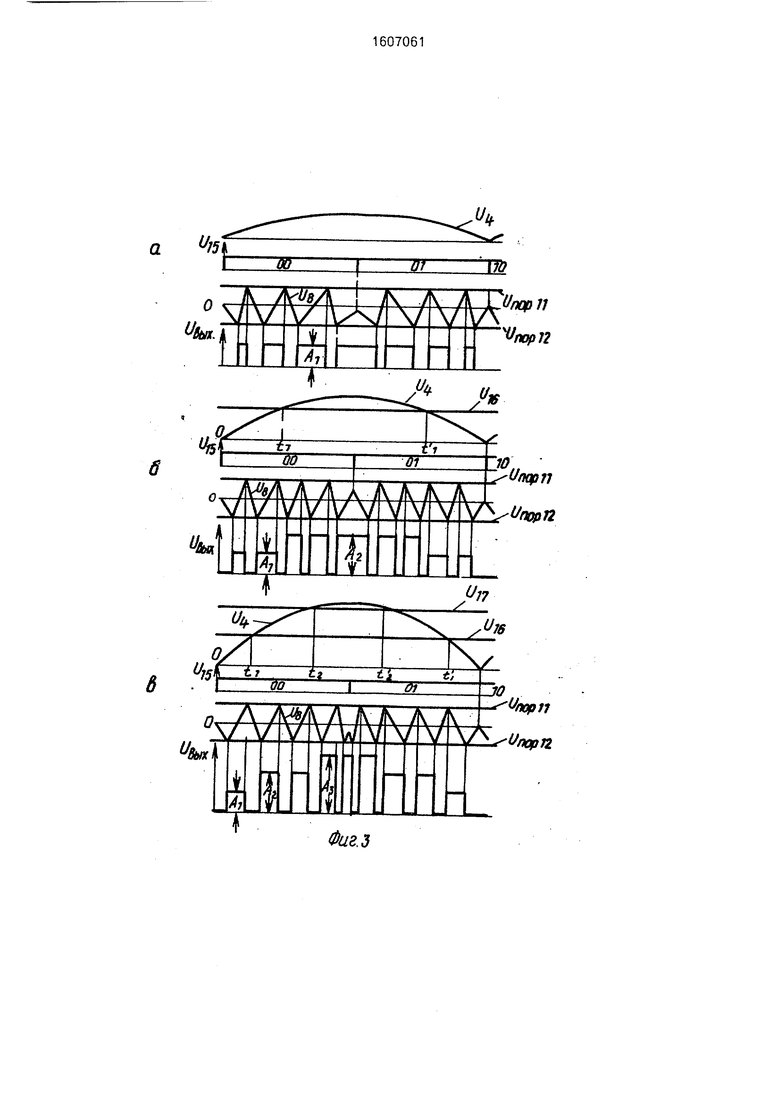

На фиг. 3 изображены временные диаграммы, иллюстрирующие принцип работы

устройства при постоянной выходной частоте преобразователя. Здесь и далее сигналы на выходах узлов устройства управления обозначены индексами, соответствующими их цифровым обозначениям на фиг 1 Работа устройства в этом режиме осуществляется следующим образом. Генератор 3 тактовых импульсов вырабатывает короткие импульсы, частота следования которых кратна частоте выходного напряжения инвертора (значительно превышая частоту выходного напряжения). Сигналы генератора 3 поступают на вход цифрового генератора 4, формирующего на каждом полупериоде многоступенчатое однополяр- ное напряжение близкой к синусоидальной формы, гладкая составляющая которого обозначена как U и определяют его выходную частоту. Период следования сигнала U4 совпадает с периодом полуволны выходного напряжения инвертора. Амплитуда сигнала UA, определяющая величину выходного напряжения инвертора, регулируется при этом аналоговым сигналом автономного канала, обозначенного на фиг. 1 как

UBBIX.

Точность аппроксимации синусоиды цифрового генератора 4 в первую очередь определяется числом уровней квантования во времени, частота следования тактовых импульсов генератора 3, задающего шаг квантования, поэтому значительно превышает выходную частоту преобразователя Делитель 5 частоты, подключенный к выходу генератора 3, уменьшает эту частоту до значения, равного удвоенной выходной ча- .стоте инвертора (сигнал, снимаемый с первого выхода делителя 5 и поступающий на управляющую цепь ключа 10), и до частоты равной учетверенной выходной частоте (импульсы, снимаемые с второго выхода делителя 5 и поступающие на вход двухпаз- рядного регистра 15).

Кривые, построенные на фиг. За поясняют процесс работы устройства при пониженных значениях величины сигнала U4 генератора 4 и соответственно величины выходного напряжения преобразователя Выходное напряжение преобразователя ивых формируется из импульсов одинаковой наименьшей) амплитуды AI. Упомянутый лизкий к синусоидальному сигнал U4 генеатора 4 поступает на минусовой вход суматора 2, в котором вычитается из значения игнала, пропорционального мгновенному начению выходного напряжения преобраователя ивь.х. Выходное напряжение суматора 2 поступает через двухпозиционный люч 7 (или через ключ 7 и логический инвер35

40

45

.-, 50

55

10

15

20

25

0

5

0

тор 6) на вход интегратора 8 с накопительным элементом 9, определяя тем самым скорость изменения выходного напряжения Us интегратора 8. Сигнал Us поступает на входы пороговых узлов 11 и 12, значения пороговых напряжений которых обозначены как Unopn и Unopi2. В моменты равенства напряжения U8 амплитудам Unopii и Unopi2 на выходах пороговых узлов попеременно вырабатываются командные сигнал ы, которые периодически изменяют состояние счетного триггера 13, связанного с входом логического распределителя 14 управляющих импульсов. Моменты переключения триггера 13 определяют момент формирования фронтов импульсов однополярного выходного напряжения преобразователя Увых Форма положительной полуволны Увых при этом на всем диапазоне регулирования совпадает с формой сигнала на выходе триггера 13.

Импульсы, поступающие с второго выхода делителя 5 частоты на двухразрядный регистр 15, периодически четыре раза за период выходной частоты изменяют его состояние, которое, выраженное в цифровой форме, обозначено на фиг. 3 как Ui5. Сигнал с выхода младшего разряда регистра 15 определяет состояние ключа 7, при нулевом значении упомянутого сигнала через ключ 7 осуществляется непосредственное подключение выхода сумматора 2 к интегратору 8 а при единичном значении сигнала ключ 7 перебрасывается в другое положение и выход сумматора 2 оказывается присоединенным к интегратору 8 через логический инвертор 6, меняющий на второй половине каждого полупериода полярность выходного сигнала сумматора 2 на противоположную. Кроме того, импульсы с первого выхода делителя 5 частоты в начале и в конце каждого полупериода вызывают кратковременное замыкание ключа 10, шунтирующего накопительный элемент 9 основного интегратора 8 устройства. Описанный алгоритм управления ключами 7 и 10 позволяет до- Ьиться повышенной степени симметрии выходного напряжения преобразователя благодаря чему в спектре выходного напряжения на всем диапазоне регулирования практически полностью отсутствуют четные и комбинационные гармонические составляющие.

Увеличение амплитуды управляющего сигнала U сопровождается последовательным увеличением длительностей импульсов кривой выходного напряжения и соответственно уменьшением продолжительностей пауз между выходными импульсами После превышения амплитудой сигнала U величины напряжения U.ie первого источника 16 опорного напряжения формирование центральной части полуволны выходного напряжения производится, как показано на фиг, 36, из импульсов с большей амплитудой (с амплитудой А2). Диапазон формирования выходных импульсов с амплитудой А2 соответствует интервалу t i-ti , на котором выполняется условие и Ui6.

При дальнейшем увеличении сигнала U4 на интервале на котором U4 Ui (Ui7 - напряжение второго источника 17 опорного напряжения) в полуволне выходной кривой осуществляется формирование выходных импульсов с амплитудой Аз (фиг. Зв). Импульсы с амплитудой А2 формируются на участках ti-t2, t2-ti, на которых формирование импульсов с минимальной амплитудой AI производится у границ полупериода, когда U4 Uie.

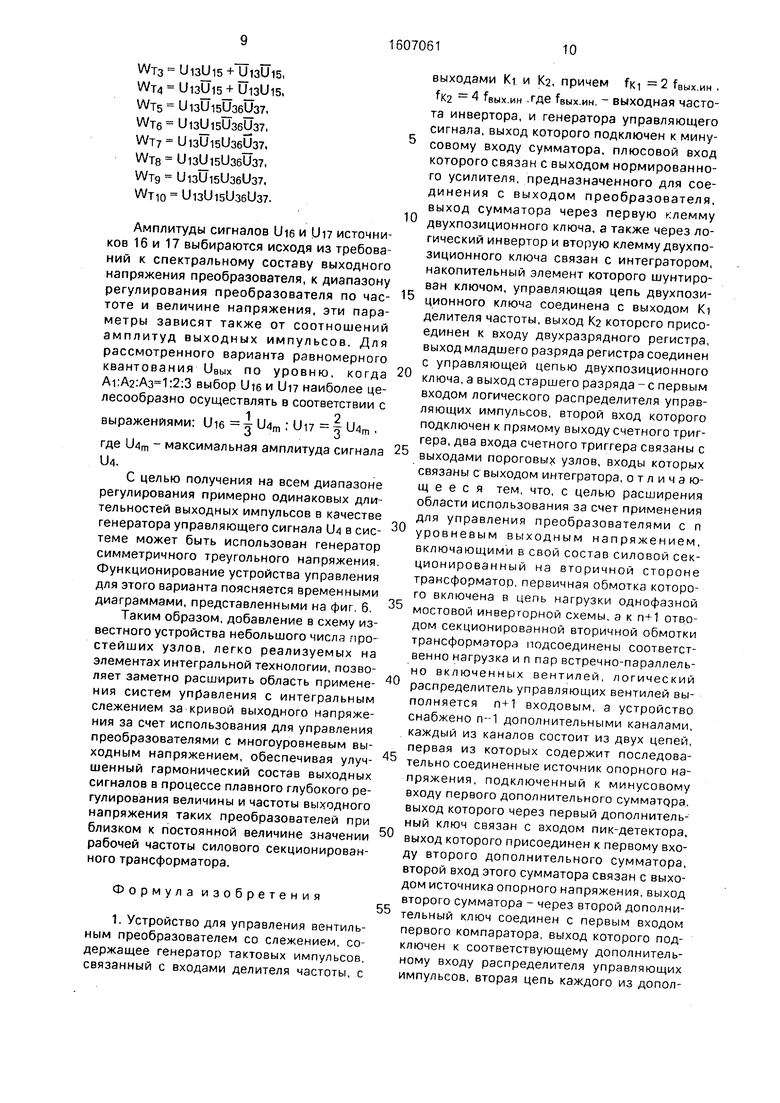

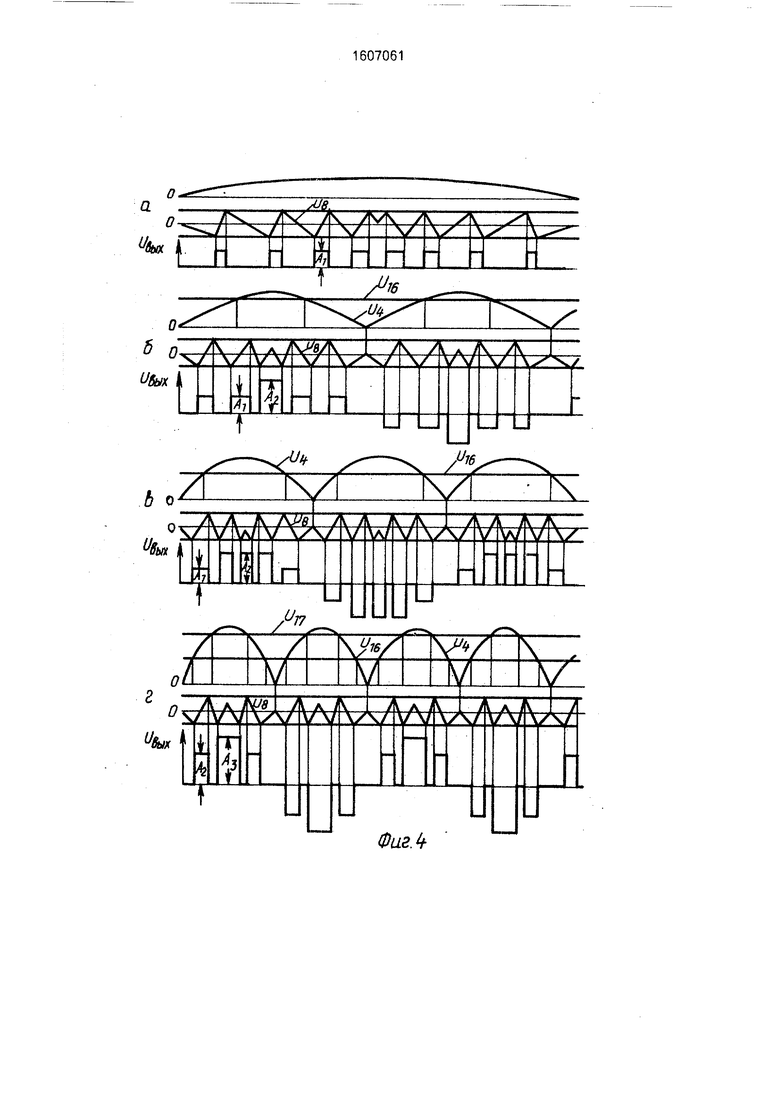

На фиг. 4 приведены временные диаграммы, иллюстрирующие процесс функцио- нирования системы при связанном регулировании частоты и величины сигнала управления U4 и соответственно величины выходного напряжения преобразователя с трехуровневым выходным напряжением. Увеличение выходной частоты сопровождается при этом последовательным уменьшением количества импульсов полуволне выходной кривой и увеличением их амплитуд, что благоприятно сказывается на спектральном составе формируемого выходно.го напряжения и на режимах работы силового оборудования преобразователя, в первую очередь - вентилей силовой схемы и силового .секционированного трансформатора, рабочая частота которого при описанном алгоритме функционирования близка к постоянному значению.

Остановимся подробнее на рассмотрении работы логической части системы управления, включающей элементы и узлы 16-41. В диапазоне пониженной величины выходного напряжения преобразователя при U4 Ui6 Ui7 эти блоки не оказывают влияния на алгоритм работы устройства..

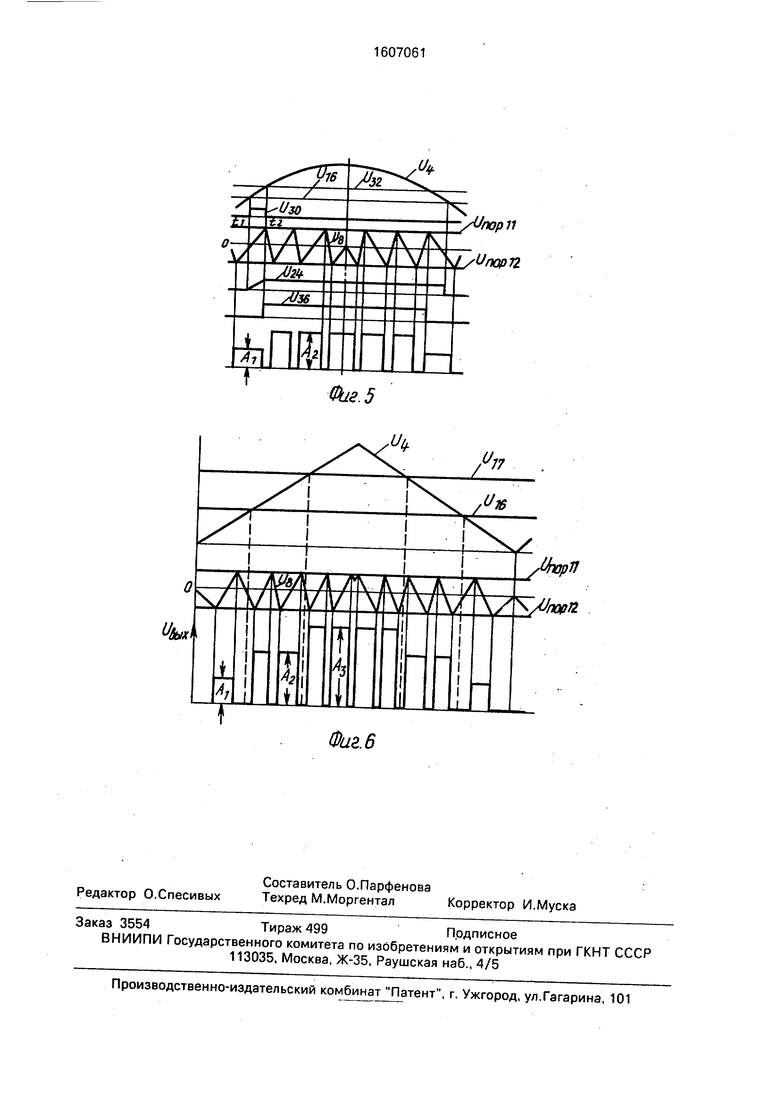

При повышении амплитуды сигнала U4 после того, как сравняются амплитуды сигналов U4 и Ut6 блока 16, на выходе компаратора 20 при U4 Ui6 формируется единичный сигнал, замыкающий с запаздыванием в несколько микросекунд ключ 34 (этот режим работы схемы поясняется временными диаграммами, представленными на фиг. 5). Одновременно в момент срабатывания компаратора 20 короткий импульс с выхода дифференцирующей цепочки 26 поступает на один из входов элeмeнta И 28, на другой вход которого поступает сигнал с прямо ю

выхода триггера 13. При единичном состоянии триггера 13 (чему соответствует режим работы преобразователя, отображенный на фиг. 5) сигнал с выхода элемента 28 посту- пает на S-вход триггера 30 и вызывает его срабатывание (сигнал Узо на фиг. 5), что приводит к замыканию ключа 22 на период времени t1-t2.

В течение этого промежутка времени 0 сигнал с выхода сумматора 18, равный разности текущего значения синусоиды U4 и напряжения Uie поступает на вход пик-детектора 24, фиксирующего максимальное значение указанного разностного сигнала, 5 достигаемое к моменту t2. Возвращение триггера 30 в исходное состояние производится сигналом с инверсного выхода триггера 13. Напряжение U24 суммируется в сумматоре 32 с сигналом Uie, суммарный 0 сигнал U32 через замкнутый ключ 34 поступает на вход компаратора 36, в котором сопоставляется с управляющей синусоидой U4. Выходной сигнал Узб компаратора 36 приходит на третий вход распределителя 14 5 управляющих импульсов. На второй половине полупериодов при происходит обратное срабатывание компаратора 20, импульс с выхода дифференцирующей цепочки 26 осуществляет кратковременное 0 замыкание ключа 38, шунтирующего зарядный элемент (конденсатор) 40 пик-детектора 24, после чего схема возвращается в исходное состояние. В режимах работы преобразователя, когда в момент первого на 35 полупериоде срабатывания компаратора 20 на прямом выходе триггера 13 формируется нулевой сигнал, срабатывания триггера 30 не происходит, переключение компаратора 36 наблюдается в этом случае в моменты 40 равенства сигналов U4 и Uie.

Аналогичным образом осуществляется работа второго логического канала управления, включающего источник 17,,сумматоры 19 и 33. компараторы 21 и 37, триггер 31, 45 дифференцирующую цепочку 27. элемент И 29, пик-детектор 25 и ключи 23 и 35. Выходной логический сигнал этого канала формируется в режимах, когда U4 Ui на выходе компаратора 37 и поступает на четвертый 50 вход логического распределителя 14 управляющих импульсов.

Логические уравнения, описывающие комбинационное устройство распределите- ля 14, вырабатывающего управляющие им- 55 пульсы на полностью управляемые вентили TI-TIO силовой схемы,, имеют следующий вид;

. WTI Ul3Ul5 + Ul3lJl5 IJ15. WT2 Ul3Ul5 + Ul3Ul5 Ul5,

WT3 Ul3Ul5 + Ul3Ul5, WT4 Ul3Ul5 +Ul3Ul5. WT5 Ul3Ul5U36U37, WT6 Ul3Ul5U36U37, WT7 Ul3Ul5U36U37. WT8 Ul3Ul5U36lJ37, Wtg Ul3Ul5U36U37. WTio Ul3Ul5U36U37.

Амплитуды сигналов Uie и .Ui7 источников 16 и 17 выбираются исходя из требований к спектральному составу выходного напряжения преобразователя, к диапазону регулирования преобразователя по частоте и величине напряжения, эти параметры зависят также от соотношений амплитуд выходных импульсов. Для рассмотренного варианта равномерного квантования Увых по уровню, когда Ai;A2:A3 1:2:3 выбор Ui6 и Ui7 наиболее целесообразно осуществлять в соответствии с

выражениями: Uie U ; Ui7 § , ,

где U4m - максимальная амплитуда сигнала U4.

С целью получения на всем диапазоне регулирования примерно одинаковых длительностей выходных импульсов в качестве генератора управляющего сигнала UA в системе может быть использован генератор симметричного треугольного напряжения Функционирование устройства управления для этого варианта поясняется временными диаграммами, представленными на фиг. 6

Таким образом, добавление в схему известного устройства небольшого числа простейших узлов, легко реализуемых на элементах интегральной технологии позволяет заметно расширить область применения систем управления с интегральным слежением за кривой выходного напряжения за счет использования для управления преобразователями с многоуровневым выходным напряжением, обеспечивая улучшенный гармонический состав выходных сигналов в процессе плавного глубокого регулирования величины и частоты выходного апряжения таких преобразователей при лизком к ПОСТОЯННОЙ величине значении абочей частоты силового секционированого трансформатора.

Формула изобретения

1. Устройство для управления вентильым преобразователем со слежением соержащее генератор тактовых импульсов вязанный с входами делителя частоты с

g gQ 55

выходами Кг и К2, причем fK, 2 fewx.MH , iK2 - 4 fflbix.MH .где fsbix.MH. - выходная частота инвертора, и генератора управляющего сигнала, выход которого подключен к минусовому входу сумматора, плюсовой вход которого связан с выходом нормированного усилителя, предназначенного для соединения с выходом преобразователя выход сумматора через первую клемму двухпозиционного ключа, а также через логический инвертор и вторую клемму двухпозиционного ключа связан с интегратором накопительный элемент которого шунтиро- ван ключом, управляющая цепь двухпозиционного ключа соединена с выходом Ki делителя частоты, выход К2 которого присоединен к входу двухразрядного регистра выход младшего разряда регистра соединен с управляющей цепью двухпозиционного ключа, а выход старшего разряда - с первым входом логического распределителя управляющих импульсов, второй вход которого подключен к прямому выходу счетного триг- 2g гера, два входа счетного триггера связаны с . выходами пороговых узлов, входы которых связаны с выходом интегратора, отличающееся тем, что, с целью расширения области использования за счет применения для управления преобразователями с п уровневым выходным напряжением включающими в свой состав силовой секционированный на вторичной стороне трансформатор, первичная обмотка которо- го включена в цепь нагрузки однофазной МОСТОВОЙ инверторной схемы, а к n+l отводом секционированной вторичной обмотки трансформатора подсоединены соответст- .венно нагрузка и п пар встречно-параллель- но включенных вентилей, логический распределитель управляющих вентилей выполняется п+1 входовым, а устройство снабжено п-1 дополнительными каналами каждый из каналов состоит из двух цепей первая из которых содержит последовательно соединенные источник опорного напряжения, подключенный к минусовому входу первого дополнительного сумматора выход которого через первый дополнитель- ныи ключ связан с входом пик-детектора выход которого присоединен к первому входу второго дополнительного сумматора второй вход этого сумматора связан с выхо- дом источника опорного напряжения, выход ,17°™ - ерез второй дополнительный ключ соединен с первым входом первого компаратора, выход которого подключен к соответствующему дополнительному входу распределителя управляющих импульсов, вторая цепь каждого из дополнительных каналов включает в свой состав второй компаратор, первый вход которого связан с соответствующим источником опорного напряжения, выход каждого из вторых компараторов связан с управляющей цепью соответствующего второго дополнительного ключа и через дифференцирующую цепочку с первым входом соответствующего элемента И, второй вход каждого из которых соединен с прямым выходом счетного триггера, выход каждого элемента И подключен к S-входу соответствующего RS- триггера, R-выходы которых связаны с инверсным выходом счетного триггера, выходы RS-триггеров присоединены к управ- ляющим цепям первых дополнительных .ключей, втЬрые входы всех компараторов, а также плюсовые входм первых дополнительных сумматоров связаны с выходом генератора управляющего сигнала, а выходы дифференцирующих цепочек подсоединены к управляющим цепям ключей, шунтирующих накопительный элемент пик-детекторов соответствующих каналов, при этом логические функции, реализуемые распре- делителем управляющих импульсов и поступающие в форме управляющих сигналов на вентили Т1-Т4 первичной и I l-j an вторичной стороны преобразователя, записываются в следующем виде . WTI Up. WT2 Up,

WT3 UrUp + UrUp,

WT4 UTUP + UiUp,

WVi UTUpUKiUK2...UK(n-l)

WV2 UTUpUKlUK2...UK(n-l)

wV3 UTUpUKiUK2...UK(n-i)

WV4 UTUpUKlUK2...UK(n-l)

W r2n-1 UTUpUKlUK2...UK(n-l) , WV2n UTUpUKiUK2...UK(n-l) ,

где Up, UTiUKi-UK (n-i) -выходные сигналы старшего разряда регистра, счетного триггера и первых компараторов соответствующих дополнительных управляющих каналов.

2. Устройство по п. 1, отличающее- с я тем, что в качестве генератора управля- . ющего сигнала использован генератор треугольного напряжения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Инфузионный насос | 1985 |

|

SU1279635A1 |

| Измеритель скорости звука | 1990 |

|

SU1758561A2 |

| Аналого-цифровой частотомер | 1988 |

|

SU1712894A1 |

| Устройство для управления мостовым инвертором со слежением за кривой выходного напряжения | 1984 |

|

SU1239810A1 |

| Устройство для управления регулируемым мостовым инвертором | 1988 |

|

SU1548830A1 |

| Устройство для управления трехфазным вентильным инвертором | 1988 |

|

SU1525845A1 |

| Устройство для управления автономным мостовым инвертором | 1987 |

|

SU1483575A1 |

| Асинхронный электропривод | 1989 |

|

SU1697252A1 |

| Устройство для управления регулируемым мостовым инвертором | 1987 |

|

SU1432699A1 |

| Устройство для измерения скорости звука | 1987 |

|

SU1474538A1 |

Изобретение относится к преобразовательной технике. Целью изобретения является расширение области применения. Устройство, осуществляющее интегральное слежение на кривой выходного напряжения, включает в свой состав нормированный усилитель 1, сумматор 2, генераторы тактовых импульсов 3 и управляющего сигнала 4, делитель частоты 5, логический инвертор 6, двухпозиционный ключ 7 и основной интегратор системы 8. Выход интегратора 8 присоединен ко входам пороговых узлов 11 и 12, подключенных ко входам счетного триггера. Выход триггера 13 связан с основным входом логического распределителя управляющих импульсов 14. Включение в состав устройства дополнительных каналов, количество которых на единицу меньше максимального числа однополярных уровней кривой формируемого напряжения, позволяет реализовать принцип слежения в широкорегулируемых преобразователях с многоуровневыми формами выходного напряжения, характеризующихся улучшенным гармоническим составом выходных сигналов. 1 з.п. ф-лы, 6 ил.

77

У Td

Фиг. г

%

6

Фиг.з

порп

nopii

Т Опорп

XZ

z

А

iJSbix 1

Т

V

хХЧ./

Фиг. 5

Фиг. В

y nopii

(у ПОР 12

7 /UnopJi

| Олещук В.И. | |||

| Чаплыгин Е.Е | |||

| Вентильные преобразователи с замкнутым контуром управления | |||

| Кишинев: Штиинца, 1980, С | |||

| Устройство для управления регулируемым инвертором напряжения | 1984 |

|

SU1246296A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1990-11-15—Публикация

1988-09-28—Подача