(21)4115616/24-21

(22)25.06.86

(46) 23.04.88„ Вкш. № 15

(72) B.C. Осетров н Г.Е. Никулин

(53) 621.317(088.8)

(56) Авторское свидетельство СССР

№ 840766, кл. G 01 R 27/18, 1979.

Авторское свидетельство СССР 1176265, кл. С 01 R 27/18, 1983.

го

(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ СОПРОТИВЛЕНИЯ ИЗОЛЯЦИИ ЭЛЕКТРИЧЕСКИХ СЕТЕЙ ПОСТОЯННОГО ТОКА

(57) Изобретение относится к электроизмерительной технике и может быть использовано для измерения эквивалентного сопротивления изоляции электрических сетей постоянного тока под напряжением. Изобретение сокра(Л

со со

о

СП

4

Фиг.

ж2

{921

щает время измерений, что достигается в результате автоматического дифференцирования во BpeMefrti измеряемого сопротивления изоляции. Устройство содержит полюса сети 1, ключи 2,3, 10,11,12,13 и 17, шунтирующий резистор 4, запоминающие элементы 5-8, сумматор 9, переменный резистор 14, нуль-орган 15, усилитель-ограничитель индикатор 18 неисправного полюса сети, блок 19 управления, блок 20 диф1390574

ференцлрования, шину 21 запуска, блок 22 выборки-хранения, делитель 23 напряжения и компаратор 24 напряжения, В предложенном устройстве время измерений каждой цепи зависит от длительности ее конкретных переходных процессов, что существенно уменьшает время измерений сопротивления изоляции для сетей с емкостью изоляции меньше максимальной. 1 з.п. ф-лы, 3 ил.

Изобретение относится к электроизмерительной технике и может быть использовано для измерения эквивалентного сопротивления изоляции электрических сетей постоянного тока под напряжением.

Цель изобретения - сокращение времени измерений путем автоматического дифференцирования во времени измеряемого сопротивления изоляции.

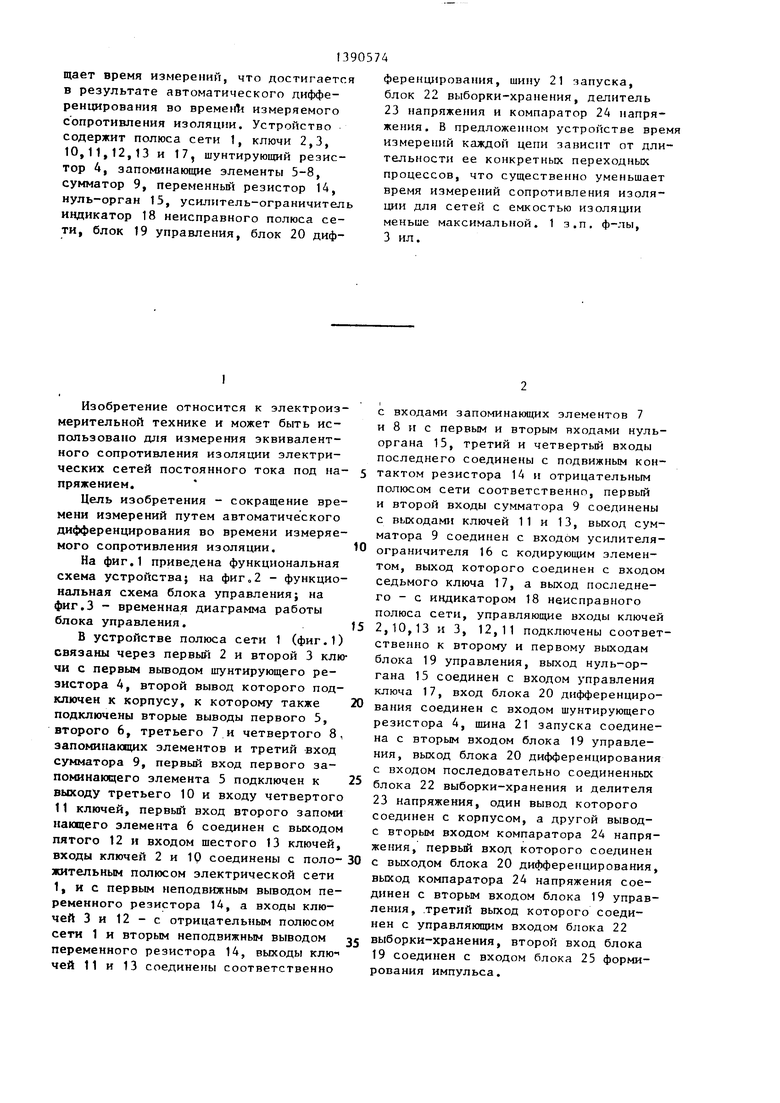

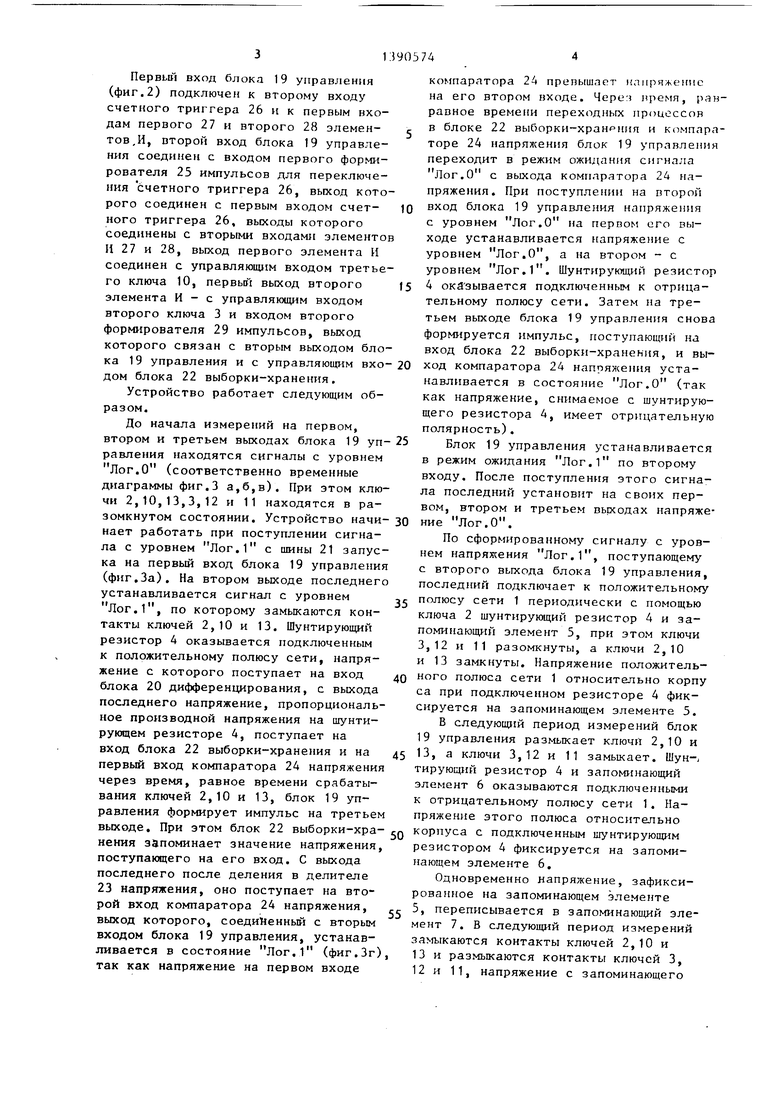

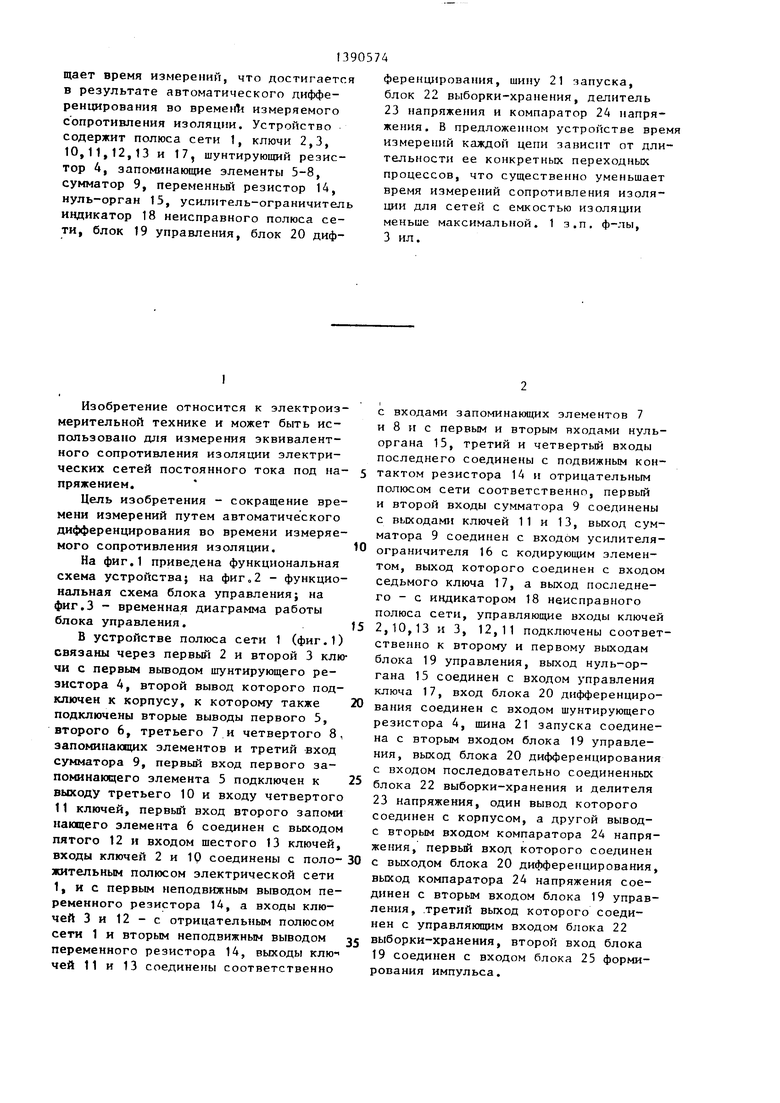

На фиг.1 приведена функциональная схема устройства; на фиг„2 - функциональная схема блока управления; на фиг.З - временная диаграмма работы блока управления.

В устройстве полюса сети 1 (фиг.1) связаны через первый 2 и второй 3 клю чи с первым вьшодом шунтирующего резистора 4, второй вывод которого подключен к корпусу, к которому также подключены вторые выводы первого 5, второго 6, третьего 7 и четвертого 8, запоминакщих элементов и третий вход сумматора 9, первый вход первого запоминающего элемента 5 подключен к выходу третьего 10 и входу четвертого 11 ключей, первьп вход второго запоми нающего элемента 6 соединен с выходом пятого 12 и входом шестого 13 ключей, входы ключей 2 и 10 соединены с поло- жительным полюсом электрической сети 1, и с первым неподвижным выводом переменного резистора 14, а входы ключей 3 и 12 - с отрицательным полюсом сети 1 и вторым неподвижным выводом переменного резистора 14, выходы клю- чей 11 и 13 соединены соответственно

0

5

0 s

0

5

с входами запоминающих элементов 7 и 8 и с первым и вторым входами нуль- органа 15, третий и четвертый входы последнего соединены с подвижным контактом резистора 14 и отрицательным полюсом сети соответственно, первый и второй входы сумматора 9 соединены с выходами ключей 11 и 13, выход сумматора 9 соединен с входом усилителя- ограничителя 16 с кодируюгцим элементом, выход которого соединен с входом седьмого ключа 17, а выход последнего - с индикатором 18 неисправного полюса сети, управляющие входы ключей 2,10,13 и 3, 12,11 подключены соответственно к второму и первому выходам блока 19 управления, выход нуль-органа 15 соединен с входом управления ключа 17, вход блока 20 дифференцирования соединен с входом шунтирующего резистора 4, шина 21 запуска соединена с вторым входом блока 19 управления, выход блока 20 дифференцирования с входом последовательно соединенных блока 22 выборки-хранения и делителя 23 напряжения, один вывод которого соединен с корпусом, а другой вывод- с вторым входом компаратора 24 напряжения, первый вход которого соединен с выходом блока 20 дифференцирования, выход компаратора 24 напряжения соединен с вторым входом блока 19 управления, .третий выход которого соединен с управляющим входом блока 22 выборки-хранения, второй вход блока 19 соединен с входом блока 25 формирования импульса.

riepBLtti вход блока 19 управления (фиг.2) подключен к второму входу счетного триггера 26 и к первым входам первого 27 и второго 28 элемен- тов,И, второй вход блока 19 управления соединен с входом первого формирователя 25 импульсов для переключения счетного триггера 26, выход которого соединен с первым входом счет- ного триггера 26, выходы которого соединены с вторыми входами элементов И 27 и 28, выход первого элемента И соединен с управляющим входом третьего ключа 10, первый выход второго элемента И - с управляющим входом второго ключа 3 и входом второго формирователя 29 импульсов, выход которого связан с вторым выходом блока 19 управления и с управляющим входом блока 22 выборки-хранения.

Устройство работает следующим образом.

До начала измерений на первом, втором и третьем выходах блока 19 управления находятся сигналы с уровнем Лог.О (соответственно временные диаграммы фиг.З а,б,в). При этом ключи 2,10,13,3,12 и 11 находятся в разомкнутом состоянии. Устройство начи- нает работать при поступлении сигнала с уровнем Лог.1 с шины 21 запуска на первый вход блока 19 управления (фиг.За). На втором выходе последнего устанавливается сигнал с уровнем Лог.1, по которому замьпсаются контакты ключей 2,10 и 13. Шунтирующий резистор А оказывается подключенным к положительному полюсу сети, напряжение с которого поступает на вход блока 20 дифференцирования, с выхода последнего напряжение, пропорциональное производной напряжения на шунтирующем резисторе 4, поступает на вход блока 22 выборки-хранения и на первый вход компаратора 24 напряжения через время, равное времени срабатывания ключей 2,10 и 13, блок 19 управления формирует импульс на третьем выходе. При этом блок 22 выборки-хра- нения запоминает значение напряжения, поступающего на его вход. С выхода последнего после деления в делителе 23 напряжения, оно поступает на второй вход компаратора 24 напряжения, выход которого, соедиНенньш с вторым входом блока 19 управления, устанавливается в состояние Лог.1 (фиг.Зг) так как напряжение на первом входе

компаратора 24 препышает нлиряженис на его втором входе. Чере:; иремл, ран равное времени переходных процессов в блоке 22 выборки-хранения и компараторе 24 напряжения блок 19 управления переходит в режим ожидания сигнала Лог.О с выхода компаратора 24 напряжения. При поступлении на второй вход блока 19 управления напряжения с уровнем Лог.О на первом его выходе устанавливается напряжение с уровнем Лог.О, а на втором - с уровнем Лог.Г. Шунтируюид1й резистор 4 окЯ зывается подключенным к отрицательному полюсу сети. Затем на третьем выходе блока 19 управления снова формируется импульс, поступающий на вход блока 22 выборки-хранения, и выход компаратора 24 наппян ения устанавливается в состояние Лог.О (так как напряжение, снимаемое с шунтирующего резистора 4, имеет отрицательную полярность).

Блок 19 управления устанавливается в режим ожидания Лог.1 по второму входу. После поступления этого сигнала последний установит на своих первом, втором и третьем вькодах напряжение Лог.О.

По сформированному сигналу с уровнем напряжения Лог.1, поступающему с второго выхода блока 19 управления, последний подключает к положительному полюсу сети 1 периодически с помощью ключа 2 щунтирующий резистор 4 и запоминающий элемент 5, при этом ключи 3,12 и 11 разомкнуты, а ключи 2,10 и 13 замкнуты. Напряжение положительного полюса сети 1 относительно корпу са при подключенном резисторе 4 фиксируется на запоминающем элементе 5. В следующий период измерений блок 19 управления размыкает ключи 2,10 и 13, а ключи 3,12 и 11 замыкает. Шун-j тирующий резистор 4 и запоминающий элемент 6 оказываются подключенными к отрицательному полюсу сети 1. Напряжение этого полюса относительно корпуса с подключенным шунтирующим резистором 4 фиксируется на запоминающем элементе 6.

Одновременно напряжение, зафиксированное на запоминающем элементе 5, переписывается в запоминающий элемент 7. В следующий период измерений замыкаются контакты ключей 2,10 и 13 и размыкаются контакты ключей 3, 12 и 11, напряжение с запоминающего

139

в ЗсЯГГОМИэлемента 6 переписывается паюций элемент 8.

После каждого этапа коммутации на первые два входа нуль-органа 15 пос- тупает сумма напряжений U, и U, при этом на третий и четвертый его входы с переменного,резистора 14 подается опорное напряжение, соответствующее пороговому значению эквива- лентиого сопротивления изоляции. Для контроля эквивалентного сопротивления изоляции достаточно сравнивать сумму напряжений с опорным напряжением и„ .

Одновременно на входы сумматора 9 подаются напряжения с запоминающих элементов 7 и 8, Сумматор 9 производит сложение абсолютных величин этих

напряжений, что равносильно вычитанию 20 полюсу сети является причиной возник

модулей значений этих напряжений. Результат поступает на усилитель-ограничитель 16 с кодирующим элементом, который производит усиление с ограничением выходного сигнала сумматора 9 и преобразует уровни напряжений на сыщения в напряжения, соответствующие Лог.1 и О, которые поступают на вход индикатора 18 неисправного полюса сети через ключ 17, и индика- Тора 18 неисправного полюса сети че-- рез ключ 17, и индикатор 18 неисправного полюса сети указывает, какой из полюсов сети 1 имеет меньшее сопротивление изоляции.

В блоке 19 управления в начальный момент времени до начала измерений на его первый вход поступает сигнал с уровнем Лог.О и подается на первые входы элементов И 27 и 28 и на второй вход счетного триггера 26 - вход сброса. На выходах элементов И 27 и 28 формируется сигнал с уровнем Лог.О, т.е. осуществляется блокировка блока 19 управления. Последняя снимается при подаче на первый вход блока 19 управления сигнала начала измерений с уровнем Лог.1, на первом выходе счетного триггера 26 формируется сигнал с уровнем Лог.1, на втором - сигнал с уровнем Лог.О.

Во время измерений блок 19 управления осуществляет управление счетным триггером 26, при этом на его первом и втором выходах формируются сигналы, тождественные сигналам, поступающим с второго и первого выходов блока 19 управления.

Счетньп триггер 26 переходит в другое устойчивое состояние при поступление на его вход переднего фронта импульса, формируемого блоком 25 формирования импульса для переключения счетного триггера. Указанный импульс появляется на вьгходе последнего для переключения счетного триггера после окончания переходного процесса на шунтирующем резисторе 4 и формируется из выходного сигнала компаратора 24 напряжения, поступающего на второй вход блока 19 управления.

Формирователь 29 импульсов с задержкой осуществляет формирование импульса из сигналов элемента И 27.

Подключение шунтирующего резистора к положительному или отрицательному

0

5

новения переходных процессов в рассматриваемом устройстве При этом i. временная зависимость напряжения на шунтирующем резисторе имеет вид: t

U(t) А + Be , (1)

где А - установившееся значение напряжения на шун1 :рующем ре- зисторе;

В - параметр переходного процесса, представляющий собой разность напряжений в момент включения шунтирующегд резистора и его установившегося значения; Г - постоянная времени электрической сети.

Параметры А,В и t переходного процесса (1) зависят от величин емкости и сопротивлений изоляции полюсов сети относительно корпуса и величины шунтирующего резистора. Для контроля сопротивления изоляции необходимо определить только параметр А. Для этого измерение напряжения на шунтирующем резисторе проводят после окончания переходного процесса, т.е. когда членом Bg можно пренебречь.

Однако так как длительность переходного процесса неизвестна, необходимо в устройстве для контроля сопротивления изоляции электрических сетей ее определить. Для этого с помощью блока дифференцирования находит- 5 ся производная U(t) от переходного процесса U(t):

5

0

5

0

U(t)

В - г

(2)

По величине производной оггределя- ют время измерений следующим образом. В блоке выборки-хранения загтоминан1т

R

значение 0(0)-;

и сравнивают это

значение, поделенное в заданное чис раз (к) делителем напряжения, с текщим значением производной IJ(t).

Измерение установившегося значен напряжения осуществляется я момент времени t, до совпадения указанных величин, т.е. когда

U(t,) и(0):(3)

Нз (3) следует, что при измерениях t

е - , Тем самым обеспечивается К

режим измерений, при котором можно пренебречь вторым слагаемым в (1). Величина К задается до проведения имерений и определяет точность порог при контроле.

В устройстве время измерений каждой цепи зависит от длительности ее конкретных переходных процессов, чт позволяет существенно уменьшить вре

измерений сопротивлений изoляlI и для сетей с емкостью изоляции, меньшей максимальной.

Формула изобретения

что, с

HtMiHbiG третий и leiTM pTt.rii ключи г по- 1ож:итрлтл{ым полюсом кпитро.чируемой сети и с пторым прлводпм третг.ет о за- nfuniFtarouif-ro члемента, )1и1й вход череп последоватр.ш.нп соединенные пя- Tbii i и шестой ключи - с отрицательным контролируемой сети и с вто- PLM пмподом четвертого запоминающег о элемента, другоГ неподвижный вывод переменного резистора соединен с по- ложителы11,1м полюсом сети, вторые выводы первого и второго запоминающих э.чементоп соединены соответственно с в,1ходами пятого и третьего ключей, управляющие входы второго, четвертого и пятого ключей соединены между собой, управляюпи е входы первого, третьего и шестого ключей соединены между собой, управляющий вход седьмого ключа подключен к выходу нуль-органа, входы сумматора соединены соответственно с нькодами четвертого и шестого ключей, выход сумматора соединен через последовательно соединенные усилитель-ограничитель с кодирую- цим элементом и седьмой ключ - с входом индикатора неисправного полюса сети, отличающеес я тем, целью сокращения времени изме- в него введены делитель напрярепии.

40

45

50

55

жения, компаратор, блок дифференцирования и блок выборки-хранения, при этом вход блока дифференцирования соединен с первым выводом щунтирующего резистора, а выход через последовательно соединенные блок выборки- хранения, делитель напряжения - с BTopi.iM входом компаратора и соединен с первым входом компаратора, выход которого подключен к второму входу блока управления, третий выход которого соединен с управляющим входом блока выборки-хранения.

Авторы

Даты

1988-04-23—Публикация

1986-06-25—Подача