Известны накапливающие десятичные сумматоры для двоично-десятичного кода 8421, применяемые в числительных устройствах и дискретной автоматике последовательного действия. Они содержат четыре двоичных полусумматора, устройство исправления результата и устройство хранения переноса в накапливающий десятичный сумматор старшего разряда.

При сложении двух десятичных чисел в коде 8421 результат сложения двух десятичных цифр необходимо исправить, если он превышает девять (т.е. равен 10-15), путем прибавления числа шесть в двоичном коде. Известные десятичные сумматоры для двоично-десятичного кода громоздки по оборудованию; исправление результата возможно после формирования всех четырех двоичных цифр, представляющих десятичную цифру-сумму, и цифры переноса в старший десятичный разряд. Таким образом, для исправления результата необходимо дополнительное время, дополнительные такты.

Предложенный сумматор отличается от известных тем, что в устройстве исправления результата, выполненном на двух динамических элементах, например феррит-диодных, вход первого элемента соединен с выходами устройств формирования цифры суммы второго и третьего полусумматоров, а выход через вход второго магнитного динамического элемента соединен с цепью управляющего ключа устройства формирования цифры суммы четвертого полусумматора; второй вход второго магнитного динамического элемента соединен с выходом устройства хранения переноса в старший десятичный разряд, а выход второго магнитного динамического элемента соединен через цепь управляющего ключа с одним из входов второго и третьего полусумматоров.

В полусумматоре вход магнитного динамического элемента соединен через цепь управляющего ключа с выходом второго динамического элемента, а к выходу второго динамического элемента подключена дополнительная нагрузка.

В предлагаемом десятичном сумматоре каждый двоичный полусумматор содержит пять феррит-диодных элементов и два полупроводниковых ключа, а схема исправления результата построена лишь на двух феррит-диодных элементах. Таким образом, с помощью предлагаемого сумматора можно решить одну из важнейших задач - уменьшить количество оборудования и тем самым размеры арифметического устройства, которое является основной частью любого вычислительного устройства и многих устройств дискретной автоматики последовательного действия.

В предлагаемом сумматоре, кроме того, исправление результата начинается еще до окончания процесса сложения двух десятичных цифр, и окончание исправления совпадает с окончанием формирования всех четырех цифр двоичной суммы - десятичной цифры. Таким образом, для исправления результата не требуется особое время, благодаря чему значительно сокращается общее время сложения двух десятичных цифр. Это позволяет решить другую важнейшую задачу при рассмотрении вычислительных и автоматических устройств последовательного действия - повышение их быстродействия без увеличения количества оборудования.

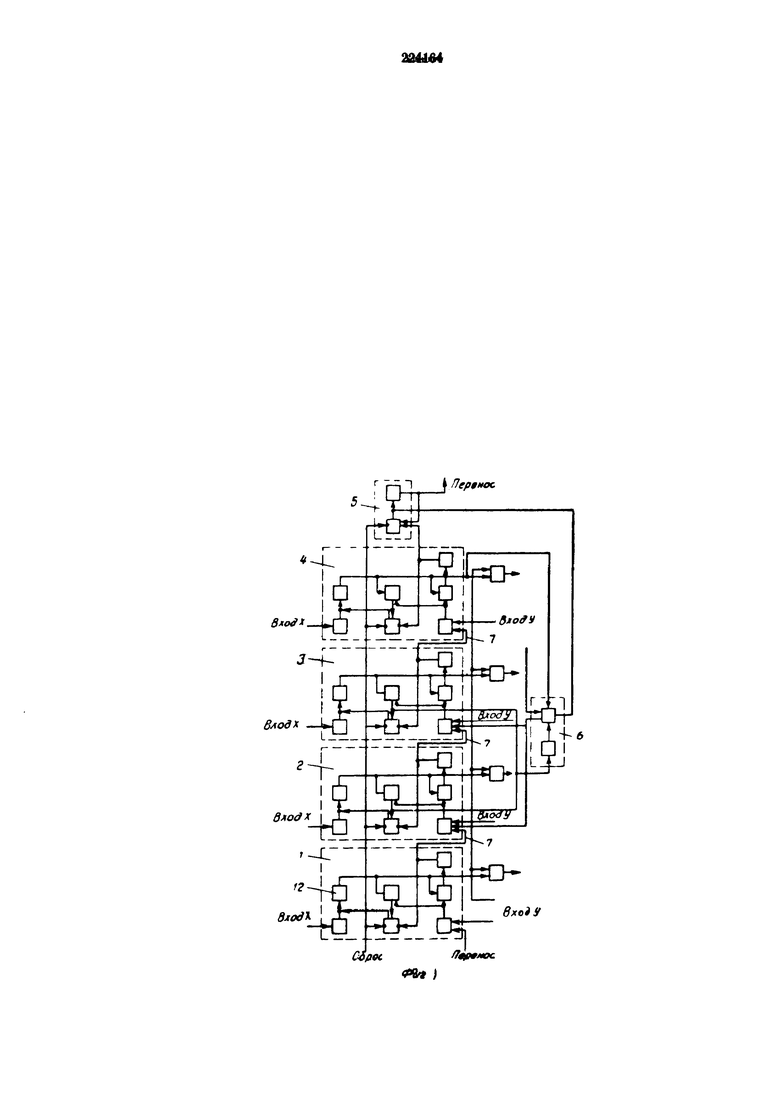

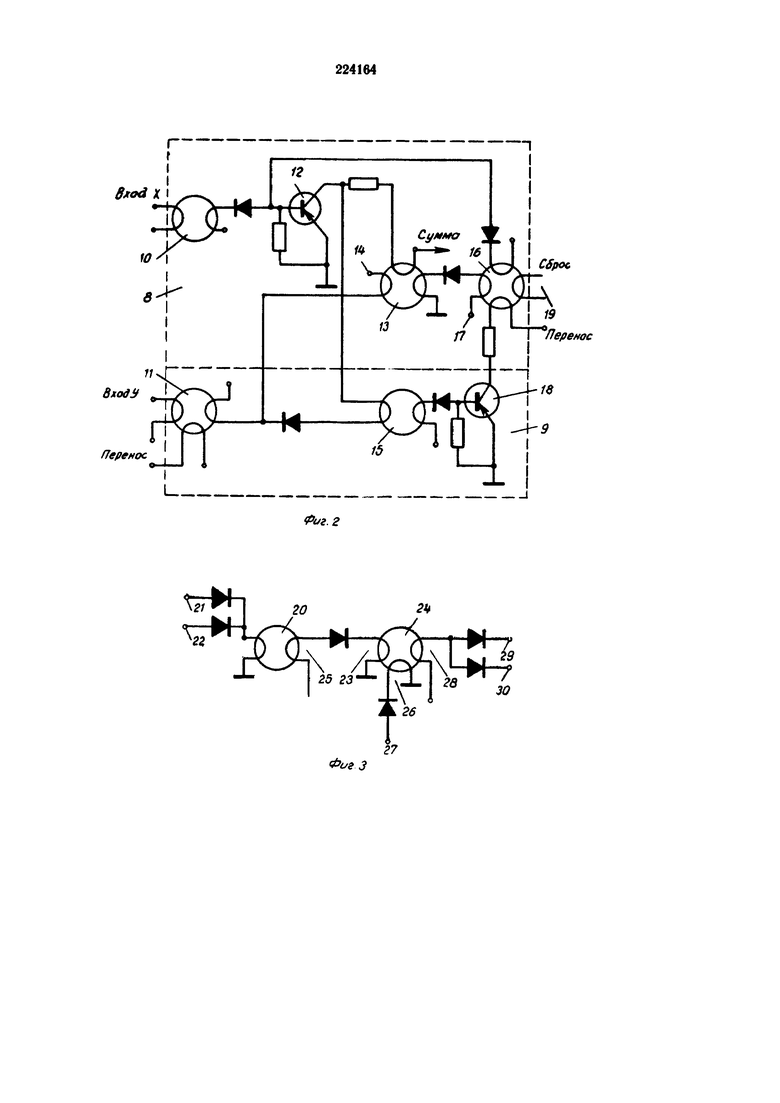

На фиг. 1 изображена блок-схема накапливающего десятичного сумматора для двоично-десятичного кода, например для кода 8421, на феррит-диодных элементах с полупроводниковыми управляющими ключами; на фиг. 2 - принципиальная схема двоичного полусумматора на феррит-диодных элементах с полупроводниковыми управляющими ключами; на фиг. 3 - принципиальная схема устройства исправления результата на феррит-диодных элементах.

На фиг. 1 пунктиром обведены двоичные полусумматоры 1-4 - соответственно первый, второй, третий, четвертый, начиная с младшего разряда; динамический триггер 5 хранения переноса в старший десятичный разряд; схема 6 исправления результата. Двоичные полусумматоры связаны между собой цепями 7 переноса из младшего двоичного разряда в старший. Входы х и у каждого полусумматора, выходы всех четырех разрядов суммы, шины сброса полусумматоров, выдачи суммы, разрешения исправления, переноса из младшего десятичного разряда и переноса в старший десятичный разряд соединены с соответствующими цепями вычислительного устройства, в состав которого входит сумматор.

На фиг. 2 пунктиром обведены две части, из которых (состоит каждый двоичный полусумматор: схема 8 образования суммы и схема 9 образования переноса. Полусумматоры содержат ферритовые импульсные трансформаторы 10 и 11, на входы которых поступают двоичные слагаемые х и у, полупроводниковый усилитель 12 - ключ суммы, импульсный трансформатор 13, с помощью которого реализуется логическая функция «ИЛИ», шину 14 управляющего ключа первого такта вычислительного устройства, ферритовый импульсный трансформатор 15, с помощью которого реализуется логическая функция «И», ферритовый импульсный трансформатор 16, с помощью которого реализуется логическая функция «И-НЕ», шину 17 управляющего ключа второго такта вычислительного устройства, полупроводниковый триод 18 - ключ переноса, обмотку сброса 19. Каждый двоичный полусумматор связан с полусумматорами старшего и младшего двоичных разрядов с помощью шин переноса. Кроме того, тактовые обмотки всех импульсных трансформаторов полусумматоров (эти обмотки на фиг. 2 не показаны) соединены с тактовой цепью всего вычислительного устройства.

Устройство исправления результата (фиг. 3) содержит первый феррит-диодный элемент с двумя входами 21 и 22, соединенными со схемой образования суммы второго 2 и третьего 3 полусумматоров; первую входную обмотку 23 импульсного трансформатора 24 второго феррит-диодного элемента, выходную обмотку 25 трансформатора 20, соединенную с цепью управляющего ключа 12 четвертого полусумматора 4; вторую входную обмотку 26 импульсного трансформатора 24, которая через диод соединена с коллектором 27 управляющего ключа динамического триггера 5 хранения переноса в старший десятичный разряд; выходную обмотку 28 импульсного трансформатора 24, соединенную со входом 29 второго полусумматора 2 и со входом 30 третьего полусумматора 3, а также с шиной разрешения исправления из соответствующей цепи всего вычислительного устройства, в состав которого входит сумматор; тактовые обмотки обоих импульсных трансформаторов (эти обмотки на фиг. 3 не показаны) соединены с тактовой цепью всего вычислительного устройства.

Полусумматор работает следующим образом (см. фиг. 2).

Двоичные цифры слагаемых х и у поступают в момент t0 на обмотки записи трансформаторов 10 и 11. Тактовым импульсом первого такта, поступающим в момент t1, информация считывается с этих трансформаторов. Выходной сигнал с трансформатора 10, если в нем была записана единица, открывает управляющий полупроводниковый ключ суммы 12. Выходной сигнал с трансформатора 11, если в нем была записана единица, перезаписывает ее в трансформатор 13, так как синхронно с тактовым импульсом первого такта открывается ключевая шина М этого такта. Перепись единицы из трансформатора 11 в трансформатор 15 происходит лишь в том случае, если открыт управляющий ключ 12. Трансформатор 13 имеет вторую обмотку записи, куда записывается единица, когда открывается ключ 12.

Таким образом, в момент t1 в трансформатор 15 записывается значение двоичной логической функции совпадения F1 («И») двух двоичных переменных (х и у). F1=x∧y. В тот же момент t2 в трансформаторе 13 записывается значение двоичной логической функции «ИЛИ» (F2) двух двоичных переменных х и у. F2=x∨y. В момент t2 действия тактового импульса второго такта выходной импульс с трансформатора 13 переписывает единицу в трансформатор 16. При этом синхронно с тактовым импульсом второго такта открывается ключевая шина 17 второго такта. Одновременно с этим выходной импульс с трансформатора 15 открывает полупроводниковый триод 18 запрета записи в трансформатор 16. Таким образом, в момент t2 в трансформаторе 16 записывается значение двоичной суммы двух двоичных слагаемых одноименных разрядов

где S - двоичная сумма двух разрядов; х, у - двоичные слагаемые; х и у - инверсии двоичных слагаемых.

Сигнал переноса в следующий разряд соответствует низкому потенциалу на коллекторе триода 18 в момент t2 р=х·у, где р - значение двоичного переноса в следующий, старший, разряд, х, у - двоичные слагаемые. В последующие моменты t3, t4, … полусумматор будет сохранять значение суммы в виде циркуляции единицы в динамическом триггере, состоящем из трансформаторов 13 и 16 и ключа 12, если сумма равна единице, или циркуляции в этом триггере не будет, если сумма равна нулю.

Выходные сигналы, соответствующие значениям суммы и переноса, могут быть взяты, например, с трансформаторов, включенных последовательно в коллекторные цепи триодов 12 и 13, хотя не исключены другие возможности использования этих ключей. В нашем случае сделано именно так. Сброс полусумматора может быть осуществлен путем подачи в один из моментов t4, t6, … импульса на обмотку сброса 19 трансформатора 16. Тем самым запрещается циркуляция импульса в описанном выше динамическом триггере.

Накапливание происходит путем последовательной подачи цифр слагаемых на трансформаторы 10 и 11 по каждому тактовому импульсу второго такта. В этом режиме полный цикл сложения двух двоичных разрядов составляет один такт. Описанный двоичный накапливающий полусумматор содержит всего четыре сердечника с прямоугольной петлей гистерезиса и два полупроводниковых триода. Трансформатор 10 относится ко входной цепи сумматора, а схема полусумматора может быть построена без него.

Данная схема, будучи простой и экономичной, в то же время надежнее, так как на ее работу не влияет время включения полупроводникового триода. Это влияние обычно сказывается в том, что при одновременном считывании с трансформаторов 10 и 11 (т.е. в случае, когда оба двоичных слагаемых хну равны единице) полупроводниковый ключ 12, управляющий переписью из трансформатора 11 в трансформатор 15, может полностью открыться с задержкой, превышающей длительность выходного импульса с трансформатора 11. В этом случае в момент t1 неполностью открытый ключ 12 представляет большое сопротивление в цепи записи в трансформатор 15, и единица может не записаться, что приведет к неправильному срабатыванию схемы. Описанная схема полусумматора, реализуемая при применении триодов массового назначения, у которых время включения не оговаривается, позволяет обеспечить опережение сигнала, открывающего управляющий ключ 12, по отношению к сигналу с выхода феррит-диодного элемента, которым управляет ключ. В схеме использовано то обстоятельство, что выходной сигнал с феррит-диодного элемента достигает максимальной величины в разное время от начала действия тактового импульса в зависимости от нагрузки на феррит-диодный элемент. Нагрузка по току для трансформатора 11, обеспечена в схеме больше (два параллельно включенных трансформатора 13 и 15), чем для трансформатора 10; поэтому максимум выходного сигнала с трансформатора 11 достигается позже, чем полностью отпирается полупроводниковый ключ 12. Этим самым вводится естественная задержка и исключается влияние времени включения триода, благодаря чему повышается надежность работы схемы. Следует отметить, что дополнительная нагрузка по току для трансформатора 11, позволяющая повысить надежность работы схемы полусумматора, осуществлена с помощью трансформатора 13, на котором, помимо этого, реализуется логическая функция «ИЛИ», т.е. трансформатор 13 входит в схему образования суммы.

Накапливающий десятичный сумматор для кода 8421 (см. фиг. 1) строится на основе четырех двоичных полусумматоров, описанных выше. Эти полусумматоры соединены друг с другом цепями 7 передачи переноса с одного полусумматора на другой. К начальному моменту времени сигнал сброса устанавливает все полусумматоры в начальное (исходное) положение. В момент t0 на входы всех четырех полусумматоров подаются цифры двоичных слагаемых, составляющие четырехразрядный код десятичной цифры определенного разряда десятичного числа. Затем по тактовым импульсам первого и второго тактов все полусумматоры работают независимо друг от друга, как описано выше. В результате этого после импульса второго такта (момент t2) в динамических триггерах полусумматоров сохранится значение первой промежуточной суммы (S′), т.е. суммы двух слагаемых без учета переноса с соседнего полусумматора предыдущего двоичного разряда десятичной цифры. В этот же момент импульс переноса, образованный в данном полусумматоре, поступает на вход второго слагаемого (вход у) полусумматора следующего старшего двоичного разряда. Во время следующих первого и второго тактовых импульсов все полусумматоры работают независимо друг от друга, складывая первую промежуточную сумму, хранившуюся в динамическом триггере каждого полусумматора, с переносом из соседнего младшего двоичного разряда. При этом в момент t2 на вход у полусумматора самого младшего двоичного разряда десятичной цифры поступает перенос со схемы образования переноса десятка, появившегося в результате предыдущего сложения двух десятичных цифр (младших разрядов складываемых десятичных чисел).

Таким образом, к моменту t4 заканчивается формирование младшего двоичного разряда суммы, и в динамических триггерах полусумматоров запоминается значение второй промежуточной суммы (S2). В момент t4-t6 в четырех полусумматорах складывается вторая промежуточная сумма с учетом переносов из разряда в разряд, образовавшихся при предыдущем промежуточном сложении. На каждом следующем такте (в момент t6, t8, …) будет определяться очередной младший двоичный разряд суммы, и в момент t12 в четырех динамических триггерах полусумматоров будет храниться результат - четыре разряда двоичной суммы, а в специальном пятом динамическом триггере - перенос в следующий десятичный разряд.

Признаком необходимости исправления результата для обычного сумматора для кода 8421 служит условие

S5∨S4(S3∨S2)=1

где S2 - двоичное значение цифры второго разряда окончательной суммы, хранящееся во втором полусумматоре (после окончательного определения всех цифр суммы и переноса в старший десятичный разряд);

S3 - двоичное значение цифры третьего разряда окончательной суммы, хранящееся в третьем полусумматоре в момент t12;

S4 - двоичное значение цифры четвертого разряда окончательной суммы, хранящееся в четвертом полусумматоре в момент t12;

S5 - двоичное значение переноса в следующий десятичный разряд, хранящееся в пятом динамическом триггере переноса в момент t12.

В целях ускорения суммирования и упрощения схемы исправления двоичного промежуточного результата предлагается исправлять результат путем анализа цифр промежуточных сумм вместо анализа окончательной суммы, т.е. не дожидаясь момента t12. С этой целью в схеме 6 исправления результата (см. фиг. 1 и 3) вход импульсного трансформатора 20 первого такта соединен с выходами динамических триггеров второго и третьего полусумматоров. Таким образом, на входы 21 и 22 трансформатора 20 непрерывно поступают текущие двоичные значения второго и третьего разрядов промежуточных сумм. С помощью этого трансформатора реализуется двоичная логическая функция

где  - текущее двоичное значение суммы, хранящееся во втором полусумматоре;

- текущее двоичное значение суммы, хранящееся во втором полусумматоре;

- текущее двоичное значение суммы, хранящееся в третьем полусумматоре;

- текущее двоичное значение суммы, хранящееся в третьем полусумматоре;

f - логическая функция «ИЛИ».

Выходной сигнал с трансформатора 20 должен поступить на вход другого импульсного трансформатора только при наличии единицы в динамическом триггере четвертого полусумматора. Необходимо соединить выходную обмотку 25 трансформатора 20 со входной обмоткой 23 трансформатора 24 через ключевой триод 12 из цепи динамического триггера четвертого полусумматора. Вторая входная обмотка 26 трансформатора 24 соединена г динамическим триггером 5, где хранится перенос в следующий десятичный разряд. Таким образом с помощью трансформаторов 20 и 24 реализуется двоичная логическая функция

где  - текущее двоичное значение второго разряда суммы, хранящееся во втором полусумматоре;

- текущее двоичное значение второго разряда суммы, хранящееся во втором полусумматоре;

- текущее двоичное значение четверо того разряда суммы, хранящееся в четвертом полусумматоре;

- текущее двоичное значение четверо того разряда суммы, хранящееся в четвертом полусумматоре;

- текущее двоичное значение четвертого разряда суммы, хранящееся в четвертом полусумматоре;

- текущее двоичное значение четвертого разряда суммы, хранящееся в четвертом полусумматоре;

- текущее двоичное значение переноса в следующий десятичный разряд, хранящееся в пятом динамическом триггере.

- текущее двоичное значение переноса в следующий десятичный разряд, хранящееся в пятом динамическом триггере.

Анализ работы предлагаемого сумматора, (включая схему исправления результата) при проверке полной таблицы сложения десятичных цифр показывает, что значение второго, третьего и четвертого разрядов третьей промежуточной суммы, образующейся в момент t6, и переноса в следующий десятичный разряд в момент t8 однозначно определяет необходимость исправления результата. Это значит, что появление на выходной обмотке трансформатора 24 импульса в момент t8, что соответствует обращению в единицу логической функции

и является достоверным признаком необходимости исправить результат прибавлением единицы ко второму и третьему разрядам суммы.  из формулы (1) - значения второго, третьего и четвертого разрядов третьей промежуточной суммы, записанные во втором, третьем и четвертом полусумматорах в момент t6, и

из формулы (1) - значения второго, третьего и четвертого разрядов третьей промежуточной суммы, записанные во втором, третьем и четвертом полусумматорах в момент t6, и  - значение третьего промежуточного переноса в следующий десятичный разряд.

- значение третьего промежуточного переноса в следующий десятичный разряд.

В момент t8 сигнал, поступивший из устройства управления, открывает ключевой триод, коллектор которого соединен с цепью выходной обмотки 28 трансформатора 24, и если необходимо исправить результат, импульс с выходной обмотки 28 следует на входы 29 и 30 вторых слагаемых второго и третьего полусумматоров. Таким образом, результат исправляется еще до окончания формирования последнего старшего разряда двоичной суммы (т.е. до момента t12), благодаря чему значительно сокращается общее время суммирования двух десятичных цифр.

Предложенная схема позволяет повысить быстродействие, надежность и экономичность устройства, упростить его, а также устранить влияние разброса параметров элементов.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДВОИЧНЫЙ ПОСЛЕДОВАТЕЛЬНЫЙ СУММАТОР НА ФЕРРИТ-ДИОДНЫХ ЭЛЕМЕНТАХ | 1967 |

|

SU204685A1 |

| К-значный фазоимпульсный сумматор | 1971 |

|

SU450163A1 |

| Накапливающий сумматор | 1990 |

|

SU1829031A1 |

| Устройство для моделирования ветви графа | 1986 |

|

SU1348847A1 |

| Сумматор последовательного действия | 1989 |

|

SU1689945A2 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код градусов,минут,секунд | 1980 |

|

SU960791A1 |

| УСТРОЙСТВО ДЛЯ СВЕРТКИ ПО МОДУЛЮ ТРИ | 1991 |

|

RU2011215C1 |

| ТРОИЧНЫЙ ПОЛНЫЙ ПОСЛЕДОВАТЕЛЬНЫЙ СУММАТОР (ВАРИАНТЫ) | 2016 |

|

RU2616887C1 |

| Двоичный сумматор | 1972 |

|

SU439809A1 |

| ШИФРАТОР | 1989 |

|

RU2033691C1 |

1. Накапливающий десятичный сумматор для двоично-десятичного кода на магнитных динамических элементах с управляющими ключами, содержащий четыре двоичных полусумматора, устройство формирования цифр суммы и переноса, устройство исправления результата и устройство хранения переноса в старший десятичный разряд, отличающийся тем, что, с целью повышения быстродействия, надежности, экономичности и упрощения устройства, в устройстве исправления результата, выполненном на двух динамических элементах, например феррит-диодных, вход первого элемента соединен с выходами устройств формирования цифры суммы второго и третьего полусумматоров, а выход соединен через вход второго магнитного динамического элемента с цепью управляющего ключа устройства формирования цифры суммы четвертого полусумматора, второй вход второго магнитного динамического элемента соединен с выходом устройства хранения переноса в старший десятичный разряд, а выход второго магнитного динамического элемента соединен через цепь управляющего ключа с одним из входов второго и третьего полусумматоров.

2. Устройство по п. 1, отличающееся тем, что, с целью устранения влияния параметров управляющих ключей, например, полупроводниковых транзисторов, в полусумматоре вход магнитного динамического элемента соединен через цепь управляющего ключа с выходом второго динамического элемента, а к выходу второго динамического элемента подключена дополнительная нагрузка.

Авторы

Даты

1968-12-20—Публикация

1966-06-21—Подача