00 со

00

сл

со

14)

де нормализатора 22 формируется сигналы логической единицы или логического нуля в зависимости от наличия сигнала на его входе. Затем сигнал через инвертор 21 поступает на С19

IJ97859

и коммутатор 20. При наличии выходного сигнала М 1 на коммутатор 20 и С 19 поступает сигнал логическогб нуля, не оказывающий управляющего воздействия. 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля параметров линейных интегральных схем | 1981 |

|

SU1030748A1 |

| ИМПУЛЬСНЫЙ РАДИОЛОКАТОР | 1985 |

|

SU1840927A1 |

| Линейный интерполятор | 1987 |

|

SU1439534A1 |

| Система экстремального регулирования | 1985 |

|

SU1352452A1 |

| Устройство для измерения амплитудных и фазовых искажений корреляционного приемника псевдослучайных сигналов | 1984 |

|

SU1205072A1 |

| Устройство для измерения вихревого компонента скорости потока | 1984 |

|

SU1265619A1 |

| Устройство для определения звукоизоляции ограждающих конструкций | 1977 |

|

SU711614A1 |

| Устройство для контроля параметров двигателя внутреннего сгорания | 1988 |

|

SU1652858A1 |

| Устройство контроля комбинационных составляющих сигнала нелинейного четырехполюсника | 1985 |

|

SU1264111A1 |

| РЕЗЕРВИРОВАННЫЙ УСИЛИТЕЛЬ | 2001 |

|

RU2199843C1 |

Изобретение относится к контрольно-измерительной технике и позволяет расширить функциональные возможности устройства. Устройство содержит генератор 2 . стимулирующих сигналов, масштабный -усилитель 3, регулируемый усилитель 4, делектор 5, блок 6 вычитания, источник 7 опорного напряжения и аттенюатор 8. Кроме того, устройство имеет регулируемый усилитель 9, детектор 10, блок 11 сравнения, усилитель 12 постоянного тока, переключатель 13, генератор 14 импульсов и реверсивный счетчик 15. В устройство введены нормализатор 17, инвертор 18, блок 23 формирования уровней и блок 24 задания пределов. На выходе порогового блока 16 происходит сравнение выходного сигнала испытуемой микросхемы (М) 1 и сигналов сформированных уровней до, тех пор, пока выходной сигнал М 1 не станет меньше очередного уровня. Счетчик (С) 19 считает количество произведенных переключений. Результаты счета вводятся на блок 25 индикации. На выхосл

1

Изобретение относится к контрольно-измерительной технике, может быть использовано для измерения параметров, контроля и классификации линейных интегральных схем по величине коэффициента усиления и является усовершенствованием устройства по авт. св. № 1030748.

Целью изобретения является расширение функциональных мозможностей за счет контроле коэффициента усиления в заданном .интервале значений и по- выпение быстродействия за счет автоматизации контроля.

На фиг.1 изображена схема устройства; на фиг. 2 - структурная схема блока формирования уровней.

Устройство содержит испытуемую микросхему 1, генератор 2 стимулирующих сигналов, масштабный усилитель 3 регулируемый усилитель 4, детектор 5, блок 6 вычитания, источник 7 опорного напряжения, аттенюатор 8, регулируемый усилитель 9, детектор 10, блок 11 сравнения, усилитель 12 постоянного тока, переключатель 13, генератор 14 импульсов, реверсивный счетчик 15, пороговый блок 16, нормализатор 17, инвертор 18, счетчик 19, коммутатор 20, инвертор 21, нормализатор 22, блок 23 формирования уровней, блок 24 задания пределов, блрк 25 индикации.

Выход генератора 2 стимулирующих сигналов соединен с входами испытуемой микросхемы 1, масштабного усили- теля 3 и блока 24 задания пределов, выход испытуемой микросхемы 1 соединен с входами аттенюатора 8, нормализатора 22 и первым входом порогового блока 16, выход масштабного усилителя 3 через последовательно соединенные регулируемый усилитель 4, детектор 5 блок 6 вычитания и усилитель 12 постоянного тока соединен с объединенными управляющими входами регулируе5

5

0 0

5 0

мых усилителей 4 и 9, второй вход блока 6 вычитания соединен с выходом источника 7 опорного напряжения, выход регулируемого усилителя 9 через детектор 10 соединен с первым входом блока 11 сравнения, второй вход которого соединен с выходом источника 7 опорного напряжения, выход блока 11 сравнения соединен с управляющим входом переключателя 13, генератор 14 импульсов через последовательно соединенные переключатель 13 и реверсивный счетчик 15 соединен с вторым входом управляемого аттенюатора 8, выход которого соединен с вторым входом регулируемого усилителя 9,выход генератора 14 импульсов через переключатель 13 соединен с прямым и инверсным счетными входами реверсивного счетчика 15, кодовые входы которого соединены с управляющими входами аттенюатора 8, второй вход порогового блока 16 соединен с выходом коммутатора 20, выход порогового блока 16 соединен с входом нормализатора 17, выход которого соединен с первым входом счетчика 19 и через последовательно включенный инвертор 18 - с прямым управляющим входом коммутатора 20, выход нормализатора 22 соединен с входом инвертора 21, выход которого соединен с вторым входом счетчика 19 и вторьм управляющим входом коммутатора 20, выходы блока 24 задания пределов соединены с входами блока 23 формирования уровней, выходы которого соединены с коммутируемыми входами коммутатора 20, выход счетчика 19 соединен с входом блока 25 индикации .

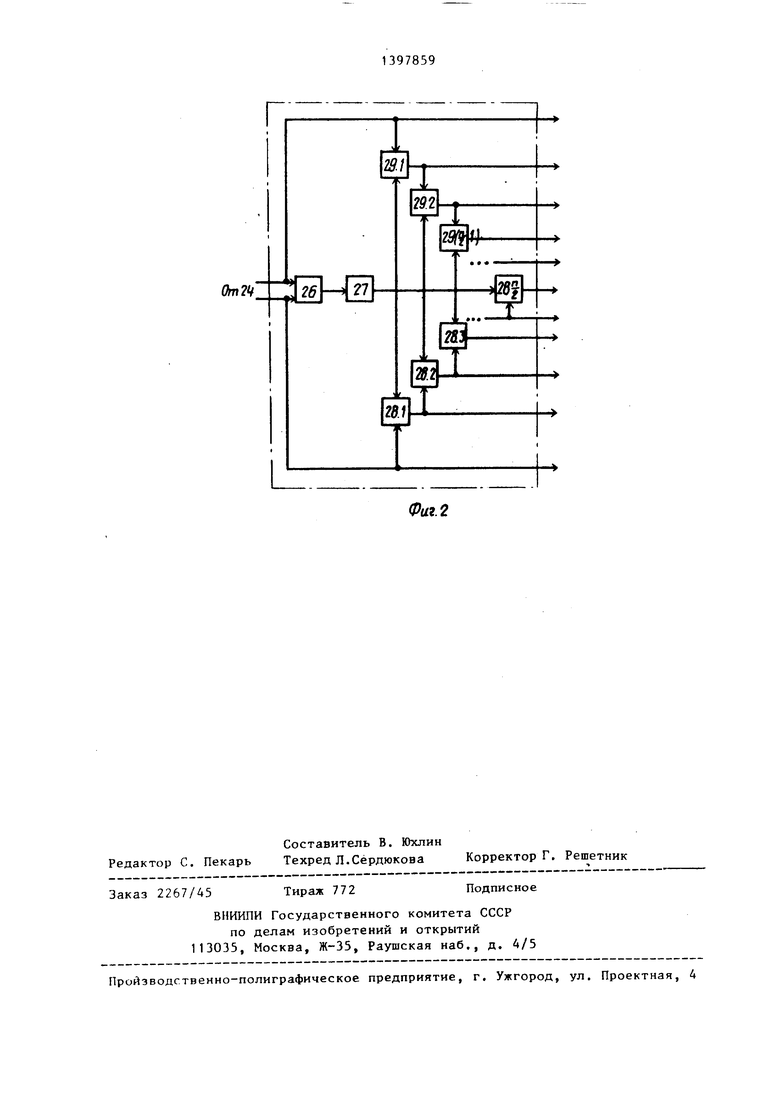

Блок 23 формирования уровней состоит из блока 26 вычитания, делителя 27, п/2 формирующих блоков 28.1- 28.п/2 сложения и (п/2-1) формирующих блоков 29.1-29(п/2-1) вычитания.

31397859

Входы блока 26 вычитания соединены с входами блока 23 формирования уровней, выход блока 26 вычитания соединен с входом делителя 27, выход которого соединен с первыми входами формирующих блоков 28.1-28.П/2 сложения и первыми входами формирующих блоков 29.1-29(п/2-1) вычитания, второй вход первого формирующего блока 29,1 вычи-ю опорного напряжения, то бло1 11 срав- тания соединен с первым входом и пер- нения в зависимости от знака разнос- вым выходом блока 23 формирования ™ (Уск -о) установит переключатель уровней, второй вход последующих формирующих блоков 29.1 вычитания соединен с выходом предыдущих формирующих 15 соответственно на прямой или ин- блоков 29.1-1 вычитания, второй вход версный вход счетчика 15. Пусть первого формирующего блока 28,1 сложения соединен с вторым входом и последним выходом блока 23 формирования

квадратичных значений 5,

При этом kp pyf kp, где k рч, коэффициент усиления регулируемого усилителя 9.

Вместе с тем, если значение у. , сигнала на выходе детектора 10 не равно значению Zp сигнала источника

13 в такое состояние, что импульсы с выхода генератора 14 будут посту(у - ZP ) О, импульсы с генератора 14 через переключатель 13 будут поступать на прямой вход счетчиуровней, второй вход последующих фор-20 ° будет увеличивать- мирующих блоков 28.1 сложения соеди- Соответственно коду N коэффициент нен с выходом предьщущих формирующих блоков 28.1-1 сложения, выходы формирующих блоков 28.1-28,п/2 сложения

25 превысит значение z

и формирующих блоков 29.1-29(п/2-1) вычитания соединены с соответствующими выходами блока 23 формирования уровней.

Устройство работает следующим образом.

Испытательный сигнал напряжения синусоидальной формы заданного уров- Ия поступает на вход испытуемой схемы, а также на вход масштабного усилителя 3 и блока 24 задания пределов, Усиленный B k раз с выхода микросхемы 1 сигнал у kx поступает на аттенюатор 8. Если значение х , преоб30

ослабления k аттенюатора 8 увеличивается до тех пор, пока значение у выходного сигнала детектора 10 не

источника 7

опорного напряжения. После этого блок 11 установит переключатель 13 в состояние, при котором импульсы с генератора 14 будут поступать на инверсный вход счетчика 15, и код N в нем и соответственно коэффициент ослабления k аттенюатора 8 будут уменьшаться до тех пор, пока значение у не станет меньше значения z и т.д, В результате нескольких чередующихся цик- лов увеличения и уменьшения коэффициент ослабления аттенюатора 8 становится равным коэффициенту ослабления ячейки аттенюатора 8, соответствующей младшему разряду счетчика 15. При этом

разованное масщтабным усилителем 3, регулируемым усилителем 4, детекторо 5 на первом входе блока 6 вычитания

не равно значению z . сигнала на выхо

де источника 7 опорного напряжения, то сигнал с выхода блока 6 вычитания усиленный и проинвертированный усили телем 12 постоянного тока, значение которого пропорционально разности (Xj. z р) , будет изменять коэффициенты усиления и. k р,, регулируемых усилителей 4, 9 до тех пор, пока не

наступит равенство х ck оПри этом Xt. x-k, k р,

1

где kp,, , k - коэффициенты усиления масштабного усилителя

ag погрешность преобразовани детектора 10 среднеквадра тичных значений в момент равенства у о При условии идентичности динамических характеристик функций преобр

3 и регулируемого уси- зования детекторов 5 и 10 в точках

&ё

лителя 4;

- погрешность преобразования детектора среднеопорного напряжения, то бло1 11 срав нения в зависимости от знака разнос ™ (Уск -о) установит переключатель соответственно на прямой или ин версный вход счетчика 15. Пусть

квадратичных значений 5,

При этом kp pyf kp, где k рч, коэффициент усиления регулируемого усилителя 9.

Вместе с тем, если значение у. , сигнала на выходе детектора 10 не равно значению Zp сигнала источника

опорного напряжения, то бло1 11 срав нения в зависимости от знака разнос ™ (Уск -о) установит переключатель соответственно на прямой или ин версный вход счетчика 15. Пусть

13 в такое состояние, что импульсы с выхода генератора 14 будут постуопорного напряжения, то бло1 11 срав- нения в зависимости от знака разнос- ™ (Уск -о) установит переключатель соответственно на прямой или ин- версный вход счетчика 15. Пусть

(у - ZP ) О, импульсы с генератора 14 через переключатель 13 будут поступать на прямой вход счетчи ° будет увеличивать- Соответственно коду N коэффициент

превысит значение z

ослабления k аттенюатора 8 увеличивается до тех пор, пока значение у выходного сигнала детектора 10 не

источника 7

опорного напряжения. После этого блок 11 установит переключатель 13 в состояние, при котором импульсы с генератора 14 будут поступать на инверсный вход счетчика 15, и код N в нем и соответственно коэффициент ослабления k аттенюатора 8 будут уменьшаться до тех пор, пока значение у не станет меньше значения z и т.д, В результате нескольких чередующихся цик- лов увеличения и уменьшения коэффициент ослабления аттенюатора 8 становится равным коэффициенту ослабления ячейки аттенюатора 8, соответствующей младшему разряду счетчика 15. При этом

у -k arr z

0

где у

значение сигнала на выходе микросхемы 1; значение коэффициента ослабления аттенюатора 8 в момент равенства yck о k р, k р;

50

ag погрешность преобразования детектора 10 среднеквадратичных значений в момент равенства у о При условии идентичности динамических характеристик функций преобраX г.. Ус. z

-о

Л& Л g7

kp + ug y-k

kp -sg.

При этом значение коэффициента ослабления аттенюатбра 8 и соответствующий ему код N в счетчике 15 равны

N k.

где k

п

х поступает на первые

коэффициент усиления испытуемой микросхемы.

Вместе с тем испытательный сигнал X с выхода генератора 2 стимулирующих сигналов поступает на вход бл-ока 2А задания пределов, на выходах которого два сигнала Ул,акс у«„„ пропорциональны заданным предельным значениям коэффициента усиления kJ,ццtИ . Выходные сигналы Ущдце и у„у„ блока 24 задания пределов поступают на входы блока 23 формирования уровней, который форми- рует заданное количество уровней.

Формирование уровней происходит следующим образом. Сигналы и У.,.и поступают на входы блока 26 выММ И

читания, на выходе которого сигнал пропорционален разности (у..,- У..,,.,)

rtKC ми п

x(k о(ис k UK ) йу. Этот сигнал с выхода блока 26 вычитания подается на вход делителя 27.

С выхода делителя 27 сигнал k цддн

входы формирующих блоков 29.1 вычитания и формирующих блоков 28.1 сложения. На второй вход первого формирующего блока 28.1 сложения подается сигнал у уц с выхода блока 24 задания пределов. С выхода первого формирующего блока 28.1 сложения сигнал

kv,«Ke +(n-1)kMi/H

-х подается на

п

вход второго формирующего блока 28.2 сложения и далее на второй вход каждого последующего формирующего блока

сложения сигнал

1 k

(n-i)k,uH

подается с выхода предыдущего формирующего блока сложения. Кроме того, выходные сигналы всех формирующих блоков сложения являются выходными сигналами блока 23 формирования уровней. На второй вход первого формирующего блока 29.1 вычитания подается сигнал с выхода блока 24 задания пределов. С выхода первого формирующего блока 29.1 вычитания сигнал

iCju.eKfV. ,

t iiu-i , X подается на

п

вход рторого формирующего блока 29.2

вычитания и далее на второй вход каждого последующего формирующего блока микс (n-i)-t-i kw.VH

вычитания сигнал

-.X

подается с выхода предыдущего формирующего блока вычитания. Кроме того, выходные сигналы всех формирующих блоков вычитания являются выходными сигналами блока 23 формирования уровней. Входные сигналы блока 23 формирования уровней у„„кс м«кс X и ммн мин X также подаются на выход блока 23 формирования уровней. Таким образом на выходе блока 23 формирования уровней формируется набор выходных сигналов величинами от

м«н маис

ДО /««цс X

- k.

п

X.

g 20

С выхода блока 23 формирования уровней сигналы поступают на входы коммутаора 20, который поочередно, начиная с k д . к, подключает входные 25 сигналы к выходу. С выхода коммута- тора 20 сигнал поступает на второй вход порогового блока 16, на первый вход которого поступает сигнал с выхода испытуемой микросхемы 1. В поро- .JQ говом блоке происходит сравнение сигнала k.x с выхода испытуемой микросхемы 1 с сигналами заданных уровней В том случае, когда

k -х -) fk + i . , 1 ,. п

%Ju

на выходе порогового блока 16 есть сигнал, в противном случае - сигнал отсутствует. С выхода порогового блока 16 сигнал поступает на вход нормализатора 17, который вьфабатьшает на выходе при наличии сигнала на входе сигнал логической единицы, при отсутствии сигнала на входе - сигнал логического нуля. Сигнал логической единицы поступает на вход счетчика 19, который производит счет поступающих логических единиц. Кроме того, сигнал с выхода нормализатора 17 через инвертор 18 поступает на первый управляющий вход коммутатора 20. При наличии сигнала логической единицы на выходе нормализатора 17 на первом управляющем входе коммутатора 20 будет сигнал логического нуля, не вызывающий никаких управляющих воздействий, при наличии сигнала логического нуля на выходе нормализатора 17 на первом управляющем входе коммутатора

40

45

20 - сигнал логической единицы, который производит прекращение переключений. Для устранения нежелательного воздействия сигнала логической единицы, появляющегося при переключении, первый управляющий вход коммутатора 20 на время переключения запирается.

Таким образом в пороговом блоке 16 производится сравнение выходного сигнала испытуемой микросхемы 1 и сигналов сформированных уровней до тех пор, пока выходной сигнал испытуемой микросхемы не станет меньше очередного уровня. Счетчик 19 считает количество произведенных переключений Результаты счета выводятся на блок 25 индикации.

Сигнал с выхода испытуемой микросхемы 1 поступает на вход нормализатора 22, на выходе которого формиру- ются сигналы логической единицы и логического нуля в зависимости от

того, есть ли или нет сигнал на входе.25 входом коммутатора, выход котоС выхода нормализатора 22 сигнал через инвертор 21 поступает на управляющий вход счетчика 19 и второй управляющий вход коммутат ора 20. При наличии выходного сигнала испытуемой микросхемы 1 на управляющий вход счетчика 19 и коммутатора 20 поступает сигнал логического нуля, не оказывающий управляющего воздействия. При замене испытуемой интегральной микросхемы 1 сигнал с ее выхода отсутствует и на управляющий вход счетчика 19 и коммутатора 20 поступает управляющий сигнал логической

Q g

0

единицы, который устанавливает их

в исходное состояние.

Формула изобретения

Устройство для контроля параметров линейных интегральных схем по авт.сн. № 1030748, отличающееся тем, что, с целью расширения функциональных возможностей за счв контроля коэффициента усиления в заданном интервале значений и повышения быстродействия за счет автоматизации контроля, в него введены пороговый блок, первый и второй нормализаторы, первый и второй инверторы, счетчик, коммутатор, блок формирования уровней, блок записи задания пределов, блок индикации, причем первый вход порогового блока соединен с клеммой для подключения выхода объекта контроля и с входом первого нормализатора, выход которого через первый инвертор соеди- нен с первым входом сг}етчика и перо

5

рого соединен с вторым входом порогового блока, выход которого через второй нормализатор соединен с входом второго инвертора и с вторым входом счетчика, выход которого соединен с входом блока индикации,выход второго инвертора соединен с вторым входом коммутатора, третьи входы которого соединены с соответствующими выходами блока формирования уровней, входы которого соединены с соответствующими выходами блока задания пределов, вход которого соединен с клеммой для подключения входа объекту контроля.

Om2if

Составитель В. Юхлин Редактор С. Пекарь Техред Л.Сёрдюкова Корректор Г. Решетник

Заказ 2267/45

Тираж 772

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

| Устройство для контроля параметров линейных интегральных схем | 1981 |

|

SU1030748A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1988-05-23—Публикация

1986-06-16—Подача