отображения информации. Целью изобретения является повышение быстродействия и расширение функциональных возможностей за счет формирования координат точек при интерполяции и сигнала окончания интерполяции. Линей- ньй интерполятор содержит первый 1, второй 2 и третий 3 блоки суммирования, первьй 4, второй 5 и третий 6 коммутаторы, блок 7 вычисления оценочной функции, четвертьй коммутатор 8, регистр 9 оценочной функции, блок 10 формирования сигналов интерполяции, блок 11 счетчиков адресных сигналов, 5лок 12 сравнения и блок 13 управления. Введение в линейный интерполй- тор третьего и четвертого коммутаторов, счетчиков адресных сигналов, блока управления и их связей обеспечивает повышение быстродействия за счет уменьшения времени выполнения первого шага путем замены части ариф метич.еских операций определения начального значения оценочной функции логическими, а также обеспечивает расширение функциональных возможностей интерполятора за счет формирования координат точек в процессе интерполяции и сигнала останова по его окончании. 2 з.п. ф-лы, 8 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Линейный интерполятор для систем интерактивной графики | 1988 |

|

SU1608691A1 |

| Линейный интерполятор | 1988 |

|

SU1538166A2 |

| Линейный интерполятор | 1987 |

|

SU1439532A1 |

| Цифровой линейный интерполятор | 1989 |

|

SU1693592A1 |

| Цифровой интерполятор | 1981 |

|

SU1003022A1 |

| Интерполятор | 1983 |

|

SU1108395A1 |

| Круговой интерполятор | 1988 |

|

SU1566321A1 |

| Цифровой линейный интерполятор | 1991 |

|

SU1807450A1 |

| Интерполятор | 1983 |

|

SU1089551A1 |

| Линейный интерполятор | 1986 |

|

SU1383302A1 |

Изобретение относится к линейным интерполяторам и может быть использовано в телевизионной технике в устройствах интерактивной графики и интерактивной живописи, в устройствах : ел акции видеосигнала сложной формы и генераторах границ спецэффекта на основе светового пера, а также в автоматике и вычислительной технике в устройствах графического

Изобретение относится-к линейным интерполяторам и может быть использовано в телевизионной технике, в , ., устройствах интерактивной графики и интерактивной живописи, в устройствам; селекции видеосигнала сложной формы и генераторах границ спецэффекта, на основе светового пера, а также в автоматике и вычислительной технике, в устройствах графического отображения информации.

Цель изобретения - повышение быстродействия и расширение функ1Сион,аль- ных возможностей за счет формирова- ния координат точек при интерполяции , а также формирования сигнала окончания интерполяции.

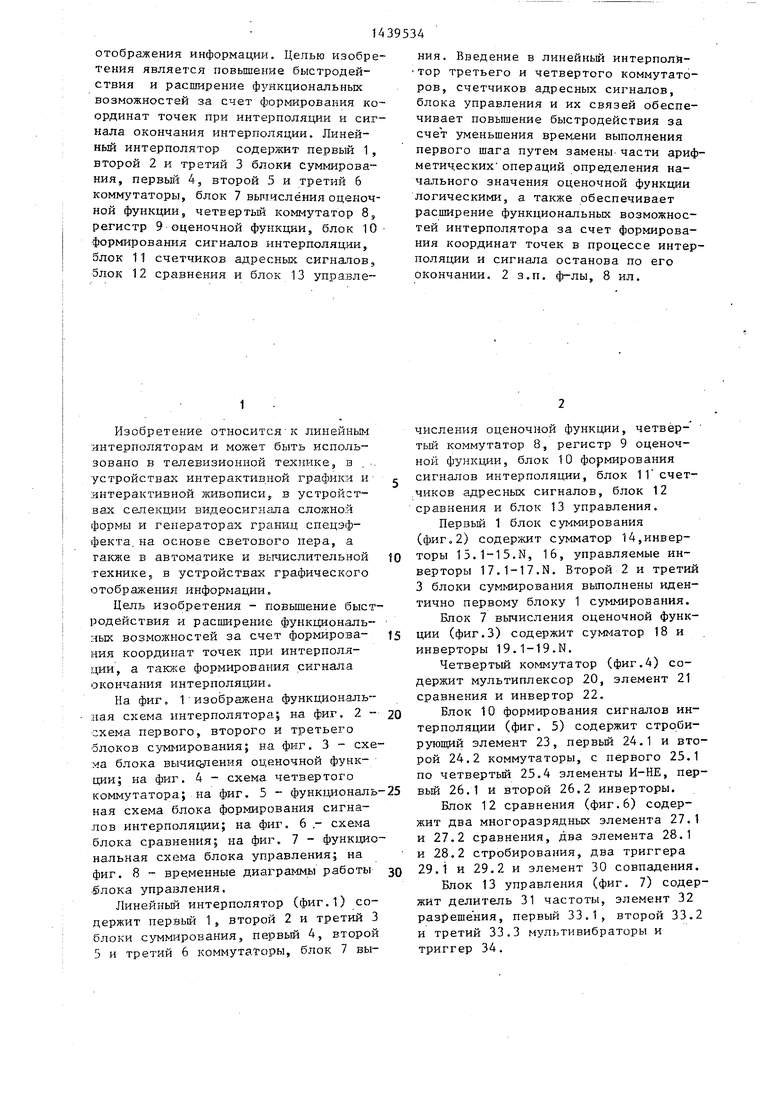

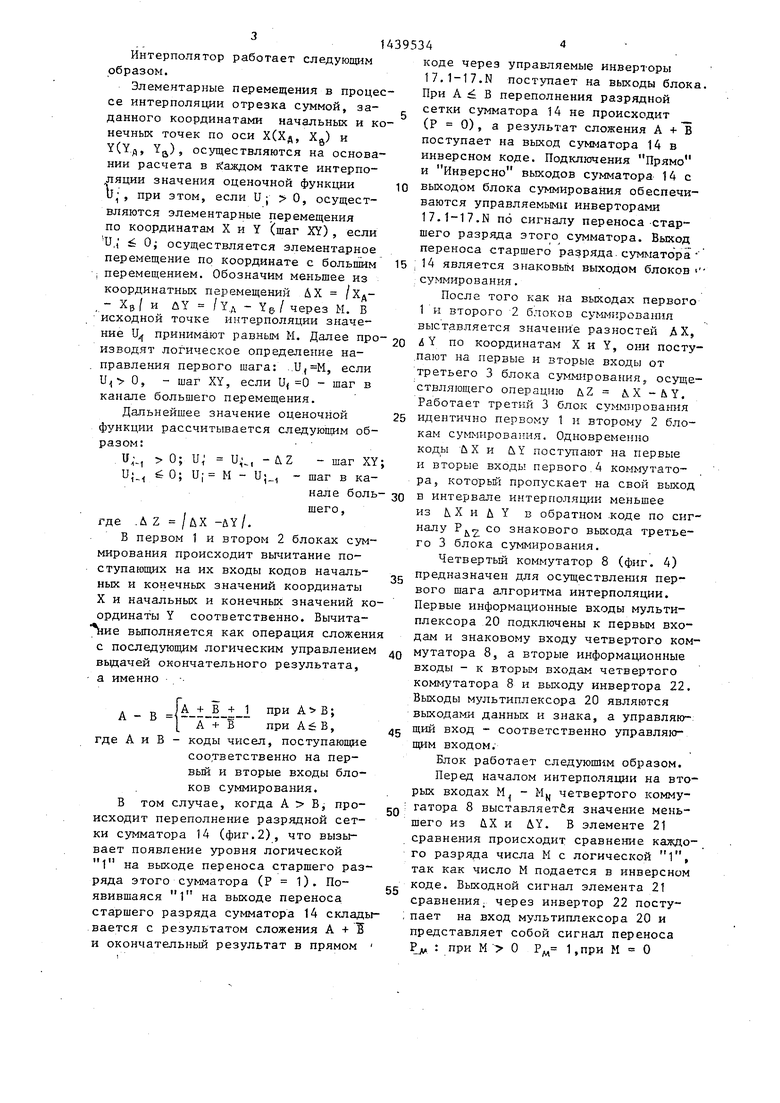

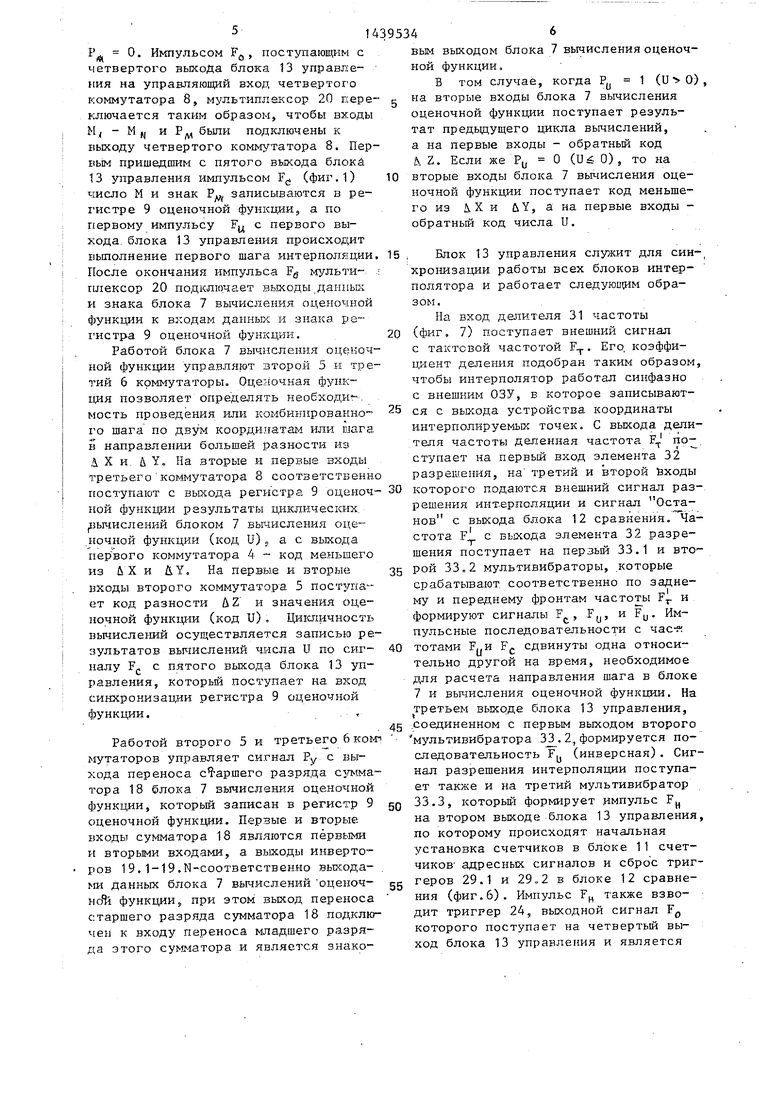

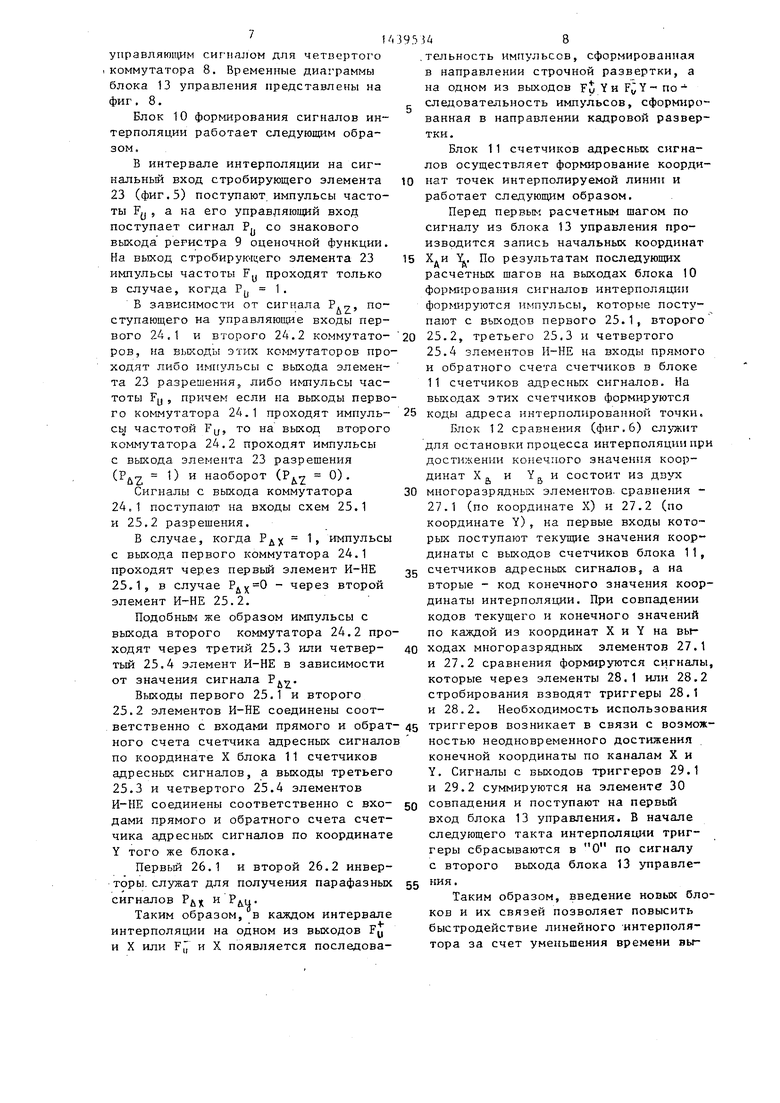

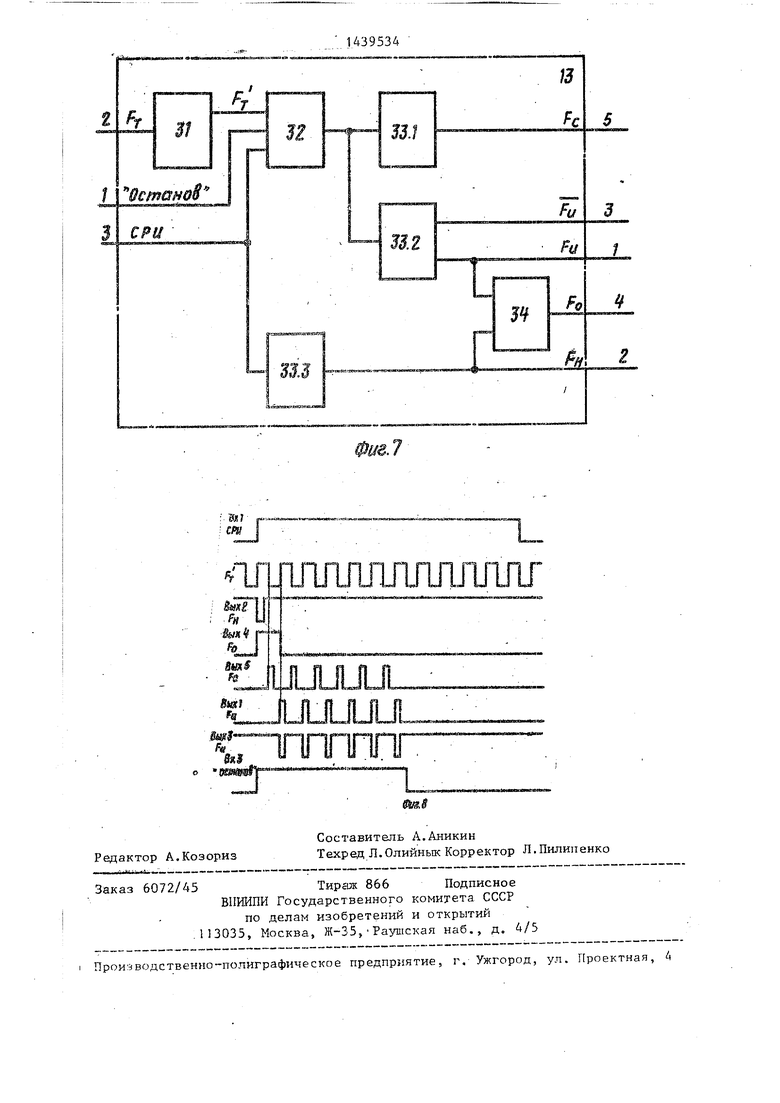

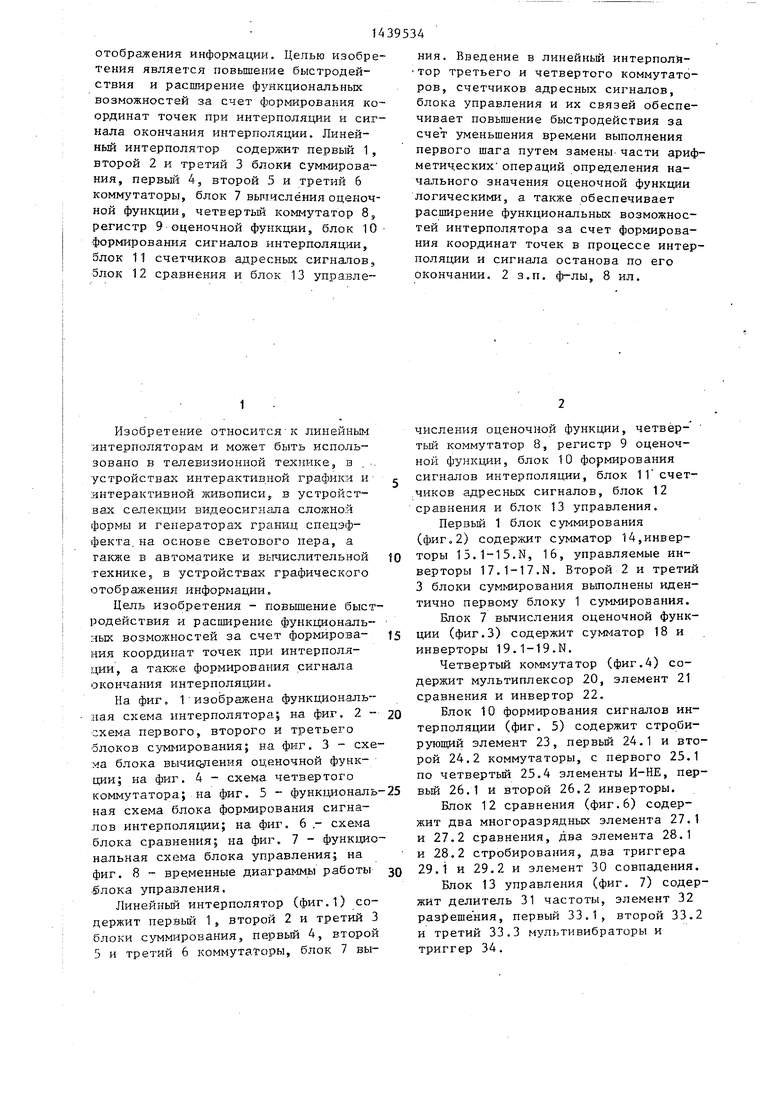

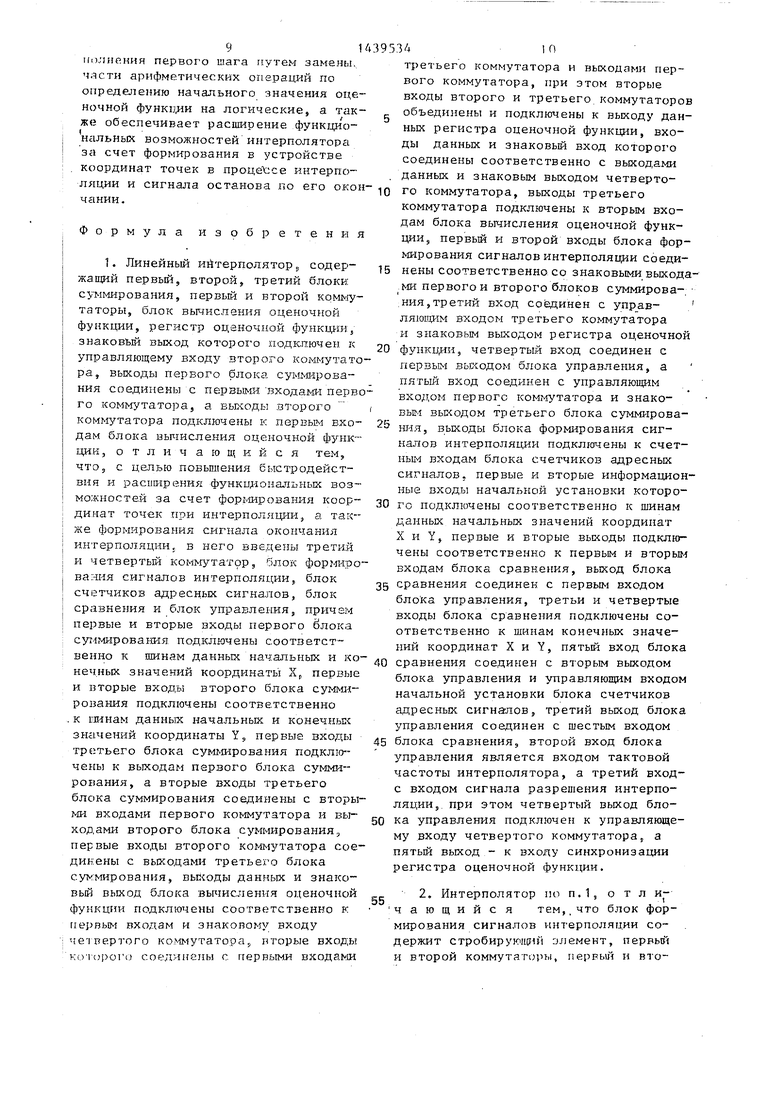

На фиг, 1 изображена функцион.аль-- ная схема интерполятора; на фиг, 2 - схема первого, второго и третьего блоков cyм шpoвaния; на фиг. 3 - схема блока вычисутения оценочной функции; на фиг. 4 - схема четвертого коммутатора; на фиг. 5 - функциональ ная схема блока формирования сигналов интерполяции; на фиг. 6 .- схема блока сравнения; на фиг, 7 функциональная схема блока управления; на фиг. 8 - вре.менные диаграммы работы .блока управления.

Линейный интерполятор (фиг.1) содержит первый 1, второй 2 и третий 3 блоки суммирования, первый 4, второй 5 и третий 6 коммутаторы, блок 7 вычисления оценочной функции, четвер- тый коммутатор 8, регистр 9 оценочной функции, блок 10 формирования сигналов интерполяции, блок 11 счетчиков адресных сигналов, блок 12 сравнения и блок 13 управления.

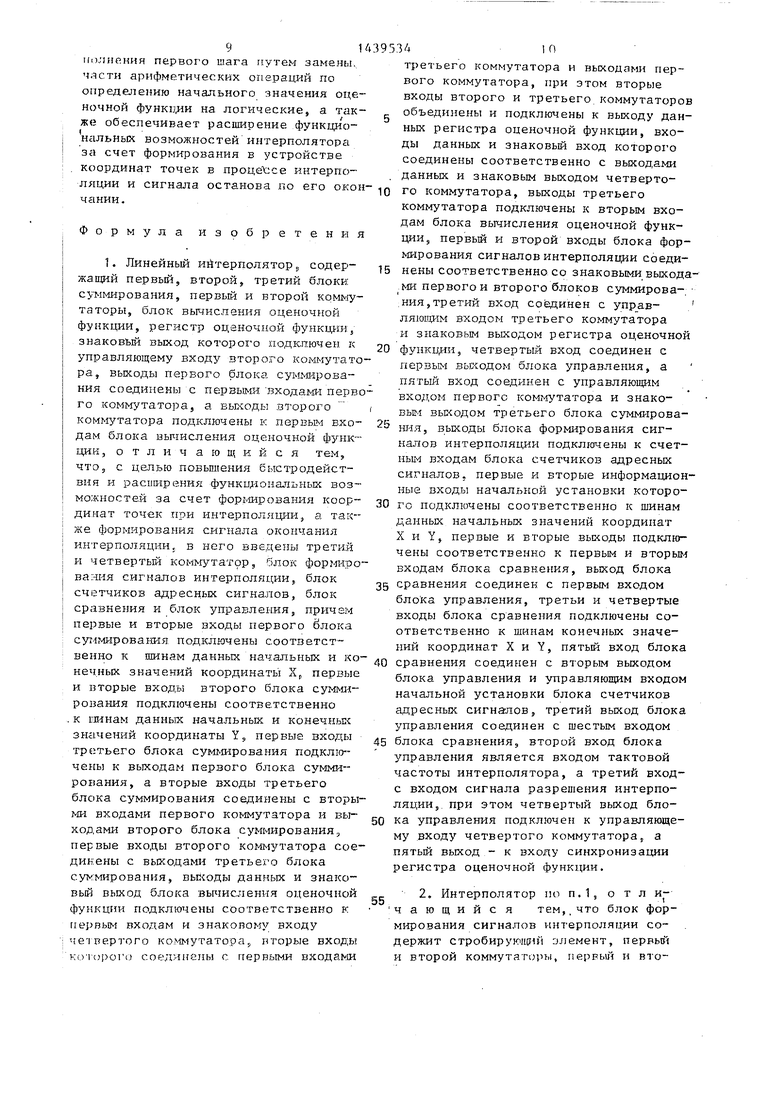

Первьй 1 блок суммирования (фиг,2) содержит сумматор 14,инверторы 15.1-15.N, 16, управляемые инверторы 17.1-17.N. Второй 2 и третий 3 блоки суммирования вьшолнены идентично первому блоку 1 суммирования.

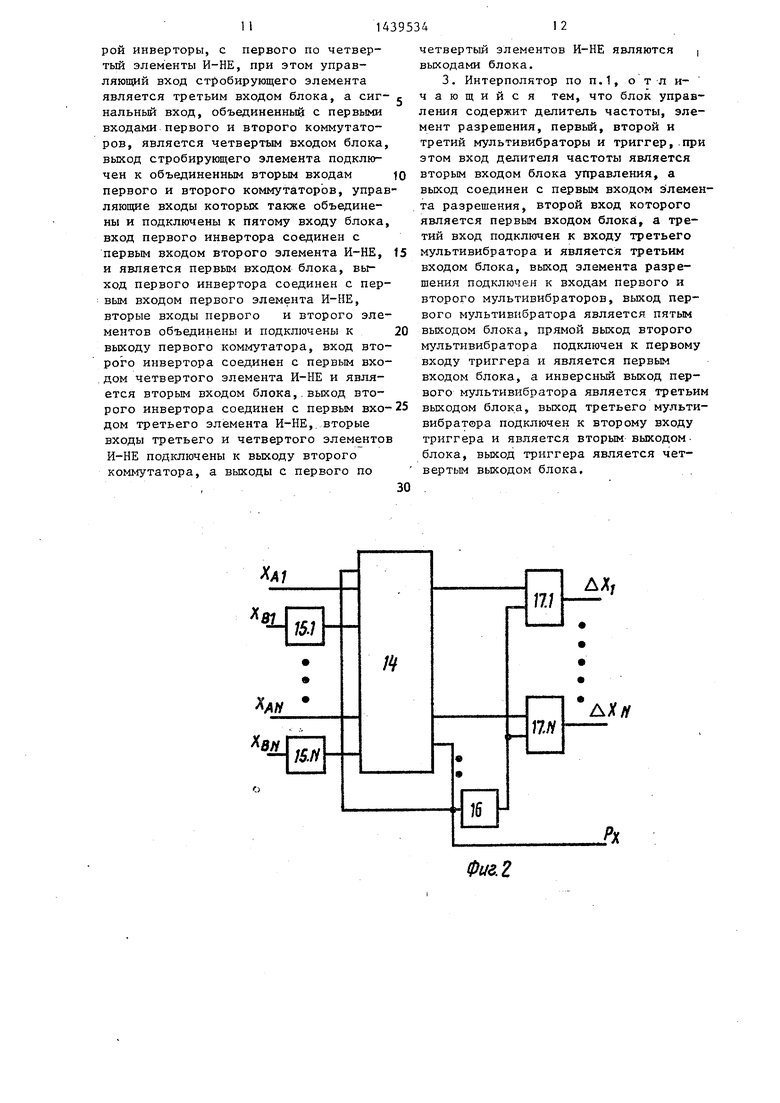

Блок 7 вьиисления оценочной функции (фиг.З) содержит сумматор 18 и инверторы 19.1-19.N.

Четвертый коммутатор (фиг.4) содержит мультиплексор 20, элемент 21 сравнения и инвертор 22.

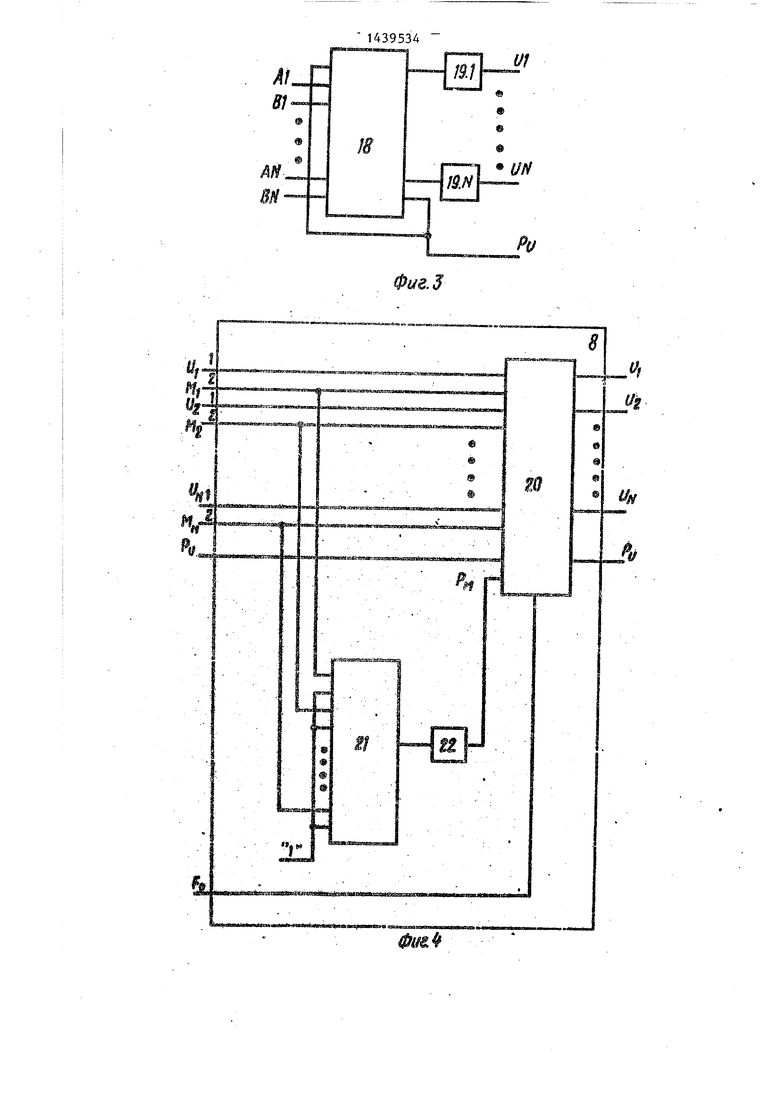

Блок 10 формирования сигналов интерполяции (фиг. 5) содержит строби- рующий элемент 23, первый 24.1 и второй 24.2 коммутаторы, с первого 25.1 по четвертьй 25.4 элементы И-НЕ, пер- вьш 26.1 и второй 26.2 инверторы.

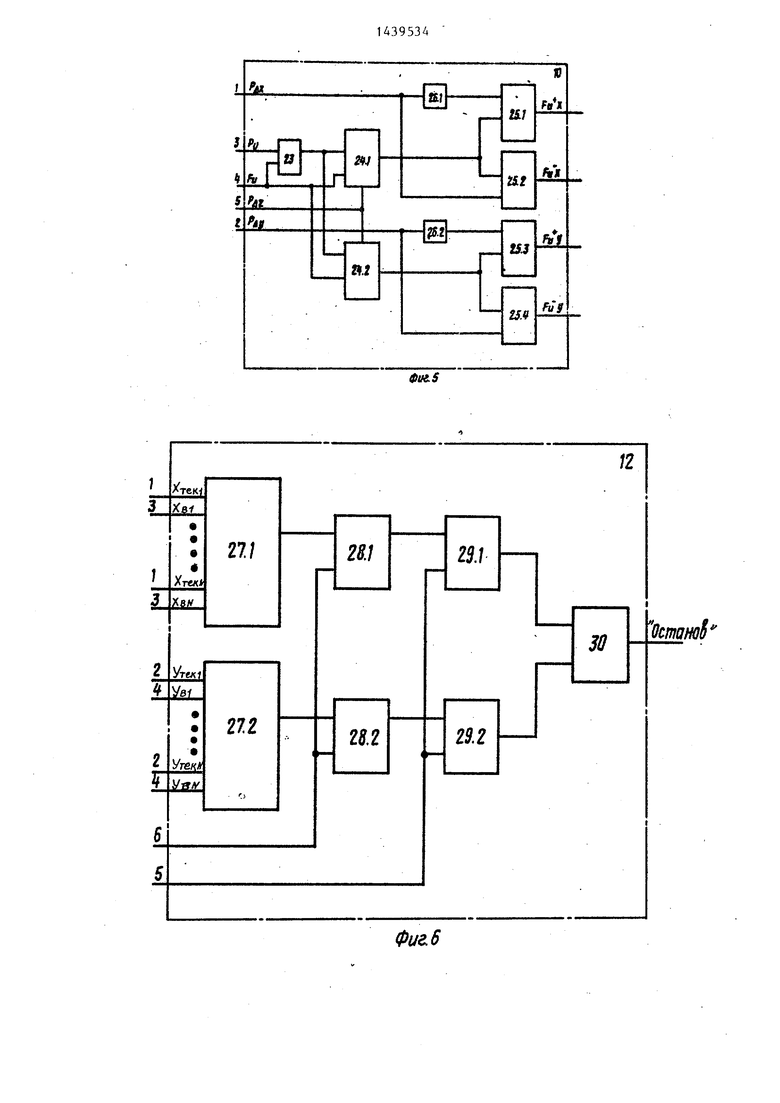

Блок 12 сравнения (фиг.6) содержит два многоразрядных элемента 27. 1 и 27.2 сравнения, два элемента 28.1 и 28.2 стробирования, два триггера 29.1 и 29.2 и элемент 30 совпадения.

Блок 13 управления (фиг. 7) содержит делитель 31 частоты, элемент 32 разрешения, первый 33.1, второй 33.2 и третий 33.3 мультивибраторы и триггер 34.

1439534

Интерполятор работает следующим образом.

Элементарные перемещения в процессе интерполяции отрезка суммой, заданного координатами начальных и конечных точек по оси Х(Хд, Х) и (д, Yg), осуществляются на основании расчета в з аждом такте интерполяции значения оценочной функции , при этом, если U; О, осуществляются элементарные перемещения по координатам X и Y (шаг XY), если и,; 0; осуществляется элементарное

коде через управляемые инверторы 17.1-17.N поступает на выходы блока При А В переполнения разрядной сетки сумматора 14 не происходит (Р 0), а результат сложения А + В поступает на выход сумматора 14 в инверсном коде. Подключения Прямо и Инверсно выходов сумматора 14 с 10 выходом блока суммирования обеспечиваются управляемыми инверторами 17.1-17.N по сигналу переноса-старшего разряда этого сумматора. Выход переноса старшего разряда, сумматора

перемещение по координате с болышм 15 I является знаковьм выходом блоков

; перемещением. Обозначим меньшее из координатных перемещений ДХ /Хд- - XB/ и Д /.д - е/ через М. В исходной точке интерполяции значесуммир о в а и ия.

После того р;ак на выходах первого

1 и второго 2 блоков CyNiMilpOBaHIin

выставляется значени е разностей Л X,

выставляется значени е разностей Л X,

ние и принимают равным М. Далее про-JQ по координатам X и , огш постуизводят логическое определение направления первого шага: ..U, М, если и О, - шаг Х, если и 0 - шаг в канапе большего перемещения.

Дальнейшее значение оценочной функции рассчитывается следующим образом:

. U;, 0; и; U , -UZ - шаг

U ё 0; U М - U;, - шаг в ка,пают на первые и вторые входы от третьего 3 блока суммирования, осуществляющего операцию uZ & X -&. Работает третий 3 блок суммирования 25 идентично первому 1 и второму 2 блокам суммировамия. Одновременно коды йХ и й поступагот на первые и вторые входы первого.4 коммутатора, который пропускает на свой выход

нале боль- зо в интервале интерполяции меньшее

шего, где -Л Z /ДХ .

В первом 1 и втором 2 блоках суммирования происходит вычитание поступающих на их входы кодов начальных и конечных значений координаты X и начальных и конечных значений координаты соответственно. Вычита- tiKe вьшолняется как операция сложения

с последующим логическим управлением Q мутатора 8, а вторые информационные

вьщачей окончательного результата, а именно

1 1-1 Р А В; при , где А и В - коды чисел, поступающие соответственно на первый и вторые входы блоков суммирования. В том случае, когда А В, происходит переполнение разрядной сетки сумматора 14 (фиг.2), что вызывает появление уровня логической 1 на выходе переноса старшего разряда этого сумматора (Р 1), По- явивщаяся 1 на выходе переноса старшего разряда сумматора 14 складывается с результатом сложения А + В и окончательный результат в прямом

коде через управляемые инверторы 17.1-17.N поступает на выходы блока. При А В переполнения разрядной сетки сумматора 14 не происходит (Р 0), а результат сложения А + В поступает на выход сумматора 14 в инверсном коде. Подключения Прямо и Инверсно выходов сумматора 14 с выходом блока суммирования обеспечиваются управляемыми инверторами 17.1-17.N по сигналу переноса-старшего разряда этого сумматора. Выход переноса старшего разряда, сумматора

суммир о в а и ия.

После того р;ак на выходах первого

1 и второго 2 блоков CyNiMilpOBaHIin

выставляется значени е разностей Л X,

по координатам X и , огш посту,пают на первые и вторые входы от третьего 3 блока суммирования, осуществляющего операцию uZ & X -&. Работает третий 3 блок суммирования 25 идентично первому 1 и второму 2 блокам суммировамия. Одновременно коды йХ и й поступагот на первые и вторые входы первого.4 коммутатора, который пропускает на свой выход

5

из X и л в обратном .коде по сигналу . знакового выхода третьего 3 блока суммирования.

Четвертый коммутатор 8 (фиг. 4) предназначен для осуществления пер вого шага а.пгоритма интерполяции. Первые информационные входы мультиплексора 20 подключены к первым входам и знаковому входу четвертого комвходы - к вторым входам четвертого комментатора 8 и выходу инвертора 22. Выходы мультиплексора 20 являются выходами данных и знака, а управляю- с щий вход - соответственно управляющим входом.

Блок работает следуюш11М образом.

Перед началом интерполяции на вторых входах М, - MU четвертого комму0

5

гатора 8 выставляется значение меньшего из UX и i. В элементе 21 сравнения происходит сравнение каждо- го разр.яда числа М с логической 1, так как число М подается в инверсном коде. Выходной сигнал элемента 21 сравнения; через инвертор 22 поступает на вход мультиплексора 20 и представляет собой сигнал переноса PJ, : при М О Р„ 1 ,при М О

Р 0. Импульсом FQ, поступаюЕЩМ с четвертого выхода блока 13 управле- ПИЯ на управляющий вход четвертого коммутатора 8, мультиплексор 20 переключается таким образом, чтобы входы

N

и

Рд, бЫПИ

подключены к

М - М

выходу четвертого коммутатора 8. ПерBbiM пришедшим с пятого выхода блоки

13

число М и

управления импульсом .знак Р

№

F (фиг.1) записываются в регистре 9 оценочной функции, а по первому импульсу Рц с первого выхода, блока 13 управления происходит вьшолнение первого шага интерполяции После окончания импульса Fg мульти-. гшексор 20 подключает выходы даи.пьп1 и знака блока 7 вычисления оценочной функции к входам данных и знака ре 1 истра 9 оценочной функции.

Работой блока 7 вычисления оценочной функции управляют второй 5 и третий 6 коммутаторы. Оценочная функ- 11ДЯ позволяет определять необходи . мость проведения или комбинированно- го шага по двум координатам или шага в направлении большей разности из Д X и. U Y. На вторые и первые входы третьего кo iмyтaтopa 8 соответственн поступают с выхода регистра 9 оценочной функции результаты циклических, вычислений блоком 7 вьгаисления оце- .ночной функции (код и)j ас выхода перового коммутатора 4 - код меньшего из UX и UY, На первы.е и вторые входы второго коммутатора 5 поступает код разности UZ и значения оценочной функции (код и). Цикличность вычислений осуществляется записью результатов вьгаислений числа U по сигналу F с пятого выхода блока 13 управления, которьм поступает на вход синхронизации регистра 9 оценочной функции.. ,

Работой второго 5 и третьего 6 KOM мутаторов управляет сигнал Ру. с выхода переноса старшего разряда слпмма- тора 18 блока 7 вычисления оценочной функции, которьй записан в регистр 9 оценочной функции. Первые и вторые входы сумматора 18 являются первыми и вторыми входами, а выходы инверторов 19.1-19.К-соответственно выходами данных блока 7 вычислений оценоч- Hofi функции, при этом выход переноса старшего разряда сумматора 18 подключен к входу переноса младшего разряда этого сумматора и является знаковым выходом блока 7 вычисления оценочной функции.

В том случае, когда Р 1 (U 0) , на вторые входы блока 7 вычисления оценочной функции поступает результат предыдущего цикла вычислений, а на первые входы - обратный код & Z. Если же Pjj О (ий 0), то на 0 вторые входы блока 7 вычисления оценочной функции поступает код меньшего из &. X и UY, а на первые входы - обратный код числа U.

5 ; Блок 13 управления служит для син- хронизации работы всех блоков интерполятора и работает следуюигим образом.

На вход делителя 31 частоты

0 (фиг. 7) поступает внешний сигнал с тактовой частотой F. Его. коэффи- деления подобран таким образом, чтобы интерполятор работал синфазно с внешним ОЗУ, в которое записывают5 ся с выхода устройства координаты

интерполируемых точек. С выхода делителя частоты деленная частота поступает на первый вход элемента 32 разрешения, на третий и второй йходы

0 которого подаются внешний сигнал раз-, решения интерполяции и сигнал Останов с вькода блока 12 сравнения. Частота F с вь)хода элемента 32 разрешения поступает на перзьй 33.1 и вто5 рой 33.2 мультивибраторы, .которые срабатьшают соответственно по заднему и переднему фронтам частоты F.. и формируют сигналы F, F,j, и F. Импульсные последовательности с час-f;

тотами Т..К F сдвинуты одна относительно другой на время, необходимое для расчета направления шага в блоке 7 и вычисления оценочной функции. На третьем выходе блока 13 управления, .соединенном с первым выходом второго мультивибратора 3. 2., формируется последовательность F(j (инверсная) . Сигнал разрешения интерполяции поступает также и на третий мультивибратор 33.3, который формирует импульс F на втором выходе блока 13 управления, по которому происходят начальная установка счетчиков в блоке 11 счетчиков адресных сигналов и сбро с триггеров 29.1 и 29„2 в блоке 12 сравнения (фиг.6). Импульс F также взво- ; дит триггер 24, выходной сигнал F которого поступает на четвертый выход блока 13 управления и является

1

управляюцщм сигналом для четвертого коммутатора 8. Временные диаграммы блока 13 управления представлены на фиг, 8.

Блок 10 формирования сигналов интерполяции работает следующим образом.

В интервале интерполяции на сигнальный вход стробирующего элемента 23 (фиг.5) поступают импульсы частоты Fy 5 а на его управляюгций вход поступает сигнал Pj со знакового выхода регистра 9 оценочной функции. На выход стробирующего элемента 23 импульсы частоты F проходят только в случае, когда Р 1 .

В зависимости от сигнала P.yj поступающего на управляюи ;ие входы первого 2А,1 и второго 24.2 коммутато- ров, на выходы этих коммутаторов проходят либо импульсы с выхода элемен- та 23 разрешения, либо импульсы частоты Fy, причем если на выходы первого коммутатора 24.1 проходят импуль- сы частотой FU, то на выход второго коммутатора 24.2 проходят импульсы с выхода элемента 23 разрешения

uZ ) наоборот (

Сигналы с выхода коммутатора

В случае, когда Рдх 1 импульсы с выхода первого коммутатора 24.1 проходят через первьй элемент И-НЕ 25.1, в случае Рдх через второй элемент И-НЕ 25.2.

Подобным же образом иьшульсы с выхода второго коммутатора 24.2 проходят через третий 25.3 или четвер- тый 25.4 элемент И-НЕ в зависимости от значения сигнала Рд.Выходы первого 25.1 и второго

И-НЕ соединены соответственно с вхо- дами прямого и обратного счета счетчика адресных сигналов по координате Y того же блока.

Первьй 26.1 и второй 26.2 инверторы, служат для получения парафазных сигналов PUX и Рд иТаким образом, в каждом интервале интерполяции на одном из выходов Fy и X или F|7 и X появляется последова; 48

.тельность импульсов, сформированная в направлении строчной развертки, а на одном из выходов FU Y и FJ Y-по- следовательность импульсов, сформированная в направлении кадровой развертки.

Блок 11 счетчиков адресных сигналов осуществляет формирование координат точек интерполируемой линии и работает следующим образом.

Перед первым расчетным шагом по сигналу из блока 13 управления производится запись начальных координат ХдИ . По результатам последующих расчетных шагов на выходах блока 10 формь рования сигналов интерполяции формируются импульсы, которые поступают с вькодов первого 25.1, второго 25.2, третьего 25.3 и четвертого 25.4 элементов И-НЕ на входы прямого и обратного счета счетчиков в блоке 11 счетчиков адресных сигналов. На выходах этих счетчиков формируются коды адреса интерполированной точки.

Блок 12 сравнения (фиг.6) служит для остановки процесса интерполяции пр достижении конечного значения координат X ц. и Y., и состоит из двух

а D

многоразрядных элементов, сравнения - 27.1 (по координате X) и 27.2 (по координате Y), на первые входы которых поступают текущие значения координаты с выходов счетчиков блока 11, счетчиков адресных сигналов, а на вторые - код конечного значения координаты интерполяции. При совпадении кодов текущего и конечного значений по каждой из координат X и Y на выходах многоразрядных элементов 27.1 и 27.2 сравнения формируются сигналы которые через элементы 28.1 или 28.2 стробирования взводят триггеры 28.1 и 28.2. Необходимость использования триггеров возникает в связи с возможностью неодновременного достижения конечной координаты по каналам X и Y. Сигналы с выходов триггеров 29.1 и 29.2 суммируются на элементе 30 совпадения и поступают на первый вход блока 13 управления. В начале следующего такта интерполяции триггеры сбрасываются в О по сигналу с второго выхода блока 13 управления.

Таким образом, введение новых блоков и их связей позволяет повысить быстродействие линейного интерполятора за счет уменьшения времени вы914

iiDJiiienHH первого шага путем замены, части арифметических операций по определению начального значения оценочной функпд1и на логические, а также обеспечивает расширение функцио- нальных возможностей интерполятора за счет формирования в устройстве координат точек в процессе интерполяции и сигнала останова по его окончании.

Формула изобретения

953/410

третьего коммутатора и выходами первого коммутатора, при этом вторые входы второго и третьего.коммутаторов g объединены и подключены к выходу данных регистра оценочной функции, входы данных и знаковый вход которого соединены соответственно с выходами , данных и знаковым выходом четверто0 го коммутатора, выходы третьего

коммутатора подключены к вторым входам блока вычисления оценочной функ- ции, первьй и второй входы блока формирования сигналов интерполяции соеди15 йены соответственно со знаковыми выхода- .ми первого и второго блоков суммирова- ния,третий вход соединен с управ- пяюищм входом третьего кo шyтaтopa и знаковым выходом регистра оценочной

0 функции, четвертый вход соединен с первым вькодом блока управления, а пятый вход соединен с управляющим вход.ом первого коммутатора и знако- вьм выходом третьего блока суммирова 5 Ш-1Я, вькоды блока формирования сигналов интерполяции подключены к счет- нът входам блока счетчиков адресных сигналов, первые и вторые информационные входы начальной установки которо0 го подключены соответственно к шинам данных начальных значений координат X и Y, первые и вторые выходы подклю чены соответственно к первым и вторьм входам блока сравнения, выход блока

35 сравнения соединен с первым входом блока управления, третьи и четвертые входы блока сравнения подключены соответственно к шинам конечных значений координат X и Y, пятьй вход блока

0 сравнения соединен с вторым выходом блока управления и управляющим входом начальной установки блока счетчиков адресных сигналов, третий выход блока управления соединен с шестым входом

5 блока сравнения, второй вход блока управления является входом тактовой частоты интерполятора, а третий вход- с входом сигнала разрешения интерполяции,, при этом четвертый выход бло0 ка управления подключен к управляющему .входу четвертого коммутатора, а пятый выход - к входу синхронизации регистра оценочной функции.

,

«{Ш

AN

ВМ

JS.fl

5

четвертый элементов И-НЕ являются | выходами блока.

UN

AXff

фиг. г

Bl

M,

KfcinaKlta ют(

tr

%.

ш

U1

«

UH

Фие.З

i/,

JTt/

UiLj

27

fii

fti

ID f.i

Ш

Zf.

fi/V

OcmoHol

Фиг 6

ЗлГ .«.от

вапвш

(у

t

te p %1J

(f

LJULJULi

Г1Г1ПППП1

о .е№йй81|« -« -- --

Г

J

Fo

| СТАНОК ДЛЯ ИЗГОТОВЛЕНИЯ ГНУТЫХ КОЛЕНЧАТЫХ ВАЛОВ | 1925 |

|

SU5546A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Линейный интерполятор | 1980 |

|

SU920636A2 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1988-11-23—Публикация

1987-04-20—Подача