53о

OS9

(Л

со :р

о:

00

стре 2 на основе анадиза поля признаков дешифратором 4 и выработки распределителем 10 импульсов сигнала,- определяющего адрес блока 7 памяти, в котором хранятся адреса блока 6, Сообщения считываются вычислительным комплексом из блока 6 и результаты

обработки сообщений заносятся в блок 9 памяти. Обращение абонентов к полученным результатам проводится через входы 52 запросов, на основании которых соответствующие результаты выдаются абонентам через группы эле- bfeHTOB И 21 - 23, 3 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для информационного поиска | 1988 |

|

SU1587543A2 |

| Устройство для информационного поиска | 1989 |

|

SU1608694A2 |

| СИСТЕМА ЭЛЕКТРОННОГО ДИСТАНЦИОННОГО SMS-ГОЛОСОВАНИЯ | 2010 |

|

RU2421813C1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ РАСПРЕДЕЛЕНИЕМ ДАННЫХ В ИНФОРМАЦИОННОЙ СЕТИ КЛИЕНТ-СЕРВЕР | 2001 |

|

RU2218595C2 |

| ИНФОРМАЦИОННАЯ СИСТЕМА СЛЕЖЕНИЯ ЗА ХОДОМ ГОЛОСОВАНИЯ ИЗБИРАТЕЛЕЙ | 2005 |

|

RU2293370C1 |

| Устройство для контроля знаний обучаемых | 1989 |

|

SU1679523A1 |

| Устройство для управления вызовом информации | 1988 |

|

SU1603363A1 |

| Устройство для управления передачей данных | 1986 |

|

SU1381569A1 |

| СИСТЕМА ИНФОРМАЦИОННОГО ВЗАИМОДЕЙСТВИЯ ИНФОРМАЦИОННО-МАРКЕТИНГОВЫХ ЦЕНТРОВ В ИНТЕГРИРОВАННОЙ ИНФРАСТРУКТУРЕ ЭЛЕКТРОННОЙ ТОРГОВЛИ | 2004 |

|

RU2271572C1 |

| СИСТЕМА УПРАВЛЕНИЯ РАСПРЕДЕЛЕНИЕМ ДАННЫХ В СЕТИ ИНФОРМАЦИОННО-АНАЛИТИЧЕСКОГО ЦЕНТРА | 2005 |

|

RU2291481C1 |

Изобретение относится к вычислительной технике и может использоваться в автоматизированных информационно-справочных системах. Цель изобретения - повьппение быстродействия. Сообщения, поступающие в регистр 1, содержат поля признаков и данных. Поле данных записывается в блок 6 памяти по адресам, сформированным в реги

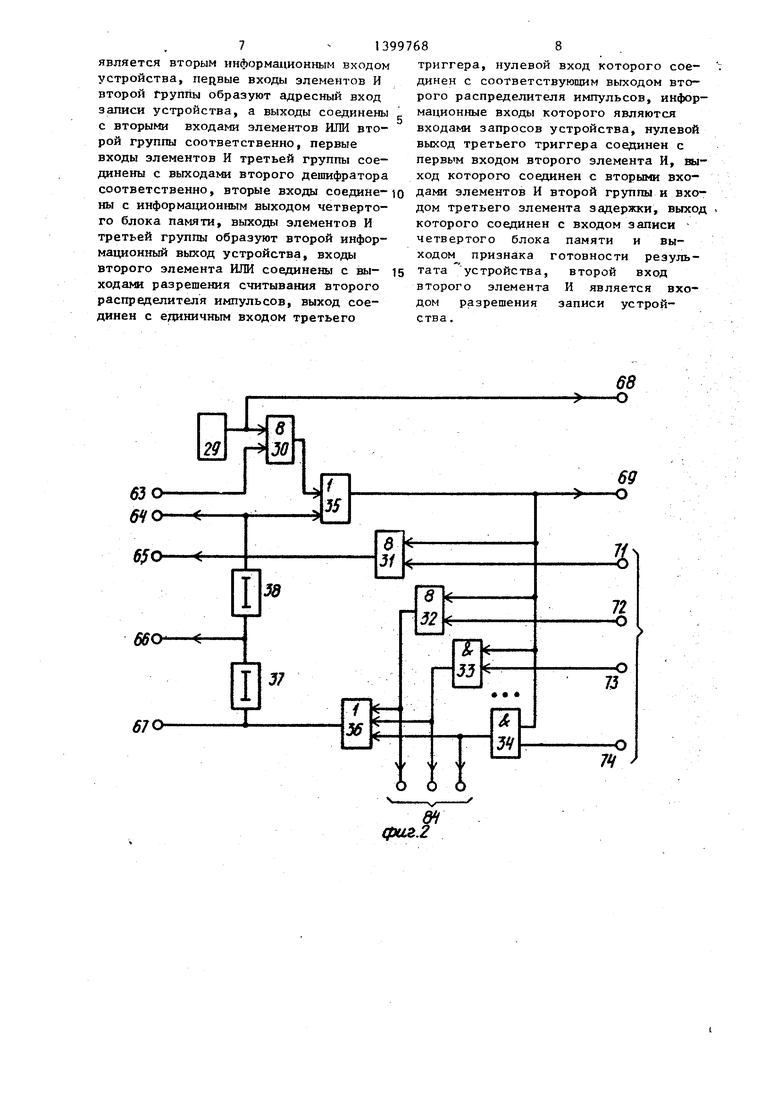

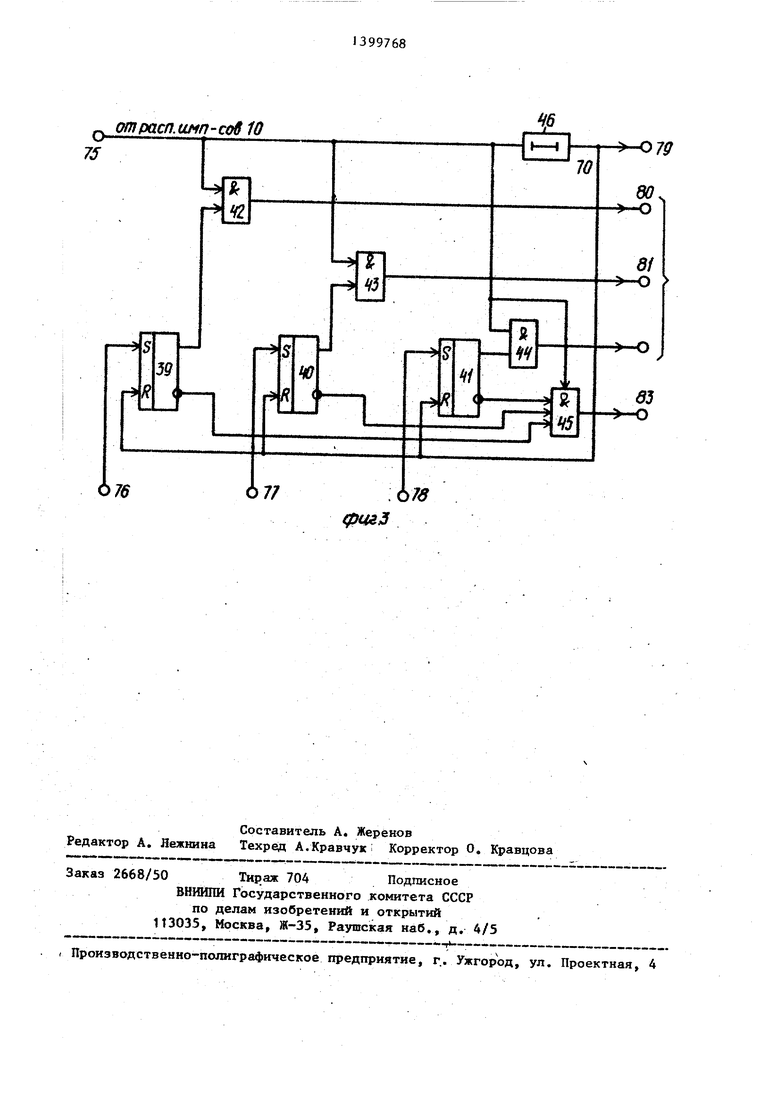

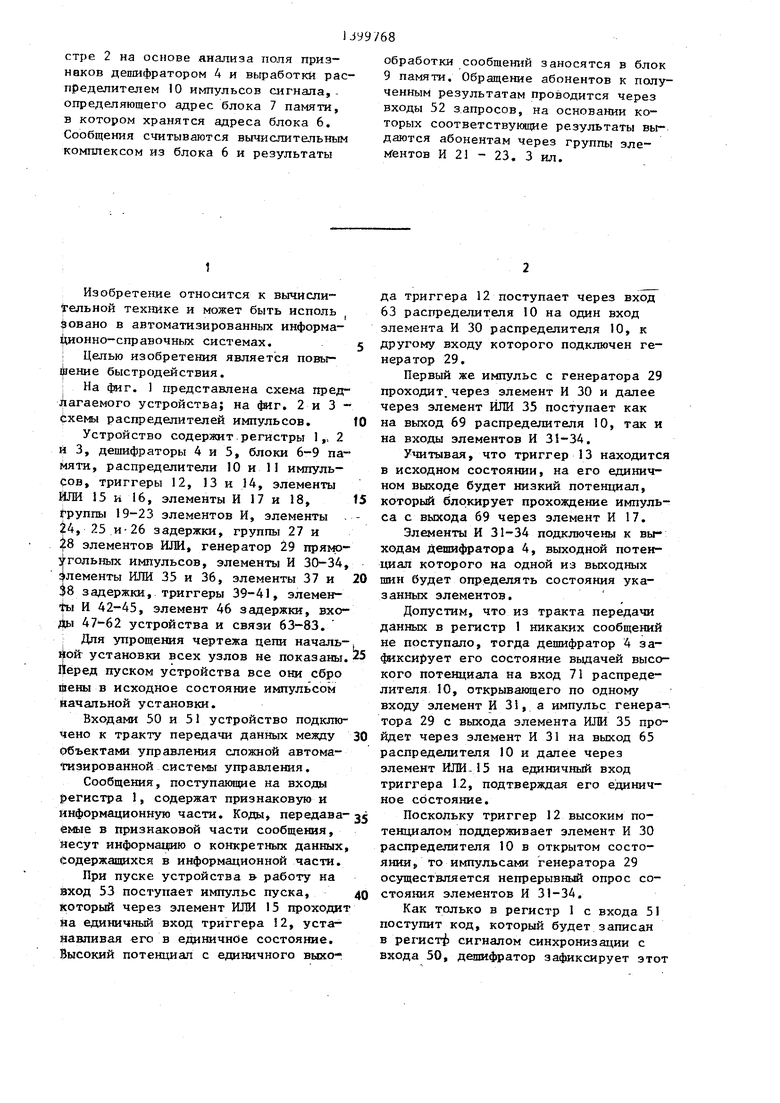

Изобретегще относится к вычисли™ Цельной технике и может быть исполь $овано в автоматизированных информа- ионно-справочных системах. Целью изобретения является повы- 1 1ение быстродействия. ; На фиг. 1 представлена схема пред- jkaraeMoro устройства; на фиг. 2 и 3 - фхемы распределителей импульсов.

Устройство содержит регистры 1,. 2 и 3, дешифраторы 4 и 5, блоки 6-9 памяти, распределители 10 и II импуль- сов, триггеры 12, 13 и 14, элементы ИЛИ 15 и 16, элементы И 17 и 18, f pynrbi 19-23 элементов И, элементы $4, 25 и-26 задержки, группы 27 и |8 элементоЕ ИЛИ, генератор 29 прямо- гольных импульсов, элементы И 30-34, : лементы РШИ 35 и 36, элементы 37 и $8 задержки, триггеры 39-41, элемен ibi И 42-45, элемент 46 задержки, вхо- 4ы 47-62 устройства и связи 63-83.

Для упрощения чертежа цепи началь О1л: установки всех узлов не показаны Перед пуском устройства все они сбро йены в исходное состояние импульсом Начальной установки.

Входами 50 и 51 устройство подключено к тракту передачи данных между объектами управления сложной автоматизированной системы управления.

Сообщения, поступакщие на входы регистра 1, содержат признаковую и информационную части. Коды, переданаемые в признаковой части сообщения, Яесут информацию о конкретных данных содержащихся в информационной части. При пуске устройства в работу на вход 53 поступает импульс пуска, который через элемент ИЛИ 15 проходи На единичный вход триггера 12, устанавливая его в единичное состояние. Высокий потенциал с единичного выхода триггера 12 поступает через вход 63 распределителя 10 на один вход элемента И 30 распределителя 10, к другому входу которого подключен генератор 29.

Первый же импульс с генератора 29 проходит,через элемент И 30 и далее через элемент ИЛИ 35 поступает как на выход 69 распределителя 10, так и на входы элементов И 31-34.

Учитывая, что триггер 13 находится в исходном состоянии, на его единичном выходе будет низкий потенциал, который блокирует прохождение импульса с выхода 69 через элемент И 17.

Элементы И 31-34 подключены к выходам дешифратора 4, выходной потенциал которого на одной из выходных шин будет определять состояния указанных элементов.

Допустим, что из тракта передачи данных в регистр 1 никаких сообщений не поступало, тогда дешифратор 4 за- 4иксирует его состояние выдачей высокого потенциала на вход 71 распределителя 10, открывающего по одному входу элемент И 31, а импульс генератора 29 с выхода элемента ИЛИ 35 пройдет через элемент И 31 на выход 65 распределителя 10 и далее через элемент ИЛИ-15 на единичный вход триггера 12, подтверждая его единичное состояние.

Поскольку триггер 12 высоким потенциалом поддерживает элемент И 30 распределителя 10 в открытом состоянии, то импульсами генератора 29 осуществляется непрерывный опрос состояния элементов И 31-34.

Как только в регистр 1 с входа 51 поступит код, который будет записан в регист; сигналом синхронизации с входа 50, дешифратор зафиксирует это

момент вьщачей высокого потетшапа на одном КЗ других выходов. Допустим, высокий потенциал поступил на вход 72 распределителя 10. Этот потенциал открывает элемент И 32, через который импульс генератора 29 с выхода элемента ИЛИ 36 проходит как на выход 84 распределителя 10 непосредственно, так и через элемент ИЛИ 36 на выход 67 и далее на нулевой вход триггера 12, сбрасывая его в исходное состояние,

С выхода 84 распределителя 10 импульс опроса поступает на вход фикси- IB равлёЬия записью, который поступает

рованной ячейки памяти блока 7, выполненного в виде постоянного запоминающего устройства (ПЗУ), где хранится начальньй адрес той зоны памяти, куда необходимо записать входную информацию с регистра 1,

Содержимое фиксированной ячейки переписывается из блока 7 в. регистр 2, выходы которого через элементы ИЛИ 27 соединены с адресным входом блока 6.

Параллельно тот же импульс с выхода элемента И 36, задержанный элементом 37 задержки на время формирования адреса в регистре 2, с выхода 66 распределителя поступает на вход записи блока 6, записывая входные сообщения по указанному адресу.

После записи сообщения тот же импульс с выхода элемента 37 задержки поступает на вход элемента 38 задеряр ки, где задерживается на время записи сообщения и поступает как на сброс в исходное состояние регистра 2 и триггера 13 с выхода 64 распределителя, так и на очередной опрос cocтoяkия элементов И 31-34.

Выход блока 6 памяти через выход 59 соединен с вычислительным комплексом (ВК) объекта управления (не показан), К непрерывно с заданньач интервалом опроса опрашивает блок 6 импулЬ сами опроса, по ступ акяцими на вход 55, Эти импульсы устанавливают триггер 13 в единичное состояние, при котором он высоким потенциалом открывает элемент И 17. Импульс опроса поступает на элемент И 17 с выхода 69 распределителя )0 в начале цикла опроса. Этот импульс проходит через элемент И 17 на вход элемента И I9 устанавливая адрес считываемого со- . общения, и через элемент 25 задержки, который задерживает импульс на время установки адреса, на ьход управления считыванием блока 6, с выхода которого информация поступает на вы- ход 59.

В ВК эти данные испальз тотся в качестве входных данных для решения установленного перечня задач, по мере решения которых полученные результаты в виде соответствующих справок выдаются на вход 56 и дапее на вход блока 9 памяти. Кроме того, на вход 57 подается адрес записи полученной справки, а на вход 58 - импульс уп

на один из входов элемента И 18, который по другому входу управляется триггером 14.

Запись информации в блок 9 осуществляется только тогда, когда триггер 14 находится в нулевом состоянии, которое фиксирует тот факт, что прямого обращения от пользователей к блоку 9 в настоящий момент времени нет. В этом случае импульс, пройдя элемент И 18, поступает на вход элементов И 20, устанавливая адрес записи с входа 57, и через элемент 26 задержки, который задерживает импульс на время установки адреса, на вход управления записью блока 9, осуществляя запись результата, полученного от ВК.

Кроме того, этот же импульс с выхода 47 поступает на вход прерывания ВК, сигнализируя о том, что запись результата осуществлена.

Обращение за справками, хранящимися в блоке 9, осуществляется с рабочих мест должностных лиц различных объектов управления через входы 52 (фиг. 1) систе и далее через входы 76-78 распределителя 11 (фиг. 3).

Допустим, запрос поступил на вход 76 распределителя П (фиг. 3). Тогда импульс запроса устанавливает триггер 39 распределителя в единичное состояние, при котором он своим высоким потенциалом открывает элемент И 42, на другой вход которого с входа 75 поступает импульс генератора 29 с зилхода 68 распределителя 10.

Этот импульс проходит через зле- gg мент И 42 и далее через выход 80 распределителя 1I поступает на входы .блока 8 памяти и элемента ИЛИ 16. Пройдя элемент ИЛИ 16, импульс поступает на единичный вход триггера .

Ь4 устянавливая его в единичное со- , и снимает тем самым высокий потенциал с элемента И 18.

Параллельно с этим импульс с выхода 80 распределителя 11 поступает на вход считывания соответствующей фиксированной ячейки блока 8, выполнеи- :ного в виде постоянного запоминаю- щего устройства, где хранятся адрес 1абонента, запрашивающего справку, и адрес зоны памяти, где хранится за- Ьрашиваемая справка. I Считанный код с блока 8 поступает в регистр 3, откуда код адреса або- 1нента подается на вход дешифратора 5 который в соответствии с входным ко- |цом открывает соответствующие элемен- |ты И 21-23, а код адреса зоны памяти

|через элементы ИЛИ 28 подается на ад- jo го блока памяти и вход первого эле есный вход блока 9.

; Параллельно с этим импульс генера- гора 29, поступивший на вход 75 рас- гределителя II, задерживается элемен- гом 46 задержки на время формирования Ццреса считывания блока 9 и с выхода 79 распределителя 1 1 поступает на Вход считывания блока 9, считывая Данные из зоны памяти через соответствующие элементы 21-23 на выходы 60- 30 дены группь элементов И, группы эле- 62, далее они передаются тому абонен-- ментов ИЛИ и второй дешифратор, вход ty, который их запрашивает.

Этот же импульс с выхода 79 распределителя 11 после задержки элементом

которого соединен с выходом третьего регистра, выходы разрядов второго регистра соединены с первыми входами

4 на время считывания данных из бло- wg элементов ИЛИ первой группы соответ ka. 9 поступает на вход регистра 3 и устанавливает его в исходное состоя- йие, подготавливая к новому циклу ра- фоты.

формулаизобретения

Устройство для информационного Поиска, содержащее регистры, триггеры, Элементы И, ИЛИ и задержки, четыре блока памяти, первый дешифратор и два распределителя импульсов, причем информационный вход первого регистра Является первым информационным вхоственно, выходы которых соединены с адресным входом первого блока памяти, выход которого является первым инфор мационным выходом устройства, первые

40 входы элементов И первой грухшы являются адресным входом устройства, первый вход первого элемента И соединен с соответствующим выходом первого распределителя импульсов, выход

g первого элемента И соединен с вторыми входами элементов И первой группы и через второй элемент задержки с входом считывания первого блока памяти, единичный вход второго триггера являДом устройства, выход разрядов призна/сд ется входом опроса устройства, нулеKOB первого регистра соединен с входом первого дещифратора, выход разрядов данных первого регистра соеди- rteH с информационным входом первого блока памяти, выходы первого дешифратора соединены с установочными входами первого распределителя импуль- doB, разрешающий вход которого соединен с выходом первого триггера, вы55

вой вход соединен с установочным входом второго регистра, единичный выход вторс/го триггера соединен с вторым входом первого элемента И, выход третьего регистра соединен с первыми входами элементов ШШ второй группы, выходы которых соединены с адресным входом четвертого блока памяти, информационный вход которого

ходы первого распределителя импульсов соединены с тактовым входом второго распределителя импульсов, входом записи первого блока памяти,

адресным входом второго блока памяти, нулевым входом первого триггера, установочньп входом второго регистра и первым входом первого элемента ИЛИ

соответственно, выход второго блока памяти соединен с информационным входом второго регистра, второй вход первого элемента ИЛИ является входом пуска устройства, а выход соединен с

единичным входом первого триггера, входы считывания третьего блока памяти соединены с выходами разрешения считывания второго распределителя импульсов, вход считывания четвертомёнта задержки соединены с соответствующими выходами второго распределителя импульсов, выход третьего блока памяти соединен с информационным входом третьего регистра, установочный вход которого соединен с выходом первого элемента задержки, отличающееся тем, что, с целью повьшения быстродействия, в него введены группь элементов И, группы эле- ментов ИЛИ и второй дешифратор, вход

которого соединен с выходом третьего регистра, выходы разрядов второго регистра соединены с первыми входами

ственно, выходы которых соединены с адресным входом первого блока памяти, выход которого является первым информационным выходом устройства, первые

входы элементов И первой грухшы являются адресным входом устройства, первый вход первого элемента И соединен с соответствующим выходом первого распределителя импульсов, выход

первого элемента И соединен с вторыми входами элементов И первой группы и через второй элемент задержки с входом считывания первого блока памяти, единичный вход второго триггера является входом опроса устройства, нуле

вой вход соединен с установочным входом второго регистра, единичный выход вторс/го триггера соединен с вторым входом первого элемента И, выход третьего регистра соединен с первыми входами элементов ШШ второй группы, выходы которых соединены с адресным входом четвертого блока памяти, информационный вход которого

является вторым информационным входом устройства, пецвые входы элементов И второй группы образуют адресный вход записи устройства, а выходы соединены с вторыми входами элементов ИЛИ второй группы соответственно, первые входы элементов И третьей группы соединены с выходами второго дешифратора соответственно, вторые входы соедине- ны с информационным выходом четвертого блока памяти, выходы элементов И третьей группы образуют второй информационный выход устройства, входы второго элемента ИЛИ соединены с вы- ходами разрешения считывания второго распределителя импульсов, выход соединен с единичным входом третьего

триггера, нулевой вход которого соединен с соответствующим выходом второго распределителя импульсов, информационные входы которого являются входами запросов устройства, нулевой выход третьего триггера соединен с первьтм входом второго элемента И, выход которого соединен с вторыми входами элементов И второй группы и входом третьего элемента задержки, выход которого соединен с входом записи - четвертого блока памяти и выходом признака готовности результата устройства, второй вход второго элемента И является входом разрешения записи устройства.

фиг

f

| Патент США № 4298930, кл | |||

| Способ получения мыла | 1920 |

|

SU364A1 |

| Патент США 4300193, ;кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-05-30—Публикация

1986-12-08—Подача