Изобретение относится к вычислительной технике и может быть использовано в аналого-цифровых вычислительных и управляющих системах и уст-с ройствах.

Цель изобретения - расширение функциональных возможностей за счет одновременного формирования инвертированных и неинвертированных значтенийю трехфазного сигнала.

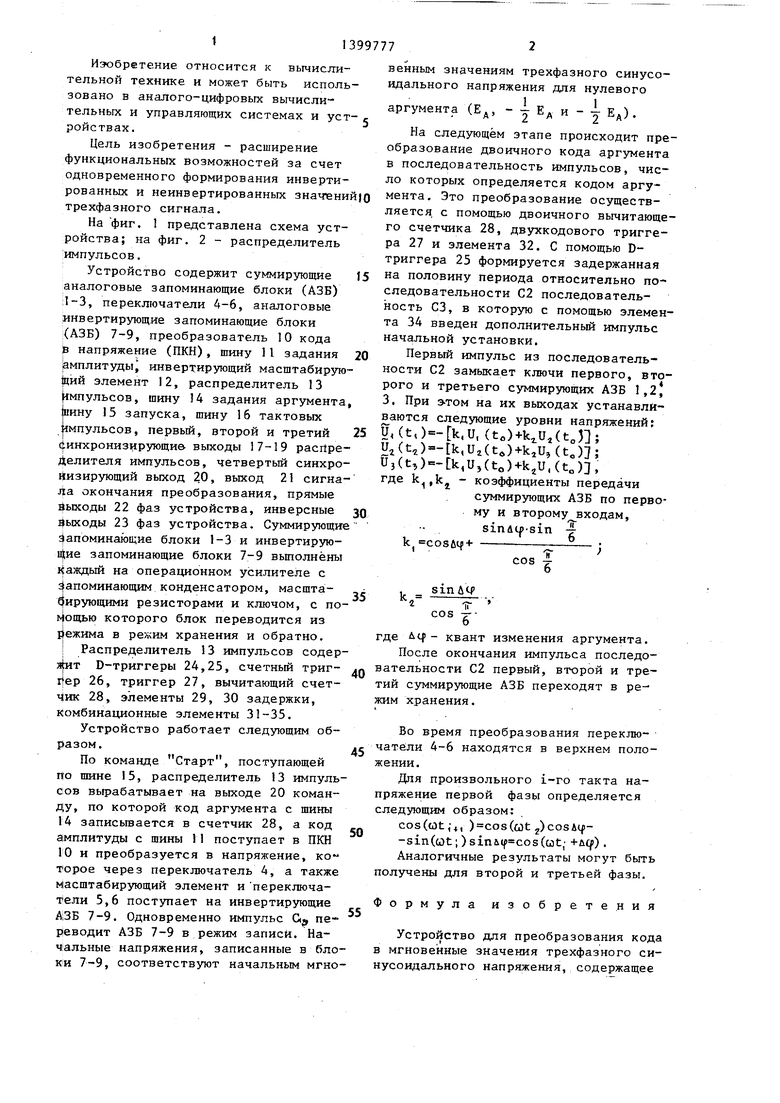

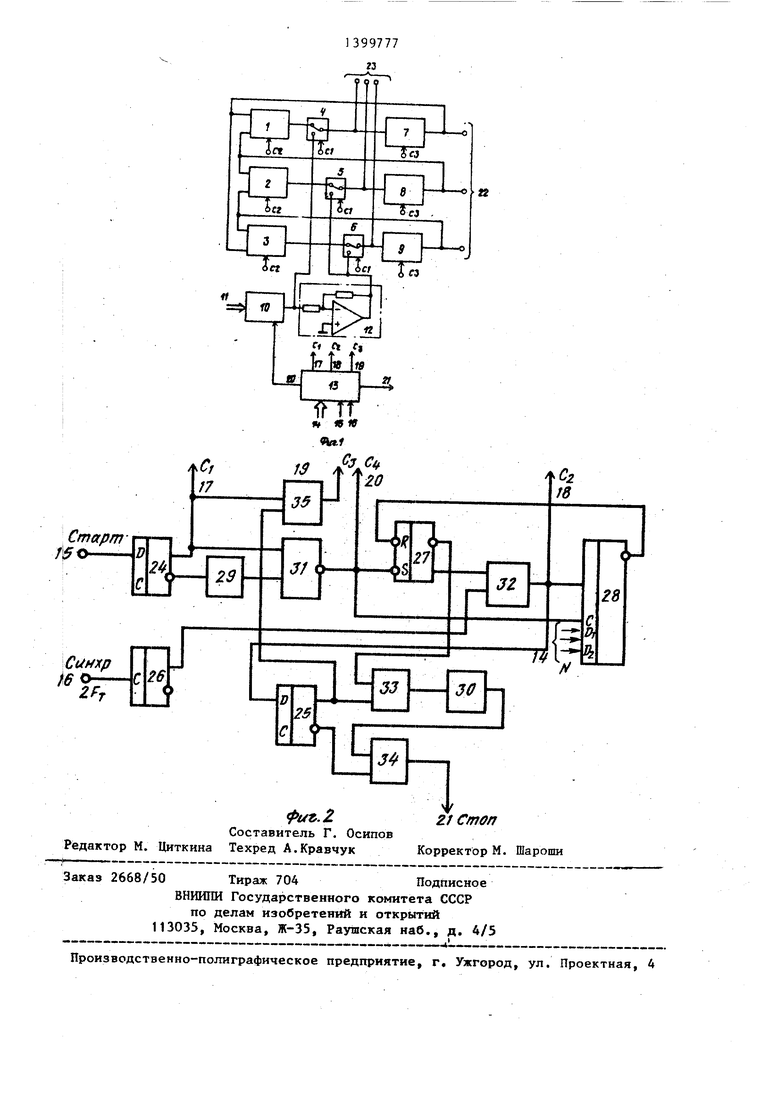

На фиг. 1 представлена схема устройства; на фиг, 2 - распределитель ;импульсов.

Устройство содержит суммирзпощие 15 аналоговые запоминающие блоки (АЗБ) ;1-3, переключатели 4-6, аналоговые инвертирующие запоминающие блоки :(АЗБ) 7-9, преобразователь 10 кода В напряжение (ПКН), шину 1I задания 20 мплитуды инвертирующий масштабируто- |ций элемент 12, распределитель 13 Цмпульсов, шину 14 задания аргумента, (пину 15 запуска, шину 16 тактовых

венным значениям трехфазного идального напряжения для нул

аргумента (Ед, - 2- Ед и - -2

На следующем этапе происх образование двоичного кода а в последовательность импульс ло которых определяется кодо мента. Это преобразование ос ляется, с помощью двоичного в го счетчика 28, двухкодового ра 27 и элемента 32. С помощ триггера 25 формируется заде на половину периода относите следовательности С2 последов ность СЗ, в которую с помощь та 34 введен дополнительный начальной установки.

Первый импульс из последо ности С2 замыкает ключи перв рого и третьего суммирующих 3. При Э.ТОМ на их выходах ус ваются следующие уровни напр

1мпульсов, первый, второй и третий 25 Ц (t, ), U, (to)(to J3

Синхронизирующие выходы 17-19 pacrtpe- Делителя импульсов, четвертый синхро- йизирующий выход 20, выход 21 сигнала окончания преобразования, прямые ыходы 22 фаз устройства, инверсные ЗО Зыходы 23 фаз устройства. Суммирующие Запоминающие блоки 1-3 и инвертирую- яе запоминающие блоки 7-9 выполнены к аждый на операционном усилителе с Запоминающим конденсатором, масщта- - 4ирующими резисторами и ключом, с по- 14ощью которого блок переводится из р|ежима в режим хранения и обратно. I Распределитель 13 импульсов содер- я|ит D-триггеры 24,25, счетный триг- д rjep 26, триггер 27, вычитающий счетчик 28, элементы 29, 30 задержки, комбинационные элементы 31-35.

Устройство работает следующим образом.

По команде Старт, поступающей По шине 15, распределитель 13 импульсов вырабатывает на выходе 20 команду, по которой код аргумента с шины 14 записьшается в счетчик 28, а код амплитуды с шины 11 поступает в ПКН 10 и преобразуется в напряжение, ко topoe через переключатель А, а также масштабирующий элемент и переключатели 5,6 поступает на инвертирующие 7-9. Одновременно импульс G переводит АЗБ 7-9 в режим записи. На- Ч альные напряжения, записанные в блоки 7-9, соответствуют начальным мгноUj(4),Uz(t)-t-k,U, (tJJ; Uj(t,),U,(tJ+k,U,(tJ3, где k.kj, - коэффициенты пер

суммирующих АЗБ

k cosuif «

му и второму вхо sinu(-sin -jcos i- b

45

50

55

. sin Atf

г- -r cos -r- b

где itp квант изменения аргу

После окончания импульса п вательности С2 первый, второй тий суммирующие АЗБ переходят жим хранения.

Во время преобразования пе чатели 4-6 находятся в верхн жении.

Для произвольного i-ro так пряжение первой фазы определ следующим образом:

cos((0t , 4, )cos(6)t cosAif-sin(cot;)sini((ot; +u(f

Аналогичные результаты мо получены для второй и третье

Формула изобрет

Устройство для преобразов в мгновенные значения трехфа нусоидального напряжения, сод

венным значениям трехфазного синусоидального напряжения для нулевого

аргумента (Ед, - 2- Ед и - -2 Ед) .

На следующем этапе происходит преобразование двоичного кода аргумента в последовательность импульсов, число которых определяется кодом аргумента. Это преобразование осуществляется, с помощью двоичного вычитающего счетчика 28, двухкодового триггера 27 и элемента 32. С помощью D- триггера 25 формируется задержанная на половину периода относительно последовательности С2 последовательность СЗ, в которую с помощью элемента 34 введен дополнительный импульс начальной установки.

Первый импульс из последовательности С2 замыкает ключи первого, второго и третьего суммирующих АЗБ 1,2, 3. При Э.ТОМ на их выходах устанавливаются следующие уровни напряжений:

Ц (t, ), U, (to)(to J3

Ц (t, ), U, (to)(to J3

Uj(4),Uz(t)-t-k,U, (tJJ; Uj(t,),U,(tJ+k,U,(tJ3, где k.kj, - коэффициенты передачи

суммирующих АЗБ по первоk cosuif «

му и второму входам, sinu(-sin -jcos i- b

. sin Atf

г- -r cos -r- b

где itp квант изменения аргумента.

После окончания импульса последовательности С2 первый, второй и третий суммирующие АЗБ переходят в ре- жим хранения.

Во время преобразования переключатели 4-6 находятся в верхнем положении.

Для произвольного i-ro такта напряжение первой фазы определяется следующим образом:

cos((0t , 4, )cos(6)t cosAif-sin(cot;)sini((ot; +u(f) .

Аналогичные результаты могут быть получены для второй и третьей фазы.

Формула изобретения

Устройство для преобразования кода в мгновенные значения трехфазного синусоидального напряжения, содержащее

первый и вторбй суммирующие аналоговые запоминающие блоки, выходы которых соединены с первыми входами первого и второго переключателей, выходы которых соединены с входами соответственно первого и второго инвертирующих аналоговых запоминающих блоков, выход первого инвертирующего аналогового запоминающего блока, являющийся прямым выходом первой фазы устройства, соединен с первым входом первого

суммирующего аналогового запоминающего блока, выход второго инвертирующего аналогового запоминающего блока, являющийся прямым выходом второй фазы устройства, coeд ffleн с первым входом второго и с вторым входом первого суммирующих аналоговых запоминающих блоков, преобразователь кода в напря- жение, информационный вход которого соединен с шиной задания амплитуды, а выход - с вторым входом первого переключателя, распределитель импульсов, информационный вход которого соединен с щиной задания аргумента, синхронизирующий вход - с шиной тактовых импульсов, вход запуска - с щиной запускающего импульса, первый, второй и третий синхронизирующие выходы распределителя импульсов соединены соответственно с управляющими входами переключателей, с управляющими .входами суммирующих аналоговых запоминающих блоков и с управляющими входами инвертирующих аналоговых запоминающих блоков, четвертый синхронизирующий выход - с входом запуска преобразователя кода в напряжение, а пятый выход является выходом сигнала окончания преобразования устройства

5

5

0

отличающееся тем, что, с целью расширения функциональных возможностей за счет одновременного формирования инвертированных и неинвертированных значений трехфазного сигнала, устройство содержит третий инвертирующий и третий суммирующий аналоговые запоминающие блоки, третий

0 переключатель и инвертирующий масшта- . бирующий элемент, при этом выход третьего суммирующего аналогового запо- нающего блока соединен с первым входом третьего переключателя, первый и вто рой входы третьего суммирующего аналогового запоминающего блока сое- динены с выходами соответственно первого и третьего инвертирующих аналоговых запоминающих блоков, выход последнего из которых, являющийся прямым выходом третьей фазы устройства, соединен также с вторым входом второго суммирующего аналогового запоминающего блока, выход преобразователя кода в напряжение через инвертирующий масштабирующий элемент соединен с вторыми входами второго и третьего переключателей, выход третьего переключателя соединен с входом третьего инвертирующего аналогового запоминающего блока, управляющие входы третьего переключателя, третьего суммирующего и третьего инвертирующего аналоговых запоминающих блоков соединены соответственно с первым, вторым и третьим синхронизирующими выходами распределителя импульсов, при этом выходы первого, второго и третьего переключателей являются инверсными

0 выходами соответствующих фаз устройства.

0

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1988 |

|

SU1589395A1 |

| Устройство для синусно-косинусного преобразования кода в напяжение | 1982 |

|

SU1089588A1 |

| Устройство для измерения параметров трехфазной сети | 1985 |

|

SU1307396A1 |

| Многофункциональный преобразователь | 1985 |

|

SU1267443A1 |

| Программируемый генератор импульсов | 1984 |

|

SU1248029A1 |

| Преобразователь угловых перемещений в код | 1985 |

|

SU1311024A1 |

| Программируемый генератор импульсов | 1985 |

|

SU1298869A2 |

| Система управления вибростендом | 1985 |

|

SU1305649A1 |

| Функциональный преобразователь | 1976 |

|

SU610137A1 |

| Статистический анализатор конечной разности фазы сигнала | 1988 |

|

SU1553919A1 |

Изобретение относится к вычислительной технике и может быть использовано в аналого-ц1Ф} р0вых вычислительных и управляющих системах и устройствах. Цель изобретения - расширение функциональных возможностей за счет одновременного формирования инвертированных и неинвертировэнных значений трехфазного сигнала. Устройство содержит суммирующие аналоговые запоминающие блоки 1-3, переключатели 4-6, инвертирующие аналоговые запоминающие блоки 7-9, преобразователь 10 кода в напряжение, щину 11 задания амплитуды, инвертир ощий масщтабирующий элемент 12, распределитель 13 импульсов, шину 14 задания аргумента, шину 15 запуска, шину 16 тактовых импульсов. Распределитель импульсов 13 вырабатывает импульсов, управляющих про-g цессами записи-перезаписи напряжений в запсжииаюцих блоках. Число управляющих ютульсов соответствует коду аргумента. 2 ил. (/ С

| Устройство для формирования гармонических колебаний | 1984 |

|

SU1231499A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для синусно-косинусного преобразования кода в напяжение | 1982 |

|

SU1089588A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-05-30—Публикация

1986-12-30—Подача