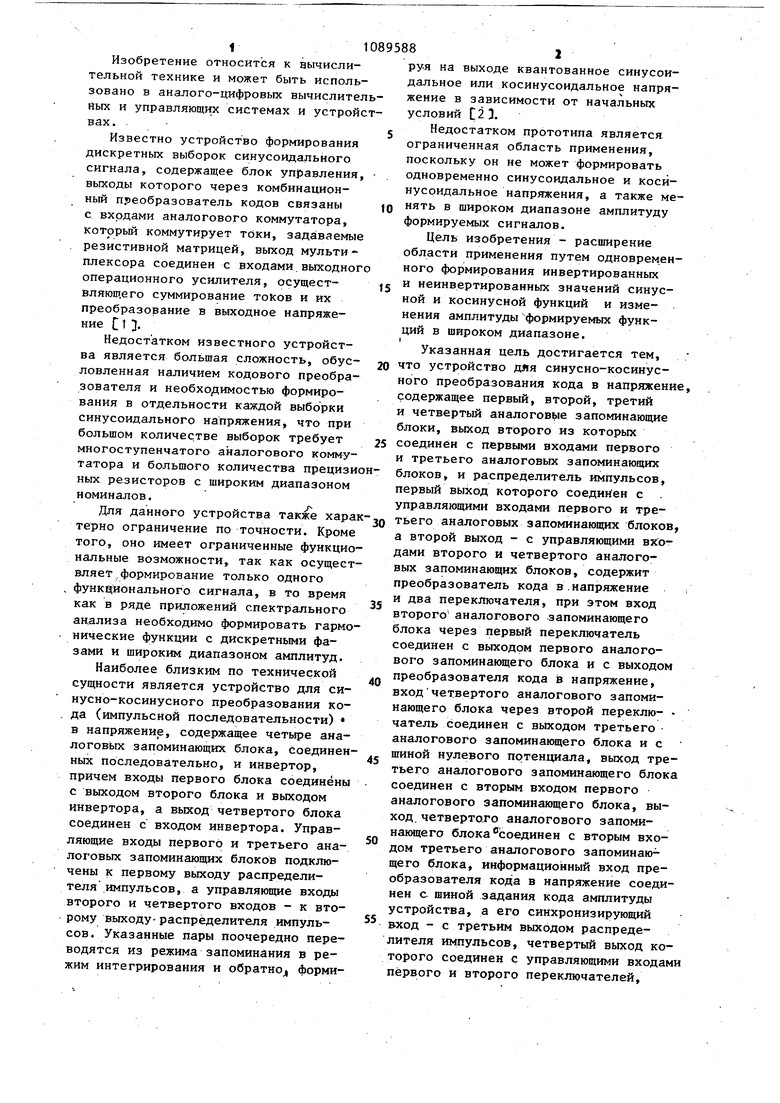

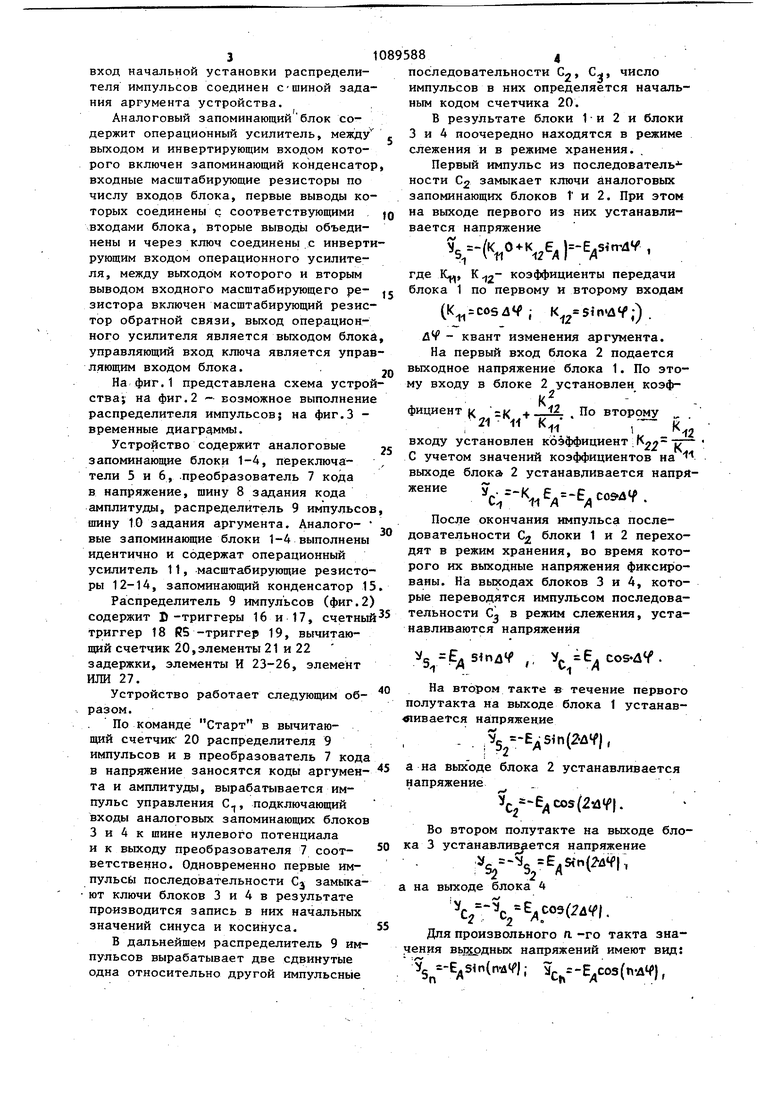

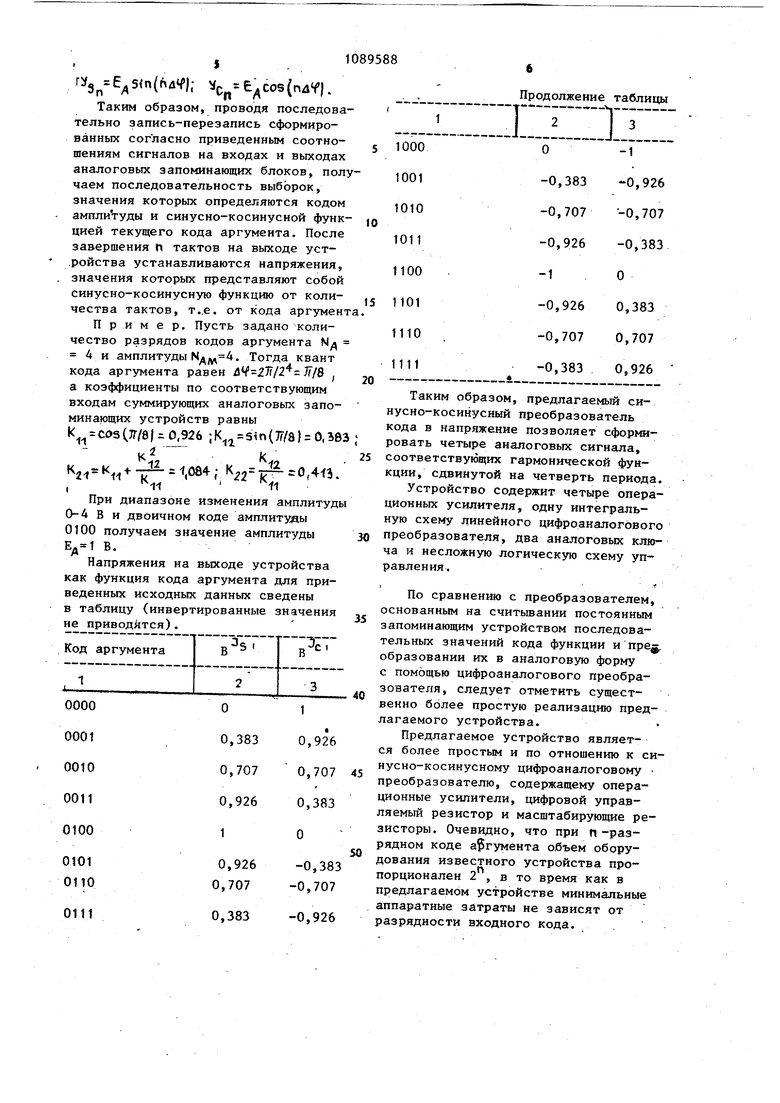

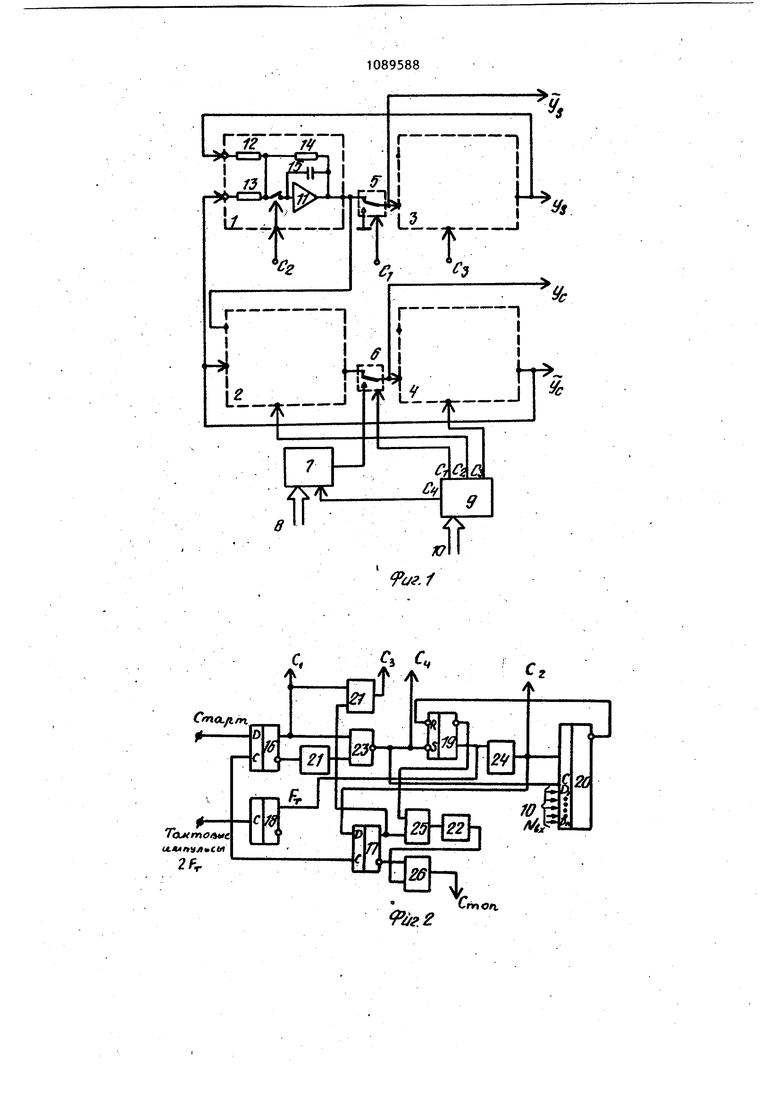

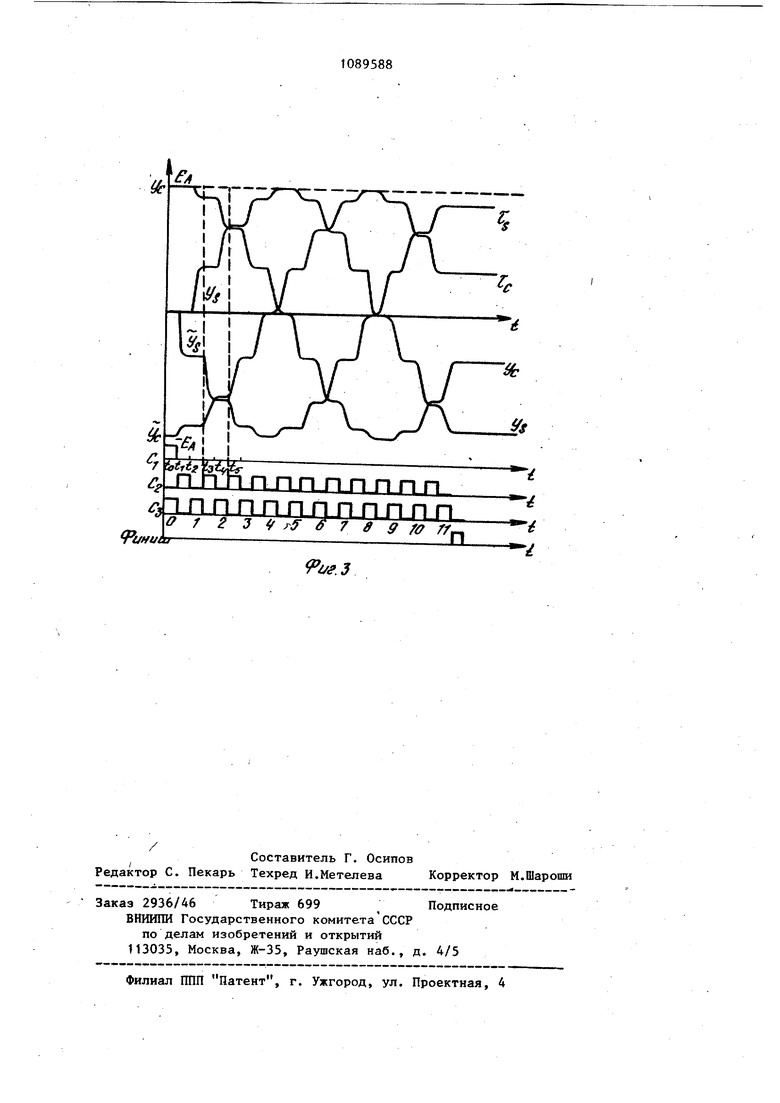

1 Изобретение относится к вычислительной технике и может быть исполь зовано в аналого-цифровых вычислител ных и управляющих системах и устрой вах. Известно устройство формирования дискретных выборок синусоидального сигнала, содержащее блок управления выходы которого через комбинационный преобразователь кодов связаны с входами аналогового коммутатора, который коммутирует тезки, задаваемые резистивной матрицей, выход мультиплексора соединен с входами.выходног операционного усилителя, осуществляющего суммирование токов и их преобразование в выходное напряжение С1 1. Недостатком известного устройства является большая сложность, обусловленная наличием кодового преобразователя и необхор(имостью формирования в отдельности каждой выборки синусоидального напряжения, что при большом количестве выборок требует многоступенчатого аналогового коммутатора и большого количества прецизи ных резисторов с широким диапазоном номиналов. Для данного устройства также хара терно ограничение по точности. Кроме того, оно имеет ограниченные функцио нальные возможности, так как осущест вляет .формирование только одного функционального сигнала, в то время как в ряде приложений спектрального анализа необходимо формировать гармо нические функции с дискретными фазами и широким диапазоном амплитуд. Наиболее близким по технической сущности является устройство для синусно-косинусного преобразования кода (импульсной последовательности) « в напряжение, содержащее четыре аналоговь1Х запоминающих блока, Соединен ных последовательно, и инвертор, причем входы первого блока соединены с выходом второго блока и выходом инвертора, а выход четвертого блока соединен с входом инвертора. Управляющие входы первого и третьего аналоговых запоминающих блоков подключены к первому выходу распределителя импульсов, а управляющие входы второго и четвертого входов - к второму выходу-распределителя импульсов. Указанные пары поочередно переводятся из режима запоминания в режим интегрирования и обратно,, форми8руя на выходе квантованное синусоидальное или косинусоидальное напряжение в зависимости от начальных условий С 2 3. Недостатком прототипа является ограниченная область применения, поскольку он не может формировать одновременно синусоидальное и косинусоидальное напряжения, а также менять в широком диапазоне амплитуду формируемых сигналов. Цель изобретения - расширение области применения путем одноврем.енного формирования инвертированных и неинвертированных значений синусной и косинусной функций и изменения амплитуды формируемых функций в широком диапазоне. Указанная цель достигается тем, что устройство для синусно-косинусного преобразования кода в напряжение, содержащее первый, второй, третий и четвертый аналоговые запоминающие блоки, выход второго из которых соединён с первыми входами первого и третьего аналоговых запоминающих блоков, и распределитель импульсов, первый выход которого соединен с управляющими входами первого и третьего аналоговых запоминающих блоков, а второй выход - с управляющими входами второго и четвертого аналоговых запоминающих блоков, содержит преобразователь кода в.напряжение i и два переключателя, при этом вход второго аналогового запоминающего блока через первый переключатель соединен с выходом первого аналогового запоминающего блока и с выходом преобразователя кода в напряжение, входчетвертого аналогового запоминающего блока через второй переклю- чатель соединен с выходом третьего аналогового запоминающего блока и с шиной нулевого потенциала, выход третьего аналогового запоминающего блока соединен с вторым входом первого аналогового запоминающего блока, выход, четвертого аналогового запоминающего блока соединен с вторым входом третьего аналогового запоминающего блока, информационный вход преобразователя кода в напряжение соединен с шиной задания кода амплитуды устройства, а его синхронизирующий вход - с третьим выходом распределителя импульсов, четвертый выход которого соединен с управляющими входами первого и второго переключателей. вход начальной установки распределителя импульсов соединен с-шиной зада ния аргумента устройства. Аналоговый запоминающийблок содержит операционный усилитель, между выходом и инвертирующим входом которого включен запоминающий конденсато входные масштабирующие резисторы по числу входов блока, первые выводы ко торых соединены с соответствующими входами блока, вторые выводы объединены и через ключ соединены с инверт рующим входом операционного усилителя, между выходам которого и вторым выводом входного масштабирующего резистора включен масштабирующий резис тор обратной связи, выход операционного усилителя является выходом блок управляющий вход ключа является упра ляющим входом блока. . На фиг.1 представлена схема устро ства; на фиг.2 - возможное выполнени распределителя импульсов; на фиг.З временные диаграммы. Устройство содержит аналоговые запоминающие блоки 1-4, переключатели 5 и 6, .преобразователь 7 кода в напряжение, шину 8 задания кода амплитуды, распределитель 9 импульсо шину 10 задания аргумента. Аналоговые запоминающие блоки 1-4 выполнены идентично и содержат операционный усилитель 11, масштабирующие резисто ры 12-14, запоминающий конденсатор 1 Распределитель 9 импульсов (фиг.2 содержит D -триггеры 16 и 17, счетны тр иггер 18 R5 -триггер 19, вычитающий счетчик 20,элементы 21 и 22 задержки, элементы И 23-26, элемент ИЛИ 27. Устройство работает следующим образом. По команде Старт в вычитающий счетчик 20 распределителя 9 импульсов и в преобразователь 7 кода в напряжение заносятся коды аргумен та и амплитуды, вырабатывается импульс управления С, подключающий входы аналоговых запоминающих блоков 3 и 4 к шине нулевого потенциала и к выходу преобразователя 7 соответственно. Одновременно первые импульсЫ последовательности С замыка ют ключи блоков 3 и 4 в результате производится запись в них начальных значений синуса и косинуса. В дальнейшем распределитель 9 импульсов вырабатывает две сдвинутые одна относительно другой импульсные последовательности Су, С, число импульсов в них определяется начальным кодом счетчика 20. В результате блоки 1и 2 и блоки 3 и 4 поочередно находятся в режиме слежения и в режиме хранения. . Первый импульс из последовательности С2 замыкает ключи аналоговых запоминающих блоков 1 и 2. При этом на выходе первого из них устанавливается напряжение ) где К, коэффициенты передачи блока 1 по первому и второму входам (; со5ЛЧ,- K,5tndY;) . ЛЧ - квант изменения аргумента. На первый вход блока 2 подается выходное напряжение блока 1. По этому входу в блоке 2 установлен коэфКфициент ц -f + - . По BTopoj iy „ входу установлен коэффициент С учетом значений коэффициентов на выходе блок 2 устанавливается напряжение 7 с с .«1в с:, ,ч После окончания импульса последовательности C-j блоки 1 и 2 переходят в режим хранения, во время которого их выходные напряжения фиксированы. На выходах блоков 3 и 4, которые переводятся импульсом последовательности Са Б режим слежения, устанавливаются напряжения Vg д ,. COS.4 . На втором такте в течение первого полутакта на выходе блока 1 устанавивается напряжение - - а на выходе блока 2 устанавливается напряжение ( Во втором полутакте на выходе блока 3 устанавливается напряжение ( на выходе блока 4 ( Для произвольного п. -го такта значения вь1Хрдных напряжений имеют вид: (пДМ|; 5с -ЕдСОз(п-дЧ), (naf). Таким образом, проводя последовательно запись-перезапись сформированных согласно приведенным соотношениям сигналов на входах и выходах аналоговых запоминающих блоков, полу чаем последовательность выборок, значения которых определяются кодом амплитуды и синусно-косинусной функцией текущего кода аргумента. После завершения п тактов на выходе устройства устанавливаются напряжения, значения которых представляют собой синусно-косинусную функцию от количества тактов, т..е. от кода аргумент Пример. Пусть задано количество разрядов кодов аргумента Мд 4 и амплитуды . Тогда квант кода аргумента равен A -2Ti/2 Jl/8 , а коэффициенты по соответствующим входам суммирующих аналоговых запоминающих устройств равны К COS(7Г/81 0,926 (77/a) 0,58 ,.0,413. 1,084 ; К 11 11 При диапазоне изменения амплитуды 0-4 В и двоичном коде амплитуды 0100 получаем значение амплитуды В. Напряжения на вьгходе устройства как функция кода аргумента для приведенных исходных данных сведены в таблицу (инвертированные значения не приводится). 0,926 -0,383 -0,707 0,707 -0,926 Продолжение таблицы Таким образом, предлагаемый синусно-косинусный преобразователь кода в напряжение позволяет сформировать четыре аналоговых сигнала, соответствующих гармонической функции, сдвинутой на четверть периода. Устройство содержит четыре операционных усилителя, одну интегральную схему линейного цифроаналогового преобразователя, два аналоговых ключа и несложную логическзто схему управления. По сравнению с преобразователем, основанным на считьгоании постоянным запоминающим устройством последовательных значений кода функции и пре образовании их в аналоговую форму с помощью цифроаналогового преобразователя, следует отметить существенно более простую реализацию предлагаемого устройства. Предлагаемое устройство является более простым и по отношению к синусно-косинусному цифроаналоговому преобразователю, содержащему операционные усилители, цифровой управляемый резистор и масштабирующие резисторы. Очевидно, что при п -разрядном коде аргумента объем оборудования известного устройства пропорционален 2 , в то время как в предлагаемом устройстве минимальные аппаратные затраты не зависят от разрядности входного кода.

9аг.1

| название | год | авторы | номер документа |

|---|---|---|---|

| Анализатор спектра | 1985 |

|

SU1287033A1 |

| Косинусный преобразователь | 1977 |

|

SU634304A1 |

| Устройство для синусно-косинусного цифро-аналогового преобразования | 1983 |

|

SU1129632A1 |

| Устройство преобразования синусно-косинусных сигналов в код | 1983 |

|

SU1104567A1 |

| Амплитудно-фазовый анализатор гармоник | 1985 |

|

SU1272272A2 |

| Устройство для преобразования кода в мгновенные значения трехфазного синусоидального напряжения | 1986 |

|

SU1399777A1 |

| Устройство для выполнения дискретного преобразования Фурье | 1989 |

|

SU1679501A1 |

| Устройство для дискретного преобразования Фурье | 1984 |

|

SU1188751A1 |

| Дискретно-аналоговый фурье-преоб-РАзОВАТЕль | 1979 |

|

SU813307A1 |

| Амплитудно-фазовый анализатор гар-МОНиК | 1979 |

|

SU815669A1 |

1. УСТРОЙСТВО ДЛЯ СИНУСНОКОСИНУСНОГО ПРЕОБРАЗОВАНИЯ КОДА В НАПРЯЖЕНИЕ, содержащее первый, второй третий и четвертый аналоговые запоминающие блоки, выход второго из которых соединен с первыми входами первого и третьего ailanoroBbix запоминающих блоков, и распределитель импульсов, первый выход которого соединен с .управляющими входами первого и третьего аналоговых запоминающих блоков, а второй выход - с управляющими входами второго и четвертого аналоговых запоминающих блоков, о тличающееся тем, что, с целью расширения области применения путем одновременного формирования инвертированных и неинвертированных значений синусной и косинусной функций и изменения амплитуды формируемых функций в широком диапазоне, оно содержит преобразователь кода в напряжение и два переключателя, при этом вход второго аналогового запоминающего блока через первый переключатель соединен с выходом первого аналогового запоминающего блока и с выходом преобразователя кода в напряжение. те fnr.ff.y-5: ;-.; . щ Ijte -f i iij i вход четвертого аналогового запомин ающего блока через второй переключатель соединен с выходом третьего аналогового за:поминающего блока и с шиной цулевого потенциала, выход третьего аналогового запоминающего блока соединен с вторым входом первого аналогового запоминающего блока, вьгаод четвертого аналогового запоминакщего блока соединен с вторым входом третьего аналогового запоминающего блока, информационный вход преобразователя кода в напряжение соединен с шиной задания кода амплитуда устройства, а его синхронизирующий вход - с третьим выходом распределителя импульсов, четвертый выход которого соединен с управляющими входами первого и второго neper ключателей, вход начальной установки распределителя импульсов соединен с щиной задания аргумента устройства. 2. Устройство по П.1, отличающееся тем, что, аналоговый запоминающий блок содержит опера30 ционный усилитель, между выходом и . :о :л инвертирующим входом которого включен запоминающий конденсатор, вход;ЭО ные масштабирующие резисторы по чисэо лу входов блока, первые выводы которых соединены с соответствующими входами блока, вторые выводы объединены и через ключ соединены с инвертирзта щим входом операционного усилителя, между выходом которого и вторым выводом входного масштабир5тои;его резистора включен масштабирующий резистор обратной связи, аькод операционного усилителя является выходом блока, управляющий вход ключа является уп . равляющйм входом блока.

С,

топ.

Пг.г

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Electroniks, 1975, 48, №20, 104-105 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Вычислительная техника.,Справочник под ред | |||

| Г | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Ветряный двигатель | 1922 |

|

SU553A1 |

Авторы

Даты

1984-04-30—Публикация

1982-12-30—Подача