(Л

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1988 |

|

SU1524178A1 |

| Программируемый генератор импульсов | 1985 |

|

SU1298869A2 |

| Цифровой фазометр | 1983 |

|

SU1114977A1 |

| Устройство для измерения показателей качества электроэнергии трехфазной сети | 1982 |

|

SU1064233A1 |

| Устройство для преобразования кода в мгновенные значения трехфазного синусоидального напряжения | 1986 |

|

SU1399777A1 |

| ИМИТАТОР СИГНАЛОВ ПАССИВНОГО РАДИОЛОКАТОРА | 1985 |

|

SU1841017A1 |

| Программируемый генератор импульсов | 1984 |

|

SU1248029A1 |

| Анализатор спектра | 1986 |

|

SU1370589A2 |

| Преобразователь напряжения в кодС САМОКОНТРОлЕМ | 1979 |

|

SU834890A1 |

| Преобразователь перемещения в код | 1984 |

|

SU1200418A1 |

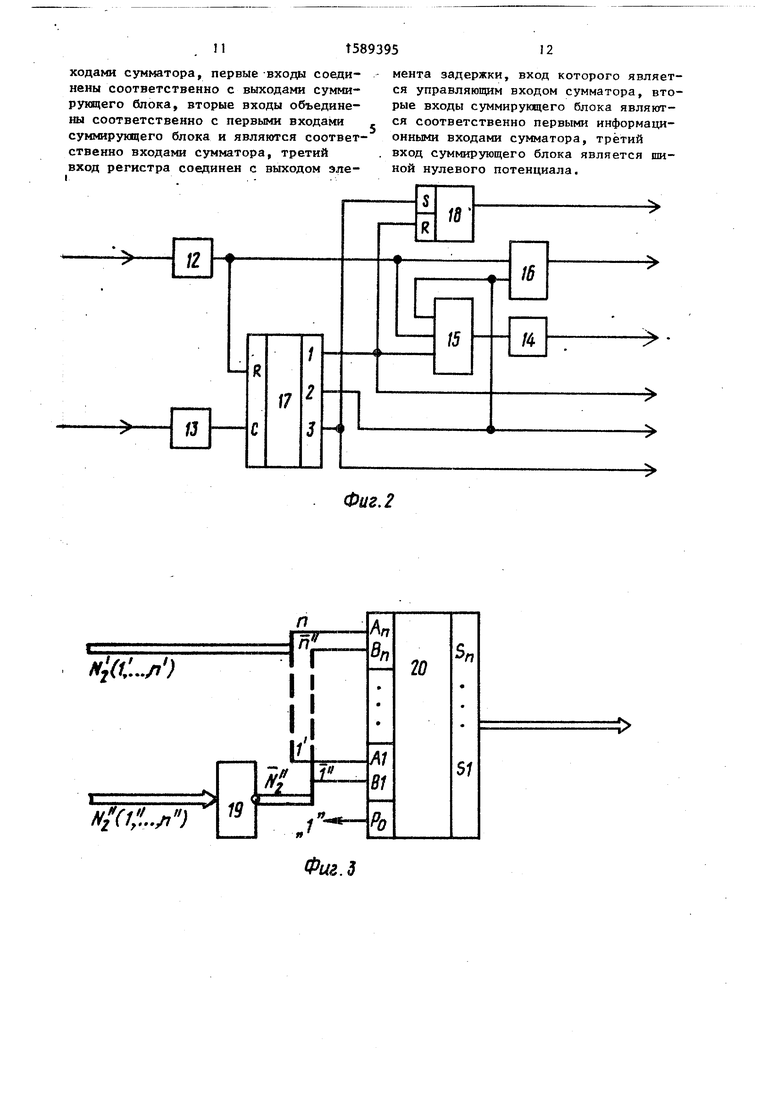

Изобретение относится к вычислительной технике. Оно позволяет повысить точность. Это достигается тем, что в аналого-цифровой преобразователь, содержащий переключатель 1, аналоговый запоминающий блок 2, усилитель 3, преобразователь 4 код-напряжение, оперативные запоминающие блоки 6 и 8, блок управления 10 и сумматор 11, введены переключатель 5, преобразователь 7 напряжение-код и блок 9 вычитания кодов. 2 з.п. ф-лы, 5 ил.

ел

00

ф ро

У1

0ui,f

Изобретение относится к вычислительной технике,

,: Цель изобретения - повышение точ- ости.

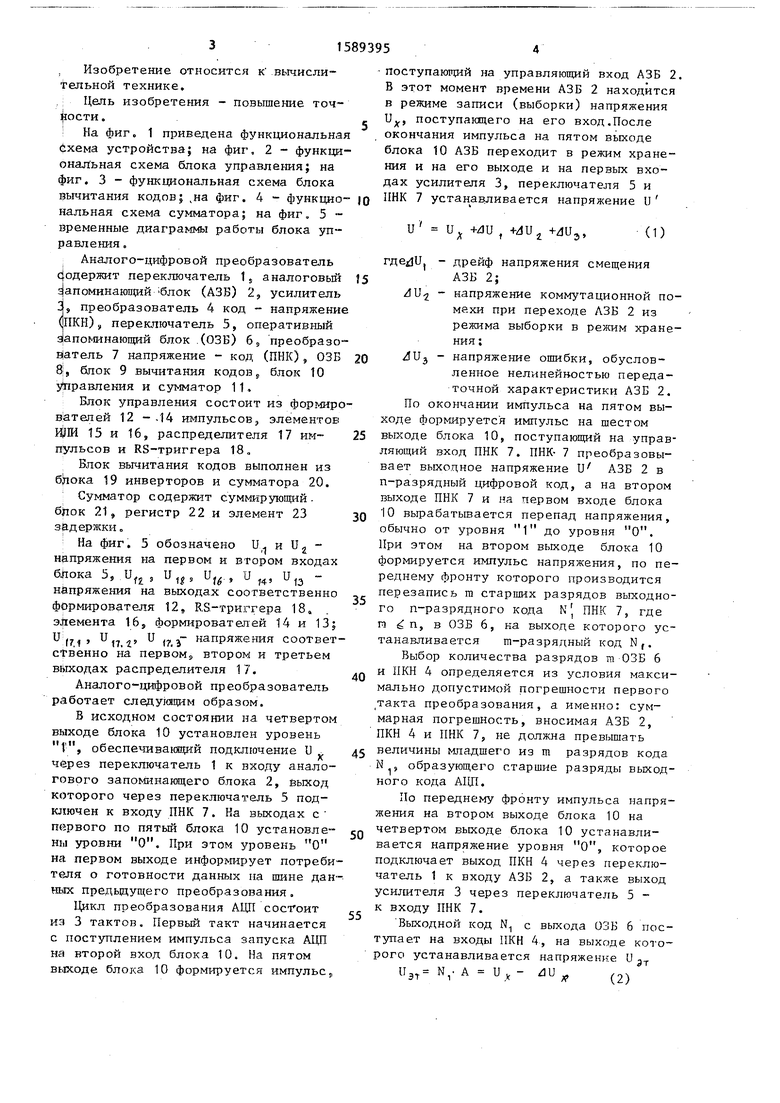

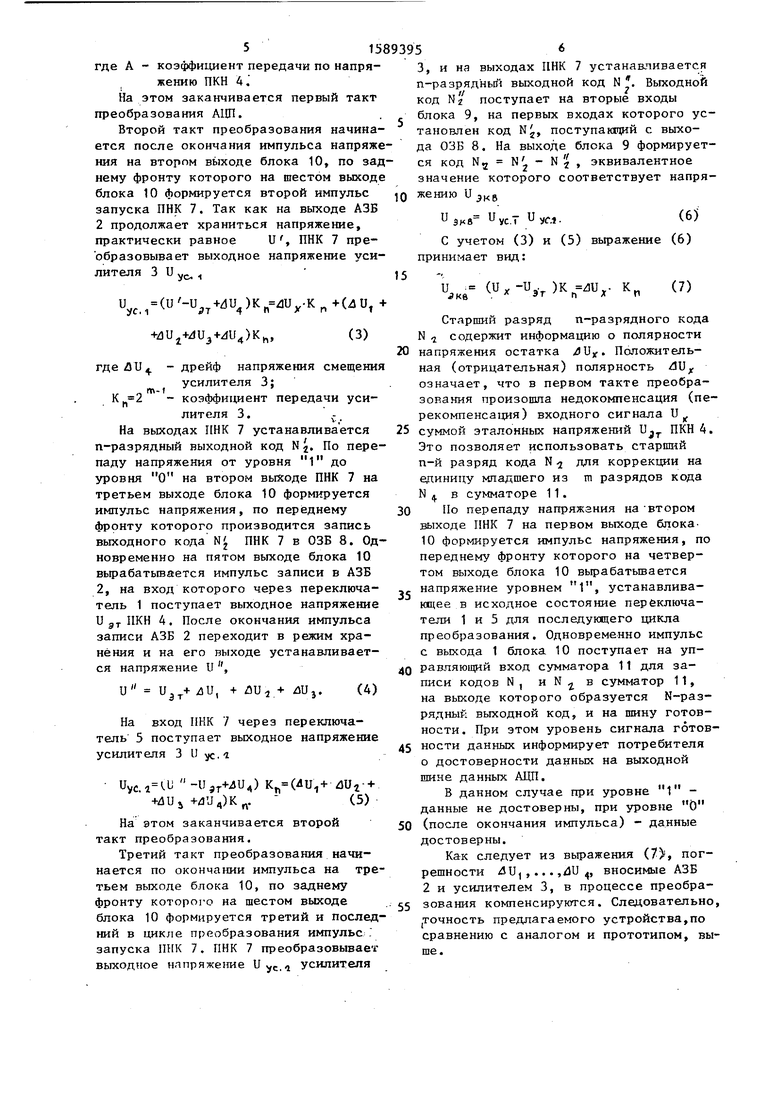

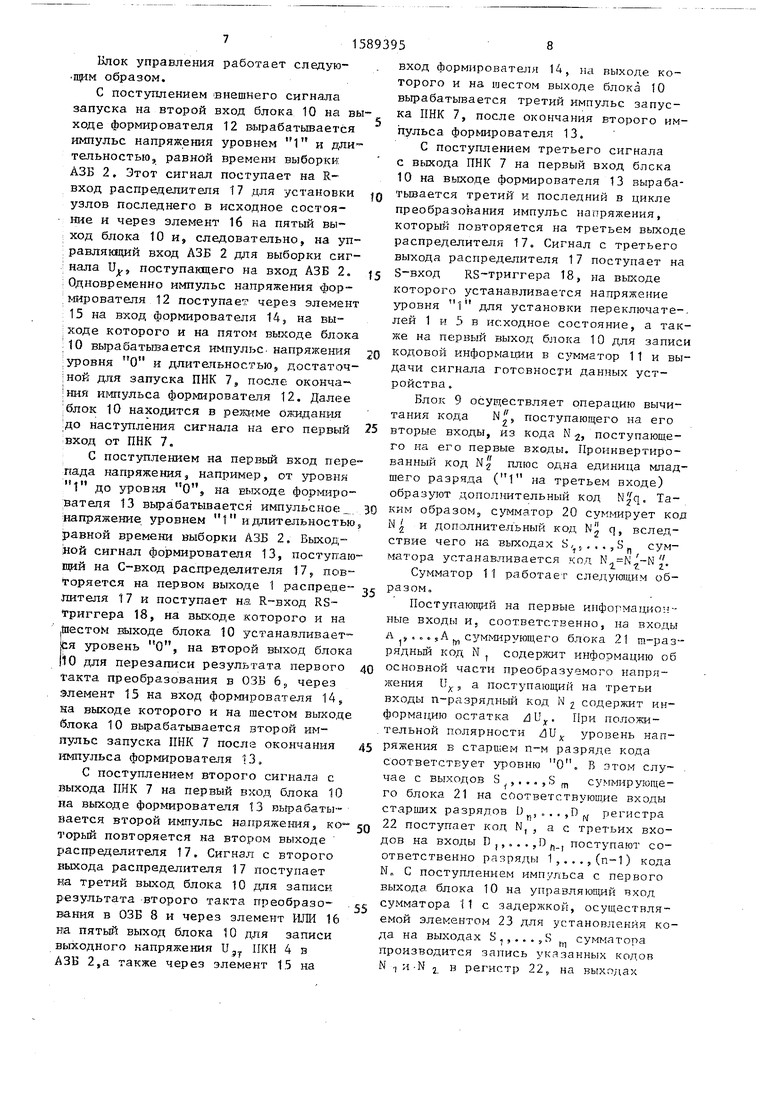

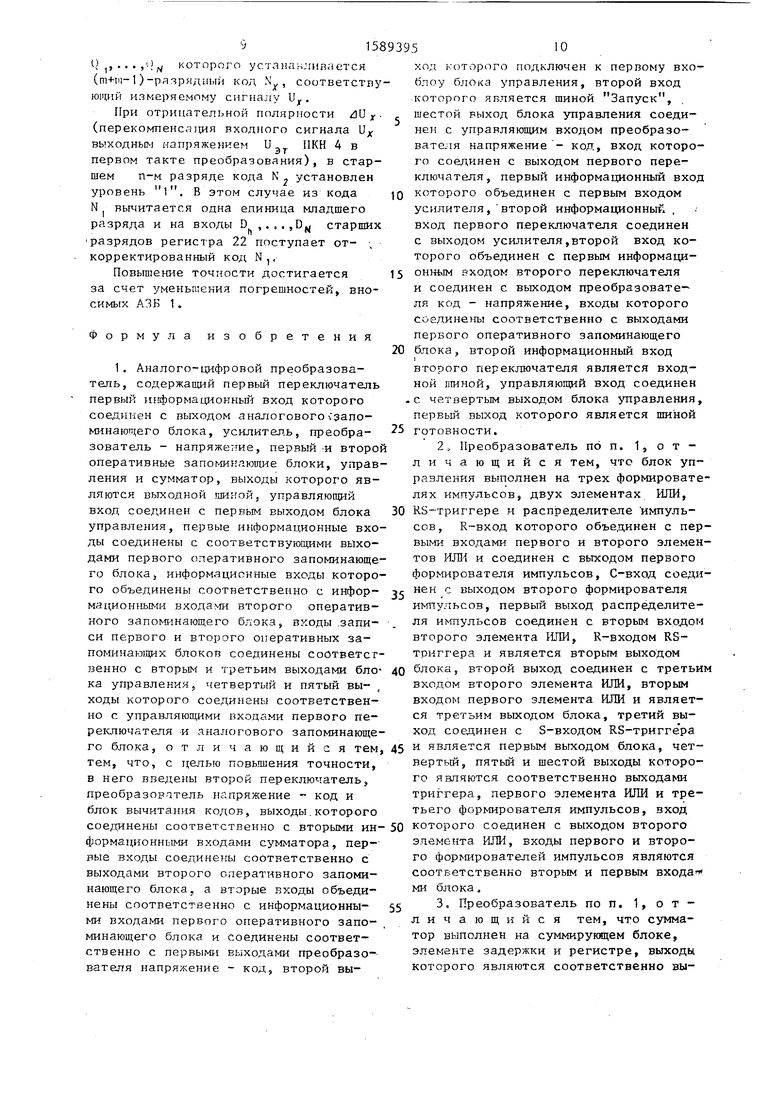

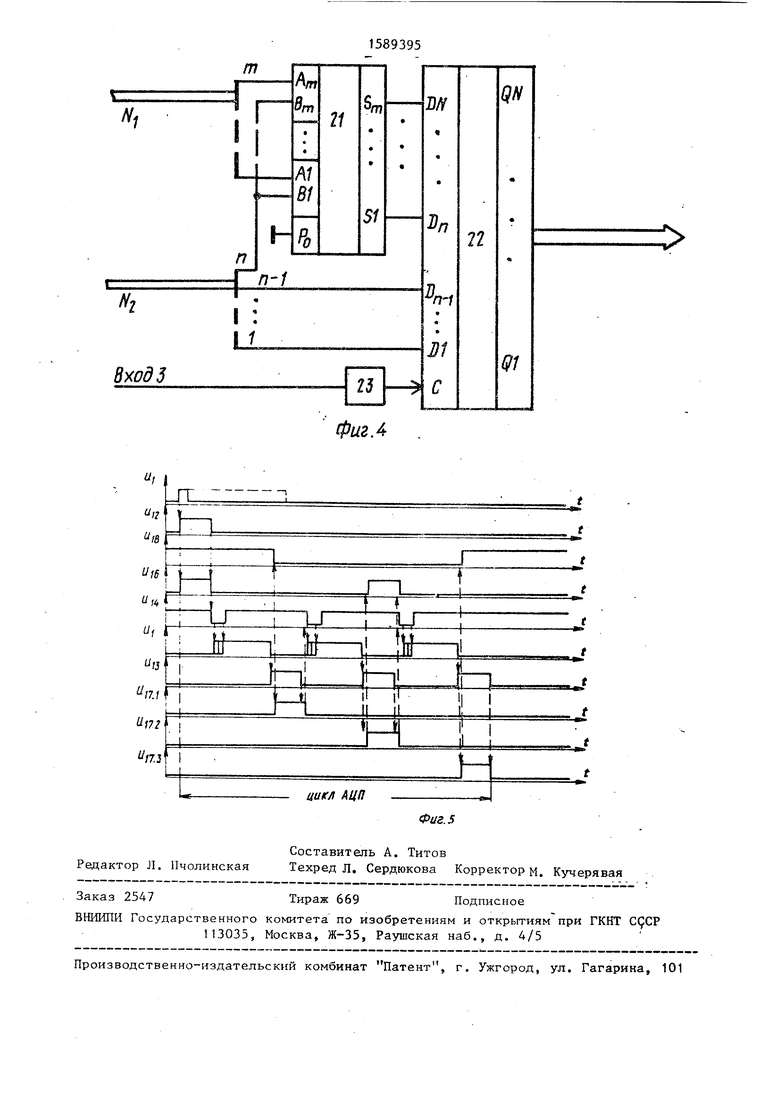

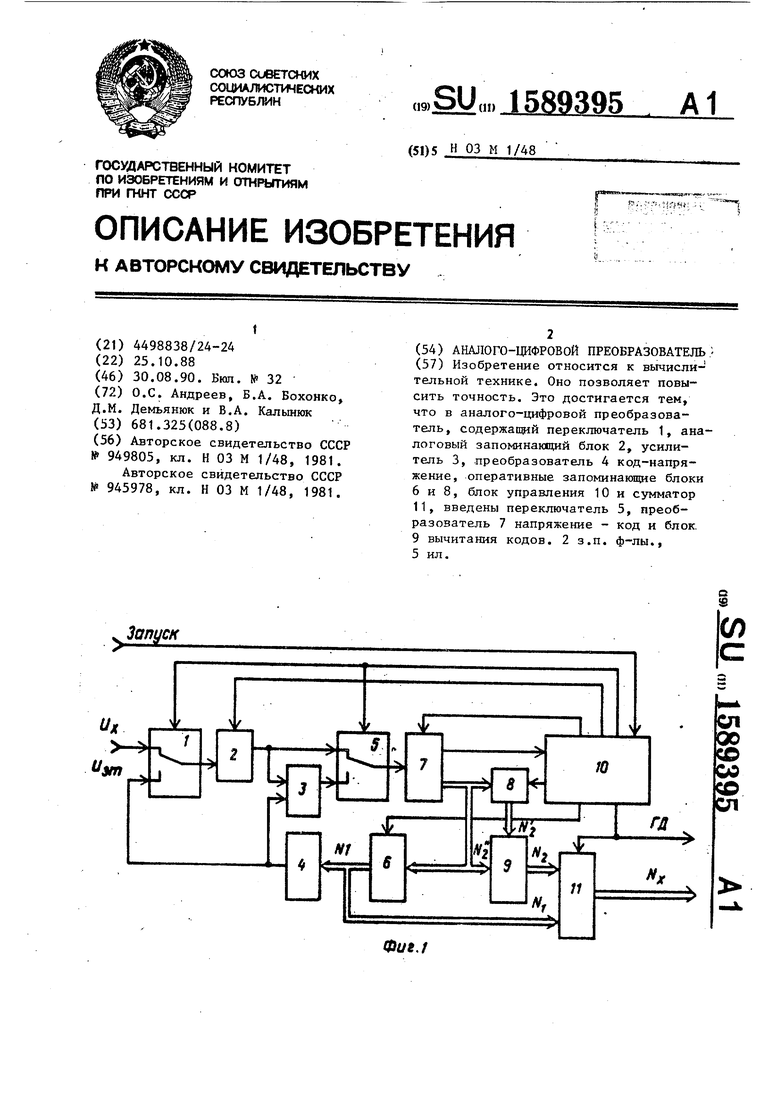

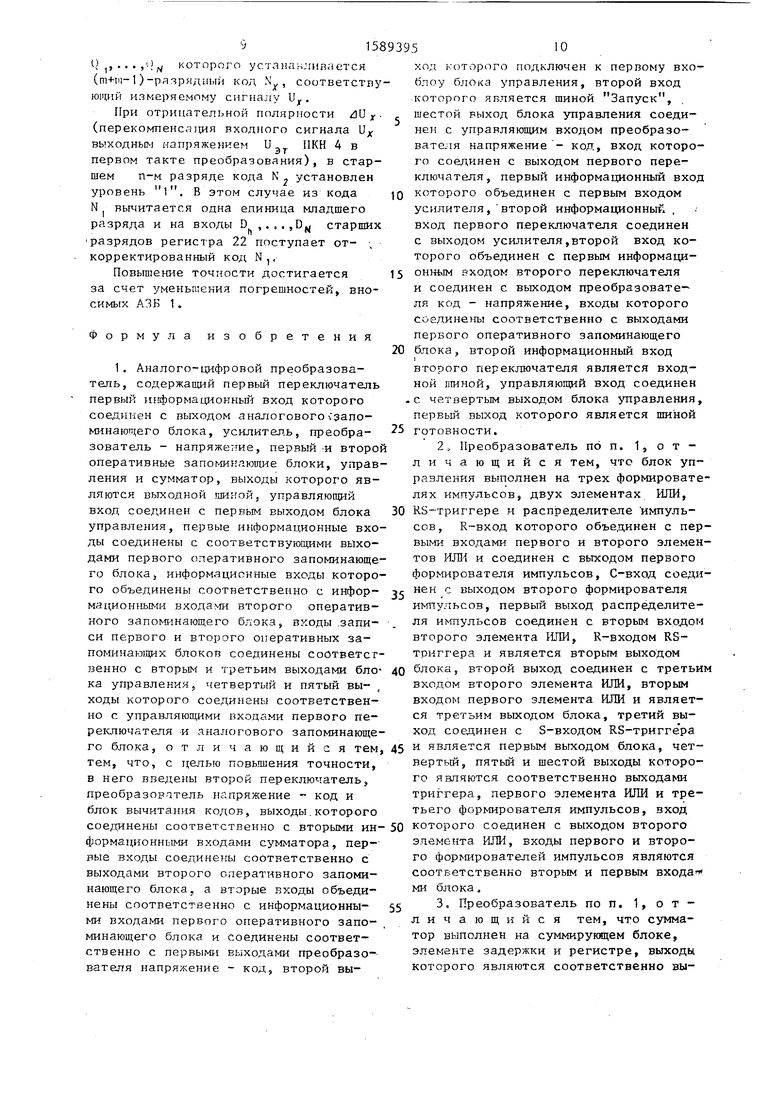

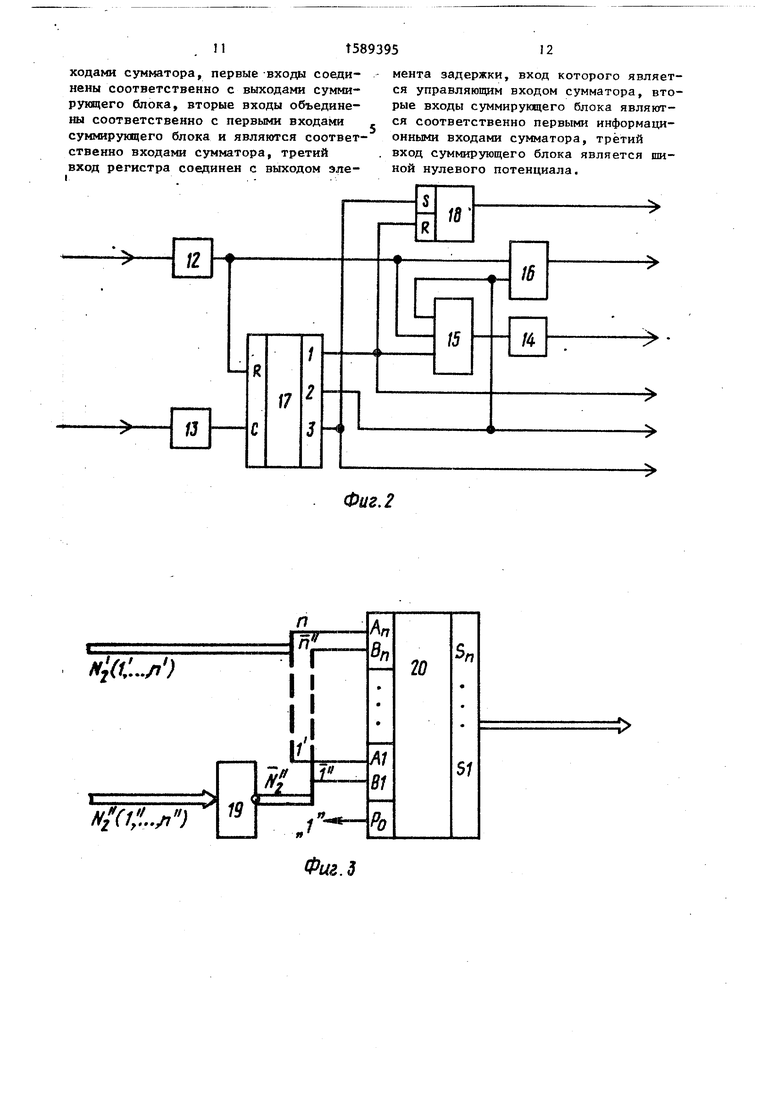

На фиг. 1 приведена функциональна ехема устройства; на фиг, 2 - функциональная схема блока управления; на фиг. 3 - функциональная схема блока вычитания кодов; на фиг. 4 - функцио нальная схема сумматора; на фиг. 5 - временные диаграммы работы блока управления.

Аналого-цифровой преобразователь Додержит переключатель Ij аналоговьш апоминаюпщй-блок (АЗБ) 2, усилитель 3s преобразователь 4 код - напряжени (|ПКН) , переключатель 5, оперативный з|апомина1ощий блок .(ОЗБ) 65 преобразо в1атель 7 напряжение - код (ПНК), ОЗБ 81, блок 9 вычитания кодов блок 10 управления и сумматор 11,

Блок управления состоит из формирователей 12 - -14 импульсов, элементов ШШ 15 и 16, распределителя 17 им- пульсов и RS-триггера 18„

Блок вычитания кодов выполнен из 19 инверторов и сумматора 20.

Сумматор содержит суммирующий. блок 21, регистр 22 и элемент 23

задержки.

; На фиг. 5 обозначено U, и U - напряжения на первом и втором входах блока 5,.и,, и,, и,.. и,„ и,з напряжения на выходах соответственно

формирователя 12, RS-триггера 18, элемента 16, формирователей 14 и 13;

(7.1 17.-2 f7.5 напряже шя соответ- ctBeHHo на первомз, втором и третьем выходах распределителя 17.

Аналого-цифровой преобразователь работает следугацим образом.

В исходном состоянии на четвертом выходе блока 10 установлен уровень

, обеспечивакщий подключение U

через переключатель 1 к входу аналогового запоминагощего блока 2, выход которого через переключатель 5 подключен к входу ПНК 7. На выходах с первого по пятый блока 10 установле- ны уровни О. При этом уровень О НсЧ первом выходе инфор шрует потребителя о готовности данных на пшне данных предыдущего преобразования.

Цикл преобразования АЦП сосгоит иа 3 тактов. Первый такт начинается с поступлением импульса запуска АЩ1 на второй вход блока 10. На пятом выходе блока 10 формируется импульс

поступающий на управляющий вход АЗБ 2, В этот момент времени АЗБ 2 находится в режиме записи (выборки) напряжения Ujj., поступающего на его вход.После окончания импульса на пятом выходе блока 10 АЗБ переходит в режим хранения и на его выходе и на первых входах усилителя 3, переключателя 5 и ПНК 7 устанавливается напряжение U

и и, +4U , ,

(1)

5 0

5

О

5

0

5

- дрейф напряжения смещения

АЗБ 2;

/lU - напряжение коммутационной помехи при переходе АЗБ 2 из режима выборки в режим хранения :

ЛПз - напряжение ошибки, обусловленное нелинейностью передаточной характеристики АЗБ 2. По окончании импульса на пятом выходе формируется импульс на шестом выходе блока 10, поступающий на управляющий вход ПНК 7. ПНК- 7 преобразовывает выходное напряжение U АЗБ 2 в п-разрядный цифровой код, а на втором выходе ПНК 7 и на первом входе блока 10 вырабатьшается перепад напряжения, обычно от уровня 1 до уровня О. При этом на втором выходе блока 10 формируется импульс напряжения, по переднему фронту которого производится перезапись га старших разрядов выходного п-разрядного кода N ПНК 7, где га ( п, в ОЗБ 6, на выходе которого устанавливается т-разрядный код N,.

Выбор количества разрядов га ОЗБ 6 и ПКН 4 определяется из условия максимально допустимой погрешности первого ,такта преобразования, а именно: суммарная погрешность, вносимая АЗБ 2, ПКН 4 и ПНК 7, не должна превгзШ1ать величины младшего из m разрядов кода N, образующего старшие разряды выходного кода АЦП.

По переднему фронту импульса напряжения на втором выходе блока 10 на четвертом выходе блока 10 устанавливается напряжение уровня О, которое подключает выход ПКН 4 через переключатель 1 к входу АЗБ 2, а также выход усилителя 3 через переключатель 5 - к входу ПНК 7.

Выходной код N с выхода ОЗБ 6 поступает на входы ПКН 4, на выходе которого устанавливается напряженке U

(2)

эт N,- А аи

5158

где А - коэффициент передачи по напряжению ПКН 4.

На этом заканчивается первый такт преобразования А1Ш,

Второй такт преобразования начинается после окончания импульса напряжения на втором выходе блока 10, по заднему фронту которого на шестом выходе блока 10 формируется второй импульс запуска ПНК 7. Так как на выходе АЗБ 2 продолжает храниться напряжение, практически равное U , ПНК 7 преобразовывает выходное напряжение усилителя 3 и

ус. 1

V.r T- 4 n y-Kn- t+4Uj+JU,,+/IU4)K,

(3)

к,2

m-t

и

ли, + UVi + /lUj.

где ли - дрейф напряжения смещени

усилителя 3;

- коэффи1|иент передачи усилителя 3.- На выходах ПНК 7 устанавливается п-разрядный выходной код N j. По перепаду напряжения от уровня 1 до уровня О на втором выходе ПНК 7 на третьем выходе блока 10 формируется импульс напряжения, по переднему фронту которого производится запись выходного кода NJ ПНК 7 в ОЗБ 8. Одновременно на пятом выходе блока 10 вырабатьгоается импульс записи в АЗБ 2, на вход которого через переключатель 1 поступает выходное напряжение и дт I1KH 4. После окончания импульса записи АЗБ 2 переходит в режим хранения и на его выходе устанавливается напряжение U ,

II J. л TI 4. ЛТ1 - л. ЛТ1 (4)

На вход ПКК 7 через переключатель 5 поступает выходное напряжение усилителя 3 U .1

Uyc.i.U -UjT+ U) K,, (4U,+ + +4U5 +/JU,)K, (5)

На этом заканчивается второй такт преобразования.

Третий такт преобразования начинается по оконча1ши импульса на третьем выходе блока 10, по заднему фронту которого на шестом выходе блока 10 формируется третий и последний в цикле преобразования импульс запуска ПНК 7, ПНК 7 преобразовывает выходное нлпряжение Uyc.i усилителя

3, и на выходах ИНК 7 устанавливается п-разрядный выходной код N . Выходной код NZ поступает на вторые входы блока 9, на первых входах которого установлен код NJ, поступакщий с выхода ОЗБ 8. На выходе блока 9 формируется код N,

N , мN 2

эквивалентное

значение которого соответствует напряжению и ц5

5

и экв- yc.т и vr.j.

С учетом (3) и (5) принимает вид:

и

вьфажение

кв

(и,-и,.),. к.

Старший разряд

(6) (6)

(7)

0

п-разрядного кода

N содержит информацию о полярности напряжения остатка . Положительная (отрицательная) полярность 31) означает, что в первом такте преобразования произопша недокомпенсация (перекомпенсация) входного сигнала U 5 суммой эталонных напряжений Uj ПКН 4. Это позволяет использовать старший п-й разряд кода N для коррекции на единицу младшего из m разрядов кода N j. в сумматоре 11.

По перепаду напряжения на втором выходе ГШК 7 на первом выходе блока- 10 формируется импульс напряжения, по переднему фронту которого на четвертом выходе блока 10 вьфабатьшается напряжение уровнем 1, устанавлива- юцее в исходное состояние переключатели 1 и 5 для последующего цикла преобразования. Одновременно импульс с выхода 1 блока 10 поступает на управляющий вход сумматора 11 для за0

5

0

писи кодов N , и N 2. в сумматор 11,

на выходе которого образуется N-раз- рядный выходной код, и на пмну готовности. При зтом уровень сигнала готов- 5 ности данных информирует потребителя о достоверности данных на выходной шине данных АЦП.

В данном случае при уровне 1 - данные не достоверны, при уровне О (после окончания импульса) - данные достоверны.

Как следует из выражения (7), погрешности 4U,,...,U, вносимые АЗБ 2 и усилителем 3, в процессе преобразования компенсируются. Следовательно, точность предлагаемого устройства,по сравнению с аналогом и прототипом, выше.

0

5

Блок управления работает следую- щим образом.

С поступлением внешнего сигнала запуска на второй вход блока 10 на входе формирователя 12 Бырабатьгоается импульс напряжения уровнем 1 и дли тепьностыо, равной времени выборки АЗБ 2, Этот сигнал поступает на R- вход распре,целнтеля 17 для установки узлов после-днего в исходное состояние и через элемент 1б на пятый выход блока 10 и, следовательно, на уп равлякщий вход АЗБ 2 для выборки сигнала Uij,, поступанщего на вход АЗБ 2. Одновременно импульс напряжения формирователя 12 поступаем через элемен 15 на вход формирователя 14, на выходе которого и на пятом выходе блока 10 вьфабатывается импульс, напряжения

Iуровня О и длительностью, достаточ- :ной для запуска ПНК 7, после оконча- :ния импульса формирователя 12. Далее ;блок 10 находится в режиме ожидания ;ДО наступления сигнала на его первый вход от ПНК 7.

С поступлением на первьш вход перепада напряжения, например, от уровня 1 до уровня 0 % на выходе формиро- :вателя 13 вырабатывается импульсное тпряжение уровнем Г и длительностью равной времени выборки АЗБ 2. Выходной сигнал формирователя 13, поступающий на С-вход распределителя 17, повторяется на первом выходе 1 распре,п,е Лителя 17 и поступает на R-вход КЗ- Триггера 18, на выходе которого и на .Шестом выходе блока 10 устанавливает- ря уровень О, на второй выход блока 10 для перезаписи результата первого Такта преобразования в ОЗБ 6, через элемент 15 на вход формирователя 14, на выходе которого и на шестом выходе блока 10 вырабатьшается второй импульс запуска ПНК 7 посла окончания 1шпульса формирователя 13.

С поступлением второго сигнала с выхода ПНК 7 на первый вход блока 10 на выходе формирователя 13 вырабатывается второй импульс напряжения, ко торый повторяется на втором выходе распределителя 17. Сигнал с второго выхода распределителя 17 поступает на третий выход блока 10 цIя записи результата -второго такта преобразования в ОЗБ 8 и через элемент ИЛИ 16 на пятый выход блока 10 для записи выходного напряжения U, ПКН 4 в АЗБ 2,а также через элемент 15 на

25

30, 40

вход формирователя 14, на выходе которого и на шестом выходе блока 10 вырабатывается третий импульс запуска ПНК 7, после окончания второго импульса формирователя 13.

С поступлением третьего сигнала с выхода ПНК 7 на первый вход блока 10 на выходе формирователя 13 выраба- JQ тьюается третий и последний в цикле преобразования импульс напряжения, который повторяется на третьем выходе распределителя 17. Сигнал с третьего выхода распределителя 17 поступает на t5 S-вход RS-триггера 18, на выходе которого устанавливается напряжение уровня 1 для установки переключате-, лей 1 и 5 в исходное состояние, а также на первый выход блока 10 для записи 20 кодовой информации в сумматор 11 и выдачи сигнала готовности данных устройства.

Блок 9 осуществляет операцию вычи45

0

тания кода , поступающего на его вторые входы, из кода N -г, поступающего на его первые входы. Проинвертиро- ванный код Nf плюс одна единица младшего разряда (1 на третьем входе) образуют дополнительный код q. Таким образом, сумматор 20 суммирует код N и дополнительный код N q, вследствие чего на выходах S,,,..,S сумматора устанавливается код N N -N .

Сумматор 11 работает следуротдим образом.

Поступающий на первые ипфог мащю - ные входы и, соответственно, на входы , sA суммирующего блока 21 т-раз- рядньм код N , содержит информацию об основной части преобразуемого напряжения и.,, а поступающий на третьи входы п-разрялный код N содержит информацию остатка . При положительной полярности 4U уровень напряжения в старшем п-м разряде кода соответствует уровню О, В этом случае с выходов S ,...,S „ суммирующего блока 21 на соответствующие входы старших разрядов и,...,п регистра 22 поступает код N,, ас третьих входов на входы D,,

(

.D

f,., поступают соответственно разряды 1 , ., , , (п-1) кода N. С поступлением импульса с первого выхода блока 10 на управляющий вход 2 сумматора 11 с задержкой, осуществляемой элементом 23 для установления кода на выходах S ,,.. . ,s сумматора производится запись указанных колов N .|H.N 2 в регистр 22, на выходах

i 5-. которого устанавливается ( )-разрядный код N, , соответствующий измеряемому сигналу Uj.

При отрицательной полярности /3U у . (перекомпенсяция входного сигнала выходным напряжением U ПКН 4 в первом такте преобразования), в старшем п-м разряде кода N установлен уровень 1, В этом случае из кода NI вычитается одна единица младшего разряда и на входы D .,,,D старших разрядов регистра 22 поступает от- -, корректированный код N,,

Повышение точности достигается за счет уменьа:ения погрешностей, вносимых АЗК 1,

Формула изобретения

1, Аналого-цифровой преобразователь, содержащий первый переключатель первый ииформационньш вход которого соединен с выходом аналогового запоминающего блока, усилитель, преобра- зователь - напряжение, первый И второй оперативные запог-шнающие блоки, управления и сумматор, выходы которого являются выходной шиной, управляющий вход соединен с первым выходом блока управления, первые И1 формационные входы соединены с соответствующими выходами первого оперативного запоминающего блока, информационные входы которого объединены соответственно с инфор- мационными входами второго оперативного запоминающего блока, входы .запи- си первого и второго оперативных за- поминаю1днх блоков соединены соответственно с вторьм и третьим выходами бло- ка управления, четвертый и пятый выходы которого соединены соответственно с управляющими входами первого переключателя -и аналогового запоминающего блока, отличающийся тем, тем, что, с целью повьпиения точности, в него введены второй переключатель, преобразователь напряжение - код и блок вычитания кодов, выходы.которого соединены соответственно с вторыми ин- формационными входами сумматора, пер- вые входы соединены соответственно с выходами второго оперативного запоминающего блока, а вторые входы объединены соответственно с информационны- ми входами первого оперативного запоминающего блока и соединены соответственно с первыми выходами преобразователя напряжение - код, второй выQ

5

0

0 c 0 5 0 5

ход которого подключен к первому вхо- блоу блока управления, второй вход которого является шиной Запуск, шестой выход блока управления соединен с управляющим входом преобразователя напряжение - код, вход которого соединен с выходом первого переключателя , первый информационный вход которого объединен с первым входом усилителя, второй информационный вход первого переключателя соединен с выходом усилителя,второй вход которого объединен с первым информационным входом второго переключателя и соединен с выходом преобразовате- ля код - напряжение, входы которого соединены соответственно с выходами первого оперативного запоминающего блока, второй информационный вход второго переключателя является входной шиной, управляющий вход соединен ,с четвертым выходом блока управления, первый, выход которого является шиной готовности.

2,Преобразователь по п. 1, о т - л и ч а ю щ и и с я тем, что блок управления выполнен на трех формирователях импульсов, двух элементах ИЛИ, RS-триггере и распределитепе импульсов, которого объединен с первыми входами первого и второго элементов liJB f и соединен с выходом первого формирователя импульсов, С-вход соеди- Hei-i с выходом второго формирователя и myльcoв, первый выход распределителя импульсов соединен с вторым входом второго элемента ИЛИ, R-входом RS- трнггера и является вторым выходом блока, второй выход соединен с третьим входом второго элемента ИЛИ, вторым входом первого элемента ИЛИ и является третьим выходом блока, третий выход соединен с S-входом RS-тригге ра

и является первым выходом блока, четвертый, пятьй и шестой выходы которого являются соответственно выходами триггера, первого элемента ИЛИ и третьего формирователя импульсов, вход которого соединен с выходом второго элемента ИЛИ, входы первого и второго формирователей импульсов являются соответственно вторым и первым входа- ми. блока.

3,Преобразователь по п. 1, отличающийся тем, что сумматор выполнен на суммирующем блоке, элементе задержки и регистре, выходы которого являются соответственно выходами сумматора, первые входы соединены соответственно с выходами сумми- руняцего блока у вторые входы объединены соответственно с первыми входами суммируищего блока и являются соответственно входами сумматора, третий вход регистра соединен с выходом элеФиг. 2

Фиг.д

мента задержки, вход которого является управляющим входом сумматора, вторые входы суммирующего блока являются соответственно первыми информационными входами сумматора, третий вход суммирующего блока является шиной нулевого потенциала.

фиг А

| Аналого-цифровой преобразователь | 1980 |

|

SU949805A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аналого-цифровой преобразователь | 1981 |

|

SU945978A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-08-30—Публикация

1988-10-25—Подача