Nj

О ел

ел

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор синусоидальных сигналов | 1990 |

|

SU1734189A1 |

| Программируемый формирователь многочастотного сигнала | 1989 |

|

SU1739472A1 |

| СИНТЕЗАТОР ЧАСТОТ | 1991 |

|

RU2007843C1 |

| Формирователь случайных сигналов | 1990 |

|

SU1732419A1 |

| Калибратор сигналов, нормированных по коэффициенту гармоник | 1988 |

|

SU1555677A1 |

| Цифровой синтезатор частоты | 1987 |

|

SU1429285A1 |

| Трехфазный генератор полигармонических сигналов | 1985 |

|

SU1343540A1 |

| Формирователь сигналов с угловой модуляцией | 1985 |

|

SU1241411A1 |

| Умножитель частоты | 1987 |

|

SU1429284A1 |

| Устройство формирования многочастотного сигнала | 1984 |

|

SU1282305A1 |

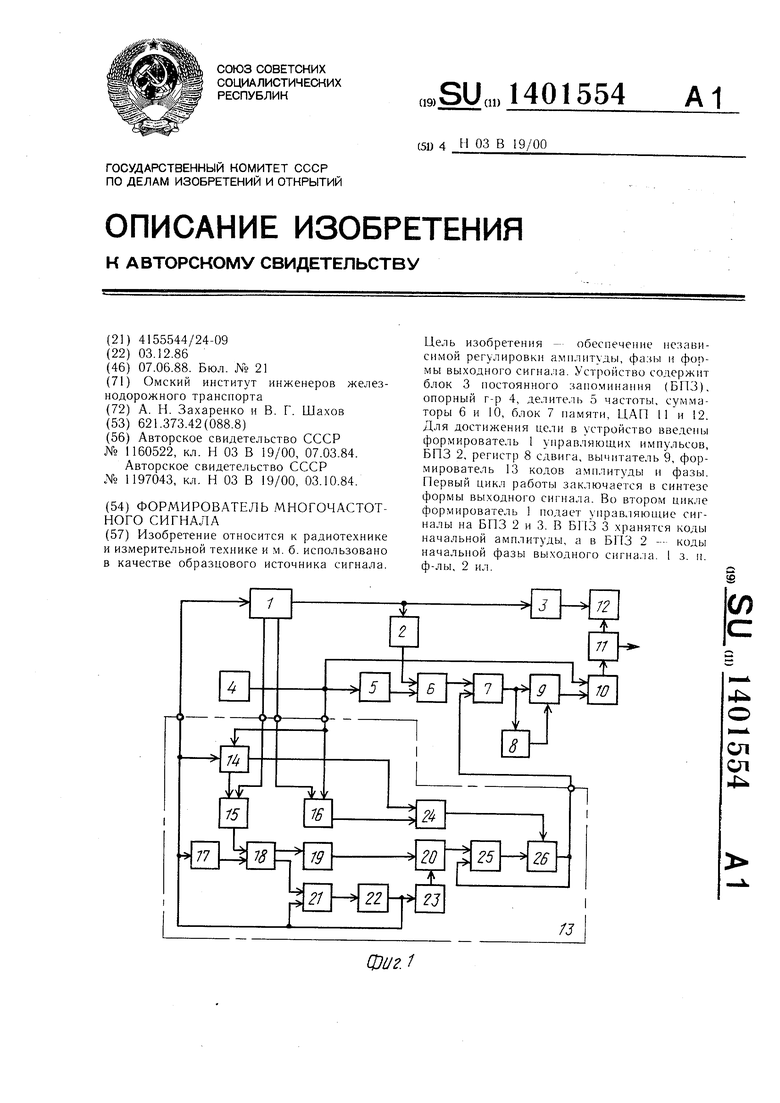

Изобретение относится к радиотехнике и измерительной технике и м.б.использовано в качестве образцового источника сигнала. Цель изобретения - обеспечение независимой регулировки амплитуды, фазы п формы выходного сигнала. Устройство содержит блок 3 постоянного запо.минания (БПЗ), опорный г-р 4, делитель 5 частоты, сумматоры 6 и 10, блок 7 памяти, ЦАП 11 и 12. Для достижения цели в устройство введены формирователь 1 управляющих импульсов, 1эПЗ 2, регистр 8 сдвига, вычитатель 9, формирователь 13 кодов ам 1;1итуды и фазы. Первый цикл работы заключается в синтезе формы выходного сигнала. Во втором цикле формирователь 1 подает управляющие сиг- палы на БПЗ 2 и 3. В БПЗ 3 хранятся коды начальной амплитуды, а в БПЗ 2 - коды начальной фазы выходного сигна.ча. I з. п. ф-лы, 2 ил. со

.1

Изобретение относится к радиотехнике и измерительной технике и может быть использовано в качестве образцового источника сигнала переменного тока.

Целью изобретения является обеспечение независимой регулировки амплитуды, фазы 5 и формы выходного сигнала.

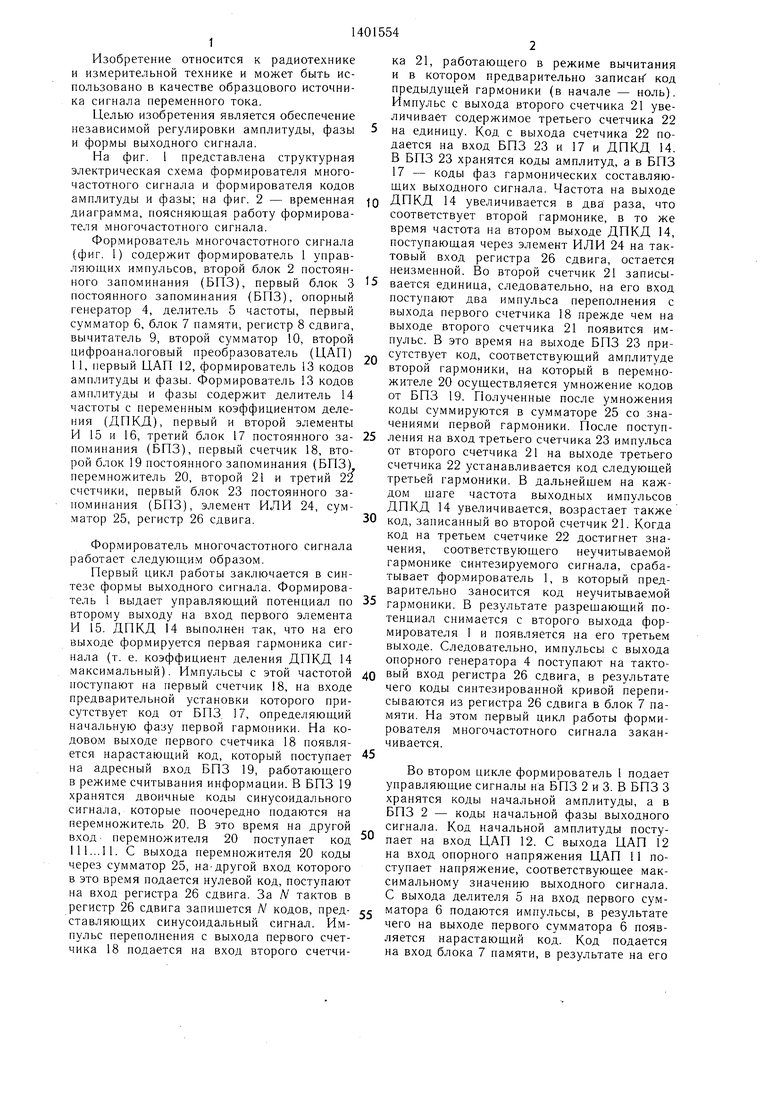

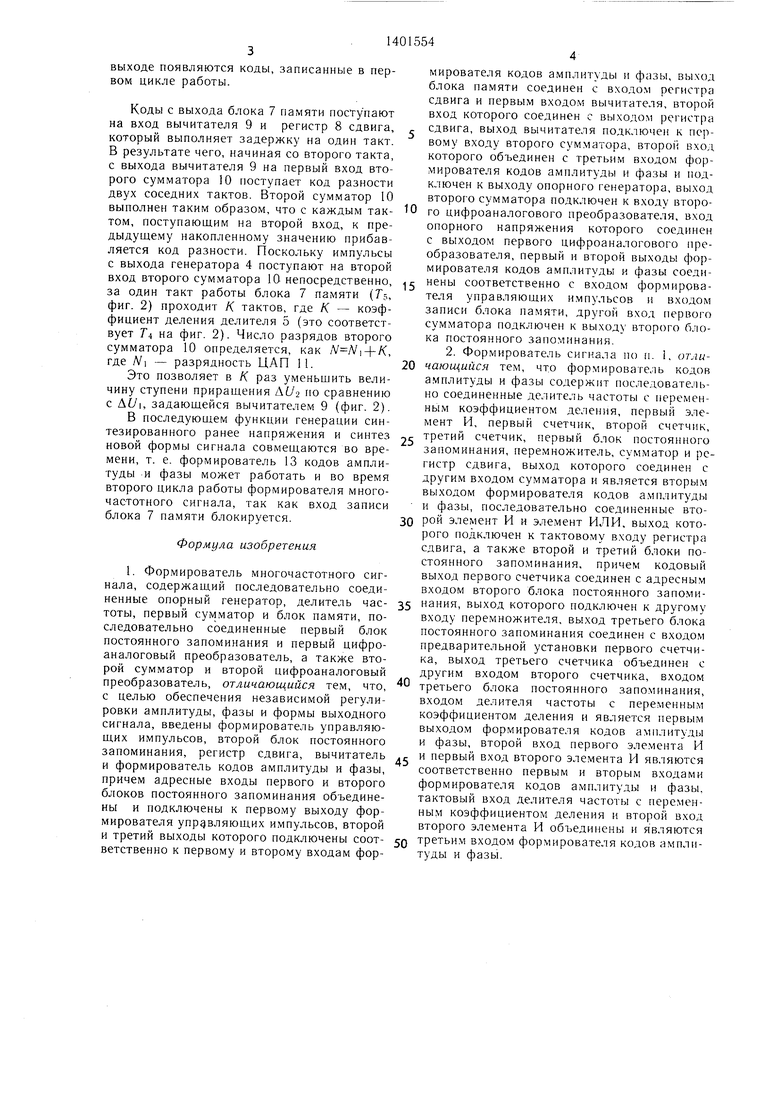

На фиг. 1 представлена структурная электрическая схема формирователя многочастотного сигнала и формирователя кодов амплитуды и фазы; на фиг. 2 - временная Q диаграмма, поясняющая работу формирователя многочастотного сигнала.

Формирователь многочастотного сигнала (фиг. 1) содержит формирователь 1 управляющих импульсов, второй блок 2 постоянного запоминания (БПЗ), первый блок 3 5 постоянного запоминания (БПЗ), опорный генератор 4, делитель 5 частоты, первый сумматор 6, блок 7 памяти, регистр 8 сдвига, вычитатель 9, второй сумматор 10, второй

ка 21, работающего в режиме вычитания и в котором предварительно записан код предыдущей гармоники (в начале - ноль). Импульс с выхода второго счетчика 21 увеличивает содержимое третьего счетчика 22 на единицу. Код с выхода счетчика 22 подается на вход БПЗ 23 и 17 и ДПКД 14. В БПЗ 23 хранятся коды амплитуд, а в БПЗ 17 - коды фаз гармонических составляющих выходного сигнала. Частота на выходе ДПКД 14 увеличивается в два раза, что соответствует второй гармонике, в то же время частота на втором выходе ДПКД 14, поступающая через элемент ИЛИ 24 на тактовый вход регистра 26 сдвига, остается неизменной. Во второй счетчик 21 записывается единица, следовательно, на его вход поступают два импульса переполнения с выхода первого счетчика 18 прежде чем на выходе второго счетчика 21 появится импульс. В это время на выходе БПЗ 23 прицифроаналоговый преобразователь (ЦАП) 2Q сутствует код, соответствующий амплитуде 11, первый ЦАП 12, формирователь 13 кодоввторой гармоники, на который в перемноамплитуды и фазы. Формирователь 13 кодовжителе 20 осуществляется умножение кодов

амплитуды и фазы содержит делитель 14от БПЗ 19. Полученные после умножения

частоты с переменным коэффициентом деле- коды суммируются в сумматоре 25 со знания (ДПКД), первый и второй элементычениями первой гармоники. После поступ- И 15 и 16, третий блок 17 постоянного за- 25 ления на вход третьего счетчика 23 импульса

от второго счетчика 21 на выходе третьего счетчика 22 устанавливается код следующей третьей гармоники. В дальнейщем на каждом щаге частота выходных импульсов ДПКД 14 увеличивается, возрастает также

поминания (БПЗ), первый счетчик 18, второй блок 19 постоянного запоминания (БПЗ)| перемножитель 20, второй 21 и третий 22 счетчики, первый блок 23 постоянного запоминания (БПЗ), элемент ИЛИ 24, сумматор 25, регистр 26 сдвига.

30 код, записанный во второй счетчик 21. Когда код на третьем счетчике 22 достигнет значения, соответствующего неучитываемой гармонике синтезируемого сигнала, срабатывает формирователь 1, в который предварительно заносится код неучитываемой

30 код, записанный во второй счетчик 21. Когда код на третьем счетчике 22 достигнет значения, соответствующего неучитываемой гармонике синтезируемого сигнала, срабатывает формирователь 1, в который предварительно заносится код неучитываемой

Формирователь многочастотного сигнала работает следующим образом.

Первый цикл работы заключается в синтезе формы выходного сигнала. Формирователь 1 выдает унравляющий потенциал по 35 гармоники. В результате разрещающий по- второму выходу на вход первого элемента тенциал снимается с второго выхода формирователя I и появляется на его третьем выходе. Следовательно, импульсы с выхода опорного генератора 4 поступают на тактовый вход регистра 26 сдвига, в результате чего коды синтезированной кривой переписываются из регистра 26 сдвига в блок 7 паИ 15. ДПКД 14 выполнен так, что на его выходе формируется первая гармоника сигнала (т. е. коэффициент деления ДПКД 14 максимальный). Импульсы с этой частотой 40 поступают на первый счетчик 18, на входе предварительной установки которого присутствует код от БПЗ. 17, определяющий начальную фазу первой гармоники. Па кодовом выходе первого счетчика 18 появляется нарастающий код, который поступает 45 на адресный вход БПЗ 19, работающего в режиме считывания информации. В БПЗ 19 хранятся двоичные коды синусоидального сигнала, которые поочередно подаются на неремножитель 20. В это время на другой ВХОД перемножителя 20 поступает код 111...II. С выхода перемножителя 20 коды через сумматор 25, на-другой вход которого в это время подается нулевой код, поступают на вход регистра 26 сдвига. За N тактов в регистр 26 сдвига запищется Л кодов, представляющих синусоидальный сигнал. Импульс переполнения с выхода первого счетчика 18 подается на вход второго счетчи50

55

мяти. На этом первый цикл работы формирователя многочастотного сигнала заканчивается.

Во втором цикле формирователь 1 подает управляющие сигналы на БПЗ 2 и 3. В БПЗ 3 хранятся коды начальной амплитуды, а в БПЗ 2 - коды начальной фазы выходного сигнала. Код начальной амплитуды поступает на вход ЦАП 12. С выхода ЦАП 12 на вход опорного напряжения ЦАП 11 поступает напряжение, соответствующее максимальному значению выходного сигнала. С выхода делителя 5 на вход первого сумматора 6 подаются импульсы, в результате чего на выходе первого сумматора 6 появляется нарастающий код. Код подается на вход блока 7 памяти, в результате на его

ка 21, работающего в режиме вычитания и в котором предварительно записан код предыдущей гармоники (в начале - ноль). Импульс с выхода второго счетчика 21 увеличивает содержимое третьего счетчика 22 на единицу. Код с выхода счетчика 22 подается на вход БПЗ 23 и 17 и ДПКД 14. В БПЗ 23 хранятся коды амплитуд, а в БПЗ 17 - коды фаз гармонических составляющих выходного сигнала. Частота на выходе ДПКД 14 увеличивается в два раза, что соответствует второй гармонике, в то же время частота на втором выходе ДПКД 14, поступающая через элемент ИЛИ 24 на тактовый вход регистра 26 сдвига, остается неизменной. Во второй счетчик 21 записывается единица, следовательно, на его вход поступают два импульса переполнения с выхода первого счетчика 18 прежде чем на выходе второго счетчика 21 появится импульс. В это время на выходе БПЗ 23 присутствует код, соответствующий амплитуде второй гармоники, на который в перемноот второго счетчика 21 на выходе третьего счетчика 22 устанавливается код следующей третьей гармоники. В дальнейщем на каждом щаге частота выходных импульсов ДПКД 14 увеличивается, возрастает также

0 код, записанный во второй счетчик 21. Когда код на третьем счетчике 22 достигнет значения, соответствующего неучитываемой гармонике синтезируемого сигнала, срабатывает формирователь 1, в который предварительно заносится код неучитываемой

5 гармоники. В результате разрещающий по- тенциал снимается с второго выхода формирователя I и появляется на его третьем выходе. Следовательно, импульсы с выхода опорного генератора 4 поступают на тактовый вход регистра 26 сдвига, в результате чего коды синтезированной кривой переписываются из регистра 26 сдвига в блок 7 пагармоники. В результате разрещающий по- тенциал снимается с второго выхода формирователя I и появляется на его третьем выходе. Следовательно, импульсы с выхода опорного генератора 4 поступают на тактовый вход регистра 26 сдвига, в результате чего коды синтезированной кривой переписываются из регистра 26 сдвига в блок 7 па

мяти. На этом первый цикл работы формирователя многочастотного сигнала заканчивается.

Во втором цикле формирователь 1 подает управляющие сигналы на БПЗ 2 и 3. В БПЗ 3 хранятся коды начальной амплитуды, а в БПЗ 2 - коды начальной фазы выходного сигнала. Код начальной амплитуды поступает на вход ЦАП 12. С выхода ЦАП 12 на вход опорного напряжения ЦАП 11 поступает напряжение, соответствующее максимальному значению выходного сигнала. С выхода делителя 5 на вход первого сумматора 6 подаются импульсы, в результате чего на выходе первого сумматора 6 появляется нарастающий код. Код подается на вход блока 7 памяти, в результате на его

выходе появляются коды, записанные в первом цикле работы.

Коды с выхода блока 7 памяти поступают на вход вычитателя 9 и регистр 8 сдвига, который выполняет задержку на один такт. В результате чего, начиная со второго такта, с выхода вычитателя 9 на первый вход второго сумматора 10 поступает код разности двух соседних тактов. Второй сумматор 10 выполнен таким образом, что с каждым тактом, поступающим на второй вход, к предыдущему накопленному значению прибавляется код разности. Поскольку импульсы с выхода генератора 4 поступают на второй вход второго сумматора 10 непосредственно, за один такт работы блока 7 памяти (Т,, фиг. 2) проходит К тактов, где К - коэффициент деления делителя 5 (это соответствует Г4 на фиг. 2). Число разрядов второго сумматора 10 определяется, как где М - разрядность ЦАП 11.

Это позволяет в К раз уменьщить величину ступени приращения Лб 2 tie сравнению с Af/i, задающейся вычитателем 9 (фиг. 2).

В последующем функции генерации синтезированного ранее напряжения и синтез новой формы сигнала совмещаются во времени, т. е. формирователь 13 кодов амплитуды и фазы может работать и во время второго цикла работы формирователя многочастотного сигнала, так как вход записи блока 7 памяти блокируется.

Формула изобретения

. сдвига, выход вычитателя подключен к первому входу второго сумматора, второй вход которого объединен с третьим в.ходом формирователя кодов амплитуды и фазы и подключен к выходу опорного генератора, выход второго сумматора подключен к входу второ0 го цифроаналогового преобразователя, вход опорного напряжения которого соединен с выходом первого цифроаналогового преобразователя, первый и второй выходы формирователя кодов амплитуды и фазы соеди5 иены соответственно с входом формирователя управляющих импульсов и входом записи блока памяти, другой вход первого сумматора подключен к выходу второго блока постоянного запоминания.

r третий счетчик, первый блок постоянного запоминания, перемножитель, сумматор и регистр сдвига, выход которого соединен с другим входом сумматора и является вторым выходом формирователя кодов амплитуды и фазы, последовательно соединенные вто0 рой элемент И и эле.мент ИЛИ, выход которого подключен к тактовому входу регистра сдвига, а также второй и третий блоки постоянного запоминания, причем кодовый выход первого счетчика соединен с адресным входом второго блока постоянного запоми5 нания, выход которого подключен к другому входу перемножителя, выход третьего блока постоянного запоминания соединен с входо.м предварительной установки первого счетчика, выход третьего счетчика объединен с другим входом второго счетчика, входом

0 третьего блока постоянного запоминания, входом делителя частоты с переменным коэффициентом деления и является первым выходом формирователя кодов амплитуды и фазы, второй вход первого элемента И

г и первый вход второго элемента И являются соответственно первым и вторым входами формирователя кодов амплитуды и фазы, тактовый вход делителя частоты с переменным коэффициентом деления и второй вход второго элемента И объединены и являются

0 третьим входом формирователя кодов амплитуды и фазь1.

.

75-

Фиг. 2

| Генератор сигналов инфранизких частот | 1984 |

|

SU1160522A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Цифровой синтезатор частот | 1984 |

|

SU1197043A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-06-07—Публикация

1986-12-03—Подача