татор 6 и сумматор 5 кодов сравнивают числа га и 2Р. Результат сравнения с коммутатора 6 через регистр 7 памяти и цифроаналоговый преобразователь 11 поступает на другой вход компаратора 9. На выходе компаратора формируется выходной сигнал цифрового синтезатора частот. В момент совпадения уровней на компараторе 9 RS-триггер 12 переходит в нулевое состояние, тем самэ1м 43 производя сброс ГПН 8 в исходное состояние. Элементы И 14, 15, ЛИ 16, D-триггер 13 и элемент задержки 20 формируют сигнал установки RS-триггера 12 в единичное состояние, при котором осуществляется запуск ГПН,8. Это происходит либо в моменты времени, совпадающие с тактовой частотой опорного генератора 18, либо со сдвигом на по|ловину этого периода, 1 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой синтезатор частоты | 1988 |

|

SU1529403A1 |

| Цифровой синтезатор частот | 1981 |

|

SU978314A1 |

| РАДИОПРИЕМНОЕ УСТРОЙСТВО МНОГОЧАСТОТНЫХ СИГНАЛОВ | 2005 |

|

RU2310992C2 |

| Синтезатор частоты с частотной модуляцией | 1986 |

|

SU1345343A1 |

| Устройство для измерения координат центра тяжести изображения объекта | 1988 |

|

SU1660208A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОРРЕЛЯЦИОННОЙ ФУНКЦИИ | 1992 |

|

RU2037198C1 |

| Цифровой синтезатор частот | 1988 |

|

SU1589366A1 |

| Генератор сигналов сложной формы | 1985 |

|

SU1280597A1 |

| Синтезатор частот | 1985 |

|

SU1363457A1 |

| Цифровой синтезатор частот | 1989 |

|

SU1704265A1 |

Изобретение относится к радиотехнике и может использоваться в технике связи и радиоизмерительных устройствах.

Цель изобретения - повышение быстродействия и улучшение спектральной чистоты выходного сигнала.

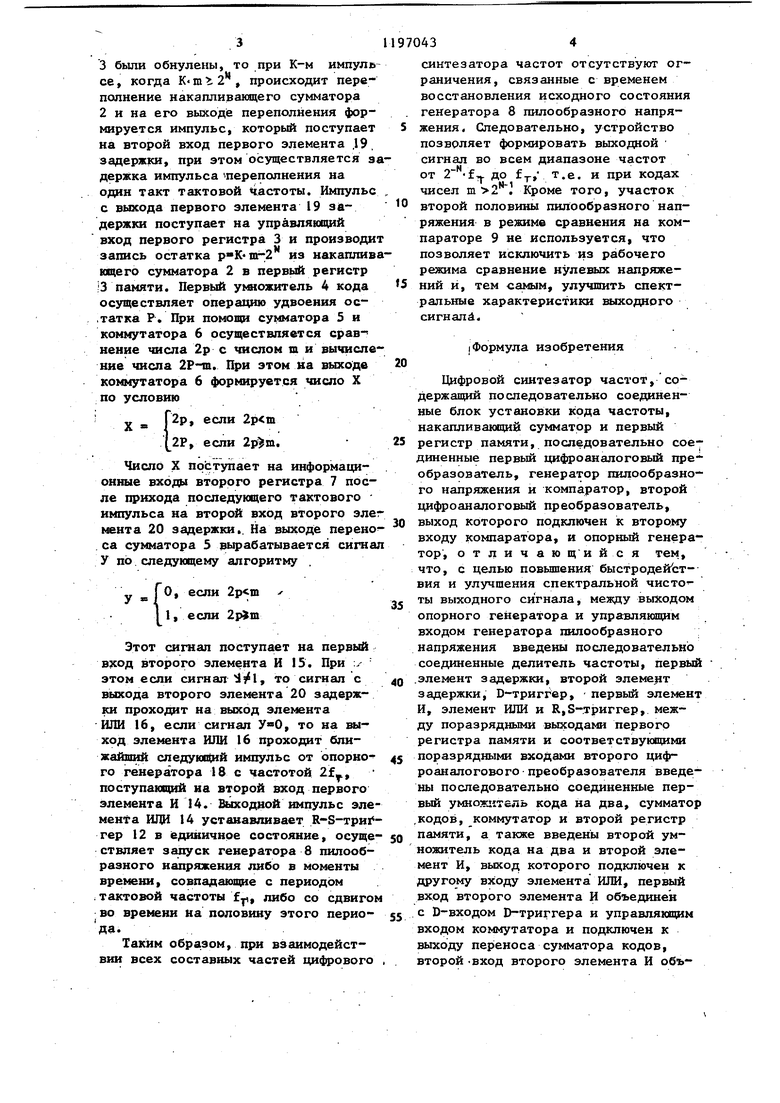

На чертеже представлена структурная электрическая схема предлагаемого цифрового синтезатора частот.

Цифровой синтезатор частот содержит бло 1 установки кода частоты, накапливающий сумматор 2, первый .регистр 3 памяти, первый умножитель 4 кода на два, сумматор 5 кодов, коммутатор 6, второй регистр 7 памяти, генератор пилообразного напряжения (ГПН) В, компаратор 9 первый цифроаналоговый преобразователь (ЦАП) 10, второй ЦАП П, R-S-триггер 12, D-триггер 13, первый элемент И 14, второй элемент И 15, элемент ИЛИ 16, делитель 17 частоты, опорный генератор 18, первый элемент 19 задержки, второй элемент 20 задержки, второй умножитель 21 кода на два.

Цифровой синтезатор частот работает спедуняцим образом.

С блока 1 установки двоичный код числа т, определяющего заданную частоту по формуле где

N

,2,3,.,2 , поступает на информационные входы второго умножителя 21 кода, накапливакнцего сумматора 2 и на сумматор 5. С выхода второго умножителя 21 кода код, соответствующий числу 2т, поступает на вход первого ЦАП 10, на выходе которого

формируется аналоговый уровень напряжения, который поступает на первьш вход генератора 8 пилообразного напряжения и задает на его выхо.

де амплитуду импульса линейного изменяющегося напряжения с отрицательным наклоном. С выхода генератора 8 пилообразного напряжения сигнал поступает на первый вход компаратора 9. Момент времени запуска генератора 8 пилообразного напряжения определяется моментом установки R-S-триггера 12 в единичное состояние по S-входу сигналом с. элемента ИЛИ 16, На другой вход компаратора 9 поступает напряжение с второго., ЦАП 11, уровень которого определяется выходным кодом второго регистра 7. В момент совпадения уровней сигнаг

лов, поступающих на входы компа{ атора 9, на его выходе формируется перепад напряжения, который переводит R-S-триггер 12 в нулевое состояние и, тем самым, производит сброс

генератора 8 пилообразного напряжения в исходное состояние. На выходе компаратора 9 формируется выходной сигнал цифрового синтезатора частот. Равномерность временной расстанрвки выходных импульсов достигается следующим образом.

По мере поступления тактовых импульсов с делителя 17 частоты,. который имеет коэффициент деления два, на тактовый вход накапливающего сумматора 2 . в нем к накопленной сумме добавляется число т. Если до прихода первого тактового импульса накапливающий сумматор 2 и первый регистр 3 бьши обнулены, то при К-м импулв се, когда К«т.2 , происходит переполнение накапливаияцего сумматора 2 и на его выходе переполнения формируется импульс, который поступает на второй вход первого элемента ,19. задержки, при этом осуществляется з держка импульса переполнения на один такт тактовой частоты. Импульс с выхода первого элемента 19 зйдержки поступает на управляющий вход первого регистра 3 и производи запись остатка р-К-пг-з из накаплив ющего сумматора 2 в первый регистр i3 памяти. Первый укшожитель 4 кода осуществляет операцию удвоения ос,татка Р. При помощи сумматора 5 и коммутатора 6 осуществляется срав нение числа 2р с числом ш и вычисле ние числа 2Р-т. При этом на выходе коммутатора 6 формируется число X по условию если если . Число X поступает на информационные входы второго регистра 7 после прихода последующего тактового импульса на второй вход второго эле мента 20 задержки.. На выходе перено са сумматора 5 вырабатывается сигна У по следующему алгоритму . если если Этот сигнал поступает на первый вход второго элемента И 15. При :.- этом если сигнал iт1, то сигнал с выхода второго элемента 20 задержки проходит на выход элемента ИЛИ 16, если сигнал , то на выход элемента ИЛИ 16 проходит ближайший следую1Е(ий импульс от опорно- го генератора 18 с частотой 2f, поступающий на второй вход первого элемента И 14. Выходной импульс эле мента ИДИ 14 устанавливает К-З-три гер 12 в единичное состояние, осуще ствляет залуск генератора 8 пилообразного напряжения либо в моменты времени, совпадающие с периодом ;тактовой частоты f, либо со сдвиго во времени на половину этого периода. . Таким образом, при взаимодействии всех составных частей цифрового синтезатора частот отсутствуют ограничения, связанные с временем восстановления исходного состояния генератора 8 пилообразного напряжения. Следовательно, устройство позволяет формировать выходной сигнал во всем диапазоне частот от до , т.е. и при кодах чисел m Кроме того, участок второй половины пилообразного напряжения в режиме сравнения на компараторе 9 не используется, что позволяет исключить из рабочего режима сравнение нулевых напряжений и, тем самым, улучшить спектралыше характеристики доходного сигнал. {Формула изобретения Цифровой синтезатор частот, содержащий последовательно соединенные блок установки кода частоты, накапливающий сумматор и первый регистр памяти, последовательно соединенные первый 1Ц{фроаналоговый преобразователь, генератор пилообразного напряжения и компаратор, второй цифроаналоговый преобразователь, выход которого подключен к второму входу компаратора, и опорный генератор, отличающийся тем, что, с целью повышения быстродейЪтвия и улучшения спектральной чистоты выходного сигнала, между выходом опорного генератора и управляющим входом генератора пилообразного напряжения введены последовательно соединенные делитель частоты, первый элемент задержки, второй элемент задержки, D-триггер, первый элемент И, элемент ИЛИ и Е,8-.т|риггер, между поразрядными выходами первого регистра памяти и соответствующими поразрядными входами второго цифроаналоговогопреобразователя введены последовательно соединенные первый умножитель кода на два, сумматор кодов, коммутатор и второй регистр памяти, а также введены второй умножитель кода на два и второй элемент И, выход которого подключен к другому входу элемента ИЛИ, первый вход второго элемента И объединен с D-входом D-триггера и управляющим входом коммутатора и подключен к выходу пер еноса сумматора кодов, второй -вход второго элемента И объединен Q управляющим входом второго регистра памяти и подключен к выходу второго элемента задержки, второй вход которого соединен с выходом делителя частоты, S-вход D-триггера подключен к выходу элемента ИЛИ, а R-вход Е,3-тряггера соединен с выходом компаратора, второй вход первого элемента И подсоединен к второму выходу опорного генератора, поразрядные входы второго умножнт-еля кода на два объединены с соответствующими входами второй группы входов сумматора кодов, и подключены к соответствующим выходам блока установки кода

частоты, поразрядные выxoдь второго множителя кода на два подключены к соответствующим поразрядным вхоам первого цифроаналогового преобразователя, поразрядные выходы первого умножителя кода на два соединены с соответствующими входами второй группы входов коммутатора,

второй вход первого элемента задержки подключен к выходу переполне-i ния накапливающего сумматора, тактовый вход накапливаняцего сумматора подключен к выходу делителя частоты, а тактовый вход первого регистра памяти подключен к выходу первого элемента задержки.

| Патент QUA | |||

| 3882403, кл | |||

| Способ переработки сплавов меди и цинка (латуни) | 1922 |

|

SU328A1 |

| Цифровой синтезатор частот | 1981 |

|

SU978314A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-12-07—Публикация

1984-10-03—Подача