/XW

ьэ

со о ч

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения длительности импульсных сигналов | 1988 |

|

SU1599838A1 |

| Устройство для измерения длительности импульса | 1989 |

|

SU1746357A1 |

| Устройство для измерения длительности импульса | 1989 |

|

SU1684732A1 |

| Измеритель длительности импульсов | 1985 |

|

SU1399695A1 |

| Измеритель длительности и временного положения импульса | 1988 |

|

SU1659973A1 |

| УСТРОЙСТВО ПОДАВЛЕНИЯ ПОМЕХ ДЛЯ ПРИЕМНИКОВ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 2003 |

|

RU2253183C1 |

| Устройство для измерения длительности импульсных сигналов | 1984 |

|

SU1330604A1 |

| Частотный дискриминатор | 1988 |

|

SU1676078A2 |

| Устройство для измерения защищенности сигнала от помех | 1986 |

|

SU1376249A1 |

| Устройство для измерения длительности импульсов | 1984 |

|

SU1251016A1 |

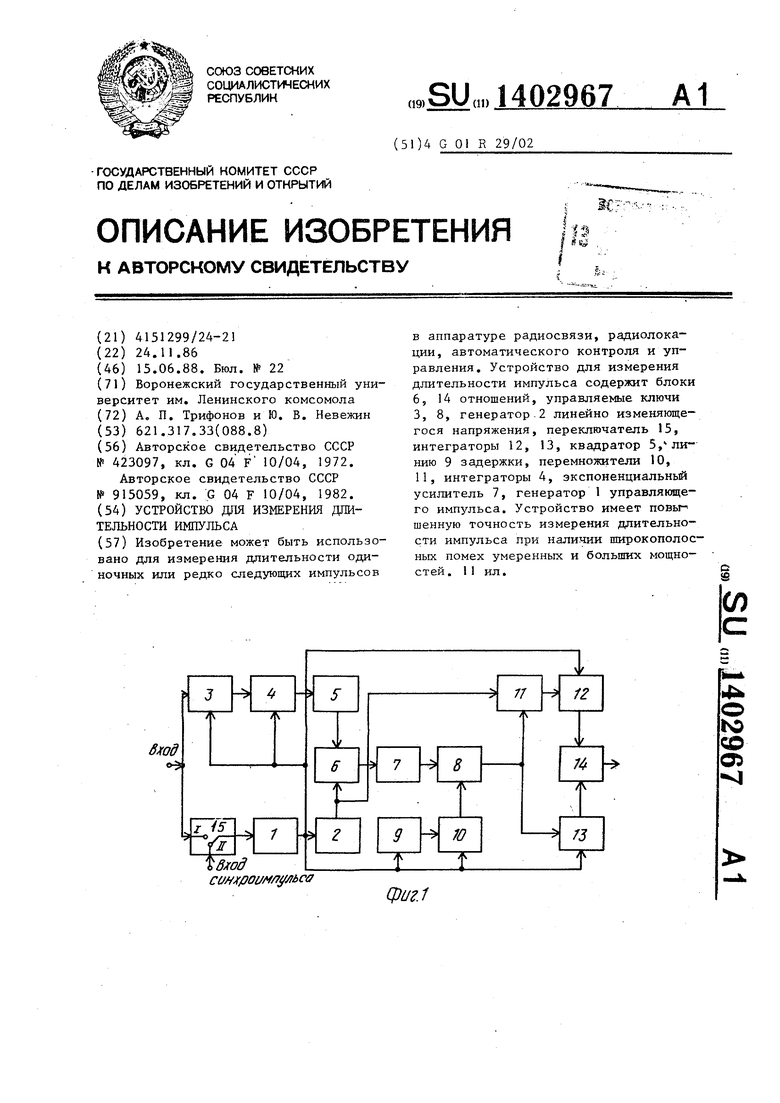

Изобретение может быть использовано для измерения длительности одиночных или редко следующих импульсов в аппаратуре радиосвязи, радиолокации, автоматического контроля и управления. Устройство для измерения длительности импульса содержит блоки 6, 14 отношений, управляемые ключи 3, 8, генератор-2 линейно изменяющегося напряжения, переключатель 15, интеграторы 12, 13, квадратор 5, линию 9 задержки, перемножители 10, 11, интеграторы 4, экспоненциальный усилитель 7, генератор 1 управляющего импульса. Устройство имеет повьп шенную точность измерения длительности импульса при наличии широкополосных помех умеренных и больших мощностей. 1 1 ил. О

cwjfflOVff/ yMca

фиг.1

1140

Изобретение относится к радиотехнике и мажет быть использовано для измерения длительности одиночных или редко следующих импульсов в со- ставе аппаратуры радиосвязи, радиолокации, автоматического контроля и управления,

Целью изобретения является повышение точности измерения длительно- сти.импульса при наличии широкополосных помех умеренных и больших мощностей

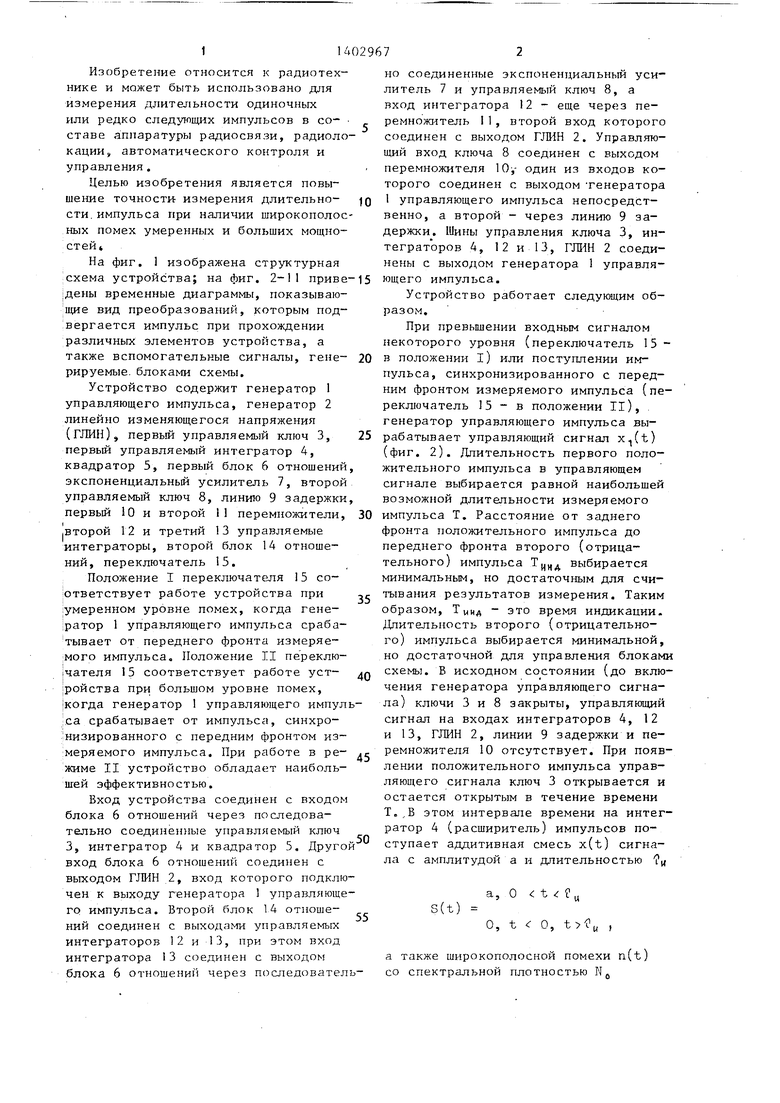

На фиг, 1 изображена структурная

схема устройства; на фиг. 2-11 приве-15 ющего импульса.

;дены временные диаграммы, показывающие вид преобразований, которым под- :вергается импульс при прохождении различных элементов устройства, а также вспомогательные сигналы, генерируемые, блоками схемы.

Устройство содержит генератор 1 управляющего импульса, генератор 2 линейно изменяющегося напряжения (глин), первый управляемый ключ 3, первый управляемый интегратор 4, квадратор 5, первый блок 6 отношений экспоненциальньй усилитель 7, второй управляемьй ключ 8, линию 9 задержки первый 10 и второй 11 перемножители, второй 12 и третий 13 управляемые

интеграторы, второй блок 14 отношений, переключатель 15.

Положение I переключателя 15 соответствует работе устройства при умеренном уровне помех, когда гене- |ратор 1 управляющего импульса сраба- тывает от переднего фронта измеряе- ;мого импульса. Положение II переклю- чателя 15 соответствует работе уст- |ройства при большом уровне помех, 1когда генератор 1 управляющего импул ;Са срабатывает от импульса, синхро- низированного с передним фронтом из- ;меряемого импульса. При работе в ре- жиме II ycTpofiCTBO обладает наибольшей эффективностью.

Вход устройства соединен с входом блока 6 отношений через последовательно соединенные управляемый ключ 3, интегратор 4 и квадратор 5. Друго вход блока 6 отношений соединен с выходом ГЛИН 2, вход которого подключен к выходу генератора 1 управляющего импульса. Второй блок 14 отношений соединен с выходами управляемых интеграторов 12 и 13, при этом вход интегратора 13 соединен с выходом блока 6 отнощений через пс следовател

но соединенные экспоненциальный усилитель 7 и управляемый ключ 8, а вход интегратора 12 - еще через перемножитель I1, второй вход которого соединен с выходом ГЖН 2. Управляющий вход ключа 8 соединен с выходом перемножителя 10-,- один из входов которого соединен с выходом генератора 1 управляющего импульса непосредственно, а второй - через линию 9 задержки. Шины управления ключа 3, интеграторов А, 12 и 13, ГЛИН 2 соединены с выходом генератора 1 управля0

0

0

Устройство работает следующим образом.

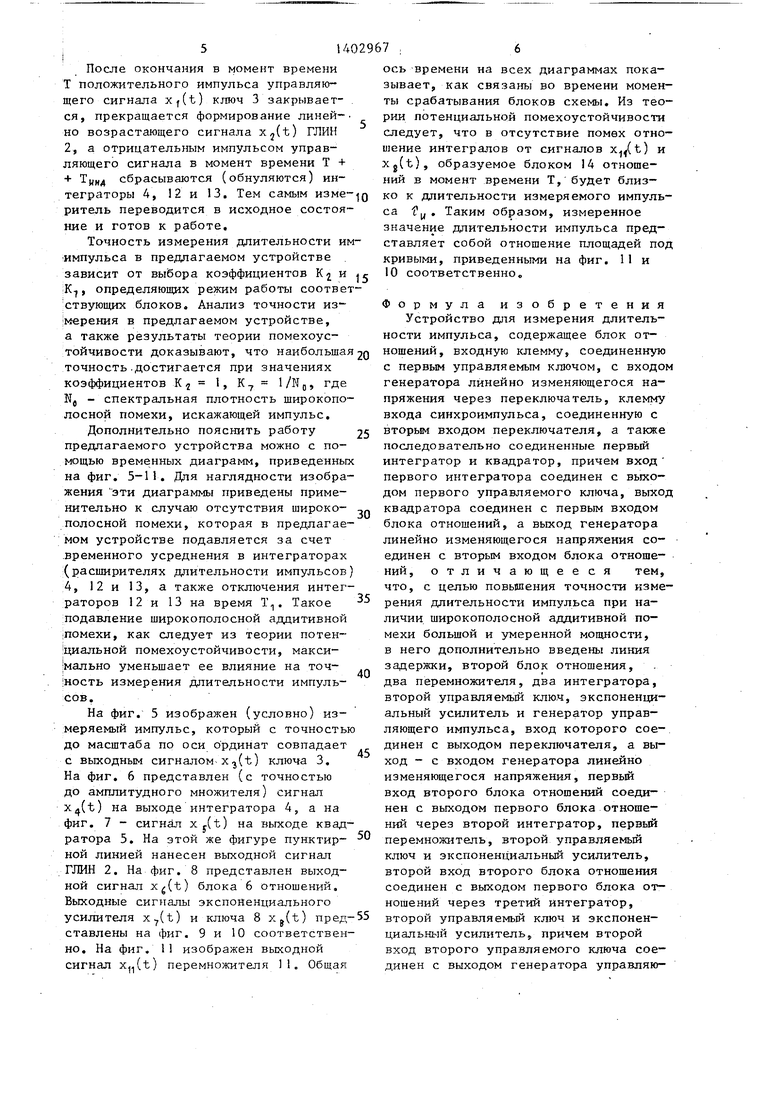

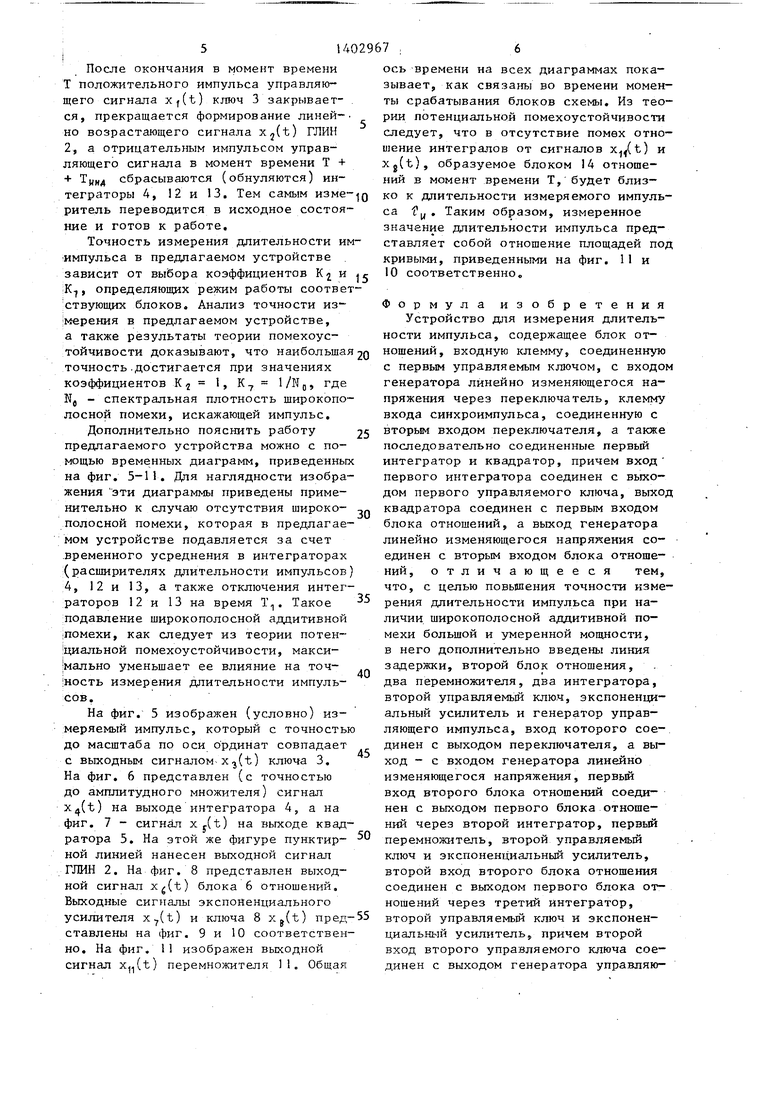

При превышении входным сигналом некоторого уровня (переключатель 15 - в положении I) или поступлении импульса, синхронизированного с передним фронтом измеряемого импульса (переключатель 15 - в положении II), генератор управляющего импульса вы5 рабатывает управляющий сигнал x(t) (фиг. 2). Длительность первого положительного импульса в управляющем сигнале выбирается равной наибольшей возможной длительности измеряемого импульса Т. Расстояние от заднего фронта положительного импульса до переднего фронта второго (отрицательного) импульса выбирается минимальным, но достаточным для счи-

5 тывания результатов измерения. Таким образом, ТИНА - это время индикации. Длительность второго (отрицательного) импульса выбирается минимальной, но достаточной для управления блоками схемы. В исходном состоянии (до включения генератора управляющего сигнала) ключи 3 и 8 закрыты, управляющий сигнал на входах интеграторов 4, 12 и 13, ГЛИН 2, линии 9 задержки и перемножителя 10 отсутствует. При появлении положительного импульса управляющего сигнала ключ 3 открывается и остается открытым в течение времени Т.,В этом интервале времени на интегратор 4 (расширитель) импульсов поступает аддитивная смесь x(t) сигнала с амплитудой а и длительностью

0

и

О

S(t)

О, t О, t

I

а также широкополосной помехи n(t) со спектральной плотностью N

x(t) S(t) + n(t) .

Ha выходе интегратора 4 формируется сигнал

t

,(t) S x(t )dt

С поступлением положительного им- 0 пульса управляющего сигнала на вход ГЛИН 2 последний начинает вырабатывать линейно воэрастаю1ций сигнал

x,(t) Kjt.

На выходе квадратора 5 формируется сигнал

{

Xj(t) X(t) 1 X(t )dt

с

Сигналы X2(t) и Xj(t) поступают на входы блока 6 отношений, выходной сигнал которого

X(t) Xy(t)(X;j(t)

J x(t )dt f/K,t. .

Xi/t) X«(t).X,(t) о

Таким образом, на вход интеграторов 12 и 13 входные сигналы x(t) и XgCt) начинают поступать после момента времени Т при t Т на выходах интеграторов формируются сигналы: на выходе интегратора 12 i

x,t) S K2t x(t )dt ,,

На выходе интегратора 13 i

x,j(t) 5 x(t )dt .

Т,

Kj S t S x(t )dt TI

Ti

1 exp K, 5 (t ),t5dt

Таким образом, величина х(т) представляет собой измеренное значе402967

С выхода блока.6 отношений сигнал поступает на усилитель 7 с экспоненциальной динамической характеристикой, формирующий выходной сигнал вида

x,(t) expLK xJt)

5 x(t ),t. о

С выхода экспоненциального усилителя 7 на последующие блоки схемы сигнал поступает через ключ 8, кото- рьш открывается с задержкой на время

:Т ТКНА относительно переднего фронта положительного импульса управляющего сигнала, где Т - минимально возможная длительность измеряемого импульса. Задержка обеспечивается тем, что управляющий сигнал ключа 8 ) (фиг. 4) представляет собой результат перемножения управляющего импульса X ,(t) (фиг. 2)и управ- .ляющего импульса x(t), прошедшего

через линию 9 задержки (фиг. З) со временем задержки Т.

Перемножитель 11 формирует произведение x(t) сигнала.-Xj(t) с выхода 2Q ГЛИН 2 и сигнала Xj(t) с выхода клю-, ча 8:- .,

x,(t). Т, с t Т

t с T,,t 7 т

В результате на выходе блока 14 отношений формируется сигнал

x(t) x(t)/x,j(t).

Этот сигнал зависит от времени только п{)и t Т. При t Т этот сигнал представляет собой постоянную вели чину, численно равную измеренному значению длительности входного импульса. Если выходной сигнал устройства x(t) выразить через входную смесь импульса и помехи x(t), то в

интервале времени от Т до Т + Т получим

ние неизвестной длительности входного импульса.

После окончания в момент времени Т положительного импульса управляющего сигнала Xf(t) ключ 3 закрывается, прекращается формирование линей-. но возрастающего сигнала Xj(t) ГЛИН 2, а отрицательным импульсом управляющего сигнала в момент времени Т + + сбрасываются (обнуляются) интеграторы 4, 12 и 13. Тем самым изме- д ритель переводится в исходное состояние и готов к работе.

Точность измерения длительности им- импульса в предлагаемом устройстве зависит от выбора коэффициентов К2 и ir K-J, определяющих режим работы соответ- Ътвующих блоков. Анализ точности из- |мерения в предлагаемом устройстве, а также результаты теории помехоустойчивости доказывают, что наибольшая2Q ношений, входную клемму, соединенную

точность .достигается при значениях коэффициентов К .2 т где NJ - спектральная плотность щирокопо- лосной помехи, искажающей импульс.

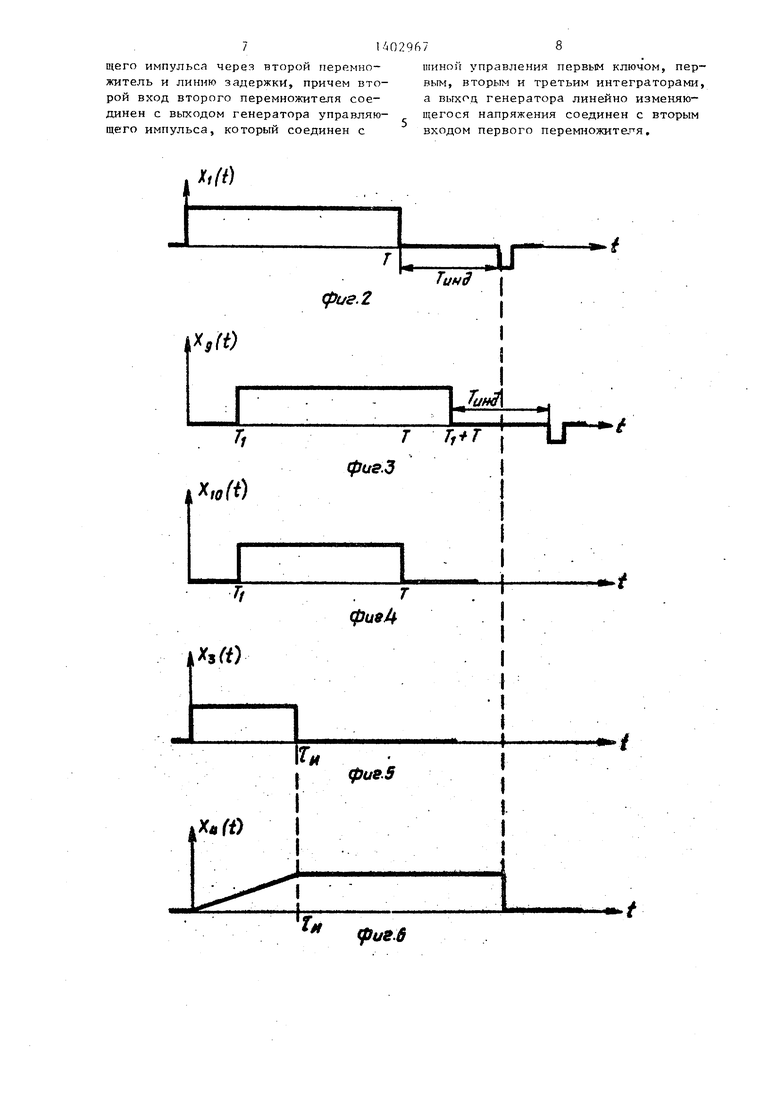

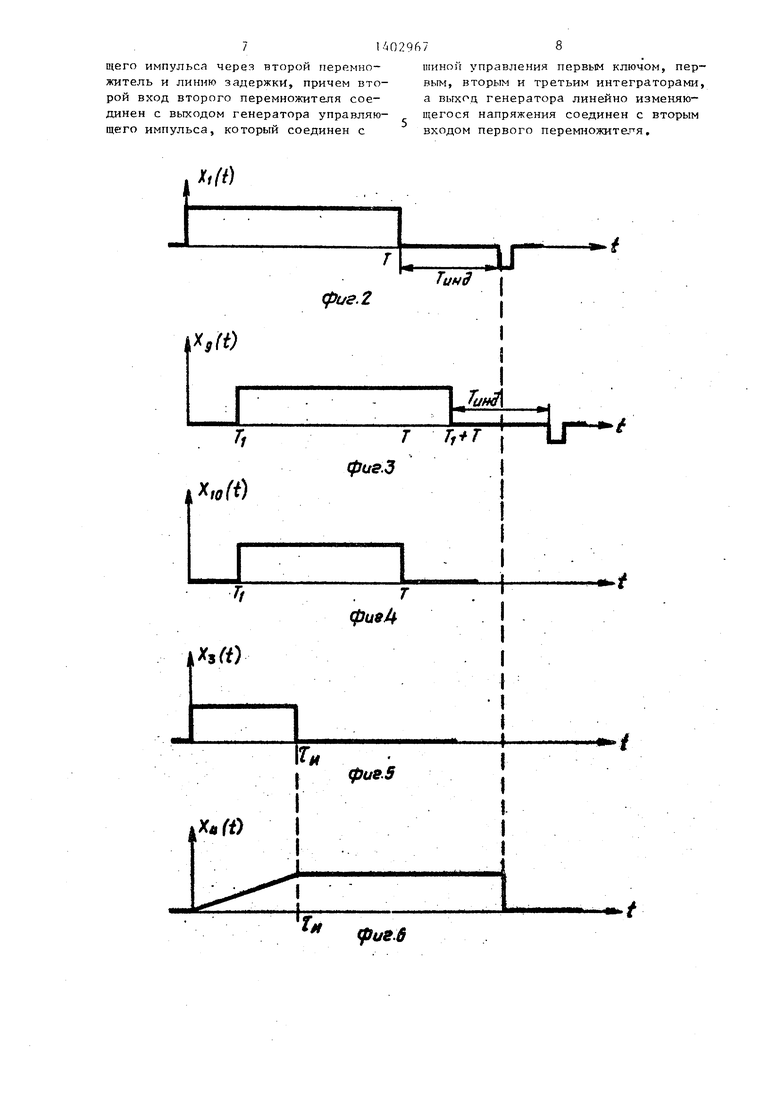

Дополнительно пояснить работу предлагаемого устройства можно с помощью временных диаграмм, приведенных на фиг. 5-11. Для наглядности изображения эти диаграммы приведены применительно к случаю отсутствия широкополосной помехи, которая в предлагаемом устройстве подавляется за счет .временного усреднения в интеграторах (расширителях длительности импульсов 4, 12 и 13, а также отключения интеграторов 12 и 13 на время Т,. Такое подавление широкополосной аддитивной :помехи, как следует из теории потен- щиальной помехоустойчивости, макси- |мально уменьшает ее влияние на точ- :ность измерения длительности импульсов.

На фиг. 5 изображен (условно) измеряемый импульс, который с точностью до масштаба по оси ординат совпадает с вьпсодным сигналом-x.j(t) ключа 3. На фиг. 6 представлен (с точностью до амплитудного множителя) сигнал x(t) на выходе интегратора 4, а на фиг. 7 - сигнал Xy(t) на выходе квадратора 5. На этой же фигуре пунктирной линией нанесен выходной сигнал ГЛИН 2. На фиг. 8 представлен выходной сигнал Xg(t) блока 6 отношений. Выходные сигналы экспоненциального усилителя yLj(t} и ключа 8 Xj(t) представлены на фиг. 9 и 10 соответственно. На фиг. 1 изображен выходной сигнал x,(t) перемножителя 11. Общая

ось времени на всех диаграммах показывает, как связаны во времени моменты срабатывания блоков схемы. Из теории потенциальной помехоустойчивости следует, что в отсутствие помех отношение интегралов от сигналов x(t) и Xg(t), образуемое блоком 14 отношений в момент времени Т, будет близко к длительности измеряемого импульса 1 . Таким образом, измеренное значение длительности импульса представляет собой отношение площадей под кривыми, приведенными на фиг. 11 и 10 соответственно.

Формула изобретения Устройство для измерения длительности импульса, содержащее блок от0

5

5

5

0

5

0

с первым управляемым ключом, с входом генератора линейно изменяющегося напряжения через переключатель, клемму входа синхроимпульса, соединенную с вторым входом переключателя, а также последовательно соединенные первьй интегратор и квадратор, причем вход первого интегратора соединен с выходом первого управляемого ключа, выход квадратора соединен с первым входом блока отношений, а выход генератора линейно изменяющегося напряжения соединен с вторым входом блока отношений, отличающееся тем, что, с целью повышения точности измерения длительности импульса при наличии широкополосной аддитивной помехи большой и умеренной мощности, в него дополнительно введены линия задержки, второй блок отношения, два перемножителя, два интегратора, второй управляемый клю.ч, экспоненциальный усилитель и генератор управляющего импульса, вход которого соединен с выходом переключателя, а выход - с входом генератора линейно изменяющегося напряжения, первый вход второго блока отношений соединен с выходом первого блока отношений через второй интегратор, первый перемножнтель, второй управляемьш ключ и экспоненциальный усилитель, второй вход второго блока отношения соединен с выходом первого блока отношений через третий интегратор, второй управляемьй ключ и экспоненциальный усилитель, причем второй вход второго управляемого ключа соединен с выходом генератора управляю-

щего импульса через второй перемножитель и линию задержки, причем второй вход второго перемножителя соединен с выходом генератора управляющего импульса, который соединен с

т

шиной управления первым ключом, первым, вторым и третьим интеграторами, а выход генератора линейно изменяющегося напряжения соединен с вторым входом первого перемножитаг я.

fpusS

Г Фие.в

Ти

фиг. 9

)(Ю

/ |Гх

fiuf fO

iXfrff)

/ г

. ft

| 1972 |

|

SU423097A1 | |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Авторское свидетельство СССР № 915059, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1988-06-15—Публикация

1986-11-24—Подача