Изобретение относится к импульсной технике, может быть использовано в многоканальных модемах передачи дискретной информации с ортогональными сигналами для автоматической подстройки частоты м является усовершенствованием изобретения по авт. св. № 1359099.

Цель изобретения - повышение точности измерения сдвига частоты в условиях действия помех.

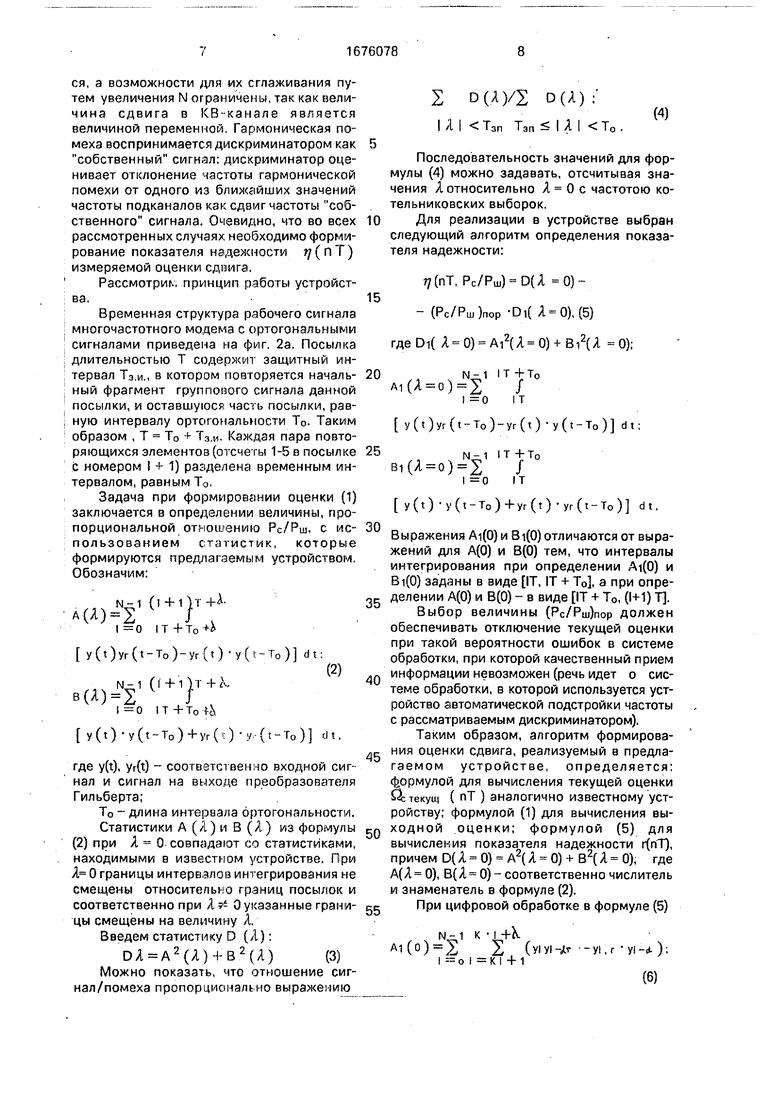

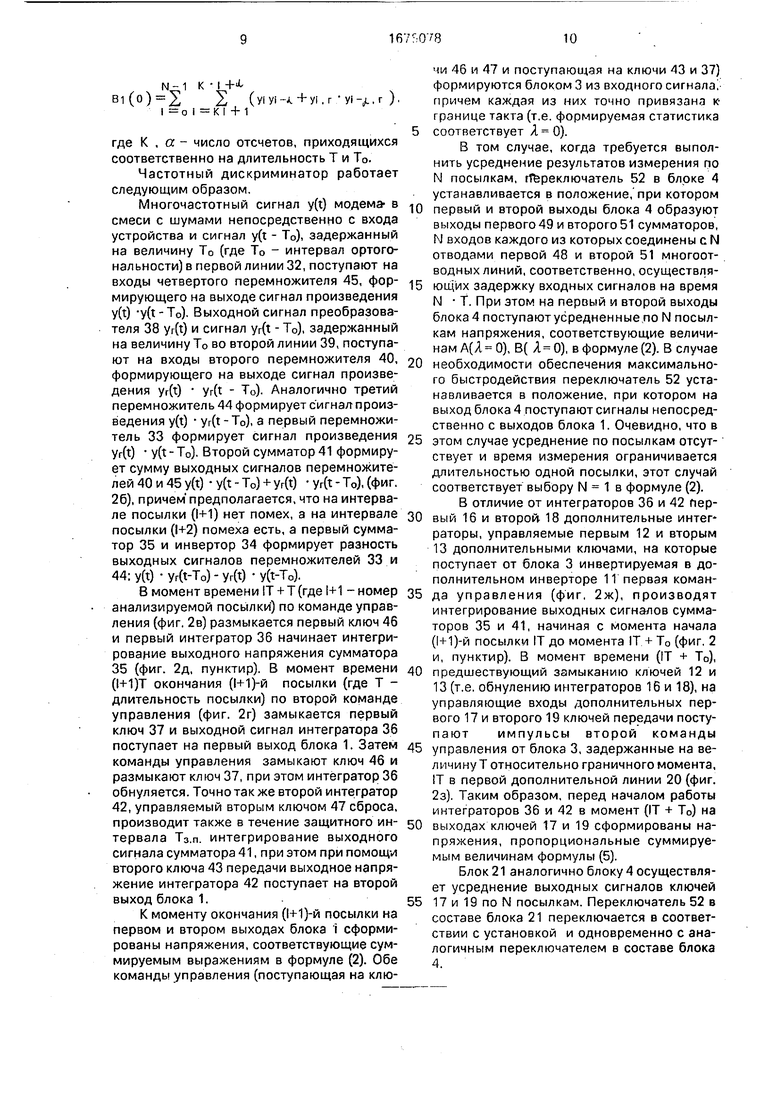

На фиг. 1 показана структурная электрическая схема устройства; на фиг. 2 -эпюры, поясняющие работу дискриминатора.

Устройство содержит блок 1 входной обработки, вход которого соединен с входной шиной 2 и сходом блока 3 управления. Первый и второй выходы блока 1 соединены соответственно с первым и вторым входами блока 4 усреднения по посылкам, первый и второй выходы которого соединены соответственно с входами первого и второго ключей 5 и б, выходы которых соединены соответственно с первым и вторым входами блока 7 памяти, первый и второй выходы которого соединены соответственно с первым и вторым входами блока 8 сравнения, выход которого через функциональный преобразователь 9 соединен с выходной шиной 10 устройства. Первый выход блока 3 соединен с первым управляющим входом блока 1, а также с входом дополнительного инвертора 11, выход которого присоединен к соединенным вместе управляющим дополнительных первого и второю ключей 12 и 13 сброса. Второй выход блока 3 соединен с вторым управляющим входом блока 1, а также с первым входом эловден а И 14, второй вход которого соединен с третьим выходом блока 3, а выход - с входом третьего ключа 15, выход которого соединен е управляющим входом блока 7, Четвертый выход блока 3 соединен с управляющим входом блока 8. Первый дополнительный выход блока 1 подключен к последовательно соединенным первому дополнительному интегратору 16 и первому дополнительному ключу 17 передачи. Второй дополнительный выход блока 1 подключен к последовательно соединенным второму дополнительному интегратору 18 и второму дополнительному ключу 19 передачи. Управляющие входы первого 17 и второго 19 дополнительных

ключей объединены и подключены к выходу первой дополнительной линии 20 задержки, вход которой также подключен к второму выходу блока 3. Первый и второй выходы первого дополнительного ключа 12 соедийены, соответственно, с первым и вторым управляющими входами интегратора 16, а первый 1 второй выходы второго дополнительного ключа 13 соединены, соответственно, с первым и вторым управляющими

входами интегратора 18. Выходы ключей 17 и 19 подключены, соответственно, к первому и второму входам дополнительного блока 21 усреднения по посылкам, первый выход которого соединен с последовательно соедипенными первым квадратором 22, пер- гшм дополнительным сумматором 23, второй дополнительной линией 24 задержки и компаратором 25, при этом первый выход блока4 также соединен с последовательно соединенными вторым квадратором

26,вторым дополнительным сумматором

27,дополнительным перемножителем 28, выход которого соединен с вторым входом компаратора 25, а второй вход перемножителя 28 соединен с шиной 29 порогового н пряжения. Вторые выходы блоков 21 и 4 усреднения по посылкам соединены, соответственно, с входами третьего 30 и четвертого 31 квадраторов, выходы которых

соединены, соответственно, с вторыми входами первого 23 и второго 27 дополнительных сумматоров, Выход компаратора 25 присоединен к соединенным вместе управляющим входам ключей 5, 6 и 15.

Блок 1 содержит последовательно соединенные первую линию 32 задержки, первый перемножитель 33, инвертор 34, первый сумматор 35, первый интегратор 36, первый ключ 37 передачи, последовательно

соединенные преобразователь Гильберта 38, вторую линию 39 задержки, второй перемножитель 40, второй сумматор 41, второй интегратор 42, второй ключ 43

передачи, а также содержит третий 44 и четвертый 45 перемножители, первый 46 и второй 47 ключи сброса. Вторые входы перемножителей 33 и 40 соединены с выходом преобразователя 38, а вторые входы перемножителей 44 и 45 соединены, соответственно, с выходами линий 39 и 32 задержки. Выходы перемножителей 44 и 45 соединены с вторыми входами, соответственно, сумматоров 35 и 41. Соединенные вместе входы линии 32 задержки, преобразователя 38, первые входы перемножителей 44 и 45 являются первым входом блока 1. Первый и второй выходы ключа 46 соединены соответственно с первым и вторым управляющими входами интегратора 36, а первый и второй выходы ключа 47 соединены соответственно с первым и вторым управляющими входами интегратора 42, причем управляющие входы ключей 46 и 47, соединенные вместе, являются первым входом управления блока 1. Соединенные вместе входы управления ключей 37 и 43 являются вторым входом управления блока 1, а выходы ключей 37 и 43 являются соответственно первым дополнительным выходом блока 1. Выход сумматора 35 является первым дополнительным выходом блока 1, а выход сумматора43-вторымдополнительным выходом блока 1.

Блок 4 и аналогичный ему блок 21 каждый содержит последовательно соединенные первую многоотводную линию 48 задержки и первый суматор 49 усреднения, последовательно соединенные вторую многоотводную линию 50 задержки и второй сумматор 51 усреднения, а также переключатель 52, при этом выходы сумматоров 49 и 51 подключены соответственно к первому и второму замыкающим контактам переключателя 52, первый размыкающий контакт которого, соединенный с входом линии 48, является первым входом блока, а второй размыкающий контакт, соединенный с входом линии 50, - вторым входом блока 4 или 21. Первый и второй переключающие контакты переключателя 52 являются соответственно первым и вторым выходами блока 4 или 21. Переключатели 52 в блоках 4 и 21 механически связаны и переключаются одновременно в одинаковые положения. Блок 3 управления аналогичен блоку управления по основному изобретению и также включает в себя известное устройство тактовой синхронизации (авт. св. № 649147). Блоки 7-9 также полностью аналогичны блокам устройства по основному изобретению.

Рассмотрим предлагаемое дополнение к основному алгоритму измерения сдвига, которое позволяет повысить точность фор

мирования оценки сдвига. Если обозначить: &с вых(пТ) - оценка сдвига на выходе дискриминатора на тактовом интервале (п-1)д-Т t n Т (Т-длительность посылки); Ос текут (пТ - текущая оценка сдвига, формируемая на n-м тактовом интервале, то оценка на выходе дискриминатора определяется выражением

IV

О:вых (пТ) Оггекущ (пТ)/(пТ, Рс/Рш) + + 4вых(п-1)Т 1-7/ (П Т, Рс/Рш),

0)

где .

7(пТ, Рс/Рш )

1 при ( Рс/Рш ) ( Рс/Рш ) пор :

О при ( РС/РШ ) (Рс/Рш ) пор ;

(Рс/Рш) - отношение мощности Рс сигнала и мощности Рш помех в канале;

(Рс/Рш)пор - пороговое значение Рс/Рш (при уменьшении Рс/Рш) на текущем такте

ниже порогового, качество текущей оценки становится неприемлемым.

Таким образом, на вцход дискриминатора поступает оценка Оггекущ (пТ), сформированная на текущем такте, если

надежность т;(пТ) этой оценки высока; если же надежность неудовлетаорительна, то на выход дискриминатора поступает выходная оценка, сформированная на предыдущем такте.

Рассмотрим ситуации, когда использование оценки (1) необходимо. В проводных каналах связи при номинальном уровне сигнала сглаживания на N посылках достаточно для того, чтобы обеспечить требуемое

качество оценки (проводной канал стационарен на больших отрезках времени и значение N можно выбрать большим). Однако если кратковременные занижения уровня являются частыми, то необходимо предусматривать защиту от возможного появления ложных оценок (т.е. оценок с неприемлемой погрешностью измерения). В КВ-канале радиосвязи на качество оценки влияют флук- туационная помеха (уровень которой растет

при замираниях сигнала), многолучевость, особенно дискретная (появление явно различных эхо-сигналов) и узкополосная помеха. В многолучевом узкополосном канале система тактовой синхронизации определяет границы посылок по наиболее мощному лучу, остальные эхо-сигналы, несущие информацию об одной и той же посылке, являются помехами при оценке сдвига, причем уровень этих помех непрерывно изменяется, а возможности для их сглаживания путем увеличения N ограничены, так как величина сдвига в КВ-канале является величиной переменной, Гармоническая помеха воспринимается дискриминатором как собственный сигнал: дискриминатор оценивает отклонение частоты гармонической помехи от одного из ближайших значений частоты подканалов как сдвиг частоты собственного сигнала. Очевидно, что во всех рассмотренных случаях необходимо формирование показателя надежности гу(пТ) измеряемой оценки сдвига.

Рассмотрим принцип работы устройства.

Временная структура рабочего сигнала многочастотного модема с ортогональными сигналами приведена на фиг. 2а. Посылка длительностью Т содержит защитный интервал Тз.и., в котором повторяется начальный фрагмент группового сигнала данной посылки, и оставшуюся часть посылки, равную интервалу ортогональности Т0. Таким образом , Т Т0 + Т3.и. Каждая пара повторяющихся элементов (отсчеты 1-5 в посылке с номером I + 1) разделена временным интервалом, равным То.

Задача при формировании оценки (1) заключается в определении величины, пропорциональной отношению Рс/Рш, с использованием статистик, которые формируются предлагаемым устройством. Обозначим:

1Т+Т0+

(2)

y(t)yr(t-T0)-yr(t) -y(t-To) dt:

в(А)( +

IT+To y(t)-y(t-To)+yr(t)-yr(t-T0) dt,

где y(t), yr(t) - соответственно входной сигнал и сигнал на выходе преобразователя Гильберта;

Т0 - длина интервала ортогональности.

Статистики А(А)иВ(А) из формулы (2) при А 0 совпадают со статистиками, находимыми в известном устройстве. При А 0 границы интервалов интегрирования не смещены относительно границ посылок и соответственно при А 0указанные границы смещены на величину А.

Введем статистику D (А):

(A) + B2(A)(3)

Можно показать, что отношение сигнал/помеха пропорционально выражению

2 D(A)/2 D (A):

I А I Тзп Тэп I А I То .

(4)

Последовательность значений для формулы (4) можно задавать, отсчитывая значения А относительно А 0 с частотою ко- тельниковских выборок. Для реализации в устройстве выбран следующий алгоритм определения показателя надежности:

15

7(пТ, Рс/Рш) 0(А 0)- - (Рс/Рш)пор Dl( ),(5)

где01( A 0) Ai2()+Bi2(A 0);

20 ,N-1 IT+TO

Ai() 2 /

I 0 IT y(t)yr(t-T0)-yr(t) -y(t-To)

25N - 1 I T + To

Bi(A o)2 /

I 0

IT

y(t)-y(t-To)+yr(t) -yr(t-To) dt.

Выражения Ai(0) и Вi(0)отличаются от выражений для А(0) и В(0) тем, что интервалы интегрирования при определении Ai(0) и Bi(0) заданы в виде IT, IT + Т0, а при определении А(0) и В(0) - в виде IT + Т0, (1+1) Т.

Выбор величины (Рс/Рш)пор должен

обеспечивать отключение текущей оценки

при такой вероятности ошибок в системе

обработки, при которой качественный прием

информации невозможен (речь идет о системе обработки, в которой используется устройство автоматической подстройки частоты с рассматриваемым дискриминатором). Таким образом, алгоритм формирования оценки сдвига, реализуемый в предлагаемом устройстве, определяется: формулой для вычисления текущей оценки М: текут ( пТ ) аналогично известному устройству; формулой (1) для вычисления выходной оценки; формулой (5) для вычисления показателя надежности ), причем D( А 0) А2( А 0) + В2( А 0), где А(), В( А 0)- соответствен но числитель и знаменатель в формуле (2).

При цифровой обработке в формуле (5)

N-1 к i+К Ai(°) 2 E (yiyi-/f --yi.r -yi-A );

I +1

(6)

N-1 К l+i

B1(0)22 (yiVI-JL+yi.r У1-/..Г )

I o I KI + 1

где К , о: - число отсчетов, приходящихся соответственно на длительность Т и Т0.

Частотный дискриминатор работает следующим образом.

Многочастотный сигнал y(t) модема- в смеси с шумами непосредственно с входа устройства и сигнал y(t - T0), задержанный на величину Т0 (где Т0 - интервал ортогональности) в первой линии 32, поступают на входы четвертого перемножителя 45, формирующего на выходе сигнал произведения y(t) y(t-To). Выходной сигнал преобразователя 38 yr(t) и сигнал yr(t - T0), задержанный на величину Т0 во второй линии 39, поступают на входы второго перемножителя 40, формирующего на выходе сигнал произведения yr(t) yr(t - То). Аналогично третий перемножитель 44 формирует сигнал произведения y(t) yr(t - То), а первый перемножи- тель 33 формирует сигнал произведения Vr(t) y(t-T0). Второй сумматор 41 формирует сумму выходных сигналов перемножителей 40 и 45 y(t) y(t - То) + yKt) yr(t - To), (фиг. 26), причем предполагается, что на интервале посылки (1+1) нет помех, а на интервале посылки (I+2) помеха есть, а первый сумматор 35 и инвертор 34 формирует разность выходных сигналов перемножителей 33 и 44: y(t) yr(t-T0) - yr(t) y(t-T0).

В момент времени IT + Т (где 1+1 -номер анализируемой посылки) по команде управления (фиг. 2в) размыкается первый ключ 46 и первый интегратор 36 начинает интегрирование выходного напряжения сумматора 35 (фиг. 2д, пунктир). В момент времени (1+1)Т окончания (1+1}-й посылки (где Т - длительность посылки) по второй команде управления (фиг. 2г) замыкается первый ключ 37 и выходной сигнал интегратора 36 поступает на первый выход блока 1. Затем команды управления замыкают ключ 46 и размыкают ключ 37, при этом интегратор 36 обнуляется. Точно так же второй интегратор 42, управляемый вторым ключом 47 сброса, производит также в течение защитного интервала Т3.п. интегрирование выходного сигнала сумматора 41, при этом при помощ-и второго ключа 43 передачи выходное напряжение интегратора 42 поступает на второй выход блока 1.

К моменту окончания (1+1)-й посылки на первом и втором выходах блока i сформированы напряжения, соответствующие суммируемым выражениям в формуле (2). Обе команды управления (поступающая на ключи 46 и 47 и поступающая на ключи 43 и 37) формируются блоком 3 из входного сигнала, причем каждая из них точно привязана к- границе такта (т.е. формируемая статистика 5 соответствует Я 0).

В том случае, когда требуется выполнить усреднение результатов измерения по N посылкам, гТереключатель 52 в блоке 4 устанавливается в положение, при котором

0 первый и второй выходы блока 4 образуют выходы первого 49 и второго 51 сумматоров, N входов каждого из которых соединены с N отводами первой 48 и второй 51 многоотводных линий, соответственно, осуществля5 ющ их задержку входных сигналов на время N Т. При этом на первый и второй выходы блока 4 поступают усредненные noN посылкам напряжения, соответствующие величинам А(А 0), В( Д 0), в формуле (2). В случае

0 необходимости обеспечения максимального быстродействия переключатель 52 устанавливается в положение, при котором на выход блока 4 поступают сигналы непосредственно с выходов блока 1. Очевидно, что в

5 этом случае усреднение по посылкам отсутствует и время измерения ограничивается длительностью одной посылки, этот случай соответствует выбору N 1 в формуле (2). В отличие от интеграторов 36 и 42 пер0 вый 16 и второй 18 дополнительные интеграторы, управляемые первым 12 и вторым 13 дополнительными ключами, на которые поступает от блока 3 инвертируемая в дополнительном инверторе 11 первая коман5 да управления (фиг, 2ж), производят интегрирование выходных сигналов сумматоров 35 и 41, начиная с момента начала (1+1)-й посылки IT до момента IT + T0 (фиг. 2 и, пунктир). В момент времени (IT + Т0),

0 предшествующий замыканию ключей 12 и 13 (т.е. обнулению интеграторов 16 и 18), на управляющие входы дополнительных первого 17 и второго 19 ключей передачи посту- пают импульсы второй команды

5 управления от блока 3, задержанные на величину Т относительно граничного момента, IT в первой дополнительной линии 20 (фиг. 2з). Таким образом, перед началом работы интеграторов 36 и 42 в момент (IT + T0) на

0 выходах ключей 17 и 19 сформированы напряжения, пропорциональные суммируемым величинам формулы (5).

Блок 21 аналогично блоку 4 осуществляет усреднение выходных сигналов ключей

5 17 и 19 по N посылкам. Переключатель 52 в составе блока 21 переключается в соответствии с установкой и одновременно с аналогичным переключателем в составе блока 4.

Первый и третий квадраторы 22 и 30 и сумматор 23 формируют напряжение (фиг. 2, и), пропорциональное выражению Di(A 0) из (5), т.е. сумму квадратов сигналов ключей 17 и 19, усредненных по N посылкам в блоке 21. Второй 26 и четвертый 31 квадраторы и сумматор 27 формируют напряжение, пропорциональное выражению D(A 0) из формулы (5), т.е. сумму квадратов сигналов ключей 37 и 43, усредненных по N посылкам в блоке 4.

Таким образом, если на выходе сумматора 23 сформирован сигнал, пропорциональный статистике, полученной при обработке сигнала на интервале Т0, то на выходе сумматора 27 получен сигнал, соответствующий величине статистики, полученной при обработке сигнала на интервале ТЭн (1+1 )-й посылки.

Линия задержки 24 задерживает выходной сигнал сумматора 23 на время Т3 п (фиг, 2к), т.е. до момента появления выходного сигнала сумматора 27. В дополнительном перемножителе 28 напряжение статистики, полученной на защитном интервале, перемножается с величиной порогового напряжения, снимаемого с шины 29 (фиг. 2е). Величина порогового напряжения пропорциональна длительности интервала ортогональности, величине Рс/Рш)пор в формуле (5) и обратно пропорциональна длительности защитного интервала. Таким образом, указанный сомножитель является весовым коэффициентом, позволяющим выполнить сравнение статистик, взятых с разным весом, образованных при обработке сигнала на разных по продолжительности временных интервалах.

Компаратор 25 выполняет сравнение напряжений указанных статистик, одновременно поступающих на его входы (фиг. 2л). Если взвешенное напряжение статистики, полученной на защитном интервале, превышает значение напряжения статистики, полученной на интервале ортогональности (выходное напряжение линии 24), этот случай соответствует обработке на данной посылке сигнала модема с уровнем, превышающим уровень помех, выходное напряжение компаратора 25 замыкает ключи 5, 6 и 15 и частотный дискриминатор работает обычным образом, за исключением того, что в блоке 7 памяти ключи сброса замыкаются для обнуления не в момент времени IT + То до конца такта (1+1) Т, как в известном устройстве, а на короткое время непосредственно перед записью очередного результата в момент(1+1)Токончания анализируемой посылки. Сигнал управления ключами сброса блока 7 (фиг, 2о) формируется в элементе И 14 путем конъюнкции сигнала с второго выхода блока 3 (фиг. 2в), импульс переписи и сигнала с третьего выхода блока 3 (фиг. 2м), импульс сброса длительностью от IT + Т0 до (1+1) Т. Блок 7 осуществляет запоминание выходных напряжений блока 4 в двух ячейках памяти и обеспечивает их хранение в течение времени Т, а затем вновь освобождается импульсом сброса непосредственно перед записью очередного результата (фиг. 2н).

Блок 8, вычисляющий отношение напряжений, поступающих на его входы с выходов блока 7 с учетом их знаков (определяющих

направление смещения частоты), управляется сигналом с четвертого выхода блока 3 (фиг. 2р) и работает в течение времени хранения информации в блоке 7. Функциональный преобразователь 9, работающий по

алгоритму Q; (1/T0)arctg X, блоки 3, 7 и 8 работают аналогично блокам известного устройства. Таким образом, в указанной ситуации после очередного интервала Т на выходной шине 10 устройства формируется

напряжение, величина которого пропорциональна величине канального смещения частоты, знак которого отражает направление смещения частоты (фиг. 2п).

Если взвешенное напряжение статистики, полученной на защитном интервале (выходное напряжение перемножителя 28), оказывается меньше, чем напряжение, соответствующее статистике, полученной на интервале ортогональности - этот случай

соответствует обработке на данной посылке сигнала модема, уровень которого меньше уровня помех-выходной сигнал компаратора 25 удерживает ключи 5, 6 и 15 в разомкнутом состоянии, сигналы с выходов блока 4 на входы блока 7 памяти не поступают, также блокируется прохожде.жз сигнала управления ключами сброса а.ска 7, и в результате он сохраняет напряжение, накопленные при обработке сигнала предыдущей посылки, т.е.

при плохом соотношении сигнал/помеха блоки 8 и 9 повторно обрабатывают зaфикcи- рованные выходные сигналы блока 7 и на выходной шине 10 устройства вновь повторяется результат измерения, полученный на

предыдущей посылке.

Таким образом, за счет экстраполяции надежных результатов измерения частотного сдвига на интервалы времени, когда в канале действует помеха сильного уровня,

точность его работы в условиях помех существенно повышается.

Формула изобретения Частотный дискриминатор по авт. св. № 1359899, отличающийся тем, что, с

целью повышения точности измерения сдвига частоты в условиях действия помех, в устройство введены дополнительный блок усреднения по посылкам, первый, второй и третий ключи, элемент И, первый и второй дополнительные интеграторы, первый и второй дополнительные ключи сброса, первый и второй дополнительные ключи передачи, дополнительный инвертор, первая и вторая дополнительные линии задержки, первый и второй дополнительные сумматоры, первый, второй, третий и четвертый квадраторы, дополнительный перемножитель, шина порогового напряжения, компаратор, причем выход первого сумматора, являющийся первым дополнительным выходом блока входной обработки, подключен через первый дополнительный интегратор к входу первого дополнительного ключа передачи, выход второго сумматора, являющий- ся вторым дополнительным выходом блока входной обработки, подключен через дополнительный второй интегратор к входу второго дополнительного ключа передачи, первые и вторые входы управления первого и второго дополнительного интеграторов соединены соответственно с первыми и вторыми выходами соответственно первого и второго дополнительных ключей сброса. входы управления которых объединены и через дополнительный инвертор подключены к первому выходу блока управления, входы управления первого и второго дополнительных ключей передачи объединены и через первую дополнительную ли- нию задержки подключены к второму выходу блока управления, а выходы дополнительных первого и второго ключей передачи подключены соответственно к первому и второму входам дополнительного блока усреднения по посылкам, первый и второй выходы которогоо соединены соответственно с входами первого и третьего квадраторов, выход первого квадратора соединен с первым входом первого дополнительного сумматора, а выход третьего квадратора - с вторым входом первого дополнительного сумматора, выход которого через вторую дополнительную линию задержки подключен к первому входу компаратора, первый выход блока усреднения го посылкам подключен к входу второго квадратора и через первый ключ к первому входу блока памяти, второй вход которого через второй ключ подключен к второму выходу блока усреднения по посылкам, который также соединен с входом четвертого квадратора, выход которого соединен с первым входом второго дополнительного сумматора, причем выход второго квадратора полключей к второму входу второго дополнительного сумматора, выход которого соединен с первым входом дополнительного перемножителя, второй вход которого соединен с шиной порогового напряжения, а выход - с вторым входом компаратора, выход которого соединен с объединенными управляющими входами первого, второго и третьего ключей, при этом выход третьего ключа соединен с управляющим входом блока памяти, а его вход - с выходом элемента И, первый и второй входы которого соединены соответственно, с вторым и третьим выходами блока управления.

1Г ()посылка/7V7J ftf2)

| название | год | авторы | номер документа |

|---|---|---|---|

| Частотный дискриминатор | 1986 |

|

SU1359899A1 |

| Анализатор сигнала тактовой синхронизации | 1988 |

|

SU1587656A1 |

| Анализатор сигнала тактовой синхронизации | 1990 |

|

SU1781834A2 |

| Когерентный демодулятор сигналов с фазоразностной модуляцией | 1980 |

|

SU906023A1 |

| Адаптивный корректор многоканального сигнала с ортогональными составляющими | 1990 |

|

SU1807571A1 |

| АВТОКОРРЕЛЯЦИОННОЕ УСТРОЙСТВО ВСКРЫТИЯ СПЕКТРАЛЬНО-ВРЕМЕННОЙ СТРУКТУРЫ СИГНАЛОВ ЦИФРОВЫХ СИСТЕМ СВЯЗИ | 2008 |

|

RU2365051C1 |

| Устройство контроля каналов связи | 1988 |

|

SU1578820A1 |

| Устройство для приема дискретных сигналов | 1986 |

|

SU1415453A1 |

| Демодулятор дискретных сигналов с фазоразностной модуляцией | 1982 |

|

SU1107325A1 |

| Демодулятор фазоманипулированных сигналов с компенсацией помех | 1987 |

|

SU1545332A1 |

Изобретение относится к импульсной технике и может быть использовано в многоканальных модемах передачи дискретной информации с ортогональными сигналами для автоматической подстройки частоты. Цель изобретения - повышение точности измерения сдвига частоты в условиях действия помех. Для достижения цели в устройство, содержащее блок 1 входной обработки, блок 3 управления, блок 4 усреднения по посылкам, блок 7 памяти, блок 8 сравнения функциональный преобразователь 9, введены ключи 5, 6, 15, инвертор 11, дополнительные ключи 12, 13 сброса, элемент И 14, дополнительные интеграторы 16, 18, дополнительные ключи 17, 19 передачи, дополнительные линии 20, 24 задержки, дополнительный блок 21 усреднения по посылкам, квадраторы 22, 26, 30, 31, дополнительные сумматоры 23, 27, компаратор 25, перемножитель 28, шина 29 поро

| Частотный дискриминатор | 1986 |

|

SU1359899A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-09-07—Публикация

1988-12-29—Подача