4ib

ЩшА

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный корректор межсимвольных искажений сигнала | 1983 |

|

SU1238247A1 |

| Корректор межсимвольных искажений | 1985 |

|

SU1241489A1 |

| Нелинейно-нелинейное устройство коррекции межсимвольной интерференции при приеме коррелированного сигнала | 1983 |

|

SU1125750A1 |

| ПРИЕМНИК ЦИФРОВЫХ СИГНАЛОВ | 2010 |

|

RU2423794C1 |

| Устройство коррекции межсимвольной интерференции при приеме коррелированного сигнала | 1983 |

|

SU1125749A1 |

| УСТРОЙСТВО ДЛЯ ДЕМОДУЛЯЦИИ ДВОИЧНЫХ СИГНАЛОВ | 1994 |

|

RU2085047C1 |

| Нелинейно-нелинейный корректор коррелированного сигнала | 1984 |

|

SU1225017A1 |

| Адаптивный корректор межсимвольной интерференции | 1987 |

|

SU1540009A1 |

| Линейное устройство коррекции межсимвольной интерференции | 1984 |

|

SU1210225A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1996 |

|

RU2099739C1 |

Изобретение относится к электро- связи Цель изобретения - повышение точности корректора. Корректор содержит сумматоры 1 и 10, блоки принятия решения (БПР) 2 и 12, многоотводную линию 6 задержки, регуляторы 8 и 9 затухания, блок согласования 11 задержки, блок регулировки (БР) 16интервала анализа, блок оценки 17величины ошибки, блок переключения 18 регулировки, БР 19 порога решения и. БПР 20 на регулировку, .Цель достигается за счет осуществления пе рестройки величин порогов решения с помощью введенных БР 16 и 19 блока оценки 17, блока переключения 18 и БПР 20. 6 ил.

со

оо

Изобретение относится к электро-- связи и может быть использовано в системах связи со сложными импульс - ными помехами, величина которых зави сит от сигнала и соизмерима с величиной межсимвольных искажений, в све- товодных системах связи,

Целью изобретения является повы юение точности корректора.

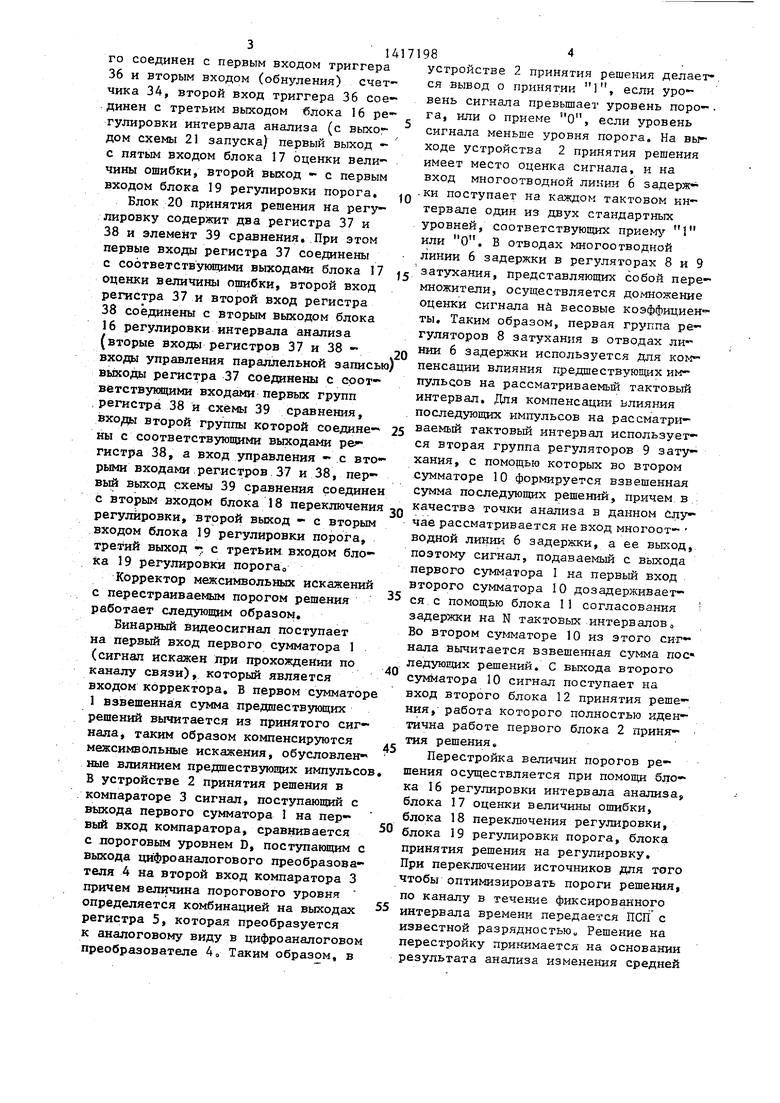

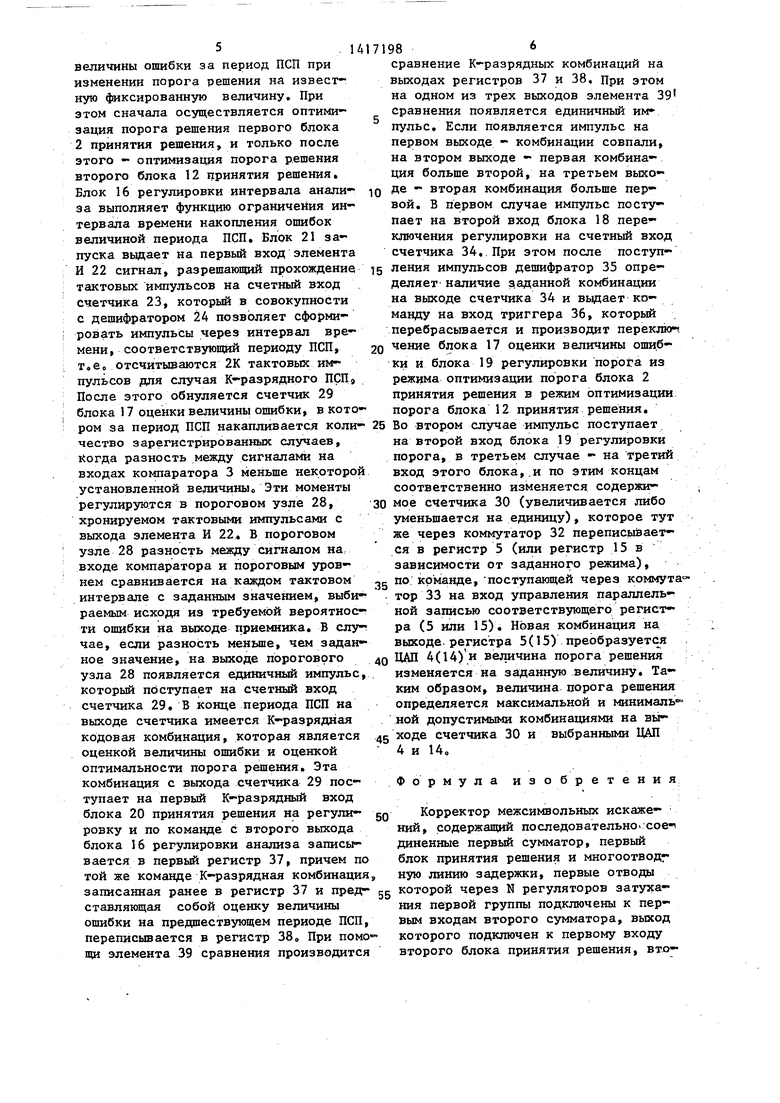

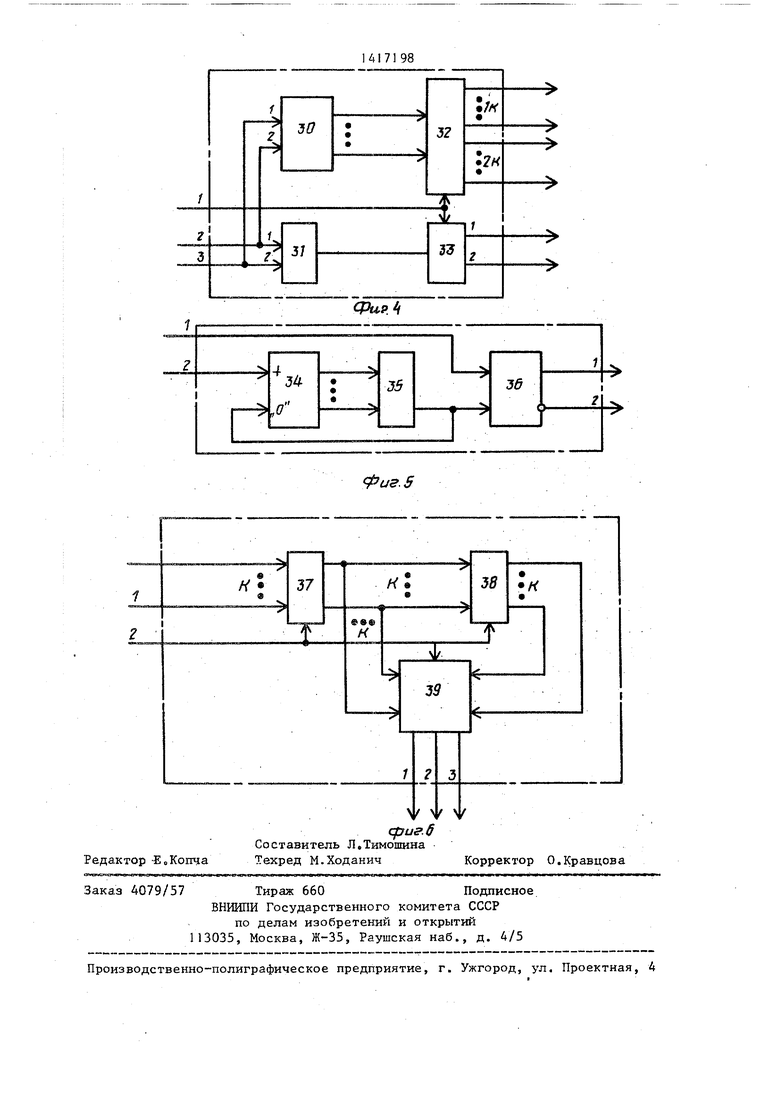

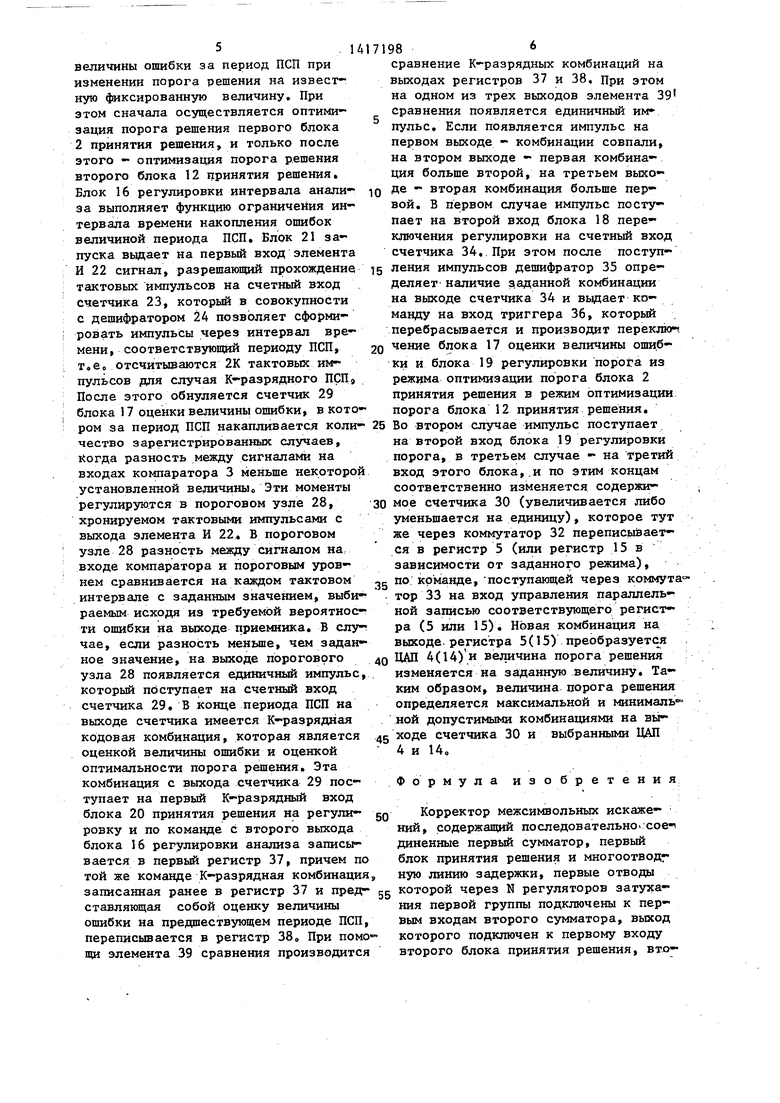

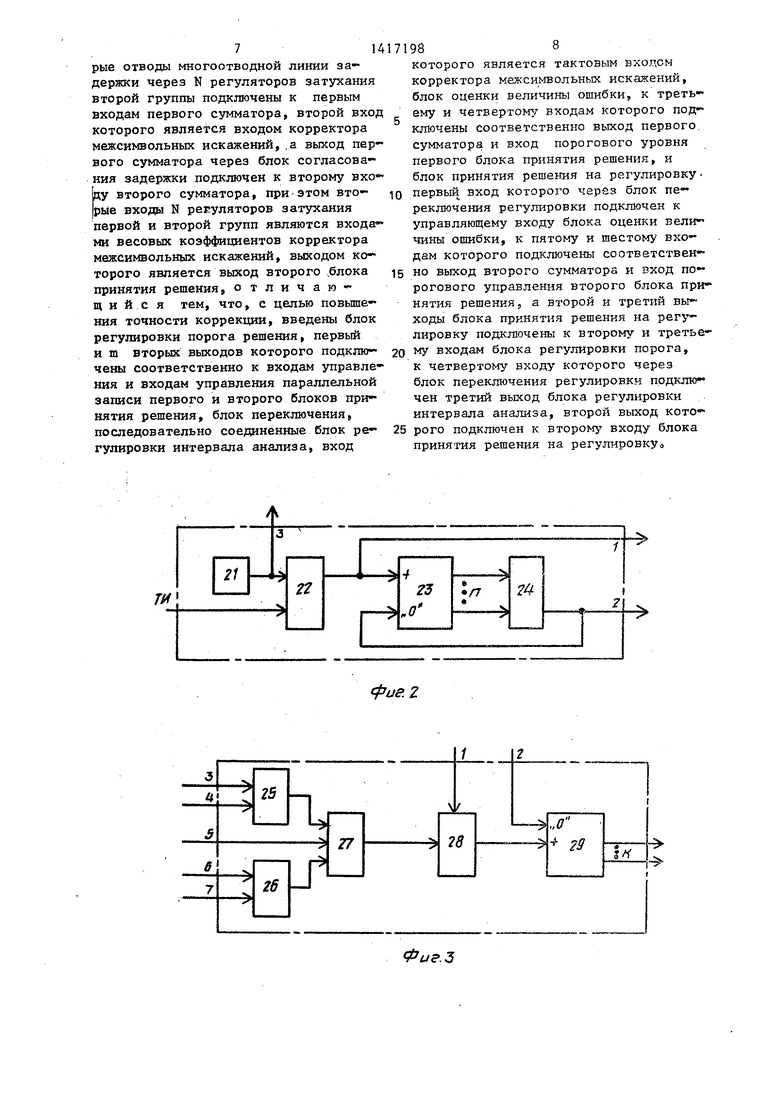

На фиГо представлена структурная схема предлагаемого корректора межсимвольных искажений (для простоты показан корректор МСИ, содержащий линию задержки из грех элементов)J на фига 2 - блок регулировки интервала анализа, на фиГоЗ - блок оценки величины ошибки; на фиг.4 - блок регулировки порога решения; на фиго5 - блок переключения регулировки; на фиГоб - блок принятия решения на регулировку.

Корректор межсимвольных искажений содержит первый сумматор 1, первый блок 2 принятия решения, содержащий компаратор 3, цифроаналоговый преобразователь ЦАП 4, регистр 5, многоотводную линию 6 задержки, составленную из N элементов 7 задержкиj N регуляторов 8 затухания первой группы, N регуляторов 9 затухания второй группы, второй сумматор 10, блок 11 согласования задержки, второ блок 12 принятия решения, содержащий компаратор 13, ЦАП 14, регистр 15, блок 16 регулировки интервала анализа, блок 1.7 оценки величины ошибки, блок 18 переключения регулировки, блок 19 регулировки порога решения, блок 20 принятия решения на регули ровку«

Блок 16 регулировки интервала анализа содержит блок 21 запуска, элемент И 22, счетчик 23 и дешифратор 24, причем на первый вход схемы 22 И поступает сигнал со схемы 21 запуска, на второй вход тактовые ИЬР- пульсы, а выход соединен со счетным входом счетчика 23 и первым входом блока 17 оценки величины ошибки. Выходы счетчика 23 соединены с соответствующими входами дешифратора 24, выход которого соединен с входом об« нуления счетчика 23 и вторым входом блока 20 принятия решения на регулировку.

Блок 17 оценки величины ошибки содержит первьй 25 и второй 26 вьг читающие узлы, коммутатор 27, поро говьй узел 28, счетчик 29. При этом первый и второй входы первого вьиита- ющего устройства 25 соединены соот. ветственно с входами компаратора 3, а выход - с первым входом коммутатора 27, первый и второй входы второго вычитающего устройства 26 соединены соответственно с входами компарй.то

O pa 13, а выход - с вторым входом коммутатора 27, третий вход которого (управления) соединен с первым выходом блока 18 переключения регулировки, а выход - с первым входом порого5 вого устройства 28, второй вход которого соединен с первым выходом блока 16 регулировки интервала анализа, а выход - со счетным входом счетчика 29, вход обнуления которого сое-

0 динен с вторым выходом блока 16 регулировки интервала анализа, К выходов счетчика .(например четырехразрядная шина) соединены с соответствующими первыми входами блока 20 при5 нятия решения на регулировкуо

Блок 19 регулировки порога содержит реверсивный счетчик 30, элемент ИЛИ 31, многоразрядный коммутатор 32 и коммутатор 33. При этом первый

0 вход (+) счетчика 30 и первый вход схемы ИЛИ 31 соединены с вторым входом блока 20 принятия решения на регулировку, второй вход (-) счетчика 30 и второй вход схемы ИЛИ 31 соеди-

г нены с третьим выходом блока 20 принятия решения на регулировку, .выходы счетчика 30-соединены с соответствующими входами многоразрядного коммутатора 32, управляющий вход коQ торого соединен с управляющим входом коммутатора 33 и вторым выходом блока 18 переключения регулировки, первая группа выходов многоразрядного коммутатора 32 соединена с соответ(- ствующими входами регистра 5, вторая группа выходов - с соответствующими входами регистра 15, первый выход коммутатора 33 соединен с первым входом (управления) регистра 5, второй выход - с первым входом (управления) регистра 15, а вход - с выходом схемы ИЛИ 31,

Блок 18 переключения регулировки содержит счетчик 34, дешифратор 35 . и триггер 36. При этом счетный вход счетчика 34 соединен с первым выходом блока 20 принятия решения на регулировку, а выходы - с соответствующими входами дешифратора 35, выход которо0

го соединен с первым входом триггера 36 и вторым входом (обнуления) счетчика 34, второй вход триггера 36 сое динен с третьим выходом 5лока 16 регулировки интервала анализа (с выхог дом схемы 21 запуска) первый выход - с пятым входом блока 17 оценки величины ошибки, второй выход - с первым входом блока 19 регулировки порога.

Блок 20 принятия решения на регулировку содержит два регистра 37 и 38 и элемент 39 сравнения. При этом первые входы регистра 37 соединены с собтветствунмцими выходами блока 17 оценки величины ошибки, второй вход регистра 37 и второй вход регистра 38 соединены с вторым выходом блока 16 регулировки интервала анализа (вторые входы регистров 37 и 38 - входы управления параллельной записью) вькоды регистра 37 соединены с срот- ветствуняцими входами первых групп регистра 38 и схемы 39 сравнения,

принятия решения делаетI111I

10

}5

20

устройстве 2

ся вывод о принятии 1, если уровень сигнала превышает уровень поро- га, или о приеме О, если уровень сигнала меньше уровня порога. На выходе устройства 2 принятия решения имеет место оценка сигнала, и на вход многоотводной линии 6 задержи .ки поступает на каждом тактовом интервале один из двух стандартных уровней, соответствующих приему 1 или О, В отводах многоотводной линии 6 задержки в регуляторах 8 и 9 затухания, представляющих собой перемножители, осуществляется домножение оценки сигнала на весовые коэффициенты. Таким образом, первая группа регуляторов 8 затухания в отводах линии 6 задержки используется Для компенсации влияния предшествующих нм пульсов на рассматриваемьй тактовый интервал. Для компенсации влияния последующих импульсов на расематри-

ВХО|ДЬ1 второй группы которой соедине-- 25 аемый тактовый интервал использует- ны с соответствующими выходами ре гистра 38, а вход управления с вторыми входами регистров 37 и 38, первый выход схемы 39 сравнения соединен

ся вторая группа регуляторов 9 затухания, с помощью которых во втором сумматоре 10 формируется взвешенная сумма последующих решений, причем в ;

С вторым входом блока 18 переключения JQ качества точки анализа в данном Слу-

регулировки, второй выход - с вторым входом блока 19 регулировки порога, третий выход ;. с третьим входом блока 19 регулировки nopora

Корректор межсимвольных искажений с перестраиваемым порогом решения работает следующим образом.

Бинарный видеосигнал поступает на первый вход первого сумматора 1 (сигнал искажен при прохождении по каналу связи), который является входом корректора, В первом сумматоре 1 взвешенная сумма предшествзтещих решений вычитается из принятого сигнала, таким образом компенсируются межсимвольные искажения, обусловлен ные влиянием предшествующих импульсов, В устройстве 2 принятия решения в компараторе 3 сигнал, поступающий с выхода первого сумматора 1 на первый вкод компаратора, сравнивается с пороговым уровнем D, поступающим с выхода цифроаналогового преобразователя 4 на второй вход компаратора 3 причем величина порогового уровня определяется комбинацией на выходах регистра 5, которая преобразуется к аналоговому виду в цифроаналоговом преобразователе 4, Таким образом, в

35

40

чае рассматривается не вкод многоотводной линии 6 задержки, а ее выход, поэтому сигнал, подаваемый с выхода первого сумматора I на первый вход второго сумматора 10 дозадерживает- ся с помощью блока 11 согласования задержки на N тактовых интернапов, Во втором суг-шаторе 10 из этого сиг нала вычитается взвешенная сумма пос« ледующих решений. С выхода второго сумматора 10 сигнал поступает на вход второго блока 12 принятия реше- ния,- работа которого полностью идентична работе первого блока 2 приня- тия решения.

Перестройка величин порогов решения осуществляется при помоащ бло ка 16 регулировки интервала анализа, блока 17 оценки величины ошибки, блока 18 переключения регулировки, 50 блока 19 регулировки порога, блока принятия решения на регулировку. При переключении источников для того чтобы оптимизировать пороги решения, по каналу в течение фиксированного интервала времени передается ДСП с известной разрядностью„ Решение на перестройку принимается на основании результата анализа изменения средней

45

55

принятия решения делает. I111I

устройстве 2

ся вывод о принятии 1, если уровень сигнала превышает уровень поро- . га, или о приеме О, если уровень сигнала меньше уровня порога. На выходе устройства 2 принятия решения имеет место оценка сигнала, и на вход многоотводной линии 6 задержи .ки поступает на каждом тактовом интервале один из двух стандартных уровней, соответствующих приему 1 или О, В отводах многоотводной линии 6 задержки в регуляторах 8 и 9 затухания, представляющих собой перемножители, осуществляется домножение оценки сигнала на весовые коэффициенты. Таким образом, первая группа регуляторов 8 затухания в отводах линии 6 задержки используется Для компенсации влияния предшествующих нм пульсов на рассматриваемьй тактовый интервал. Для компенсации влияния последующих импульсов на расематри-

аемый тактовый интервал использует-

ся вторая группа регуляторов 9 затухания, с помощью которых во втором сумматоре 10 формируется взвешенная сумма последующих решений, причем в ;

качества точки анализа в данном Слу-

чае рассматривается не вкод многоотводной линии 6 задержки, а ее выход, поэтому сигнал, подаваемый с выхода первого сумматора I на первый вход второго сумматора 10 дозадерживает- ся с помощью блока 11 согласования задержки на N тактовых интернапов, Во втором суг-шаторе 10 из этого сиг нала вычитается взвешенная сумма пос« ледующих решений. С выхода второго сумматора 10 сигнал поступает на вход второго блока 12 принятия реше- ния,- работа которого полностью идентична работе первого блока 2 приня- тия решения.

Перестройка величин порогов решения осуществляется при помоащ бло ка 16 регулировки интервала анализа, блока 17 оценки величины ошибки, блока 18 переключения регулировки, блока 19 регулировки порога, блока принятия решения на регулировку. При переключении источников для того чтобы оптимизировать пороги решения, по каналу в течение фиксированного интервала времени передается ДСП с известной разрядностью„ Решение на перестройку принимается на основании результата анализа изменения средней

величины ошибки за период ПСП при изменении порога решения на извест ную фиксированную величину. При этом сначала осуществляется оптимизация порога решения первого блока 2 принятия решения, и только после этого - оптимизация порога р.ешения второго блока 12 принятия решения. Блок 16 регулировки интервала анализа выполняет функцию ограничения интервала времени накопления ошибок величиной периода ПСП, Блок 21 запуска выдает на первый вход элемента И 22 сигнал, разрешающий прохождение тактовых импульсов на счетный вход счетчика 23, который в совокупности с дешифратором 24 позволяет сформировать импульсы через интервал времени, соответствующий периоду ПСП, т.е отсчитываются 2К тактовых импульсов для случая К-разрядного ПСЦ После этого обнуляется счетчик 29

20 чение блока 17 оценки величины опшб- ки и блока 19 регулировки порога из режима оптимизации порога блока 2 принятия решения в режим оптимизации порога блока 12 принятия решения.

блока 17 оценки величины ошибки, в котором за период ПСП накапливается коли- 25 Во втором случае импульс поступает честно зарегистрированных случаев, на второй вход блока 19 регулировки 1(огда разность между сигналами на входах компаратора 3 меньше некоторой установленной ведичиныо Эти моменты регулируются в пороговом узле 28, хронируемом тактовыми импульсами с выхода элемента И 22, В пороговом узле 28 разность между сигналом на входе компаратора и пороговым уровнем сравнивается на каждом тактовом

порога, в третьем случае - на третий вход этого блока,,и по этим концам соответственно изменяется содержи30 мое счетчика 30 (увеличивается либо уменьшается на единицу), которое ту же через коммутатор 32 переписывается в регистр 5 (или регистр 15 в зависимости от заданного режима),

.jg по команде, поступающей через комму тор 33 на вход управления параллельной записью соотзетствующего регистра (5 или 15), Новая комбинация на выходе регистра 5(15) преобразуется

интервале с заданным значением, выбираемым исходя из требуемой вероятности ошибки на выходе приемника, В случае, если разность меньше, чем заданное значение, на выходе порогового узла 28 появляется единичный импульс, который поступает на счетный вход счетчика 29, В конце периода ПСП на выходе счетчика имеется К-разрядная

50

кодовая комбинация, которая является x.ofs.e счетчика 30 и выбранными ЦАП оценкой величины ошибки и оценкой 4и14о оптимальности порога решения. Эта комбинация с выхода счетчика 29 поступает на первый К-разрядный вход блока 20 принятия решения на регулировку и по команде с второго выхода блока 16 регулировки анализа записывается в первый регистр 37, причем по той же команде К-разрядная комбинация,, записанная ранее в регистр 37 и пред- gg которой через N регуляторов затуха- ставляющая собой оценку величины ния первой группы подключены к пер- ошибки на предшествующем периоде ПСП, переписывается в регистр 38о При помощи элемента 39 сравнения производится

Формула изобретения

Корректор межсимвольных искажений, содержащий последовательно, соединенные первый сумматор, первый блок принятия решения и многоотводную линию задержки, первые отводы

вым входам второго сумматора, выход которого подключен к первому входу второго блока принятия решения, вто-

171986

сравнение К-разрядных комбинаций на выходах регистров 37 и 38. При этом на одном из трех выходов элемента 39 сравнения появляется единичный им пульс. Если появляется импульс на первом выходе - комбинации совпали, на втором выходе - первая комбинация больше второй, на третьем выхо1Q де - вторая комбинация больше первой. В первом случае импульс поступает на второй вход блока 18 пере ключения регулировки на счетный вход счетчика 34, При этом после поступ15 пения импульсов дешифратор 35 определяет наличие з(аданной комбинации на выходе счетчика 34 и выдает команду на вход триггера 36, который перебрасьюается и производит nepexjno

20 чение блока 17 оценки величины опшб- ки и блока 19 регулировки порога из режима оптимизации порога блока 2 принятия решения в режим оптимизации порога блока 12 принятия решения.

25 Во втором случае импульс поступает на второй вход блока 19 регулировки

25 Во втором случае импульс поступает на второй вход блока 19 регулировки

порога, в третьем случае - на третий вход этого блока,,и по этим концам соответственно изменяется содержи30 мое счетчика 30 (увеличивается либо уменьшается на единицу), которое тут же через коммутатор 32 переписывается в регистр 5 (или регистр 15 в зависимости от заданного режима),

.jg по команде, поступающей через коммут тор 33 на вход управления параллельной записью соотзетствующего регистра (5 или 15), Новая комбинация на выходе регистра 5(15) преобразуется

40 ЦАП 4(14) и величина порога решения изменяется на заданную величину. Таким образом, величина порога решения определяется максимальной и минималь ной допустимыми комбинациями на вы50

x.ofs.e счетчика 30 и выбранными ЦАП 4и14о ,, gg которой через N регуляторов затуха- ния первой группы подключены к пер-

Формула изобретения

Корректор межсимвольных искажений, содержащий последовательно, соеп диненные первый сумматор, первый блок принятия решения и многоотводную линию задержки, первые отводы

x.ofs.e счетчика 30 и выбранными ЦАП 4и14о которой через N регуляторов затуха- ния первой группы подключены к пер-

вым входам второго сумматора, выход которого подключен к первому входу второго блока принятия решения, вто-

714

рые отводы многоотводной линии задержки через N регуляторов затухания второй группы подключены к первым входам первого сумматора, второй вход которого является входом корректора межсимвольных искажений, ,а выход первого сумматора через блок согласования задержки подключен к второму вхо« 1ду второго сумматора, при-этом вто- рые входы N регуляторов затухания первой и второй групп являются входами весовых коэффициентов корректора межсимвольных искажений, выходом которого является выход второго .блока принятия решения, отличающийся тем, что, с целью повыше- ння точности коррекции, введены блок регулировки порога решения, первый и m вторых выходов которого подклю- чены соответственно к входам управления и входам управления параллельной записи первого и второго блоков принятия решения, блок переключения, последовательно соединенные блок ре- гулировки интервала анализа, вход

988

которого является тактовым входом корректора межсимвольных искажений, блок оценки величины ошибки, к третьему и четвертом ; входам которого подключены соответственно выход первого. сумматора и вход порогового уровня первого блока принятия решения, и блок принятия решения на регулировку первый вход которого через блок пе реключения регулировки подключен к управляющему входу блока оценки величины ошибки, к пятому и шестому входам которого подключены соответственно выход второго сумматора и вход по рогового управления второго блока принятия решения, а второй и третий ходы блока принятия решения на регулировку подключены к второму и третьему входам блока регулировки порога, к четвертому входу которого через блок переключения регулировки подклю чен третий выход блока регулировки интервала анализа, второй выход которого подключен к втором5 входу блока принятия решения на регулировку.

риа2

Фиг.З

Авторы

Даты

1988-08-15—Публикация

1987-01-04—Подача