Приемник цифровых сигналов - это устройство, которое относится к технике радиосвязи и может быть использовано для приема цифровых сигналов, использующих бинарную фазовую манипуляцию (BPSK - binary phase shift keying) в каналах с многолучевым распространением сигналов, вызывающим межсимвольную интерференцию.

При использовании бинарной фазовой манипуляции сигналы передаются на одной и той же несущей. В зависимости от передаваемых символов начальная фаза несущей может принимать два различных значения, различающихся на 180°, при этом сигналы несущей противоположны по знаку.

При прохождении трасс различного вида (тропосферных, ионосферных, трасс мобильной связи и др.) сигналы от передатчика к приемнику, зачастую, приходят сразу по нескольким путям, число которых может быть довольно значительным. При прохождении по каждому из путей сигналы испытывают задержку по времени, пропорциональную длине данного пути. Поскольку длины путей могут заметно различаться, то и величины задержки каждой копии сигнала, прошедшей по своему пути, также заметно различаются.

Если разброс подобной временной задержки больше длительности одного символа, то в каждый момент времени на приемник приходит сумма данного передаваемого символа и еще нескольких предыдущих символов. Количество символов в подобной суперпозиции равно соотношению временной длительности одного символа в данной системе передачи и максимальной разности по времени задержки между сигналами, пришедшими различными путями, это соотношение может достигать величины нескольких единиц.

Соотношения между уровнями сигналов, составляющих суммарный принимаемый сигнал, случайны по величине и случайно изменяются по времени. Случаен также и их взаимный фазовый сдвиг, поэтому в каждый момент времени весовые коэффициенты отдельных сигналов в суммарном сигнале после демодуляции могут быть различных знаков. Кроме того, поскольку передаваемая информация является последовательностью логических нулей и единиц, появление которых можно считать равновероятным, то и отклик демодулятора на каждый отдельный символ может равновероятно принимать как положительные, так и отрицательные значения.

Поэтому, когда в результате межсимвольной интерференции к принимаемому символу прибавляется суммарный отклик от нескольких предыдущих символов, демодулятор может принять ошибочное решение о действительной величине принимаемого символа, что приведет к появлению ошибки. Одновременное воздействие МСИ и теплового шума аппаратуры усиливает подобный негативный эффект. В результате при появлении МСИ значительно возрастает средняя величина вероятности ошибки и снижается помехоустойчивость и качество передачи информации.

Известны различные устройства, снижающие негативное влияние межсимвольной интерференции. При передаче применяются различные виды кодирования, описанные, например, в книге: Б.Скляр. «Цифровая связь. Теоретические основы и практическое применение». - М.: Издательский дом «Вильяме», 2003. Устройства содержат на передающей стороне кодеры, вводящие в цифровой поток дополнительные символы, определенным образом связанные с передаваемыми информационными символами.

На приемной стороне осуществляется детектирование с помощью корреляционной обработки и сравнения результата детектирования с пороговым напряжением. Корреляционная обработка производится в корреляторе, состоящем из перемножителя и интегратора. Перемножитель осуществляет перемножение входного сигнала на сигнал, вырабатываемый опорным генератором. Интегратор интегрирует результаты перемножения на временном интервале TC, равном длительности одного символа.

Сравнение результата с пороговым уровнем производится в пороговом блоке. Если входной сигнал порогового блока больше порогового уровня, то вырабатывается решение о приеме логической единицы, если меньше порогового уровня, то вырабатывается решение о приеме логического нуля. При использовании бинарной фазовой манипуляции пороговый уровень принимается равным нулю.

Принятая последовательность детектированных символов декодируется. При декодировании на основе принятой последовательности символов может быть восстановлена часть символов, неправильно декодированных из-за воздействия МСИ. Восстановление возможно за счет того, что определенные взаимосвязи между символами известны. Кодирование требует использования дополнительных символов, что уменьшает скорость передачи информационных символов. Из-за подобного уменьшения скорости передачи используется небольшое число дополнительных символов, поэтому и может быть восстановлена небольшая часть от общего числа символов. При воздействии же МСИ может быть повреждена достаточно большая доля символов. В этом случае использование кодирования неэффективно.

Известны также устройства, использующие МСИ в качестве варианта разнесенного приема, в частности, система RAKE, описанная, например, в книге: «Системы мобильной связи» авторов Ипатова В.П. и др. - М.: Горячая линия. - Телеком, 2003. - 272 с., раздел 6.2.2. Устройство содержит несколько корреляторов, состоящих из перемножителя и интегратора, также содержит генератор опорных сигналов и устройство комбинирования. Генератор опорных сигналов вырабатывает копии опорных сигналов с различными временными сдвигами. Количество опорных сигналов и величина временных сдвигов должны соответствовать наиболее сильным лучам, прошедшим по различным путям. При этом предполагается, что многолучевое распространение проявляется в виде небольшого числа достаточно сильных лучей. Кроме того, предполагается, что заранее известны относительные временные сдвиги этих лучей.

Таким образом, для работы рассматриваемого аналога необходимо предварительное использование специальных тестовых сигналов для определения временных параметров лучей. Если использование тестовых сигналов невозможно, то и применение аналога не дает желаемого эффекта. Кроме того, для его использования необходимо, чтобы многолучевость носила выраженный дискретный характер. В случае непрерывной многолучевости, когда принимаемый сигнал состоит из множества лучей с небольшим относительным временным сдвигом, применение устройства-аналога также не приводит к устранению многолучевости.

Наиболее близким по технической сущности к заявляемому является устройство, описанное в уже упомянутой книге «Системы мобильной связи», раздел 6.3.3. Устройство представляет собой линейный адаптивный эквалайзер. Для устранения воздействия многолучевости в нем производится выравнивание частотной характеристики канала распространения сигнала.

Устройство содержит блоки временной задержки, перемножители, сумматоры, детекторы и генератор обучающей последовательности. Блоки задержки, перемножители и сумматоры представляют собой управляемый трансверсальный фильтр. При работе устройства в некоторый начальный интервал времени на основе специальной обучающей последовательности производится настройка частотной характеристики фильтра. Далее при работе производится подстройка его характеристик.

Недостатки устройства заключаются в необходимости знания характеристик канала распространения для организации обучающей последовательности и для выбора величины временных задержек блоков временных задержек. Если же невозможно предварительно получить информацию о характеристиках канала распространения, то функционирование устройства-прототипа не обеспечивает требуемую помехоустойчивость передачи информации, так как не позволяет эффективно устранять воздействие межсимвольной интерференции.

Задачей предлагаемого изобретения является повышение помехоустойчивости и надежности передачи цифровой информации по каналам с многолучевым распространением сигналов.

Поставленная задача решается тем, что в устройство, содержащее детектор, состоящий из коррелятора и порогового блока, генератор опорных сигналов и первый сумматор, введены сдвиговый регистр, тактовый генератор, формирователь адреса, аналоговый коммутатор, вычислитель, 2M блоков усреднения, M блоков регулировки, второй сумматор, первый и второй усреднители, первый и второй вычитатели, квадратор, регулируемый усилитель, источник опорного напряжения и (М-1) блоков переключения, каждый из блоков переключения содержит инвертор и ключ, каждый из блоков регулировки содержит канальный квадратор и канальный регулируемый усилитель, при этом вход устройства и выход генератора опорных сигналов подключены ко входам коррелятора, а его выход через регулируемый усилитель - к сигнальному входу аналогового коммутатора и к первому входу порогового блока, выход которого соединен с выходом устройства и с сигнальным входом сдвигового регистра, выход тактового генератора соединен с тактовыми входами сдвигового регистра и аналогового коммутатора, первый выход сдвигового регистра подключен к одному из входов формирователя адреса, а другие М-1 выходов сдвигового регистра подключены к управляющим входам ключей всех блоков переключения и к другим М-1 входам формирователя адреса, а его выходы - к адресным входам аналогового коммутатора, каждый выход аналогового коммутатора через соответствующий блок усреднения подключен к одному из 2M входов вычислителя, каждый из M выходов вычислителя через соответствующий блок регулировки, содержащий последовательно соединенные канальный регулируемый усилитель и канальный квадратор, соединен с соответствующим входом второго сумматора, выход которого через второй усреднитель подключен к одному из входов второго вычитателя, выход второго вычитателя подключен к регулировочным входам канальных регулируемых усилителей всех блоков регулировки, вход квадратора соединен с выходом регулируемого усилителя, а выход через первый усреднитель - с одним из входов первого вычитателя, а его выход - с другим входом регулируемого усилителя, выход источника опорного напряжения подключен к другим входам первого и второго вычитателей, выходы канальных регулируемых усилителей блоков регулировки от второго номера до номера M соединены со входами соответствующих блоков переключения, выходы всех блоков переключения - со входами первого сумматора, а его выход - со вторым входом порогового блока, вход каждого блока регулировки подключен к одному из входов ключа и через инвертор - к другому входу ключа, а выход ключа подсоединен к выходу данного блока регулировки.

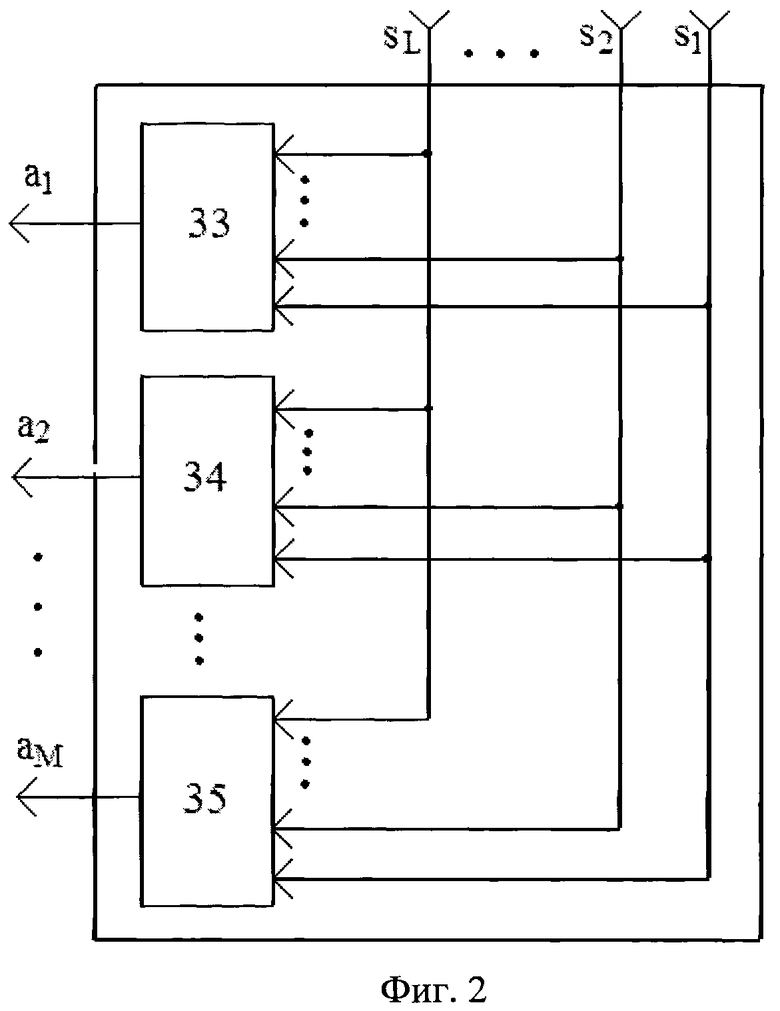

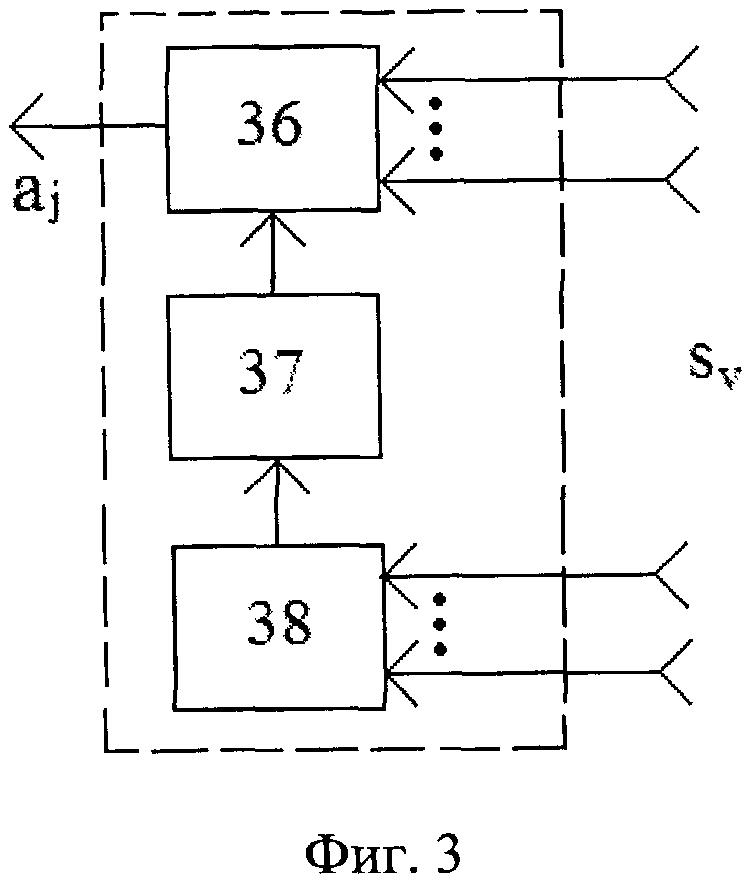

На чертежах представлены: на фиг.1 - структурная схема заявляемого приемника цифровых сигналов; на фиг.2 - пример реализации структурной схемы вычислителя; на фиг.3 - пример реализации структурной схемы сумматора прямых и инверсных сигналов.

На фиг.1 обозначены: генератор опорных сигналов 1, детектор 2, коррелятор 3, пороговый блок 4, тактовый генератор 5, сдвиговый регистр 6, формирователь адреса 7, аналоговый коммутатор 8, блоки усреднения 9, 10 и 11, первый 12 и второй 13 вычитатели, первый 14 и второй 15 усреднители, вычислитель 16, источник опорного напряжения 17, первый 18 и второй 19 сумматоры, блоки регулировки 20, 21 и 22, блоки переключения 23 и 24, регулируемый усилитель 25, канальные регулируемые усилители 26 и 27, квадратор 28, канальные квадраторы 29 и 30, инвертор 31 и ключ 32.

На фиг 2. обозначены: сумматоры прямых и инверсных сигналов 33, 34 и 35.

На фиг.3 обозначены: сумматоры 36 и 37 и инвертор 38.

Блоки устройства на фиг.1 работают следующим образом. Генератор опорного сигнала 1 вырабатывает опорный сигнал, согласованный с сигналом, переносящим один символ в данной системе передачи. В корреляторе 3 вырабатывается напряжение, пропорциональное величине корреляции между принимаемым сигналом и сигналом с генератора опорных сигналов. В пороговом блоке 4 оно сравнивается с текущим значением порога, поступающим с сумматора 20 на второй вход порогового блока 4. Если напряжение с выхода коррелятора больше значения порога, то пороговый блок 4 вырабатывает сигнал, обозначающий в устройстве логическую единицу. Если напряжение с выхода коррелятора меньше значения порога, то пороговый блок 4 вырабатывает сигнал, обозначающий в устройстве логический нуль.

Выходные сигналы порогового блока являются выходными сигналами устройства, а также они подаются на сигнальный последовательный вход сдвигового регистра 6. Логические сигналы, поступившие на последовательный вход сдвигового регистра 6, с приходом каждого нового символа через время TC (TC равно длительности одного символа) сдвигаются в соседние ячейки регистра. Последовательным сдвигом содержимого ячеек управляют сигналы тактового генератора 5.

Сигналы, поступающие с параллельных выходов сдвигового регистра 6, подаются на входы формирователя адреса 7. На основе этих сигналов в нем формируется адресный код, поступающий на адресный вход аналогового коммутатора 8 и определяющий, на какой из выходов аналогового коммутатора будет подключен сигнал с его сигнального входа. Работа аналогового коммутатора синхронизируется с помощью сигналов тактового генератора 5.

Выходные сигналы каждого выхода аналогового коммутатора 8 поступают на соответствующие блоки усреднения 9, 10, 11. Выходной сигнал каждого блока усреднения пропорционален его входному напряжению, усредненному за определенный промежуток времени. Параметры всех блоков усреднения одинаковы.

В вычислителе 16 осуществляется матричное преобразование совокупности его входных сигналов, состоящее в их весовом суммировании. На каждом выходе вычислителя напряжение равно сумме входных сигналов вычислителя, взятых с определенными взвешивающими коэффициентами. Наборы взвешивающих коэффициентов, формирующих выходные напряжения вычислителя, различны для каждого выходного сигнала. Вся совокупность взвешивающих коэффициентов постоянна при работе в данных условиях и известна заранее.

Напряжения с выходов вычислителя подаются на входы однотипных блоков регулировки 20, 21, 22 и в них - на входы однотипных канальных регулируемых усилителей 26, 27. Параметры канальных регулируемых усилителей всех блоков регулировки одинаковы. Выходные сигналы с выходов всех канальных регулируемых усилителей подаются на канальные квадраторы 29, 30. Напряжения на их выходах равны квадрату от входных напряжений. Все канальные квадраторы имеют одинаковые характеристики. Их выходные сигналы складываются во втором сумматоре 19 и усредняются по времени во втором усреднителе 15. Далее во втором вычитателе 13 находится разность между выходным сигналом второго усреднителя 15 и напряжением источника опорного напряжения 17, которое сохраняется постоянным на все время работы устройства. Выходной сигнал второго вычитателя 13 управляет величиной усиления канальных регулируемых усилителей всех блоков регулировки 20, 21, 22.

С помощью канальных регулируемых усилителей, канальных квадраторов, второго сумматора, второго усреднителя и второго вычитателя осуществляется совместная автоматическая регулировка уровней сигналов блоков регулировки таким образом, чтобы выходной сигнал второго усреднителя 15 оставался постоянным и равным выходному напряжению источника опорного напряжения 17.

Аналогичную процедуру осуществляют блоки 25, 28, 14, 12. В квадраторе 28 определяется квадрат от выходного напряжения регулируемого усилителя 25. Далее производится усреднение по времени в первом усреднителе 14. В первом вычитателе 12 определяется разность выходных напряжений первого усреднителя 14 и источника опорного напряжения 17. С помощью этого разностного сигнала управляется коэффициент усиления регулируемого усилителя 25 таким образом, чтобы уровень выходного напряжения первого усреднителя 14 оставался постоянным и равным выходному напряжению источника опорного напряжения 17.

Параметры регулируемого усилителя 25 и канальных регулируемых усилителей всех блоков регулировки 20, 21, 22 одинаковы, также одинаковы параметры квадратичного детектора 28 и квадратичных детекторов всех блоков регулировки 20, 21, 22. Кроме этого, первый 14 и второй 15 усреднители идентичны, первый 12 и второй 13 вычитатели также идентичны. В результате в процессе работы выходные сигналы первого 14 и второго 15 усреднителей поддерживаются одинаковыми.

Сигналы с выходов канальных регулируемых усилителей всех блоков регулировки кроме первого (соответствующего коэффициенту a1), т.е. всего М-1 сигналов, поступают на (М-1) блоков переключения 23, 24. В каждом блоке переключения ключ 32 подключает на выход блока переключения либо непосредственно входной сигнал данного блока, либо входной сигнал данного блока, прошедший инвертор 31. В инверторе знак входного сигнала изменяется на противоположный, а величина сигнала остается прежней.

Работа ключей всех блоков переключения управляется сигналами с выходов сдвигового регистра под номерами со второго по номер М. Нумерация выходов сдвигового регистра начинается с выхода первой ячейки, куда по последовательному входу поступает текущий символ. Сигнал первого выхода - это текущий символ, сигнал последнего выхода - это из предшествующих символов самый удаленный по времени символ от текущего символа. Если управляющий сигнал соответствует логической единице, то ключ подключает на выход соответствующего блока переключения сигнал непосредственно с его входа. Если управляющий сигнал соответствует логическому нулю, то ключ на выход блока переключения подключает выходной сигнал инвертора.

Далее выходные сигналы всех блоков переключения суммируются в первом сумматоре 18. Выходное напряжение первого сумматора 18 подается на второй вход порогового блока 4 и используется как текущее значение порогового уровня при выработке им решения о значении принимаемого символа.

Блоки вычислителя 16 на фиг.2 работают следующим образом. Входные сигналы вычислителя подаются на входы сумматоров прямых и инверсных сигналов 33, 34 и 35. Выходной сигнал каждого из этих сумматоров является разностью суммы сигналов, поступающих на прямые входы сумматора и суммы сигналов, поступающих на инверсные входы сумматора. Какие из входных сигналов поступают на прямые входы сумматоров, а какие - на инверсные входы сумматоров, определяется элементами матрицы, заложенной перед началом работы устройства и постоянной на все время работы.

Блоки сумматоров прямых и инверсных сигналов на фиг.3 работают следующим образом. Сумматоры 36 и 37 имеют единичные коэффициенты передачи по всем входам. Входы сумматора 37 являются инверсными входами. После суммирования в этом сумматоре сигналов инверсных входов выходной сигнал этого сумматора инвертируется в инверторе 38 и подается на вход сумматора 36. На другие входы этого сумматора подаются сигналы прямых входов.

Принцип работы устройства заключается в следующем.

При работе систем радиосвязи, когда в точку приема приходят сигналы от передатчика по нескольким путям, возникают условия для появления многолучевости. Протяженность каждого луча различна, следовательно, различно время задержки при распространении по каждому лучу. В результате принимаемый сигнал растягивается по времени независимо от того, приходят ли несколько хорошо выраженных лучей или приходит множество лучей с близкими значениями временной задержки и отдельные лучи мало выражены.

Величина рассеяния энергии каждого символа при цифровой связи может составлять несколько TC, где TC - длительность одного символа. В результате возникает значительная межсимвольная интерференция (МСИ), когда вместо каждого нового символа будет кроме него приниматься сумма этого нового символа и нескольких предыдущих символов. Весовые коэффициенты в этой сумме - случайные величины, меняющиеся по времени. Количество налагающихся друг на друга символов определяется параметрами трассы и используемым частотным диапазоном.

Если в системе связи используется бинарная фазовая манипуляция (BPSK), то в отсутствие МСИ в приемнике на выходе коррелятора 3 будет наблюдаться чередование уровней +U и -U в зависимости от того, какой из двух логических сигналов передается. Пусть приему логической единицы соответствует появление уровня +U, приему логического нуля соответствует появление уровня -U. (На принцип работы не влияет, если реализуется обратное соответствие.)

Обозначим последовательность информационных логических символов, передаваемых по системе связи, через {ui}. Если бы не было МСИ и теплового шума, то на выходе коррелятора им бы однозначно соответствовала последовательность {xi}, где логической единице соответствует уровень сигнала после коррелятора, равный +U, а логическому нулю - уровень сигнала, равный -U. Появление логических единицы и нуля равновероятно.

В результате прохождения канала с рассеянием по времени на сигнал воздействуют МСИ и на приемной стороне после коррелятора образуется уже другая последовательность символов {yi}. Если без МСИ уровень всех сигналов постоянный (без учета знака символов), то теперь он становится различным, поскольку определяется суммой с несколькими предыдущими символами разного уровня, фазы которых могут как совпадать с фазой текущего символа, так и отличаться от нее на 180°.

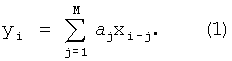

Обозначим общее число взаимно налагающихся символов через М, считая и текущий символ. Таким образом, каждый принятый символ yi при воздействии МСИ представляет собой сумму (М-1) предыдущих символов и текущего символа, взятых с некоторыми весовыми коэффициентами a j, т.е.:

(В этой формуле текущий символ обозначен индексом j=1, символ, наиболее удаленный от текущего, обозначен индексом j=М). Величины коэффициентов a i определяются текущим состоянием канала передачи. Величина символов yi принимает уже не одно из двух возможных значений, а может принимать множество значений в некотором интервале. Поскольку в случае использования относительных методов модуляции знак коэффициента a i у текущего символа значения не имеет, будем считать его положительным.

Из принятой последовательности yi в пороговом блоке 4 опять формируется бинарная последовательность zi путем сравнения значений yi с некоторым пороговым уровнем V. Если входной сигнал меньше V, то пороговый блок вырабатывает решение, что передавался логический ноль, если входной сигнал больше V, то вырабатывается решение, что передавалась логическая единица.

В случае отсутствия МСИ, на пороговый блок приходят сигналы xi (или с учетом медленного изменения коэффициента передачи в канале - сигналы a ixi), он должен только определить знак сигналов xi, и пороговый уровень V при этом должен быть равным нулю. В таком случае последовательности zi и xi совпадают.

В условиях многолучевости на пороговый блок, кроме «правильного» сигнала, приходит еще и «добавка», равная:

Она суммируется с «правильным» сигналом, т.е. yi=a1xi+εi и вызывает появление ошибок при детектировании сигнала. Чтобы устранить влияние этой добавки, пороговый уровень порогового блока теперь должен быть равным не нулю, а величине εi. Тогда в результате такой коррекции порогового уровня в соответствии с текущими условиями сравнение yi с εi позволить вновь вырабатывать правильные решения о знаке величины xi, то есть о значении переданного символа ui, и последовательности zi и xi вновь будут совпадать.

При обработке входных сигналов, реализуемой структурной схемой заявляемого устройства, осуществляется детектирование с учетом различного порогового уровня для разных принимаемых символов. Для этого символы zi продетектированной последовательности подаются с выхода порогового блока 4 на последовательный вход сдвигового регистра 6, имеющего M ячеек.

Для выработки уровня εi корректирующего значение порога, вычисляются оценки величин коэффициентов a j. Выработка оценок производится вычислителем 16. Для этого накапливается информация о значениях отсчетов yi и по ним вычисляются оценки.

Каждый отсчет yi равен сумме:

yi=a 1xi+a 2xi-1+…+a Mxi-M.

Поскольку величины xi могут принимать только два значения, то возможны L=2M вариантов наборов {x1, …, xM}. Значения коэффициентов меняются медленно, и за время измерения их можно считать постоянными. Тогда каждому варианту набора {x1, …, xM} без учета теплового шума соответствует одно и то же значение yi, которое можно приписать этому варианту набора.

В заявляемом устройстве наборы величин {x1, …, xM} обозначены наборами {z1, …, zM} их продетектированных значений. Если бы не было межсимвольной интерференции, то каждому набору {z1, …, zM} соответствовало бы также одно и то же значение yi, и, имея только M отсчетов yi и зная соответствующие им наборы {z1, …, zM}, можно было бы по ним безошибочно определить значения коэффициентов a j.

Однако из-за наличия шумов и межсимвольной интерференции возникают ошибки отождествления каждого zi с соответствующим xi. Последовательность {zi} не равна в точности последовательности {ui} и не всегда наборы {z1, …, zM} правильно соответствуют наборам {x1, …, xM}. Это означает, что в результате таких ошибок на основе продетектированных сигналов zi набору {x1, …, xM} не всегда будет правильно поставлен в соответствие его отсчет yi.

В заявляемом устройстве с приходом каждого нового символа производится анализ его значения и значений последних М-1 символов. Таких групп символов возможны L вариантов. Определяется, какому варианту группы соответствует текущий принятый символ yi. Далее путем усреднения находится среднее значение от всех принятых ранее значений yi, попавших в данную группу. Такая обработка производится параллельно по каждой из L групп.

Поскольку величины xi с равной вероятностью принимают значения +1 и -1, а уровень каждого отсчета yi определяется арифметической суммой по формуле (1), то среднее значение величин yi отнесенных к каждой группе, приближается к правильному значению yi, которое было бы измерено без воздействия шумов и межсимвольной интерференции. Эта оценка тем точнее, чем по большему количеству отсчетов производится усреднение.

Кроме того, для определения M неизвестных величин aj было бы достаточно использовать усредненные символы только M групп из имеющихся L групп. Однако во всех группах находится полезная информация, позволяющая уточнить значения оценок, поэтому в заявляемом устройстве для оценивания используются все L групп.

Пронумеруем группы индексами ν=1÷L, каждый индекс соответствует какому-то варианту набора {z1, …, zM}. Среднее значение отсчетов, накопившееся к текущему моменту в каждой группе, обозначим, как sν. В каждой группе величины sν образованы суммированием коэффициентов а 1÷a M с разными весовыми коэффициентами, равными либо +1, либо -1.

Представим совокупность величин sν в виде вектора s размера L×1, совокупность величин a 1÷a M в виде вектора a размера M×1, а совокупность весовых коэффициентов, с которыми из вектора a образуется вектор s - в виде матрицы Q размера L×M. При таком представлении s=Qa.

Необходимо на основе знания измеренных значений элементов вектора s определить значения элементов вектора a. Для этого можно использовать взвешенную сумму значений элементов s. Совокупность взвешивающих коэффициентов обозначим матрицей H размера L×M. Тогда a=HTs. (Верхний индекс «T» обозначает операцию транспонирования матрицы.) Непосредственное определение элементов этой матрицы H затруднительно, т.к. матрица Q не является квадратной, и для нее не существует обратной матрицы. Кроме этого, элементы матрицы H должны быть выбраны так, чтобы при обратном преобразовании была одновременно минимизирована погрешность измерения.

Для этой цели в заявляемом устройстве использована матрица, определяемая уравнением: H=Q(QTQ)-1. (Индекс «-1» обозначает операцию нахождения матрицы, обратной к исходной матрице.) Покажем, что такой вид матрицы H обеспечивает вычисление коэффициентов a j и, одновременно, минимизацию погрешностей измерения.

Поскольку коэффициенты матрицы Q известны заранее и не меняются в процессе работы, то и коэффициенты матрицы H также постоянны и могут быть заранее установлены еще до начала работы устройства. Из введенных обозначений следует, что a=HTs=HTQa, то есть

где E - единичная матрица.

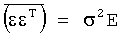

Рассмотрим набор погрешностей εν, возникающих при определении соответствующих sν. Все они вычисляются по одинаковому правилу, поэтому дисперсии всех погрешностей принимаются одинаковыми и равными σ2. Из этих погрешностей можно составить вектор ε. Элементы этого вектора можно считать взаимно независимыми, т.е.:

,

,

где верхняя черта означает операцию усреднения. С помощью матрицы H кроме оценок величин a j можно также получить вектор их погрешностей εP=HTε. Эти погрешности относятся не к элементам вектора s, а к элементам вектора a. Они уже не являются независимыми.

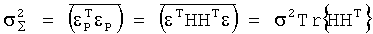

Суммарная погрешность всех элементов вектора оценок a определится суммой дисперсий погрешностей по каждому его элементу и будет равна:

,

,

где Tr{·} - след матрицы (сумма элементов ее главной диагонали).

Обозначим элементы матрицы H строки номера i и столбца номера j через hij. Тогда на основе свойств матричных преобразований можно записать

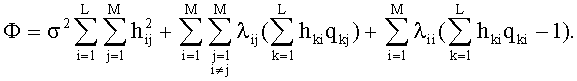

Для получения алгоритма обработки необходимо добиться минимизации выражения (4) при одновременном соблюдении условия (3). Для достижения этой цели воспользуемся методом неопределенных множителей Лагранжа, при этом минимизируемая функция описывается с помощью уравнения (4). Для получения необходимых для минимизации уравнений связи воспользуемся выражением (3). Обозначим через qij элемент строки i, столбца j матрицы Q. Тогда уравнение HTQ=E аналогично системе из M2 уравнений связи вида

Вводим M2 неопределенных множителей λij, i=1÷M, j=1÷M. Тогда функция Лагранжа будет иметь вид:

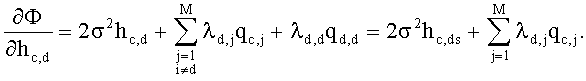

Выберем некоторый элемент hc,d матрицы H и продифференцируем по нему функцию Лагранжа.

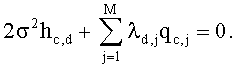

Дифференцируя функцию Ф по всем элементам матрицы H и приравнивая результаты дифференцирования нулю, получаем систему из L×M уравнений (c=1÷L, d=1÷M) вида:

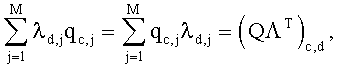

Составим из неопределенных множителей Лагранжа λd,j матрицу Λ (здесь d - номер ее строки, j - номер ее столбца). Элементы этой матрицы: (Λ)d,j=λd,j. (Размер этой матрицы равен M×M.) Элемент транспонированной матрицы (ΛT)j,d=λj,d. В результате получаем:

где (QΛT)c,d - элемент матрицы QΛT с индексами c, d. Приравнивая элементы с одинаковыми индексами, совокупность уравнений можно записать в виде одного матричного уравнения:

2σ2H+QΛT=0.

Или:

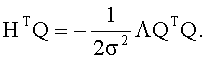

Транспонируем (5) и, домножив обе части уравнения справа на Q, получим:

Но было установлено, что HTQ=E. Отсюда:

так как матрица Λ оказывается симметричной. Далее, подставляя полученное значение матрицы Λ в уравнение (5), получаем выражение для искомой матрицы H:

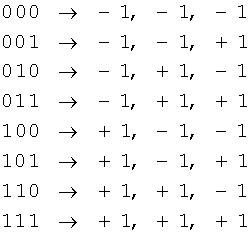

Пусть строки матрицы Q составлены в соответствии с последовательно возрастающим двоичным кодом. Поясним на примере для M=3.

Последовательно возрастающий двоичный код и соответствующие ему строки матрицы Q будут иметь следующий вид:

Проанализируем выражение (6), в частности, сомножитель QTQ. Строки матрицы Q (и столбцы матрицы QT) образованы на основе возрастающего двоичного кода. Таким образом, элемент i-й строки j-го столбца матрицы QTQ есть сумма произведений элементов одинаковых номеров из i-го и j-го столбцов матрицы Q. Нетрудно установить, что эта сумма равна нулю для всех i≠j, так как вектора, составленные из элементов столбцов матрицы Q, являются попарно ортогональными. А для i=j эта сумма равна числу элементов в столбце, т.е. равна L=2M.

Следовательно, матрица QTQ - диагональная и имеет вид: QTQ=ME. Соответственно, матрица (QTQ)-1=(1/L)E и, окончательно:

Матрица H совпадает с матрицей Q с поправкой на постоянный коэффициент 1/L. Умножение вектора s на матрицу H есть, по сути, просто сложение элементов этого вектора с коэффициентами +1 или -1, определяемыми соответствующим столбцом матрицы Q.

Подстройка порогового уровня производится следующим образом. Последовательность символов zi поступает на вход сдвигового регистра 6. Он содержит M ячеек, в которых в каждый текущий момент располагается текущий символ и M-1 предыдущих символов. С приходом каждого нового символа, символ, записанный в каждой ячейке, сдвигается в соседнюю ячейку.

На выходах канальных регулируемых усилителей 26, 27 присутствует совокупность измеренных коэффициентов a 1÷a M. Из них с помощью блоков переключения 23, 24 и первого сумматора 18 формируется текущая величина εi для коррекции порогового уровня. Для этого каждый коэффициент подается на вход первого сумматора либо непосредственно, либо через соответствующий инвертор 31. Выбор одного или другого пути прохождения сигнала определяется соответствующим ключом 32.

Каждый ключ управляется выходным сигналом с соответствующей ячейки сдвигового регистра 6, в которой расположены символы z2÷zM, т.е. все, кроме текущего символа. Если выходной сигнал ячейки равен единице, то ключ подключает ко входу первого сумматора 18 напряжение соответствующего коэффициента a без инвертирования, т.е. +a, а если выходной сигнал ячейки равен нулю, то ключ подключает инвертированное напряжение коэффициента a, т.е -a. В результате формируется «добавка» εi к пороговому уровню согласно формуле (2).

Вычисление оценок коэффициентов a j производится так. Текущее значение символа yi с выхода регулируемого усилителя 25 с помощью аналогового коммутатора 8 поступает на вход одного из блоков усреднения 9, 10, 11. Выбор блока усреднения производится с помощью адресного сигнала, поступающего на адресный вход аналогового коммутатора с формирователя адреса 7. Формирователь адреса формирует текущий нужный адрес на основе текущего набора сигналов в ячейках сдвигового регистра 6, т.е. на основе текущего набора z1÷zM. и направляет отсчет yi текущего символа в соответствующую адресу группу.

В каждом блоке усреднения 9, 10, 11 их входные сигналы усредняются (т.е. образуются сигналы sν) и подаются на вычислитель 16. В вычислителе они умножаются на соответствующие коэффициенты hij, далее складываются в соответствии с правилами умножения вектора на матрицу.

Блоки 5, 28, 14, 12, а также блоки 26, 27, 29, 30, 19, 15, 13 служат для необходимой совместной регулировки уровней коэффициентов аj при изменении условий распространения радиосигналов. В квадраторе 28 измеряется квадрат уровня текущего сигнала yi. В первом усреднителе 14 он усредняется по времени. Выходной сигнал первого усреднителя равен:

В первом вычитателе 12 он сравнивается с выходным напряжением источника опорного напряжения 17. С помощью полученного разностного сигнала регулируется коэффициент усиления регулируемого усилителя 5 таким образом, чтобы уровень суммы (8) оставался постоянным.

В каждом блоке регулировки 20, 21, 22 выходные сигналы канальных регулируемых усилителей 26, 27, равные вырабатываемым оценкам коэффициентов a 1÷a M, подаются на канальные квадраторы 29, 30 и далее на второй сумматор 19. После этого суммарный сигнал усредняется во втором усреднителе и становится равным сумме квадратов оценок коэффициентов a 1÷a M.

Далее он во втором вычитателе 13 также сравнивается с сигналом источника опорного напряжения 17. Полученный разностный сигнал одновременно регулирует коэффициенты усиления всех канальных регулируемых усилителей 26, 27 таким образом, чтобы уровень напряжения на выходе второго вычитателя 13 оставался постоянным.

Таким образом, средний уровень истинных значений коэффициентов a 1÷a M и их оценок поддерживается всегда одинаковым независимо от изменения свойств канала распространения, что обеспечивает правильную работу порогового блока.

Возможный вариант реализации вычислителя 16 представлен на фиг.2.

Он состоит из однотипных сумматоров 33, 34, 35 прямых и инверсных сигналов, имеющих по M/2 прямых входов и M/2 инверсных входов. Выходной сигнал каждого сумматора равен разности между суммой сигналов, поступивших на его прямые входы, и суммой сигналов, поступивших на его инверсные входы. Каждый сумматор вырабатывает напряжение, пропорциональное одному из коэффициентов a 1÷a M.

Каждому коэффициенту a j соответствует свой сумматор и свой столбец в матрице H. К инверсным входам этого сумматора подсоединяются те из сигналов s1÷sL, которым в этом столбце соответствуют элементы, равные -1, к прямым входам этого сумматора подсоединяются те из сигналов s1÷sL, которым в этом столбце соответствуют элементы, равные +1. Наличие в записи матрицы (7) общего множителя, равного 1/L, компенсируется совместной автоматической регулировкой коэффициентов усиления канальных регулируемых усилителей в блоках регулировки 20, 21, 22 и в регулируемом усилителе 25, обеспечивающей соответствие уровней коэффициентов a 1÷a M и вычисляемых их оценок.

Возможный вариант реализации структурной схемы каждого сумматора прямых и инверсных сигналов представлен на фиг.3. Все сигналы из совокупности s1÷sL, которые должны складываться при формировании соответствующего a j с коэффициентом -1, предварительно складываются в сумматоре 37, выходной сигнал которого далее инвертируется и поступает на вход сумматора 36. На другие его входы подаются из совокупности s1÷sL, которые должны складываться при формировании соответствующего a j с коэффициентом +1.

С началом работы устройства оценки коэффициентов a 1÷a M из-за усреднения в блоках усреднения 9, 10 и 11 постепенно становятся все более точными. В результате этого пороговый уровень в пороговом блоке 4 позволяет точнее демодулировать последовательность yi, и количество ошибок в демодулированной последовательности zi уменьшается. А это в свою очередь дает возможность уменьшить погрешности при вычислении оценок и дополнительно снизить количество ошибок при детектировании и т.д.

Предлагаемый приемник цифровых сигналов позволяет уменьшить влияние межсимвольной интерференции и снизить вероятность ошибок при передаче цифровых сигналов по многолучевым каналам, тем самым повысить помехоустойчивость и надежность передачи информации.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ДЕКОДИРОВАНИЯ СВЕРТОЧНЫХ КОДОВ | 2012 |

|

RU2516624C1 |

| Многоканальный приемник с кодовым разделением каналов для приема сигналов с квадратурной m-ичной амплитудно-инверсной модуляцией | 2017 |

|

RU2669371C1 |

| ОБНАРУЖИТЕЛЬ СИГНАЛОВ | 1991 |

|

RU2106652C1 |

| Расходомер двухфазных сред | 1990 |

|

SU1783304A1 |

| Устройство разнесенного приема | 1981 |

|

SU1088140A1 |

| Устройство для детектирования фазоманипулированных сигналов | 1982 |

|

SU1051737A1 |

| ЦИФРОВОЙ РАДИОПЕЛЕНГАТОР | 1999 |

|

RU2149419C1 |

| СПОСОБ ПРИЕМА ПАРАЛЛЕЛЬНОГО МНОГОЧАСТОТНОГО СОСТАВНОГО СИГНАЛА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2207732C2 |

| АДАПТИВНОЕ ПРИЕМНОЕ УСТРОЙСТВО ШУМОПОДОБНЫХ СИГНАЛОВ | 1997 |

|

RU2128881C1 |

| АВТОМАТИЧЕСКИЙ КОМПЕНСАТОР | 1983 |

|

SU1840994A1 |

Изобретение относится к технике радиосвязи и может быть использовано для приема цифровых сигналов, использующих бинарную фазовую манипуляцию в каналах с многолучевым распространением сигналов, вызывающим межсимвольную интерференцию. Достигаемый технический результат - повышение помехоустойчивости и надежности передачи цифровой информации по каналам с многолучевым распространением сигналов. Устройство содержит генератор опорных сигналов, детектор, коррелятор, пороговый блок, тактовый генератор, сдвиговый регистр, формирователь адреса, аналоговый коммутатор, блоки усреднения, первый и второй вычитатели, первый и второй усреднители, вычислитель, источник опорного напряжения, первый и второй сумматоры, блоки регулировки, блоки переключения, регулируемый усилитель, канальные регулируемые усилители, квадратор, канальные квадраторы, инвертор, ключ. 3 ил.

Приемник цифровых сигналов, содержащий детектор, состоящий из коррелятора и порогового блока, генератор опорных сигналов и первый сумматор, отличающийся тем, что в него введены сдвиговый регистр, тактовый генератор, формирователь адреса, аналоговый коммутатор, вычислитель, 2M блоков усреднения, М блоков регулировки, второй сумматор, первый и второй усреднители, первый и второй вычитатели, квадратор, регулируемый усилитель, источник опорного напряжения и (М-1) блоков переключения, каждый из блоков переключения содержит инвертор и ключ, каждый из блоков регулировки содержит канальный квадратор и канальный регулируемый усилитель, при этом вход устройства и выход генератора опорных сигналов подключены ко входам коррелятора, а его выход через регулируемый усилитель - к сигнальному входу аналогового коммутатора и к первому входу порогового блока, выход которого соединен с выходом устройства и с сигнальным входом сдвигового регистра, выход тактового генератора соединен с тактовыми входами сдвигового регистра и аналогового коммутатора, первый выход сдвигового регистра подключен к одному из входов формирователя адреса, а другие М-1 выходов сдвигового регистра подключены к управляющим входам ключей всех блоков переключения и к другим М-1 входам формирователя адреса, а его выходы - к адресным входам аналогового коммутатора, каждый выход аналогового коммутатора через соответствующий блок усреднения подключен к одному из 2M входов вычислителя, каждый из М выходов вычислителя через соответствующий блок регулировки, содержащий последовательно соединенные канальный регулируемый усилитель и канальный квадратор соединен с соответствующим входом второго сумматора, выход которого через второй усреднитель подключен к одному из входов второго вычитателя, выход второго вычитателя подключен к регулировочным входам канальных регулируемых усилителей всех блоков регулировки, вход квадратора соединен с выходом регулируемого усилителя, а выход через первый усреднитель - с одним из входов первого вычитателя, а его выход - с другим входом регулируемого усилителя, выход источника опорного напряжения подключен к другим входам первого и второго вычитателей, выходы канальных регулируемых усилителей блоков регулировки от второго номера до номера М соединены со входами соответствующих блоков переключения, выходы всех блоков переключения - со входами первого сумматора, а его выход - со вторым входом порогового блока, вход каждого блока регулировки подключен к одному из входов ключа и через инвертор - к другому входу ключа, а выход ключа подсоединен к выходу данного блока регулировки.

| Способ приготовления мыла | 1923 |

|

SU2004A1 |

| СПОСОБ КОМПЕНСАЦИИ ВНУТРИКАНАЛЬНЫХ АДДИТИВНЫХ РАДИОПОМЕХ В ПРИЕМНИКАХ АМПЛИТУДНО-МОДУЛИРОВАННЫХ, ЧАСТОТНО- И ФАЗОМАНИПУЛИРОВАННЫХ РАДИОСИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1996 |

|

RU2100903C1 |

| ПРИЕМНИК-КОМПАРАТОР СИГНАЛОВ СПУТНИКОВЫХ РАДИОНАВИГАЦИОННЫХ СИСТЕМ | 2002 |

|

RU2236753C2 |

| WO 00/54418 A1, 14.09.2000. | |||

Авторы

Даты

2011-07-10—Публикация

2010-06-01—Подача