Группа изобретений относится к области вычислительной техники и может быть использована для эмуляции нейронных сетей и цифровой обработки сигналов в реальном масштабе времени.

Известен нейропроцессор [1], содержащий регистр входных данных и четыре нейронных узла, каждый из которых состоит из сдвигового регистра, регистра весовых коэффициентов, восьми умножителей, схемы многооперандного сложения и блока для вычисления пороговой функции.

Такой нейропроцессор в каждом такте выполняет взвешенное суммирование фиксированного числа входных данных для фиксированного числа нейронов независимо от реального диапазона значений входных данных и их весовых коэффициентов. При этом каждое входное данное, так же как и каждый весовой коэффициент, представляется в виде операнда фиксированной разрядности, определяемой разрядностью аппаратных узлов нейропроцессора. Однако, значения входных данных и весовых коэффициентов могут варьироваться в очень широком диапазоне как при переходе от одной нейронной сети к другой, так и при переходе от одного фрагмента нейронной сети к другому фрагменту этой же сети. Поэтому при эмуляции нейронной сети или ее фрагмента с малыми значениями входных данных и (или) весовых коэффициентов аппаратура известного нейропроцессора используется неэффективно.

Таким образом, основным недостатком известного нейропроцессора является отсутствие возможности программно изменять разрядность обрабатываемых входных данных и их весовых коэффициентов, что в свою очередь приводит к аппаратной избыточности и относительно низкой производительности нейропроцессора при эмуляции фрагментов нейронных сетей с малыми значениями входных данных и (или) весовых коэффициентов.

Наиболее близким по технической сущности к первому изобретению является нейропроцессор [2], содержащий три регистра, мультиплексор, блок памяти магазинного типа, операционное устройство для вычисления скалярного произведения двух векторов данных программируемой разрядности с прибавлением накапливаемого результата и устройство для вычисления нелинейной функции.

На входы такого нейропроцессора подаются вектора входных данных и вектора их весовых коэффициентов. В каждом такте нейропроцессор выполняет взвешенное суммирование нескольких входных данных для одного нейрона путем вычисления скалярного произведения вектора входных данных на вектор весовых коэффициентов. Причем нейропроцессор поддерживает обработку векторов, разрядность отдельных составляющих которых может быть программно выбрана из ряда фиксированных значений. С уменьшением разрядности отдельных входных данных и весовых коэффициентов увеличивается их количество в каждом векторе и тем самым повышается производительность нейропроцессора. Однако, разрядность получаемых результатов фиксирована и определяется разрядностью аппаратных узлов нейропроцессора.

Таким образом, основным недостатком известного нейропроцессора является отсутствие возможности программно изменять разрядность выходных данных, что в свою очередь приводит к аппаратной избыточности и относительно низкой производительности нейропроцессора при эмуляции фрагментов нейронных сетей с малыми значениями входных данных и (или) весовых коэффициентов.

Известно цифровое устройство ограничения числа по модулю [3], содержащее три регистра, сумматор, два преобразователя кодов, два блока анализа знаков, блок коррекции, две группы элементов И и группу элементов ИЛИ. Такое устройство позволяет за 2N тактов вычислять функции насыщения для вектора из N входных операндов.

Недостатками известного устройства ограничения числа по модулю являются низкая производительность и большие аппаратные затраты.

Наиболее близким по технической сущности к второму изобретению является устройство для вычисления функций насыщения [4], содержащее мультиплексор, компаратор и два индикатора насыщения. Такое устройство позволяет за N тактов вычислять функции насыщения для вектора из N входных операндов.

Недостатком такого устройства для вычисления функций насыщения является низкая производительность при обработке множества операндов, имеющих малые значения.

Известно вычислительное устройство [2], содержащее умножители, сумматоры, регистры, мультиплексор и блок памяти магазинного типа. Данное устройство позволяет за один такт вычислить скалярное произведение двух векторов, каждый из которых содержит по M операндов, и за N тактов выполнить умножение матрицы, содержащей N x М операндов, на вектор, состоящий из М операндов.

Недостатками известного вычислительного устройства являются низкое быстродействие и большие аппаратные затраты.

Наиболее близким по технической сущности к третьему изобретению является вычислительное устройство [5], содержащее 3N/2 логических элементов И, N/2 дешифраторов разрядов множителя по алгоритму Бута, матрицу умножения из N столбцов по N/2 ячеек, каждая из которых состоит из схемы формирования разряда частичного произведения по алгоритму Бута и одноразрядного сумматора, 2N-разрядный сумматор, N/2 мультиплексоров, N/2 дополнительных схем формирования разряда частичного произведения по алгоритму Бута и N/2 логических элементов импликации. Данное устройство позволяет за один такт перемножить два N-разрядных операнда или перемножить поэлементно два вектора, каждый из которых содержит по два (N/2)-разрядных операнда.

Недостаток такого вычислительного устройства заключается в его ограниченных функциональных возможностях, не позволяющих выполнять умножение матрицы операндов на вектор операндов.

Известно устройство для сложения векторов операндов программируемой разрядности [6], содержащее сумматоры и логические элементы ЗАПРЕТ.

Недостатками известного устройства являются низкое быстродействие, вследствие последовательного распространения сигналов переноса между сумматорами, и ограниченные функциональные возможности.

Наиболее близким по технической сущности к четвертому изобретению является сумматор [7], содержащий схему формирования переносов и в каждом своем разряде - полусумматор и логический элемент ИСКЛЮЧАЮЩЕЕ ИЛИ. Данный сумматор позволяет за N тактов выполнить сложение двух векторов, состоящих из N операндов каждый.

Недостатком такого сумматора является низкая производительность при сложении векторов данных.

Достигаемый технический результат первого изобретения заключается в повышении производительности нейропроцессора путем обеспечения возможности программно изменять разрядности результатов.

Указанный технический результат достигается тем, что в нейропроцессор, содержащий первый, второй и третий регистры, первый блок памяти магазинного типа и мультиплексор, первый информационный вход каждого разряда которого соединен с выходом соответствующего разряда первого регистра, информационный вход каждого разряда второго регистра подключен к соответствующему разряду первой входной шины нейропроцессора, входы управления первого, второго и третьего регистров являются соответствующими управляющими входами нейропроцессора, введены четвертый, пятый и шестой регистры, сдвиговый регистр, логический элемент И, второй блок памяти магазинного типа, коммутатор с трех направлений в два, два устройства для вычисления функций насыщения, сумматор и вычислительное устройство, имеющее входы разрядов вектора первых операндов, входы разрядов вектора вторых операндов, входы разрядов вектора третьих операндов, входы установки границ данных в векторах первых операндов и результатов, входы установки границ данных в векторах вторых операндов, входы установки границ данных в векторах третьих операндов, первый и второй входы управления загрузкой векторов третьих операндов в первый блок памяти, вход управления пересылкой матрицы третьих операндов из первого блока памяти во второй блок памяти и выходы разрядов вектора первых и вектора вторых слагаемых результатов операции сложения вектора первых операндов с произведением вектора вторых операндов на матрицу третьих операндов, хранящуюся во втором блоке памяти, причем первые информационные входы разрядов коммутатора с трех направлений в два, информационные входы первого блока памяти магазинного типа, первого, третьего и четвертого регистров и параллельные информационные входы сдвигового регистра поразрядно объединены и подключены к соответствующим разрядам первой входной шины нейропроцессора, каждый разряд второй входной шины которого соединен с вторым информационным входом соответствующего разряда коммутатора с трех направлений в два, первый выход каждого разряда которого соединен с входом соответствующего разряда вектора входных операндов первого устройства для вычисления функций насыщения, управляющий вход каждого разряда которого соединен с выходом соответствующего разряда второго регистра, второй выход каждого разряда коммутатора с трех направлений в два соединен с входом соответствующего разряда вектора входных операндов второго устройства для вычисления функций насыщения, управляющий вход каждого разряда которого соединен с выходом соответствующего разряда третьего регистра, выход каждого разряда вектора результатов первого устройства для вычисления функций насыщения соединен с вторым информационным входом соответствующего разряда мультиплексора, выход каждого разряда которого соединен с входом соответствующего разряда вектора первых операндов вычислительного устройства, вход каждого разряда вектора вторых операндов которого соединен с выходом соответствующего разряда вектора результатов второго устройства для вычисления функций насыщения, информационные выходы первого блока памяти магазинного типа соединены с входами соответствующих разрядов вектора третьих операндов вычислительного устройства, выход каждого разряда вектора первых слагаемых результатов операции сложения вектора первых операндов с произведением вектора вторых операндов на матрицу третьих операндов, хранящуюся во втором блоке памяти, которого соединен с входом соответствующего разряда вектора первых слагаемых сумматора, вход каждого разряда вектора вторых слагаемых которого соединен с выходом соответствующего разряда вектора вторых слагаемых результатов операции сложения вектора первых операндов с произведением вектора вторых операндов на матрицу третьих операндов, хранящуюся во втором блоке памяти, вычислительного устройства, каждый вход установки границ данных в векторах первых операндов и результатов которого соединен с выходом соответствующего разряда пятого регистра и с соответствующим входом установки границ данных в векторах слагаемых и сумм сумматора, выход каждого разряда вектора сумм которого соединен с соответствующим информационным входом второго блока памяти магазинного типа, каждый информационный выход которого подключен к соответствующему разряду выходной шины нейропроцессора и соединен с третьим входом соответствующего разряда коммутатора с трех направлений в два, выход каждого разряда четвертого регистра соединен с информационным входом соответствующего разряда пятого регистра и соответствующим входом установки границ данных в векторах третьих операндов вычислительного устройства, каждый вход установки границ данных в векторах вторых операндов которого соединен с выходом соответствующего разряда шестого регистра, информационный вход каждого разряда которого соединен с выходом соответствующего разряда сдвигового регистра, последовательные информационные вход и выход которого объединены и подключены к первому входу управления загрузкой векторов третьих операндов в первый блок памяти вычислительного устройства и к первому входу элемента И, выход которого соединен с входом управления чтением первого блока памяти магазинного типа, второй вход элемента И, вход управления сдвигом сдвигового регистра и второй вход управления загрузкой векторов третьих операндов в первый блок памяти вычислительного устройства объединены и подключены к соответствующему управляющему входу нейропроцессора, вход управления пересылкой матрицы третьих операндов из первого блока памяти во второй блок памяти вычислительного устройства и входы управления пятого и шестого регистров объединены и подключены к соответствующему управляющему входу нейропроцессора, управляющие входы коммутатора с трех направлений в два, мультиплексора и четвертого регистра, входы управления записью сдвигового регистра и первого блока памяти магазинного типа и входы управления чтением и записью второго блока памяти магазинного типа являются соответствующими управляющими входами нейропроцессора, выходы состояния первого и второго блоков памяти магазинного типа являются выходами состояния нейропроцессора.

В нейропроцессоре может применяться вычислительное устройство, содержащее сдвиговый регистр, выполняющий за один такт арифметический сдвиг всех операндов хранящегося в нем N-разрядного вектора на J разрядов влево, где J - минимальная величина, которой кратны разрядности данных в векторах вторых операндов вычислительного устройства, элемент задержки, первый блок памяти, имеющий порт ввода магазинного типа и содержащий N/J ячеек для хранения N-разрядных данных, второй блок памяти, содержащий N/J ячеек для хранения N-разрядных данных, N/J блоков умножения, каждый из которых умножает N-разрядный вектор данных программируемой разрядности на J-разрядный множитель, и схему сложения векторов, формирующую двухрядный код суммы N/J+1 векторов данных программируемой разрядности, причем входы разрядов вектора третьих операндов вычислительного устройства подключены к информационным входам сдвигового регистра, выходы которого соединены с информационными входами первого блока памяти, выходы каждой ячейки которого соединены с информационными входами соответствующей ячейки второго блока памяти, выходы каждой ячейки которого соединены с входами разрядов вектора множимых соответствующего блока умножения, входы разрядов множителя которого подключены к входам соответствующей J-разрядной группы разрядов вектора вторых операндов вычислительного устройства, выходы каждого блока умножения соединены с входами разрядов соответствующего вектора слагаемых схемы сложения векторов, входы разрядов (N/J+1)-го вектора слагаемых которой подключены к входам разрядов вектора первых операндов вычислительного устройства, входы установки границ данных в векторах третьих операндов которого подключены к соответствующим входам установки границ данных в векторах операндов сдвигового регистра, вход режима работы которого подключен к первому входу управления загрузкой векторов третьих операндов в первый блок памяти вычислительного устройства, второй вход управления загрузкой векторов третьих операндов в первый блок памяти которого подключен к тактовому входу сдвигового регистра и входу элемента задержки, выход которого соединен с входом управления записью первого блока памяти, вход управления записью второго блока памяти подключен к входу управления пересылкой матрицы третьих операндов из первого блока памяти во второй блок памяти вычислительного устройства, каждый вход установки границ данных в векторах вторых операндов которого подключен к входу знаковой коррекции соответствующего блока умножения, входы установки границ данных в векторах первых операндов и результатов вычислительного устройства подключены к входам установки границ данных в векторах множимых и результатов каждого блока умножения и к входам установки границ данных в векторах слагаемых и результатов схемы сложения векторов, выходы разрядов векторов первых и вторых слагаемых результатов которой являются соответствующими выходами вычислительного устройства.

Достигаемый технический результат первого изобретения может быть усилен путем уменьшения длительности процессорного такта.

Указанное усиление технического результата достигается тем, что в описанном выше нейропроцессоре каждое из устройств для вычисления функций насыщения содержит регистр входных данных, информационные входы которого являются входами соответствующих разрядов вектора входных операндов этого устройства, вычислительное устройство содержит регистр входных данных, информационные входы которого являются входами соответствующих разрядов векторов первых и вторых операндов вычислительного устройства, сумматор содержит регистр входных данных, информационные входы которого являются соответствующими входами сумматора.

Достигаемый технический результат второго изобретения заключается в повышении производительности устройства для вычисления функций насыщения путем обеспечения возможности одновременной обработки вектора входных операндов программируемой разрядности.

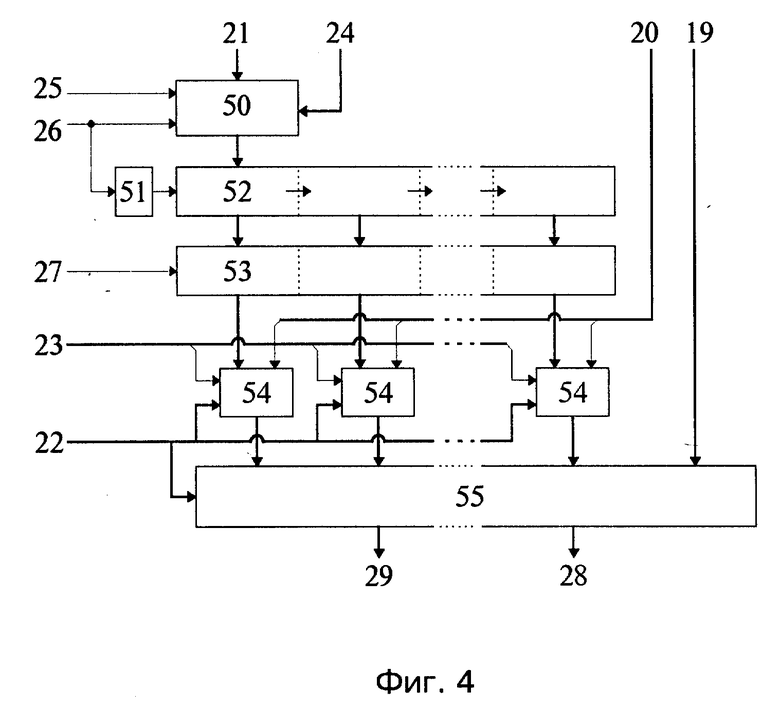

Указанный технический результат достигается тем, что в устройство для вычисления функций насыщения, содержащее в каждом из N разрядов первый мультиплексор, второй информационный вход которого подключен к входу соответствующего разряда вектора входных операндов устройства, выход каждого разряда вектора результатов которого подключен к выходу первого мультиплексора соответствующего разряда устройства, введены схема распространения переносов и схема формирования переносов, а в его каждый разряд введены второй мультиплексор и логические элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, РАВНОЗНАЧНОСТЬ, И-НЕ и ЗАПРЕТ, причем прямой вход элемента ЗАПРЕТ и первые входы элементов И-НЕ и РАВНОЗНАЧНОСТЬ каждого разряда устройства объединены и подключены к соответствующему управляющему входу устройства, выход элемента И-НЕ n-го разряда устройства соединен с входом распространения переноса через (N-n+1)-й разряд схемы формирования переносов, выход переноса в (N-n+2)-й разряд которой соединен с управляющим входом первого мультиплексора n-го разряда устройства, выход элемента ЗАПРЕТ которого соединен с управляющим входом второго мультиплексора этого же разряда устройства, входом генерации переноса в (N-n+1)-м разряде схемы формирования переносов и инверсным входом распространения переноса через (N-n+1)-й разряд схемы распространения переносов, вход переноса из (N-n+1)-го разряда которой соединен с выходом второго мультиплексора n-го разряда устройства (где n=1,2,...N), первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и прямой вход элемента ЗАПРЕТ q-го разряда устройства соединены соответственно с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и инверсным входом элемента ЗАПРЕТ (q-1)-го разряда устройства, первый информационный вход второго мультиплексора которого соединен с выходом переноса в (N-q+2)-й разряд схемы распространения переносов (где q=2,3,...,N), входы начальных переносов схемы распространения переносов и схемы формирования переносов, второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, инверсный вход элемента ЗАПРЕТ и первый информационный вход второго мультиплексора N-го разряда устройства объединены и подключены к шине логического нуля, а в каждом разряде устройства выход второго мультиплексора соединен с вторым входом элемента РАВНОЗНАЧНОСТЬ, выход которого соединен с первым информационным входом первого мультиплексора, второй информационный вход которого соединен с вторым информационным входом второго мультиплексора и первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с вторым входом элемента И-НЕ этого же разряда устройства.

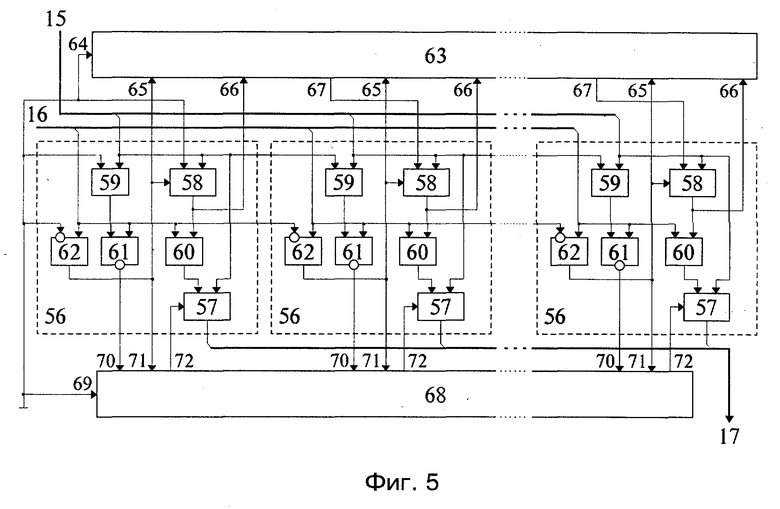

В частных случаях применения второго изобретения, когда предъявляются жесткие требования по минимизации аппаратных затрат, в схеме распространения переносов выход переноса в q-й разряд соединен с входом переноса из (q-1)-ro разряда (где q=2,3,...,N), а схема формирования переносов содержит по N логических элементов И и ИЛИ, причем каждый вход распространения переноса через соответствующий разряд схемы формирования переносов подключен к первому входу соответствующего элемента И, выход которого соединен с первым входом соответствующего элемента ИЛИ, второй вход и выход которого подключены соответственно к входу генерации переноса в соответствующем разряде схемы формирования переносов и выходу переноса в этот же разряд схемы формирования переносов, второй вход первого элемента И является входом начального переноса схемы формирования переносов, второй вход q-го элемента И соединен с выходом (q-1)-ro элемента ИЛИ (где q=2,3,...,N).

Достигаемый технический результат третьего изобретения заключается в расширении функциональных возможностей вычислительного устройства.

Указанный технический результат достигается тем, что в вычислительное устройство, содержащее N/2 дешифраторов разрядов множителя и матрицу умножения из N столбцов по N/2 ячеек, каждая из которых состоит из схемы формирования разряда частичного произведения и одноразрядного сумматора, причем соответствующие управляющие входы схем формирования разряда частичного произведения i-x ячеек всех столбцов матрицы умножения объединены и подключены к соответствующим выходам i-го дешифратора разрядов множителя (где i= 1,2, . . . ,N/2), первый вход одноразрядного сумматора каждой ячейки матрицы умножения соединен с выходом схемы формирования разряда частичного произведения этой же ячейки матрицы умножения, введены N/2 логических элементов ЗАПРЕТ, элемент задержки и N-разрядный сдвиговый регистр, каждый разряд которого состоит из логического элемента ЗАПРЕТ, мультиплексора и триггера, а в каждую ячейку матрицы умножения введены первый и второй триггеры, выполняющие функции ячеек памяти соответственно первого и второго блоков памяти устройства, логический элемент ЗАПРЕТ и мультиплексор, причем вход каждого разряда вектора первых операндов устройства подключен к второму входу одноразрядного сумматора первой ячейки соответствующего столбца матрицы умножения, управляющие входы мультиплексоров и инверсные входы элементов ЗАПРЕТ всех ячеек каждого столбца которой объединены и подключены к соответствующему входу установки границ данных в векторах первых операндов и результатов устройства, каждый вход установки границ данных в векторах вторых операндов которого подключен к инверсному входу соответствующего элемента ЗАПРЕТ, выход которого соединен с первым входом соответствующего дешифратора разрядов множителя, второй и третий входы i-го дешифратора разрядов множителя подключены к входам соответственно (2i-1)-го и (2i)-го разрядов вектора вторых операндов устройства (где i=1,2,...,N/2), прямой вход j-го элемента ЗАПРЕТ соединен с третьим входом (j-1)-го дешифратора разрядов множителя (где j= 2,3, . ..,N/2), вход каждого разряда вектора третьих операндов устройства подключен к второму информационному входу мультиплексора соответствующего разряда сдвигового регистра, первый информационный вход которого соединен с выходом элемента ЗАПРЕТ этого же разряда сдвигового регистра, первый инверсный вход которого подключен к соответствующему входу установки границ данных в векторах третьих операндов устройства, второй инверсный вход элемента ЗАПРЕТ q-го разряда сдвигового регистра соединен с первым инверсным входом элемента ЗАПРЕТ (q-1)-го разряда сдвигового регистра (где q=2,3,..., N), прямой вход элемента ЗАПРЕТ r-го разряда сдвигового регистра соединен с выходом триггера (r-2)-го разряда сдвигового регистра (где r=3,4,...,N), управляющие входы мультиплексоров всех разрядов сдвигового регистра объединены и подключены к первому входу управления загрузкой векторов третьих операндов в первый блок памяти устройства, входы синхронизации триггеров всех разрядов сдвигового регистра и вход элемента задержки объединены и подключены к второму входу управления загрузкой векторов третьих операндов в первый блок памяти устройства, выход мультиплексора каждого разряда сдвигового регистра соединен с информационным входом триггера этого же разряда сдвигового регистра, выход которого соединен с информационным входом первого триггера последней ячейки соответствующего столбца матрицы умножения, выход первого триггера j-й ячейки каждого столбца матрицы умножения соединен с информационным входом первого триггера (j-1)-й ячейки этого же столбца матрицы умножения (где j= 2,3, ...,N/2), входы синхронизации первых триггеров всех ячеек матрицы умножения объединены и подключены к выходу элемента задержки, входы синхронизации вторых триггеров всех ячеек матрицы умножения объединены и подключены к входу управления пересылкой матрицы третьих операндов из первого блока памяти во второй блок памяти устройства, второй информационный вход схемы формирования разряда частичного произведения i-й ячейки q-го столбца матрицы умножения соединен с выходом элемента ЗАПРЕТ i-й ячейки (q-1)-го столбца матрицы умножения (где i=1,2,...,N/2 и q=2,3,...,N), второй вход одноразрядного сумматора j-й ячейки каждого столбца матрицы умножения соединен с выходом суммы одноразрядного сумматора (j-1)-й ячейки этого же столбца матрицы умножения (где j=2,3,...,N/2), третий вход одноразрядного сумматора j-й ячейки q-го столбца матрицы умножения соединен с выходом мультиплексора (j-1)-й ячейки (q-1)-го столбца матрицы умножения (где j=2,3, . . . , N/2 и q=2,3,...,N), третий вход одноразрядного сумматора j-й ячейки первого столбца матрицы умножения соединен с третьим выходом (j-1)-го дешифратора разрядов множителя (где j=2,3,...,N/2), выход суммы одноразрядного сумматора последней ячейки каждого столбца матрицы умножения является выходом соответствующего разряда вектора первых слагаемых результатов устройства, выход мультиплексора последней ячейки (q-1)-го столбца матрицы умножения является выходом q-го разряда вектора вторых слагаемых результатов устройства (где q= 2,3, ...,N), первый разряд вектора вторых слагаемых результатов которого подключен к третьему выходу (N/2)-го дешифратора разрядов множителя, второй инверсный и прямой входы элемента ЗАПРЕТ первого разряда и прямой вход элемента ЗАПРЕТ второго разряда сдвигового регистра, вторые информационные входы схем формирования разряда частичного произведения всех ячеек первого столбца матрицы умножения, третьи входы одноразрядных сумматоров первых ячеек всех столбцов матрицы умножения и прямой вход первого элемента ЗАПРЕТ объединены и подключены к шине логического нуля, а в каждой ячейке матрицы умножения выход первого триггера соединен с информационным входом второго триггера, выход которого соединен с прямым входом элемента ЗАПРЕТ и первым информационным входом схемы формирования разряда частичного произведения, третий управляющий вход которой соединен с вторым информационным входом мультиплексора, первый информационный вход которого соединен с выходом переноса одноразрядного сумматора этой же ячейки матрицы умножения.

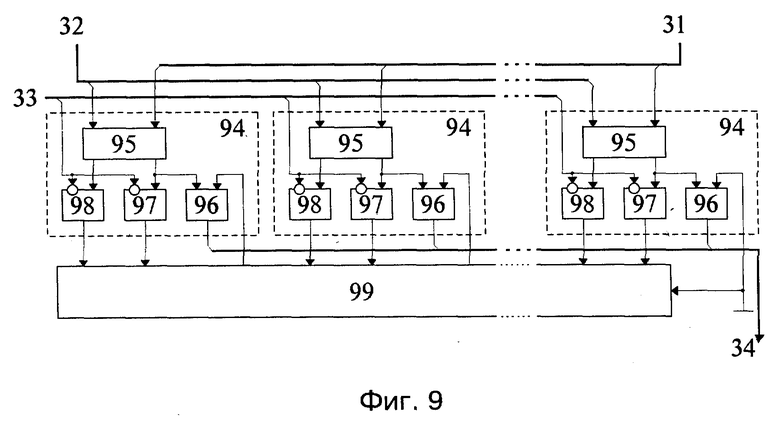

Достигаемый технический результат четвертого изобретения заключается в повышении производительности сумматора путем введения в состав выполняемых им операций арифметических операций над векторами данных программируемой разрядности.

Указанный технический результат достигается тем, что в каждый разряд сумматора, содержащего схему формирования переносов, а в каждом из N своих разрядов - полусумматор и логический элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, причем вход каждого разряда вектора первых слагаемых сумматора и вход соответствующего разряда вектора вторых слагаемых сумматора подключены соответственно к первому и второму входам полусумматора соответствующего разряда сумматора, выход суммы которого соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ этого же разряда сумматора, выход которого является выходом соответствующего разряда вектора сумм сумматора, второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ q-го разряда сумматора соединен с выходом переноса в q-й разряд схемы формирования переносов (где q= 2,3, . . .,N), вход начального переноса которой и второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ первого разряда сумматора подключены к шине логического нуля, введены первый и второй логические элементы ЗАПРЕТ, причем выход суммы полусумматора каждого разряда сумматора соединен с прямым входом первого элемента ЗАПРЕТ этого же разряда сумматора, выход которого соединен с входом распространения переноса через соответствующий разряд схемы формирования переносов, выход переноса полусумматора каждого разряда сумматора соединен с прямым входом второго элемента ЗАПРЕТ этого же разряда сумматора, выход которого соединен с входом генерации переноса в соответствующем разряде схемы формирования переносов, инверсные входы первого и второго элементов ЗАПРЕТ каждого разряда сумматора объединены и подключены к соответствующему входу установки границ данных в векторах слагаемых и сумм сумматора.

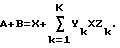

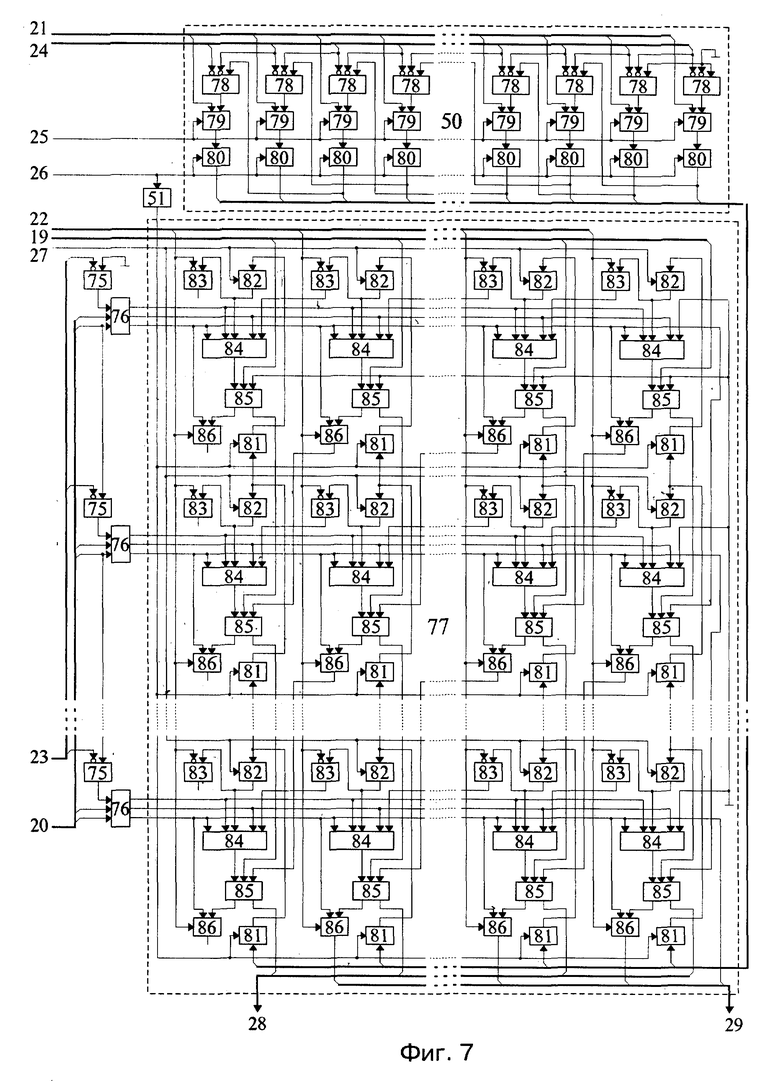

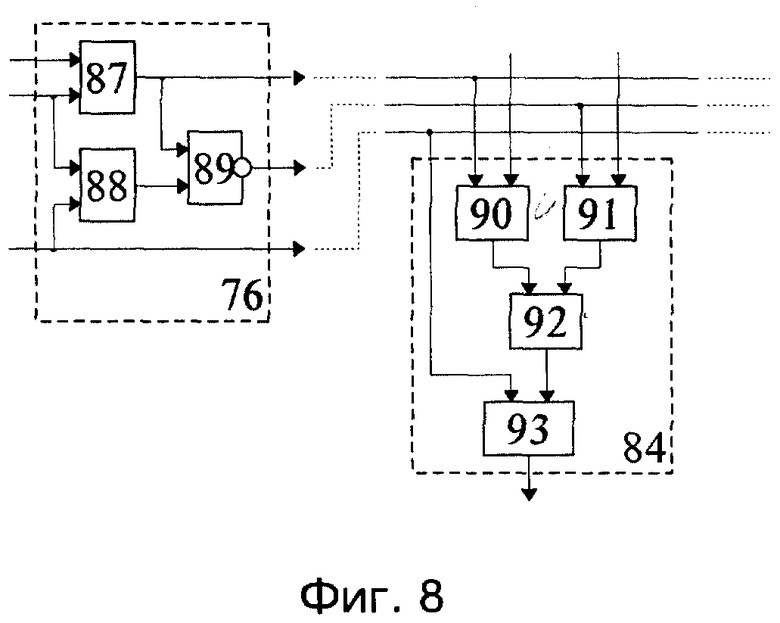

На фиг. 1 приведена блок-схема нейропроцессора, на фиг.2 - общий вид функций насыщения, формируемых устройствами для вычисления функций насыщения, на фиг.3 - модель слоя нейронной сети, эмулируемой нейропроцессором, на фиг. 4 - блок-схема вычислительного устройства, на фиг.5 - схема устройства для вычисления функций насыщения векторов данных программируемой разрядности, на фиг.6 - схема формирования переносов, которая может применяться в устройстве для вычисления функций насыщения, на фиг.7 - схема вычислительного устройства, на фиг.8 - примеры схемотехнической реализации дешифратора разрядов множителя и схемы формирования разряда частичного произведения по алгоритму Бута, применяемых в вычислительном устройстве, на фиг.9 - схема сумматора векторов данных программируемой разрядности.

Нейропроцессор, блок-схема которого представлена на фиг.1, содержит первый 1, второй 2, третий 3, четвертый 4, пятый 5 и шестой 6 регистры, сдвиговый регистр 7, логический элемент И 8, первый 9 и второй 10 блоки памяти магазинного типа, коммутатор с трех направлений в два 11, мультиплексор 12, первое 13 и второе 14 устройства для вычисления функций насыщения, каждое из которых имеет входы разрядов вектора входных операндов 15, управляющие входы 16 и выходы разрядов вектора результатов 17, вычислительное устройство 18, имеющее входы разрядов вектора первых 19, вектора вторых 20 и вектора третьих 21 операндов, входы установки границ данных в векторах первых операндов и результатов 22, в векторах вторых операндов 23 и векторах третьих операндов 24, первый 25 и второй 26 входы управления загрузкой векторов третьих операндов в первый блок памяти, вход управления пересылкой матрицы третьих операндов из первого блока памяти во второй блок памяти 27 и выходы разрядов вектора первых 28 и вектора вторых 29 слагаемых результатов операции сложения вектора первых операндов с произведением вектора вторых операндов на матрицу третьих операндов, хранящуюся во втором блоке памяти, и сумматор 30, имеющий входы разрядов вектора первых 31 и вектора вторых 32 слагаемых, входы установки границ данных в векторах слагаемых и сумм 33 и выходы разрядов вектора сумм 34. Нейропроцессор имеет первую 35 и вторую 36 входные шины и выходную шину 37. Управляющие входы 38 коммутатора с трех направлений в два 11, управляющий вход 39 мультиплексора 12, управляющий вход 40 первого регистра 1, управляющий вход 41 второго регистра 2, управляющий вход 42 третьего регистра 3, управляющий вход 43 четвертого регистра 4, вход управления записью 44 сдвигового регистра 7, вход управления записью 45 первого блока памяти магазинного типа 9, входы управления записью 46 и чтением 47 второго блока памяти магазинного типа 10 и указанные выше управляющие входы 26 и 27 вычислительного устройства 18 являются соответствующими управляющими входами нейропроцессора. Выходы состояния 48 первого блока памяти магазинного типа 9 и выходы состояния 49 второго блока памяти магазинного типа 10 являются выходами состояния нейропроцессора.

Первые информационные входы разрядов коммутатора с трех направлений в два 11, информационные входы первого блока памяти магазинного типа 9, первого 1, второго 2, третьего 3 и четвертого 4 регистров и параллельные информационные входы сдвигового регистра 7 поразрядно объединены и подключены к первой входной шине 35 нейропроцессора, разряды второй входной шины 36 которого соединены с вторыми информационными входами соответствующих разрядов коммутатора с трех направлений в два 11. Первые выходы разрядов коммутатора с трех направлений в два 11 соединены с входами соответствующих разрядов вектора входных операндов 15 первого устройства для вычисления функций насыщения 13, управляющие входы 16 разрядов которого соединены с выходами соответствующих разрядов второго регистра 2. Вторые выходы разрядов коммутатора с трех направлений в два 11 соединены с входами соответствующих разрядов вектора входных операндов 15 второго устройства для вычисления функций насыщения 14, управляющие входы 16 разрядов которого соединены с выходами соответствующих разрядов третьего регистра 3. Выходы разрядов первого регистра 1 соединены с первыми информационными входами соответствующих разрядов мультиплексора 12, вторые информационные входы разрядов которого соединены с выходами соответствующих разрядов вектора результатов 17 первого устройства для вычисления функций насыщения 13. Выходы разрядов мультиплексора 12 соединены с входами соответствующих разрядов вектора первых операндов 19 вычислительного устройства 18, входы разрядов вектора вторых операндов 20 которого соединены с выходами соответствующих разрядов вектора результатов 17 второго устройства для вычисления функций насыщения 14. Информационные выходы первого блока памяти магазинного типа 9 соединены с входами соответствующих разрядов вектора третьих операндов 21 вычислительного устройства 18, выходы разрядов вектора первых слагаемых результатов 28 которого соединены с входами соответствующих разрядов вектора первых слагаемых 31 сумматора 30, входы разрядов вектора вторых слагаемых 32 которого соединены с выходами соответствующих разрядов вектора вторых слагаемых результатов 29 вычислительного устройства 18, входы установки границ данных в векторах первых операндов и результатов 22 которого соединены с выходами соответствующих разрядов пятого регистра 5 и соответствующими входами установки границ данных в векторах слагаемых и сумм 33 сумматора 30, выходы разрядов вектора сумм 34 которого соединены с соответствующими информационными входами второго блока памяти магазинного типа 10, информационные выходы которого подключены к соответствующим разрядам выходной шины 37 нейропроцессора и соединены с третьими входами соответствующих разрядов коммутатора с трех направлений в два 11. Выходы разрядов четвертого регистра 4 соединены с информационными входами соответствующих разрядов пятого регистра 5 и соответствующими входами установки границ данных в векторах третьих операндов 24 вычислительного устройства 18, входы установки границ данных в векторах вторых операндов 23 которого соединены с выходами соответствующих разрядов шестого регистра 6, информационные входы которого соединены с выходами соответствующих разрядов сдвигового регистра 7, последовательные информационные вход и выход которого объединены и подключены к первому входу управления загрузкой векторов третьих операндов в первый блок памяти 25 вычислительного устройства 18 и первому входу элемента И 8, выход которого соединен с входом управления чтением первого блока памяти магазинного типа 9. Вход управления сдвигом сдвигового регистра 7 соединен с вторым входом элемента И 8 и вторым входом управления загрузкой векторов третьих операндов в первый блок памяти 26 вычислительного устройства 18, вход управления пересылкой матрицы третьих операндов из первого блока памяти во второй блок памяти 27 которого соединен с управляющими входами пятого 5 и шестого 6 регистров.

Нейропроцессор работает следующим образом.

Исполнительными узлами нейропроцессора являются первое 13 и второе 14 устройства для вычисления функций насыщения, вычислительное устройство 18 и сумматор 30. Каждое из этих устройств выполняет операции над векторами данных программируемой разрядности, представленных в дополнительном коде.

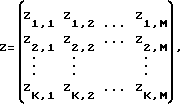

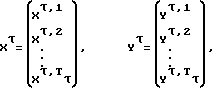

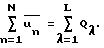

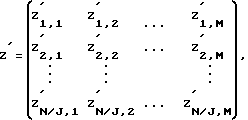

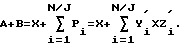

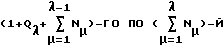

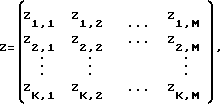

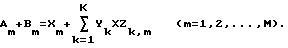

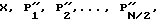

В каждом такте работы нейропроцессора вычислительное устройство 18 формирует двухрядный код результата операции умножения вектора Y = (Y1 Y2 .. . Yk), разряды которого подаются на входы 20 вычислительного устройства 18, на матрицу

предварительно загруженную и хранящуюся во втором блоке памяти вычислительного устройства 18, с прибавлением к полученному произведению вектора X = (X1 X2 ... XM), разряды которого подаются на входы 19 вычислительного устройства 18. При этом на выходах 28 и 29 вычислительного устройства 18 формируются разряды векторов A = (A1 A2 ... AM) и B = (B1 B2 ... BM), сумма которых является результатом операции X + Y • Z. То есть сумма m-х элементов векторов A и B определяется выражением (m=1,2,...,M)

(m=1,2,...,M)

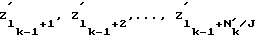

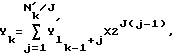

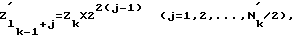

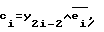

Вектор X представляет собой N-разрядное слово, в котором упаковано M данных, представленных в дополнительном коде и являющихся элементами этого вектора. При этом младшие разряды вектора X являются разрядами первого данного X1, далее следуют разряды второго данного X2 и т.д. Старшие разряды вектора X являются разрядами M-го данного XM. При такой упаковке ν- разряд m-го данного Xm является

разрядом вектора X, где Nm - разрядность m-го данного Xm вектора X, ν=1,2,...,Nm, m=1,2,...,M. Количество данных M в векторе X и количество разрядов Nm в m-м данном Xm этого вектора могут принимать любые целочисленные значения от 1 до N, где m=1,2,...,M. Единственное ограничение заключается в том, что суммарная разрядность всех данных, упакованных в одном векторе X, должна быть равна его разрядности

Вектор Y представляет собой N-разрядное слово, в котором упаковано K данных, представленных в дополнительном коде и являющихся элементами этого вектора. Формат вектора Y аналогичен формату вектора X. Однако данные векторы могут различаться количеством и разрядностью отдельных данных, упакованных в этих векторах. Минимальная разрядность J каждого данного, упакованного в векторе Y, определяется схемотехнической реализацией операции умножения в вычислительном устройстве 18. При реализации алгоритма частичных произведений J равно 1, при реализации модифицированного алгоритма Бута J равно 2. Количество разрядов N

k-я строка матрицы Z представляет собой вектор данных Zk=(Zk,1 Zk,2 ... Zk,M), где k= 1,2, ...,K. Причем каждый из векторов Z1, Z2, ..., ZK должен иметь точно такой же формат, что и вектор X.

Векторы A и B, формируемые на выходах 28 и 29 вычислительного устройства 18, имеют точно такой же формат, что и вектор X.

Настройка аппаратуры вычислительного устройства 18 на обработку векторов требуемых форматов осуществляется путем загрузки N-разрядного управляющего слова H в пятый регистр 5, выходы которого подключены к входам 22 вычислительного устройства 18, и (N/J)-разрядного управляющего слова E в шестой регистр 6, выходы которого подключены к входам 23 вычислительного устройства 18.

Единичное значение n-го разряда hn слова H означает, что вычислительное устройство 18 будет рассматривать n-й разряд каждого из векторов X, Z1, Z2, ..., ZK, как старший (знаковый) разряд соответствующего элемента данного вектора. Количество единичных битов в слове H равно количеству элементов в каждом из векторов X, Z1, Z2, ..., ZK

Единичное значение i-го разряда ei, слова E означает, что вычислительное устройство 18 будет рассматривать i-ю J-разрядную группу разрядов вектора Y, как группу младших разрядов соответствующего элемента данного вектора. Количество единичных битов в слове E равно количеству элементов в векторе Y

Выполнению вычислительным устройством 18 описанной выше операции должна предшествовать процедура загрузки матрицы Z во второй блок памяти вычислительного устройства 18 и управляющих слов H и E в пятый 5 и шестой 6 регистры соответственно. Данная процедура выполняется в несколько этапов.

Первоначально в первый блок памяти магазинного типа 9 с первой входной шины 35 нейропроцессора последовательно записываются векторы Z1, Z2, ..., ZK. Загрузка всей матрицы Z в первый блок памяти магазинного типа 9 выполняется за K процессорных тактов, в каждом из которых на вход 45 нейропроцессора подается активный сигнал управления записью в первый блок памяти магазинного типа 9.

Затем в четвертый регистр 4 с первой входной шины 35 нейропроцессора загружается управляющее слово H, для чего на вход 43 нейропроцессора в течение одного такта подается активный сигнал, разрешающий запись в четвертый регистр 4. В следующем такте в сдвиговый регистр 7 с первой входной шины 35 нейропроцессора загружается управляющее слово E, для чего на вход 44 нейропроцессора в течение одного такта подается активный сигнал, разрешающий запись в сдвиговый регистр 7.

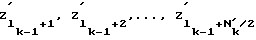

В течение следующих N/J тактов матрица Z пересылается из первого блока памяти магазинного типа 9 в первый блок памяти вычислительного устройства 18. В каждом из этих N/J тактов на управляющий вход нейропроцессора, подключенный к входу управления сдвигом сдвигового регистра 7, одному из входов элемента И 8 и входу 26 вычислительного устройства 18, подается активный управляющий сигнал. В каждом такте данный сигнал инициирует сдвиг содержимого сдвигового регистра 7 на один разряд вправо и, как следствие, выдачу на его последовательный выход очередного разряда управляющего слова E. Сигнал с последовательного выхода сдвигового регистра поступает на управляющий вход 25 вычислительного устройства 18 и на один из входов элемента И 8. При единичном значении данного сигнала на выходе элемента И 8 формируется активный сигнал, поступающий на вход управления чтением первого блока памяти магазинного типа 9. В результате на входы 21 вычислительного устройства 18 из первого блока памяти магазинного типа 9 поступает один из векторов Z1, Z2, . .., ZK, который записывается в первый блок памяти вычислительного устройства 18. Количество тактов, необходимых для загрузки одного вектора Zk, зависит от разрядности N

После этого на управляющий вход нейропроцессора, подключенный к управляющему входу 27 вычислительного устройства 18 и управляющим входам пятого 5 и шестого 6 регистров, подается активный сигнал. В результате этого за один такт матрица Z пересылается из первого блока во второй блок памяти вычислительного устройства 18, управляющее слово H переписывается из четвертого регистра 4 в пятый регистр 5, а управляющее слово E переписывается из сдвигового регистра 7 в шестой регистр 6.

Начиная со следующего такта вычислительное устройство 18 будет в каждом такте выполнять описанную выше операцию

A + B = X + Y • Z.

Сумматор 30 осуществляет в каждом такте сложение векторов A и B, поступающих на его входы 31 и 32 с выходов 28 и 29 вычислительного устройства 18. При этом на выходах 34 сумматора 30 формируется вектор S = (S1 S2 ... SM), m-й элемент которого равен сумме m-х элементов векторов A и B

Sm = Am + Bm,

где m=1,2,...,M

Причем вектор S будет иметь такой же формат, что и векторы A и B. Настройка аппаратуры сумматора 30 на обработку векторов требуемых форматов обеспечивается путем подачи на входы 33 сумматора 30 управляющего слова H, хранящегося в пятом регистре 5.

Таким образом, последовательное включение вычислительного устройства 18 и сумматора 30 позволяет в каждом такте выполнять операцию S = X + Y • Z над векторами данных программируемой разрядности. Результаты выполнения данной операции над различными наборами векторов входных операндов записываются во второй блок памяти магазинного типа 10, выполняющий функции аккумулятора промежуточных результатов, для чего на вход 46 нейропроцессора подается сигнал разрешения записи во второй блок памяти магазинного типа 10.

Вычислительное устройство 18 и сумматор 30 могут использоваться в качестве однотактного коммутатора K данных, упакованных в одном N-разрядном векторе Y, подаваемом на входы 20 вычислительного устройства 18, в M данных, упакованных в одном N-разрядном векторе S, формируемом на выходах 34 сумматора 30. Такая коммутация осуществляется путем выполнения операции S = X + Y • Z, при которой на входы 19 вычислительного устройства 18 подается вектор X, все разряды которого имеют нулевые значения, а во втором блоке памяти вычислительного устройства 18 хранится матрица Z, определяющая правила коммутации. При этом матрица Z должна удовлетворять следующим требованиям: элемент Zk,m, находящийся на пересечении k-й строки и m-го столбца матрицы Z, должен иметь единичное значение (00... 01)b, если требуется, чтобы m-й элемент Sm вектора S был равен k-му элементу Yk вектора Y, или нулевое значение (00. . . 00)b в противном случае; вектор Zk, представляющий собой k-ю строку элементов матрицы Z, должен иметь такой же формат, что и вектор S; а каждый столбец матрицы Z должен содержать не более одного элемента, имеющего единичное значение (k=1,2,...,K; m=1,2,...,M). Выполнению операции коммутации должна предшествовать описанная выше процедура загрузки управляющего слова H, определяющего требуемый формат вектора S, в пятый регистр 5, управляющего слова E, определяющего требуемый формат вектора Y, в шестой регистр 6 и матрицы Z, определяющей правила коммутации, во второй блок памяти вычислительного устройства 18.

Операция S = X + Y • Z выполняется за один такт, в то время как процесс загрузки матрицы Z в первый блок памяти вычислительного устройства 18 занимает не менее N/J тактов. Поэтому эффективное использование вычислительных ресурсов нейропроцессора достигается только при пакетной обработке векторов данных, для поддержки которой в вычислительное устройство 18 введен второй блок памяти, а в качестве аккумулятора промежуточных результатов 10 используется не регистр, а двухпортовый блок памяти магазинного типа.

При пакетной обработке множество векторов входных операндов, подаваемых последовательно на каждый из входов 19 и 20 вычислительного устройства 18, разбивается на последовательно обрабатываемые подмножества (пакеты). Совокупность векторов входных операндов, последовательно подаваемых на каждый из входов 19 и 20 вычислительного устройства 18 и входящих в τ-пакет, можно представить в виде вектора векторов данных

где Tτ - количество векторов, входящих в состав каждого τ-го пакета. Причем все векторы, входящие в состав одного пакета, должны иметь одинаковый формат, то есть содержимое пятого 5 и шестого 6 регистров в процессе обработки одного пакета векторов не должно измеряться.

Обработка τ-х пакетов Xτ и Yτ выполняется за Tτ тактов. При этом в t-м такте вычислительное устройство 18 и сумматор 30 выполняют операцию

Sτ,t=Xτ,t+Yτ,t•Zτ (t=1,2,...Tτ),

где Zτ - содержимое второго блока памяти вычислительного устройства 18, которое в процессе обработки τ -х пакетов Xτ и Yτ должно оставаться неизменным. Весь процесс обработки τ -х пакетов Xτ и Yτ можно рассматривать как процедуру умножения матрицы данных  на матрицу данных Zτ с накоплением результатов.

на матрицу данных Zτ с накоплением результатов.

Одновременно с обработкой τ -х пакетов векторов выполняется описанная выше процедура последовательной загрузки управляющего слова Hτ+1, определяющего формат векторов (τ+1)-го пакета Xτ+1, в четвертый регистр 4, управляющего слова Eτ+1, определяющего формат векторов (τ+1)-го пакета Yτ+1, в сдвиговый регистр 7 и пересылки матрицы Zτ+1 из первого блока памяти магазинного типа 9 в первый блок памяти вычислительного устройства 18. Причем загрузка новых значений в четвертый регистр 4 требуется только в том случае, если векторы (τ+1)-го пакета Xτ+1 отличаются по формату от векторов τ- -го пакета Xτ, а загрузка новых значений в сдвиговый регистр 7 требуется только в том случае, если векторы (τ+1)-го пакета Yτ+1 отличаются по формату от векторов τ-го пакета Yτ. Данная процедура выполняется не более чем за N/J+2 тактов.

По окончании обоих указанных процессов на управляющий вход 27 нейропроцессора подается активный сигнал, инициирующий одновременную пересылку слова Hτ+1 из четвертого регистра 4 в пятый регистр 5, слова Eτ+1 из сдвигового регистра 7 в шестой регистр 6, и матрицы Zτ+1 из первого во второй блок памяти вычислительного устройства 18. Все указанные пересылки выполняются за один такт.

Количество векторов Tτ в каждом τ-м пакете может задаваться программно, но не должно превышать величины Tmax, которая равна количеству ячеек во втором блоке памяти магазинного типа 10. С другой стороны, нецелесообразно использовать пакеты векторов с Tτ меньшим, чем N/J+2, так как при этом будут простаивать вычислительные средства нейропроцессора.

Одновременно с пересылкой матрицы Zτ+1 из первого блока памяти магазинного типа 9 в первый блок памяти вычислительного устройства 18 может выполняться последовательная загрузка с первой входной шины 35 нейропроцессора векторов третьих операндов, составляющих матрицы Zτ+2, Zτ+3 и т.д., в первый блок памяти магазинного типа 9.

Синхронизация всех одновременно протекающих процессов осуществляется путем анализа сигналов состояния первого 9 и второго 10 блоков памяти магазинного типа, выдаваемых на выходы 48 и 49 нейропроцессора, и подачи управляющих сигналов на соответствующие входы нейропроцессора.

Коммутатор с трех направлений в два 11 и мультиплексор 12 образуют систему коммутации, благодаря которой, как на входы вектора первых операндов 19, так и на входы вектора вторых операндов 20 вычислительного устройства 18, может подаваться содержимое второго блока памяти магазинного типа 10 или информация, поступающая по одной из входных шин 35 или 36 нейропроцессора. Кроме того, на входы 19 вычислительного устройства 18 может подаваться содержимое регистра 1, предварительно записанное в него с первой входной шины 35 нейропроцессора путем подачи активного сигнала на управляющий вход 40 нейропроцессора. Выбор источников информации, поступающей на входы 19 и 20 вычислительного устройства 18, осуществляется подачей определенной комбинации сигналов на управляющие входы 38 и 39 нейропроцессора. Причем, если источником информации является второй блок памяти магазинного типа 10, на управляющий вход 47 нейропроцессора необходимо подать сигнал разрешения чтения из второго блока памяти магазинного типа 10.

Векторы данных, подаваемые на входы 19 и 20 вычислительного устройства 18 из второго блока памяти магазинного типа 10 или с одной из входных шин 35 или 36 нейропроцессора, проходят через устройства для вычисления функций насыщения 13 и 14. Каждое из устройств 13 и 14 вычисляет за один такт функцию насыщения от каждого элемента вектора D = (D1 D2 ... DL), поступающего на входы 15 данного устройства.

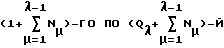

Вектор D представляет собой N-разрядное слово, в котором упаковано L данных, представленных в дополнительном коде и являющихся элементами этого вектора. Формат вектора D аналогичен формату описанного выше вектора X. Однако, данные векторы могут различаться количеством и разрядностью отдельных данных, упакованных в этих векторах. Минимальная разрядность данных, составляющих вектор D, равна двум. Количество данных L в векторе D может принимать любые целочисленные значения от 1 до N/2. Однако, суммарная разрядность всех данных, упакованных в одном векторе D, должна быть равна его разрядности

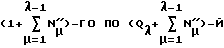

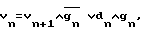

На выходах 17 устройства для вычисления функций насыщения 13 или 14 формируется вектор F = (F1 F2 ... FL), который имеет точно такой же формат, что и вектор D. Причем λ-й элемент Fλ вектора F является результатом вычисления функции насыщения от λ -го операнда Dλ вектора D

где Qλ - параметр функции насыщения, вычисляемой для операнда Dλ(λ=1,2,...,L). Общий вид функций насыщения, вычисляемых устройствами 13 и 14, представлен на фиг.2 и описывается следующими выражениями: ΨQ(D)=D, если -2Q≤D≤2Q - 1; YQ(D) = 2Q - 1, если D>2Q - 1; YQ(D) = -2Q, если D<-2Q.

Количество значащих бит в элементе Fλ вектора F без учета знакового разряда равно значению параметра Qλ(λ=1,2,...,L). Очевидно, что значение Qλ должно быть меньше разрядности  операндов Dλ и Fλ.

операндов Dλ и Fλ.

Настройка аппаратуры каждого из устройств для вычисления функций насыщения 13 или 14 на требуемый формат векторов D и F, а также на требуемые значения параметров реализуемых функций насыщения, осуществляется путем подачи N-разрядного управляющего слова U на управляющие входы 16 данного устройства.

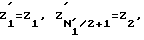

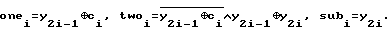

При этом разряды слова U должны иметь следующие значения: разряды с первого по (Q1)-й - нулевые, разряды с (Q1+1)-го по  - единичные, разряды с

- единичные, разряды с  нулевые, разряды c

нулевые, разряды c  единичные и т.д. В общем случае разряды слова U с

единичные и т.д. В общем случае разряды слова U с

должны иметь нулевые значения, а разряды c

единичные значения (λ=1,2,...,L).

Если значение n-го разряда слова U равно единице (Un=1), а значение (n+1)-го разряда равно нулю (Un+1=0), то устройство для вычисления функций насыщения 13 или 14 будет рассматривать n-й разряд вектора D, как старший (знаковый) разряд соответствующего элемента данного вектора. Количество нулевых битов в слове U равно суммарному числу значащих бит во всех элементах вектора результатов F

Если U= (100...0)b, то информация с входов 15 устройства для вычисления функций насыщения 13 или 14 будет проходить на его выходы 17 без изменения (F=D).

Управляющее слово первого устройства для вычисления функций насыщения 13 загружается с первой входной шины 35 нейропроцессора во второй регистр 2, выходы которого соединены с управляющими входами 16 устройства для вычисления функций насыщения 13. Данная загрузка выполняется за один такт путем подачи активного сигнала на управляющий вход 41 второго регистра 2.

Управляющее слово второго устройства для вычисления функций насыщения 14 загружается с первой входной шины 35 нейропроцессора в третий регистр 3, выходы которого соединены с управляющими входами 16 устройства для вычисления функций насыщения 14. Данная загрузка выполняется за один такт путем подачи активного сигнала на управляющий вход 42 третьего регистра 3.

Устройства для вычисления функций насыщения 13 и 14 являются эффективным средством для предотвращения арифметических переполнений при обработке векторов входных операндов.

Каждое из устройств для вычисления функций насыщения 13 или 14 позволяет уменьшить только количество значащих разрядов в элементах обрабатываемого вектора данных. Разрядность отдельных элементов вектора данных и его формат

остаются без изменений. Вместе с тем, в ряде случаев целесообразно выполнить вычисление функций насыщения для элементов вектора данных с уменьшением разрядности каждого элемента вектора результатов путем отбрасывания всех его старших разрядов, которые являются расширением знакового разряда данного элемента. Такое уменьшение разрядности элементов вектора F = (F1 F2. . . FL), сформированного на выходах 17 устройства для вычисления функций насыщения 14, и связанная с ним переупаковка элементов в векторе могут быть выполнены за один такт с помощью вычислительного устройства 18 и сумматора 30, работающих в режиме коммутатора данных с 2L направлений в L+1. В качестве примера ниже приводится описание операции преобразования вектора F в формируемый на выходах 34 сумматора 30 вектор S = (S1 S2... SL+1), у которого λ -й элемент Sλ представляет собой Qλ+1 младших (значащих) разрядов λ -го элемента Fλ вектора F (λ=1,2,...,L), a (L+1)-й элемент SL+1, расположенный в старших разрядах вектора S, равен (00...0)b. Вектор F, формируемый на выходах 17 устройства для вычисления функций насыщения 14, можно представить в виде поступающего на входы 20 вычислительного устройства 18 вектора Y = (Y1 Y2. . . Y2L), у которого первый Y2λ-1 и второй Y2λ элементы λ -й пары элементов представляют собой соответственно Qλ+1 младших и  старших разрядов λ -го

старших разрядов λ -го  разрядного элемента Fλ вектора F (λ=1,2,...,L). В режиме коммутации данных на входы 19 вычислительного устройства 18 подаются нулевые значения, в результате чего на выходах 34 сумматора 30 формируется результат операции умножения вектора Y на матрицу Z, хранящуюся во втором блоке памяти вычислительного устройства 18. Данный результат будет представлять собой вектор S требуемого формата, если в пятом регистре 5 хранится управляющее слово H, определяющее описанный выше формат вектора S, в шестом регистре 6 - управляющее слово E, определяющее описанный выше формат вектора Y, а во втором блоке памяти вычислительного устройства 18 - матрица Z, содержащая по L+1 элементов в каждой из 2L строк. Причем матрица Z должна удовлетворять следующим требованиям: разрядность каждого элемента λ -го столбца матрицы Z должна быть равна Qλ+1; элемент Z2λ-1,λ, находящийся на пересечении (2λ-1)-й строки и λ -гo столбца матрицы Z, должен иметь единичное значение (00... 01)b, а остальные элементы матрицы Z - нулевые значения (00...00)b (λ=1,2,...,L).

разрядного элемента Fλ вектора F (λ=1,2,...,L). В режиме коммутации данных на входы 19 вычислительного устройства 18 подаются нулевые значения, в результате чего на выходах 34 сумматора 30 формируется результат операции умножения вектора Y на матрицу Z, хранящуюся во втором блоке памяти вычислительного устройства 18. Данный результат будет представлять собой вектор S требуемого формата, если в пятом регистре 5 хранится управляющее слово H, определяющее описанный выше формат вектора S, в шестом регистре 6 - управляющее слово E, определяющее описанный выше формат вектора Y, а во втором блоке памяти вычислительного устройства 18 - матрица Z, содержащая по L+1 элементов в каждой из 2L строк. Причем матрица Z должна удовлетворять следующим требованиям: разрядность каждого элемента λ -го столбца матрицы Z должна быть равна Qλ+1; элемент Z2λ-1,λ, находящийся на пересечении (2λ-1)-й строки и λ -гo столбца матрицы Z, должен иметь единичное значение (00... 01)b, а остальные элементы матрицы Z - нулевые значения (00...00)b (λ=1,2,...,L).

Если при выполнении описанной выше операции по преобразованию вектора F, формируемого на выходах 17 устройства для вычисления функций насыщения 14, на входы 19 вычислительного устройства 18 подать вектор X = (X1 X2 ... XM+1), первый элемент X1 которого равен нулю и имеет разрядность, равную

то на выходах 34 сумматора 30 будет сформирован вектор S = (S1 S2 ... SL+M), у которого λ -й элемент Sλ представляет собой Qλ+1 младших (значащих) разрядов λ -го, элемента Fλ вектора F (λ=1,2,...,L), a (L+m)-й элемент равен (m+1)-му элементу Xm+1 вектора X (m=1,2,...,M). Таким образом, нейропроцессор позволяет за один такт выполнить операцию по вычислению функций насыщения над элементами вектора входных данных и упаковать полученный результат в другой вектор входных данных.

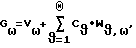

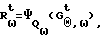

Основное назначение нейропроцессора - это эмуляция всевозможных нейронных сетей. На фиг. 3 представлена модель слоя нейронной сети, реализуемой предлагаемым нейропроцессором. В общем случае один слой нейронной сети состоит из Ω нейронов и имеет Θ нейронных входов. При этом ω -й нейрон выполняет взвешенное суммирование Θ данных C1, C2,...,  подаваемых на соответствующие нейронные входы, с учетом порогового смещения Vω данного нейрона

подаваемых на соответствующие нейронные входы, с учетом порогового смещения Vω данного нейрона

где Wϑ,ω - весовой коэффициент ϑ -го входа в ω -м нейроне (ϑ=1,2,...,Θ; ω=1,2,...,Ω). Затем ω -й нейрон вычисляет функцию насыщения  от результата взвешенного суммирования Gω

от результата взвешенного суммирования Gω

Общий вид функций насыщения, реализуемых нейропроцессором, представлен на фиг.2. Все входные данные, весовые коэффициенты, пороговые значения и результаты представляются в дополнительном коде.

Специфика предлагаемого нейропроцессора заключается в том, что при его использовании пользователь может программно задавать следующие параметры нейронной сети: число слоев, число нейронов и нейронных входов в каждом слое, разрядность данных на каждом нейронном входе, разрядность каждого весового коэффициента, разрядность выходного значения каждого нейрона, параметр функции насыщения для каждого нейрона.

Один нейропроцессор позволяет эмулировать нейронную сеть практически неограниченных размеров. Эмуляция нейронной сети осуществляется послойно (последовательно слой за слоем).

Каждый слой нейронной сети разбивается на последовательно обрабатываемые фрагменты. Данное разбиение осуществляется следующим образом. Множество нейронных входов слоя разбивается на группы входов так, чтобы суммарная разрядность данных, подаваемых на все входы каждой группы входов, была равна разрядности нейропроцессора N. Множество нейронов слоя разбивается на группы нейронов так, чтобы суммарная разрядность результатов взвешенного суммирования всех входных данных для каждой группы нейронов была равна разрядности нейропроцессора N. При этом весь слой нейронной сети разбивается на фрагменты двух типов, имеющих различное функциональное назначение. Каждый фрагмент первого типа выполняет взвешенное суммирование данных, которые подаются на все нейронные входы, входящие в состав одной группы входов, для всех нейронов, входящих в состав одной группы нейронов. Каждый фрагмент второго типа формирует выходные значения для всех нейронов, входящих в состав одной группы нейронов, путем вычисления функции насыщения от результатов взвешенного суммирования всех входных данных.

Фиг.3 можно использовать в качестве иллюстрации описанного выше принципа разбиения слоя нейронной сети на фрагменты. Для этого необходимо представить, что каждый блок, приведенный на фиг.3, выполняет операции над N-разрядными векторами данных, и трактовать приведенные на фиг. 3 обозначения следующим образом: Cϑ - вектор входных данных, подаваемых на ϑ -ю группу нейронных входов (ϑ=1,2,...,Θ); Vω - вектор пороговых значений ω -й группы нейронов (ω=1,2,...,Ω); Wϑ,ω - матрица весовых коэффициентов входных данных, подаваемых на ϑ -ю группу нейронных входов, в ω -й группе нейронов (ϑ=1,2,...,Θ; ω=1,2,...,Ω); Gω - вектор результатов взвешенного суммирования входных данных в ω -й группе нейронов (ω=1,2,...Ω); Rω - вектор выходных значений ω -й группы нейронов (ω=1,2,...Ω).

При этом на фиг. 3 каждому фрагменту первого типа соответствует пара устройств, выполняющих умножение и сложение, а каждому фрагменту второго типа соответствует одно устройство вычисления функций насыщения.

Весь процесс эмуляции слоя нейронной сети на одном нейропроцессоре можно представить в виде Ω последовательно выполняемых процедур, каждая из которых осуществляет эмуляцию одной группы нейронов и состоит из Θ+1 последовательно выполняемых макроопераций, каждая из которых эмулирует один фрагмент слоя нейронной сети. Причем ϑ -я макрооперация данной процедуры осуществляет эмуляцию фрагмента первого типа, выполняющего взвешенное суммирование данных, подаваемых на ϑ -ю группу нейронных входов, с накоплением результата (ϑ=1,2,...,Θ). Последняя макрооперация процедуры эмулирует фрагмент второго типа, выполняющий вычисление функций насыщения от взвешенной суммы данных, подаваемых на все нейронные входы, для соответствующей группы нейронов.

Каждая макрооперация, выполняемая в процессе эмуляции слоя нейронной сети, имеет подготовительную и исполнительные фазы. Обработка данных, подаваемых на нейронные входы, ведется в пакетном режиме - по T наборов входных данных в каждом пакете.

В течение подготовительной фазы первой макрооперации процедуры эмуляции ω -й группы нейронов последовательно выполняются следующие операции. С первой входной шины 35 нейропроцессора в первый регистр 1 загружается вектор Vω. С первой входной шины 35 нейропроцессора в четвертый регистр 4 загружается управляющее слово, определяющее формат вектора Vω и всех векторов частичных сумм, формируемых в результате выполнения каждой ϑ -й макрооперации (ϑ=1,2,...,Θ). С первой входной шины 35 нейропроцессора в сдвиговый регистр 7 загружается управляющее слово, определяющее формат векторов данных, подаваемых на первую группу нейронных входов. Матрица W1,ω пересылается из первого блока памяти магазинного типа 9, куда данная матрица должна быть предварительно загружена с первой входной шины 35 нейропроцессора, в первый блок памяти вычислительного устройства 18.

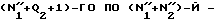

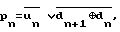

В течение каждого t-го такта исполнительной фазы первой макрооперации процедуры эмуляции ω -й группы нейронов на входы вектора первых операндов 19 вычислительного устройства 18 из первого регистра 1 поступает вектор Vω, а на входы вектора вторых операндов 20 вычислительного устройства 18 с второй входной шины 36 нейропроцессора поступает вектор C

G

который записывается во второй блок памяти магазинного типа 10. Причем, начиная с процедуры эмуляции второй группы нейронов, одновременно с данной операцией в каждом такте будет выполняться пересылка содержимого одной из ячеек второго блока памяти магазинного типа 10 во внешнюю память через выходную шину 37 нейропроцессора.

В течение подготовительной фазы θ -й макрооперации  процедуры эмуляции ω -й группы нейронов последовательно выполняются следующие операции. С первой входной шины 35 нейропроцессора в сдвиговый регистр 7 загружается управляющее слово, определяющее формат векторов данных, подаваемых на θ -ю группу нейронных входов. Матрица Wθ,ω пересылается из первого блока памяти магазинного типа 9, куда данная матрица должна быть предварительно загружена с первой входной шины 35 нейропроцессора, в первый блок памяти вычислительного устройства 18.

процедуры эмуляции ω -й группы нейронов последовательно выполняются следующие операции. С первой входной шины 35 нейропроцессора в сдвиговый регистр 7 загружается управляющее слово, определяющее формат векторов данных, подаваемых на θ -ю группу нейронных входов. Матрица Wθ,ω пересылается из первого блока памяти магазинного типа 9, куда данная матрица должна быть предварительно загружена с первой входной шины 35 нейропроцессора, в первый блок памяти вычислительного устройства 18.

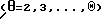

В течение каждого t-го такта исполнительной фазы θ -й макрооперации (θ=2,3,...Θ) процедуры эмуляции ω -й группы нейронов на входы вектора первых операндов 19 вычислительного устройства 18 из второго блока памяти магазинного

типа 10 поступает вектор частичных сумм G

G

который записывается во второй блок памяти магазинного типа 10.

При выполнении Θ первых макроопераций каждой процедуры эмуляции группы нейронов устройство для вычисления функций насыщения 13 может использоваться для ограничения значений частичных сумм с целью исключения возможности арифметического переполнения при взвешенном суммировании входных данных. В этом случае подготовительная фаза макроопераций должна включать загрузку управляющего слова во второй регистр 2 с первой входной шины 35 нейропроцессора.

В течение подготовительной фазы (Θ+1)-й макрооперации процедуры эмуляции ω-й группы нейронов последовательно выполняются следующие операции. С первой входной шины 35 нейропроцессора в третий регистр 3 загружается управляющее слово, определяющее параметры функций насыщения, вычисляемых для ω-й группы нейронов. Затем в четвертый регистр 4, сдвиговый регистр 7 и в первый блок памяти вычислительного устройства 18 загружается управляющая информация, необходимая для выполнения операции по сжатию и упаковке результатов вычисления функций насыщения.

В течение каждого t-го такта исполнительной фазы (Θ+1)-й макрооперации процедуры эмуляции ω-й группы нейронов на входы 15 устройства для вычисления функций насыщения 14 из второго блока памяти магазинного типа 10 поступает вектор частичных сумм G

который затем поступает на входы 20 вычислительного устройства 18. Вычислительное устройство 18 и сумматор 30 осуществляют сжатие вектора R

При выполнении любой макрооперации по эмуляции фрагмента слоя нейронной сети переход от подготовительной фазы к исполнительной осуществляется путем подачи активного сигнала на управляющий вход 27 нейропроцессора в течение одного такта, предшествующего первому такту исполнительной фазы. При этом содержимое четвертого регистра 4 переписывается в пятый регистр 5, содержимое сдвигового регистра 7 переписывается в шестой регистр 6, а содержимое первого блока памяти вычислительного устройства 18 пересылается в его второй блок памяти.

Последовательное выполнение макроопераций осуществляется нейропроцессором в конвейерном режиме, при котором исполнительная фаза очередной макрооперации выполняется одновременно с подготовительной фазой следующей макрооперации. Количество тактов, необходимых для выполнения всех операций подготовительной фазы макрооперации, колеблется в диапазоне от N/J до N/J+4 в зависимости от количества управляющих слов, загружаемых в регистры нейропроцессора. Количество тактов, необходимых для выполнения исполнительной фазы любой макрооперации, равно количеству обрабатываемых наборов входных данных T, которое задается пользователем. Таким образом, минимальный период выполнения макрооперации определяется длительностью подготовительной фазы и равен длительности N/J процессорных тактов. Значение T целесообразно выбирать равным N/J, так как при меньших значениях T будут простаивать исполнительные узлы нейропроцессора, а при больших значениях T возрастает время реакции нейропроцессора на очередной набор данных на нейронных входах, что нежелательно при эмуляции нейронных сетей реального масштаба времени.

В общем случае процесс эмуляции слоя нейронной сети, разбиваемого на Ω×(Θ+1) фрагментов, для T наборов входных данных выполняется на одном нейропроцессоре за Ω×(Θ+1)×T тактов, но не менее, чем за Ω×(Θ+1)×N/J тактов.

Небольшой слой нейронной сети, у которого суммарная разрядность данных, подаваемых на все нейронные входы, и суммарная разрядность результатов взвешенного суммирования для всех нейронов не превышают разрядности нейропроцессора N каждая, эмулируется путем выполнения двух макроопераций. Первая макрооперация эмулирует взвешенное суммирование всех входных данных для всех нейронов слоя, а вторая - вычисление функций насыщения для всех нейронов слоя.

Наличие в нейропроцессоре двух входных 35 и 36 и одной выходной 37 шин позволяет создавать на его основе эффективно работающие мультипроцессорные системы. Система, состоящая из Ξ нейропроцессоров, будет выполнять эмуляцию слоя нейронной сети в Ξ раз быстрее, чем один нейропроцессор. В предельном случае каждый фрагмент каждого слоя нейронной сети может эмулироваться отдельным нейропроцессором.

Основным узлом нейропроцессора является вычислительное устройство 18. На фиг.4 приведена блок-схема одной из возможных реализаций вычислительного устройства 18 для выполнения операций над векторами данных программируемой разрядности, содержащего сдвиговый регистр 50, выполняющий за один такт арифметический сдвиг всех операндов хранящегося в нем N-разрядного вектора на J разрядов влево, где J - минимальная величина, которой кратны разрядности данных в векторах вторых операндов вычислительного устройства 18, элемент задержки 51, первый блок памяти 52, имеющий порт ввода магазинного типа и содержащий N/J ячеек для хранения N-разрядных данных, второй блок памяти 53, содержащий N/J ячеек для хранения N-разрядных данных, N/J блоков умножения 54, каждый из которых умножает N-разрядный вектор данных программируемой разрядности на J-разрядный множитель, и схему сложения векторов 55, формирующую двухрядный код суммы N/J+1 векторов данных программируемой разрядности.

Входы разрядов вектора третьих операндов 21 вычислительного устройства 18 подключены к информационным входам сдвигового регистра 50, выходы которого соединены с информационными входами первого блока памяти 52, выходы каждой ячейки которого соединены с информационными входами соответствующей ячейки второго блока памяти 53, выходы каждой ячейки которого соединены с входами разрядов вектора множимых соответствующего блока умножения 54, входы разрядов множителя которого подключены к входам соответствующей J-разрядной группы разрядов вектора вторых операндов 20 вычислительного устройства 18. Выходы каждого блока умножения 54 соединены с входами разрядов соответствующего вектора слагаемых схемы сложения векторов 55, входы разрядов (N/J+1)-го вектора слагаемых которой подключены к входам разрядов вектора первых операндов 19 вычислительного устройства 18, входы установки границ данных в векторах третьих операндов 24 которого подключены к соответствующим входам установки границ данных в векторах операндов сдвигового регистра 50, вход режима работы которого подключен к первому входу управления загрузкой векторов третьих операндов в первый блок памяти 25 вычислительного устройства 18, второй вход управления загрузкой векторов третьих операндов в первый блок памяти 26 которого подключен к тактовому входу сдвигового регистра 50 и входу элемента задержки 51, выход которого соединен с входом управления записью первого блока памяти 52. Вход управления записью второго блока памяти 53 подключен к входу управления пересылкой матрицы третьих операндов из первого блока памяти во второй блок памяти 27 вычислительного устройства 18, каждый вход установки границ данных в векторах вторых операндов 23 которого подключен к входу знаковой коррекции соответствующего блока умножения 54. Входы установки границ данных в векторах первых операндов и результатов 22 вычислительного устройства 18 подключены к входам установки границ данных в векторах множимых и результатов каждого блока умножения 54 и к входам установки границ данных в векторах слагаемых и результатов схемы сложения векторов 55, выходы разрядов векторов первых и вторых слагаемых результатов которой являются соответствующими выходами 28 и 29 вычислительного устройства 18.

Вычислительное устройство 18 работает следующим образом.

Процедура загрузки матрицы Z во второй блок памяти 53 вычислительного устройства 18 выполняется в два этапа.

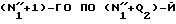

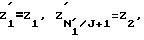

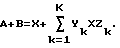

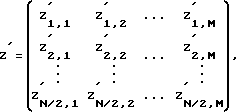

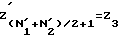

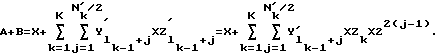

Первоначально в течение N/J тактов матрица Z преобразуется в матрицу

которая загружается в первый блок памяти 52 вычислительного устройства 18. Причем i-я строка матрицы Z' представляет собой вектор данных Z матрицы Z', формируемых в соответствии с выражением

матрицы Z', формируемых в соответствии с выражением

где lk - суммарное количество J-разрядных групп разрядов в k первых операндах вектора Y, N

Из представленного выше выражения следует, что

и т.д. То есть все строки матрицы Z будут присутствовать и в матрице Z' но, как правило, на других позициях.

и т.д. То есть все строки матрицы Z будут присутствовать и в матрице Z' но, как правило, на других позициях.

Преобразование матрицы Z в матрицу Z' выполняется с помощью сдвигового регистра 50 за N/J тактов. В каждом из этих N/J тактов на управляющий вход 26 вычислительного устройства 18 подается синхросигнал, который поступает на тактовый вход сдвигового регистра 50, а на входы 24 вычислительного устройства 18 непрерывно подается описанное выше N-разрядное управляющее слово H, которое поступает на входы установки границ данных в векторах операндов сдвигового регистра 50. В i-м такте (i=1,2,...,N/J) на управляющий вход 25 вычислительного устройства 18 подается i-й разряд ei, описанного выше (N/J)-разрядного управляющего слова E. Данный сигнал поступает на вход управления режимом работы сдвигового регистра 50.

В (lk+1+1)-м такте (k= 1,2, . ..,K), когда на вход 25 вычислительного устройства 18 подается разряд слова E, имеющий единичное значение, сдвиговый регистр 50 переходит в режим загрузки вектора Zk, подаваемого на входы 21 вычислительного устройства 18. В каждом из остальных N/J-K тактов, когда на вход 25 вычислительного устройства 18 подается разряд слова E, имеющий нулевое значение, сдвиговый регистр 50 будет выполнять арифметический сдвиг на J разрядов влево хранящегося в нем вектора данных.

Таким образом, по окончании i-го такта (i=1,2,...,N/J) процесса преобразования матрицы Z в матрицу Z' в сдвиговом регистре 50 будет храниться вектор Z

Синхросигнал, подаваемый на вход 26 вычислительного устройства 18 в каждом такте в течение всего процесса преобразования матрицы Z в матрицу Z', поступает через элемент задержки 51, в качестве которого может быть использован обычный инвертор, на вход управления записью первого блока памяти 52 вычислительного устройства 18. Поэтому одновременно с преобразованием матрицы Z в матрицу Z' будет происходить загрузка матрицы Z' в первый блок памяти 52 вычислительного устройства 18. По окончании процесса загрузки в i-й ячейке первого блока памяти 52 вычислительного устройства 18 будет содержаться вектор Z

После этого на управляющий вход 27 вычислительного устройства 18 в течение одного такта подается синхросигнал, по которому содержимое всех ячеек первого блока памяти 52 переписывается в соответствующие ячейки второго блока памяти 53 вычислительного устройства 18. Таким образом, за один такт происходит пересылка матрицы Z' из первого 52 во второй 53 блок памяти вычислительного устройства 18.

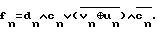

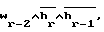

Начиная со следующего такта исполнительные узлы вычислительного устройства 18, к которым относятся блоки умножения 54 и схема сложения векторов 55, будут в каждом такте формировать двухрядный код результата операции X + Y • Z. При этом i-й блок умножения 54 служит для формирования частичного произведения вектора Z

Pi=Z

На входы 23 вычислительного устройства 18 подается управляющее слово E, j-й разряд ej которого поступает на вход знаковой коррекции (j-1)-го блока умножения 54 (j=2,3,...,N/J). На вход знаковой коррекции (N/J)-го блока умножения 54 поступает младший разряд e1 управляющего слова E. Поэтому каждый блок умножения 54, на входы разрядов множителя которого подается группа старших разрядов одного из элементов вектора Y, будет выполнять умножение в дополнительном коде. Остальные N/J-K блоков умножения 54 будут работать в прямом коде.

Схема сложения векторов 55 формирует двухрядный код суммы частичных произведений P1, P2, ..., PN/J, и вектора X, подаваемого на входы 19 вычислительного устройства 18. Данная схема может быть построена на основе сумматоров с отложенными переносами.

На входы 22 вычислительного устройства 18 подается управляющее слово H, которое поступает на входы установки границ данных в векторах множимых каждого блока умножения 54 и на входы установки границ данных в векторах слагаемых схемы сложения векторов 55. При этом в каждом исполнительном узле вычислительного устройства 18 будет блокироваться распространение переносов между разрядами этих узлов, обрабатывающими разные элементы входных векторов.

На выходах схемы сложения векторов 55 формируются векторы A и B, сумма которых равна

Сгруппировав частичные произведения, относящиеся к отдельным элементам вектора Y, последнее выражение можно представить в следующем виде

С учетом того, что каждый k-й элемент вектора Y равен

предыдущее выражение преобразуется следующим образом

Таким образом, на выходах 28 и 29 вычислительного устройства формируется двухрядный код результата операции X + Y • Z.

В общем случае длительность процессорного такта нейропроцессора определяется суммарной задержкой переключения последовательно включенных коммутатора с трех направлений в два 11, устройства для вычисления функций насыщения 14, вычислительного устройства 18 и сумматора 30. Производительность нейропроцессора можно существенно увеличить, если использовать устройства для вычисления функций насыщения 13 и 14, содержащие регистры входных данных, информационные входы которых подключены к входам 15 этих устройств, вычислительное устройство 18, содержащее регистр входных данных, информационные входы которого подключены к входам 19 и 20 вычислительного устройства 18, и сумматор 30, содержащий регистр входных данных, информационные входы которого подключены к входам 31, 32 и 33 сумматора 30. Наличие таких регистров в исполнительных узлах нейропроцессора позволяет вести обработку данных в конвейерном режиме, обеспечивающем в каждом такте параллельное выполнение трех процессов: формирования вычислительным устройством 18 двухрядного кода результата взвешенного суммирования очередного набора входных данных, сложения на сумматоре 30 двухрядного кода результата взвешенного суммирования предыдущего набора входных данных и вычисления на устройствах 13 и 14 функций насыщения для следующего набора входных операндов. Так как максимальные задержки переключения устройств для вычисления функций насыщения 13 и 14, вычислительного устройства 18 и сумматора 30 имеют приблизительно одинаковые значения, то введение конвейерных регистров позволяет практически в три раза повысить тактовую частоту работы нейропроцессора.