ff

INO

сд

00 О)

Изобретение относится к автоматике и вычислительной технике и может Найти применение в устройствах считывания выходных сигналов интегральных cjLxeM с зарядовой связью ИСЗС) и Других устройствах,в которых необ- запоминание отсчетов сигнала,

Цель изобретения - повышение быстродействия устройства.

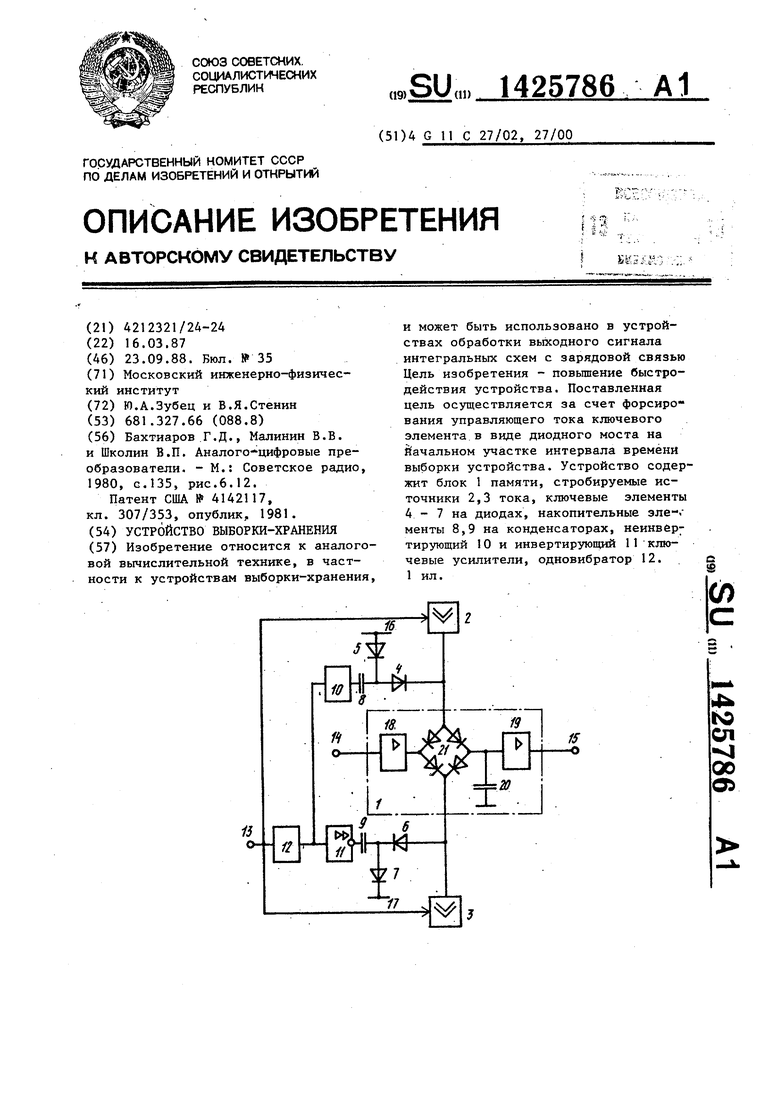

На чертеже представлено устройст-- йо выборки-хранения. ; Устройство содержит блок 1 памяти, первый 2 и второй 3 стробируемые Щеточники тока, первый 4, второй 5, |гретий 6 и четвертый 7 ключевые эле- енты на диодах, первый 8 и второй 9 |1акопительные элементы на конденсато- jpax, первый 10 (неинвертирующий клю- евой) и второй 11 (инвертирующий Ключевой) усилители, одновибратор 12 Управляющий вход 13 устройства, ин- | ормационные вход 14 и выход 15 уст- |ройства5 первую 16 и вторую 17 шины питания устройства. На шину 16 пода- ется отрицательный потенцил, на ши- |ну 17 - положительный, ; Блок 1 содержит буферные усилите- ;ли 18 И 19, накопительный элемент 20 на конденсаторе, ключевой элемент 21 в виде диодного моста. : Устройство работает следующим ;образом.

i В режиме хранения на выходе од- новибратора 12 формируется низкое значение логического сигнала, на выходе неинвертирующего усилителя 1 О напряжение, близкое к напряжению шины 16 устройства, на элементе 8 напряжение, близкое к нулю. На выходе усилителя 11 напряжение, близко к напряжению шины 17 устройства, на элементе 9 напряжение, близкое к нулевому. Элементы 4 и 6 находятся в

0

5

0

5

0

ла на входе I3 в начале интервала времени выборки на выходе одновибра- тора 12 формируется сигнал высокого уровня, на входах усилителей 10 и 11 появляются напряжения, значения которых противоположны первоначальным и близким к максимальным напряжениям . питания устройства на шинах 17, и 16, элементы 5 и 7 закрьюаются и элементы 8 и 9 заряжаются через открьшающиеся элементы 4 и 6.

После заряда элементов 8 и 9 по окончании действия логического сигна ла высокого уровня на выходе одновиб- ратора 12 выходные напряжения усилителей 10 и 11 возвращаются к первона чальным, близким к напряжению на шинах 16 и 17 устройства. Элементы 4 и 6 закрываются, элементы В и 9 отключаются от блока 1 и разряжаются через прямосмещенные элементы 5 и 7, По окончании действия сигнала высокого уровня на выходе одновибратора 12 блок 1 продолжает оставаться в режиме выборки, напряжение на выходе 15 устанавливается более точно, при этом устраняются ошибки от различия сопротивлений внутренних ветвей блока 1 и возможные ошибки от разности зарядов переключения элементов 4 и 6. По окончании действий сигнала высокого логического уровня на входе 13 устройства источники тока выключаются и блок 1 выборки и хранения переходит в режим хранения.

Максимальная скорость изменения выходного напряжения наблюдается только на начальном этапе интервала времени выборки в моменты максимального несоответствия входного и выходного напряжений.

По сравнению с известным устройством быстродействие увеличивается

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство аналоговой памяти | 1986 |

|

SU1377916A1 |

| Устройство выборки-хранения | 1990 |

|

SU1716571A1 |

| Устройство выборки-хранения | 1986 |

|

SU1401519A1 |

| УСТРОЙСТВО ДЛЯ МАГНИТНО-ИМПУЛЬСНОЙ ОБРАБОТКИ РАСТЕНИЙ | 2013 |

|

RU2523162C1 |

| УСТРОЙСТВО ДЛЯ МАГНИТНО-ИМПУЛЬСНОЙ ОБРАБОТКИ РАСТЕНИЙ | 2014 |

|

RU2573349C1 |

| Аналоговое запоминающее устройство | 1989 |

|

SU1691895A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU881866A1 |

| Устройство выборки-хранения | 1987 |

|

SU1508285A2 |

| Аналоговое запоминающее устройство | 1987 |

|

SU1472951A1 |

| Аналоговое запоминающее устройство | 1983 |

|

SU1104587A1 |

Изобретение относится к аналоговой вычислительной технике, в частности к устройствам выборки-хранения. и может быть использовано в устройствах обработки выходного сигнала интегральных схем с зарядовой связью Цель изобретения - повышение быстродействия устройства. Поставленная цель осуществляется за счет форсиро вания управляющего тока ключевого элемента в виде диодного моста на Йачальном участке интервала времени выборки устройства. Устройство содержит блок 1 памяти, стробируемые источники 2,3 тока, ключевые элементы 4 - 7 на диодах, накопительные эле-. менты 8,9 на конденсаторах, неинвертирующий 10 и инвертирующий 11 ключевые усилители, одновибратор 12. 1 ил. а S (Л

закрытом состоянии. В режиме хранения четыре раза при погрешности выборки

источники 2 и 3 тока выключены, на управляющие входы блока 1 управляющие сигна пы не поступают, блок 1 находится в режиме хранения и напряжение на выходе 15 сохраняется неизменным .

При поступлении сигнала выборки на вход 13 источники 2 и 3 тока формируют ТОК;, переводящий блок 1 в режим выборки, однако величина одного этого тока недостаточна для достижения высокого значения скорости нарастания вьпкодкого напряжения блока 1 . По переднему фронту управляющего сигна50

55

сигнала 0,1%.

Формула изобретения

Устройство выборки-хранения, содержащее блок памяти, первый и BTopojft стробируемые источники тока, управляющие входы которых являются управляющим входом устройства, вход и выход блока памяти являются соответственно информационными входом и выходом устройства, первый и второй управляющие входы блока памяти подключены соответственно к выходам первого и второго стробируемь х источни четыре раза при погрешности выборки

сигнала 0,1%.

Формула изобретения

Устройство выборки-хранения, содержащее блок памяти, первый и BTopojft стробируемые источники тока, управляющие входы которых являются управляющим входом устройства, вход и выход блока памяти являются соответственно информационными входом и выходом устройства, первый и второй управляющие входы блока памяти подключены соответственно к выходам первого и второго стробируемь х источни,1425786.

34

КОВ тока, отличающеесядиода первого и катоду диода третье- тем, что, с целью повышения быстро-го ключевых элементов, катод диода действия устройства, в него введеныпервого и анод диода третьего клю- первый и второй усилители, первый ичевьсх элементов подключены соответ- второй накопительные элементы на кон-ственно к первому и второму управ- денсаторах, первого по четнертьйляющим входам блока памяти, анод и ключевые элементы на диодах, одно -катод диода второго ключевого эле- вибратор, вход которого подключен кмента подключены соответственно к управляющему входу устройства, а вы- IQпервой шине питания устройства и ход подключен к входам первого и вто-второму вьшоду первого накопитепьно- рого усилителей, выходы которых под-го элемента, катод и анод диода чет- ключены соответственно к первым вы-;вертого ключевого элемента подключе- водам первого и второго накопитель-ны соответственно к второй шине пи- ных элементов вторые выводы которых 15тания устройства и второму выводу подключены соответственно к аноду .второго накопительного элемента.

| Бахтиаров Г.Д., Малинин В.В | |||

| и Школин В.П | |||

| Аналого-цифровые преобразователи | |||

| - М.: Советское радио, 1980, с.135, рис.6.12 | |||

| Патент США № 4142117, кл | |||

| Приспособление для выпечки формового хлеба в механических печах с выдвижным подом без смазки форм жировым веществом | 1921 |

|

SU307A1 |

Авторы

Даты

1988-09-23—Публикация

1987-03-16—Подача