(Л

4 to

сл

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приведения р-кодов Фибоначчи к минимальной форме | 1988 |

|

SU1547073A1 |

| Устройство для приведения р-кодов Фибоначчи к минимальной форме | 1982 |

|

SU1019434A1 |

| Нормализатор кодов Фибоначчи | 1982 |

|

SU1027717A1 |

| Устройство для приведения I-кодов фибоначчи к минимальной форме | 1981 |

|

SU1005024A1 |

| Устройство для приведения р-кодов фибоначчи к минимальной форме | 1976 |

|

SU662930A1 |

| Устройство для приведения р-кодовфибОНАччи K МиНиМАльНОй фОРМЕ | 1979 |

|

SU842782A1 |

| Сумматор кодов с иррациональным основанием | 1991 |

|

SU1837279A1 |

| Устройство для приведения р-кодов фибоначчи к минимальной форме | 1978 |

|

SU779997A1 |

| Устройство для приведения @ -кодов Фибоначчи к нормальной форме | 1988 |

|

SU1508351A1 |

| Устройство для приведения р-кодовфибОНАччи K МиНиМАльНОй фОРМЕ | 1978 |

|

SU842786A1 |

Изобретение относится к вычислительной технике и может быть использовано для приведения кодов избыточных систем счисления к минимальной форме. Целью изобретения является расширение области применения за счет приведения к минимальной форме кодов двоичной избыточной системы счисления. Устройство содержит блоки свертки, каждый из которых выходы 2 и 3, входы 4-15 и содержит триггер 16, элементы И 17-22, элементы ИЛИ 23-28. 1 з.п.ф-лы, 2 ил.

qStus.Z

Изобретение относится к вычислительной технике и может быть использовано для приведения кодов избыточных систем счисления к минимальной форме.

Целью изобретения является расширение области применения за счет приведения к минимальной форме кодов двоичной избыточной системы счисления.

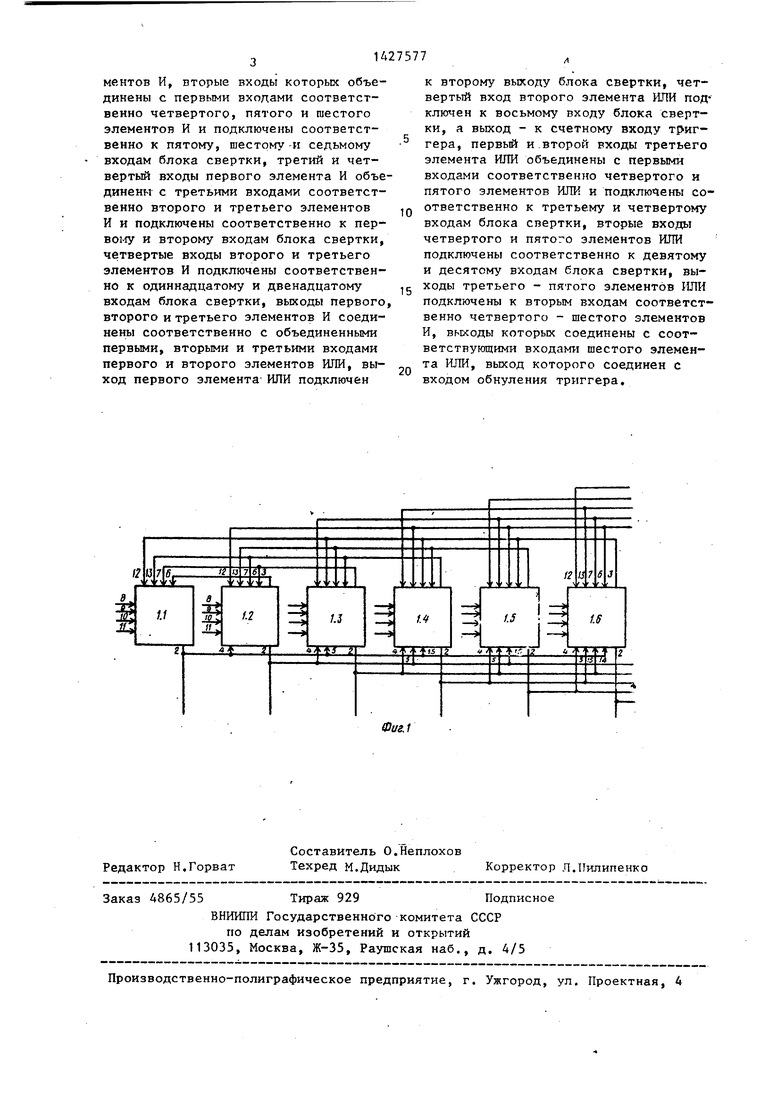

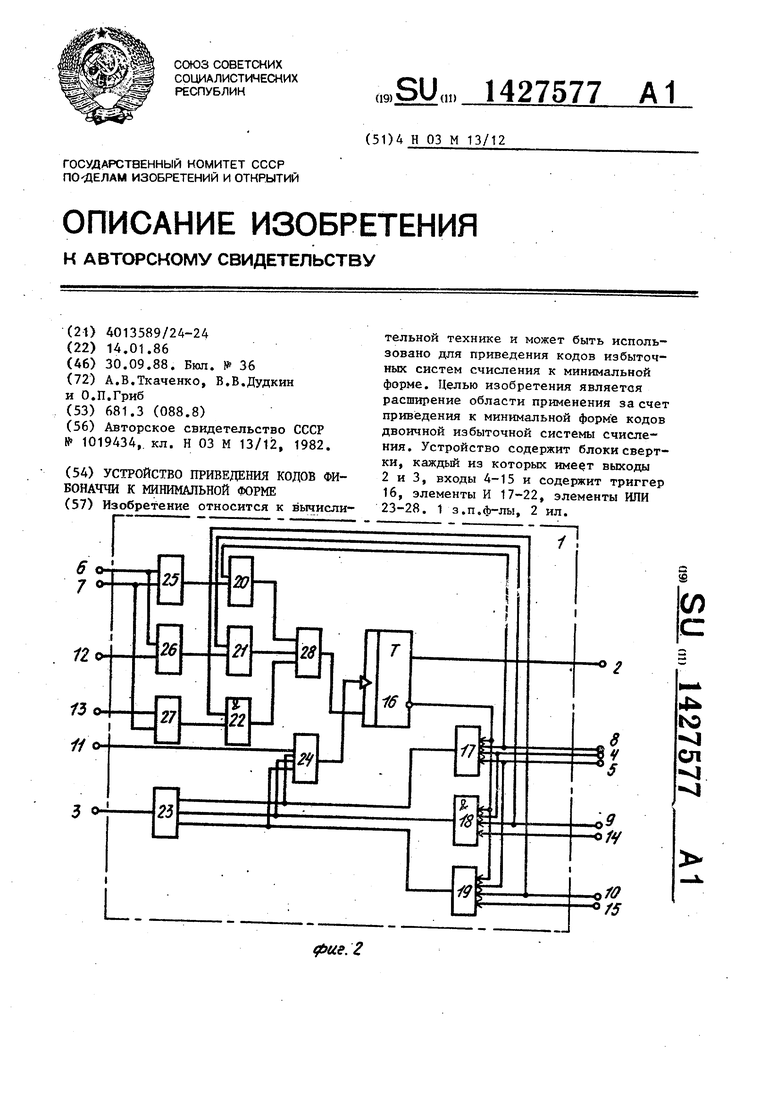

На фиг.1 приведена функциональная схема устройства; на фиг.2 - схема блока свертки.

Устройство содержит блоки 1 сверт ки, каждый блок свертки имеет пе рвьй и второй выходы 2 и 3, первый - одиннадцатый входы 4-15, каждый блок свертки - триггер 16, элементы И 17- 22, элементы ИЛИ 23-28.

Устройство работает следующим об разом.

В начальном состоянии триггеры 16 блоков обнулены. Входной код подается на входы 11 блоков 1, е,п;иничные информационные сигналы поступают через элементы ИЛИ 24 на счетные входы триггеров 16 соответствующих разрядов и переводят их в единичные состояния. При подаче разрешающего сигнала на входы 8 блоков 1 осуществляется свертка кодов Фибоначчи. При этом с .помощью элемента И 17 в каждой группе из трех смежных разрядов вьщеляются ком бинации типа 110 и при наличии подоб ной комбинации на выходе элемента И 16 формируется единичнБй сигнал, который, проходя через элемент ИЛИ 24, поступает на счетный вход триггера 16 и переводит его в единичное состо яние. Этот же сигнал через элемент ИЛИ 23 поступает на выход 3 блока 1 и далее на входы 6 и 7 блоков 1 сверт ки младших разрядов, в которых он проходит через элементы ИЛИ 25, И 20, ИЛИ 28 и обнуляет триггер 16. В результате кодовая комбинация 110 в трех смежных разрядах переходит в комбинацию 001.

При приведении кодов в двоичной избыточной системе счисления разрешающие сигналы попеременно подаются на входы 9 и 10 блоков 1. В результа- те этого с помощью элементов И 18 выделяются кодовые комбинации, когда значение i-ro разряда .нулевое, а значения (i-1)-ro и (i-5)-ro разрядов единичные. С помощью элемента И 19 вьщеляются комбинации, когда значение i-ro разряда нулевое, а значения (i-2)-ro и (i-3)-ro разрядов единич

20

25

|Q

5055

30

35

40

45

ные. Далее сигналы с выходов элементов И 18 и 19 через элемент ИЛИ 24 переводят триггер 16 i-ro разряда в единичное значение, а через элемент И 23 блока 1 i-ro разряда и элементы ИЛИ 26, И 21 и ИЛИ 28 переводят триггеры 16 блоков 1 (i-l)-ro и (i-5) -ro разрядов в нулевое состояние. Обнуление триггеров 16 блоков 1 свертки (i-2)-ro и (i-3)-ro разрядов производится с помощью сигнала, поступающего на вход обнуления триггера 16 через элементы ИЛИ 27, И 22 к ИЛИ 28 блока 1 соответствующего разряда. Выходной код снимается с выходов 2 блоков 1.

Формула изобретения

и четвертым входом (i-2)-ro блока свертки, объединённые пятые, шестые и седьмые входы блоков свертки являются соответственно первым, вторым и третьим управляющими входами устройства, восьмой вход каждого блока свертки является соответствующим информационным входом устройства, о личающееся тем, что, с целью расширения области применения за счет приведения к минимальной форме кодов избыточной системы счисле- . ния, девятый вход (i-5)-ro блока свертки объединен с дёйятым входом (i-3)-ro блока свертки и подключен ко второму выходу i-ro блока свертки, одиннадцатый вход (i+5)-ro и двенадцатый вход (i+3)-ro блоков свертки подключены к первому выходу блока свертки.

0

5

0

к второму выходу блока свертки, четвертый вход второго элемента ИЛИ подключен к восьмому входу блока свертки, а выход - к счетному входу триггера, первый и.второй входы третьего элемента ИЛИ объединены с первыми входами соответственно четвертого и пятого элементов ИЛИ и подключены соответственно к третьему и четвертому входам блока свертки, вторые входы четвертого и пятого элементов ИЛИ подключены соответственно к девятому и десятому входам блока свертки, выходы третьего - пятого элементов ИЛИ подключены к вторым входам соответственно четвертого - шестого элементов И, выходы которых соединены с соответствующими входами шестого элемента ИЛИ, выход которого соединен с входом обнуления триггера.

| Устройство для приведения р-кодов Фибоначчи к минимальной форме | 1982 |

|

SU1019434A1 |

| кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-09-30—Публикация

1986-01-14—Подача