k-

-13

-я

л-J5

-16

сл С

| название | год | авторы | номер документа |

|---|---|---|---|

| ПОСЛЕДОВАТЕЛЬНЫЙ СУММАТОР | 1991 |

|

RU2006914C1 |

| Устройство для последовательного деления | 1986 |

|

SU1304017A1 |

| Последовательный сумматор | 1989 |

|

SU1691835A1 |

| Микропрограммное устройство управления с самоконтролем | 1985 |

|

SU1247871A1 |

| Устройство вычисления функции @ @ с исправлением ошибок | 1984 |

|

SU1288690A1 |

| Функциональный преобразователь | 1988 |

|

SU1501021A1 |

| Матричное устройство для возведения в квадрат | 1989 |

|

SU1619260A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1700558A1 |

| Устройство цифрового интегрирования | 1986 |

|

SU1345192A1 |

| Устройство для умножения | 1985 |

|

SU1309019A1 |

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных устройствах с повышенной достоверностью обработки информации. Целью изобретения является увеличение среднего быстродействия работы сумматора. Это достигается тем, что сумматор кодов с иррациональным основанием, содержащий шестиразрядный блок б свертки, трехразрядный блок 4 конт

оа со vi го

VI

Ч)

роля перемещения, четырехразрядный блок 7 контроля свертки и функциональные свя- .зи, снабжён (т-Т)-рэзрядами блоков 4, 7 контроля перемещения и свертки, коммутатором 1,(гти-2)-разрядным блоком 2 переме- щения-развертки; m-разрядным блоком 5

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных устройствах с повышенной достоверностью обработки информации, представленной кодами с иррациональным основанием (кодами Фибоначчи или кодами золотой пропорции), обладающих высокой ошибко- обнаруживающей способностью.

Цель изобретения - увеличение среднего быстродействия сумматора.

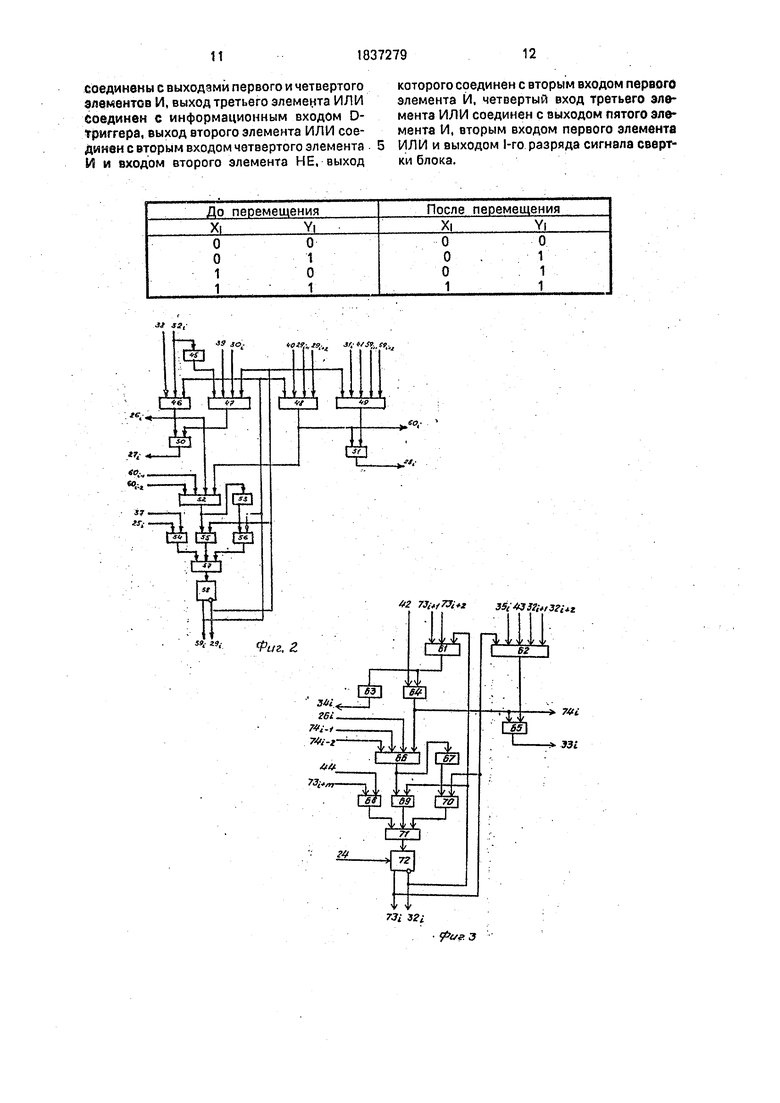

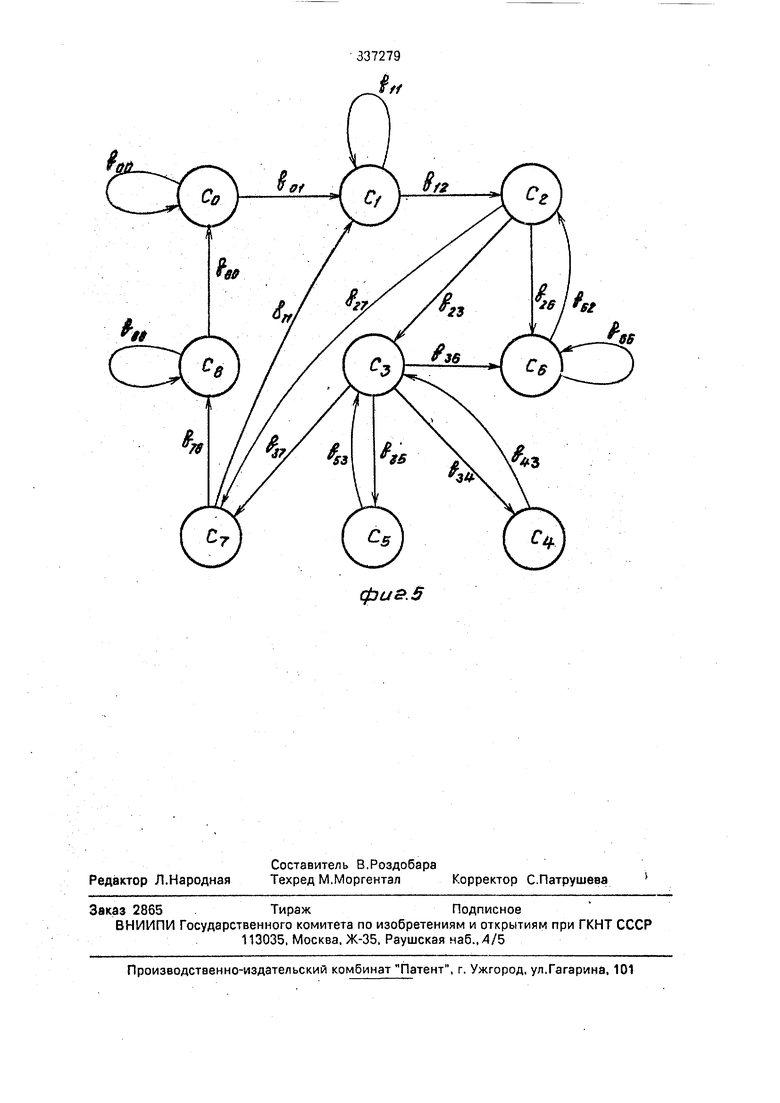

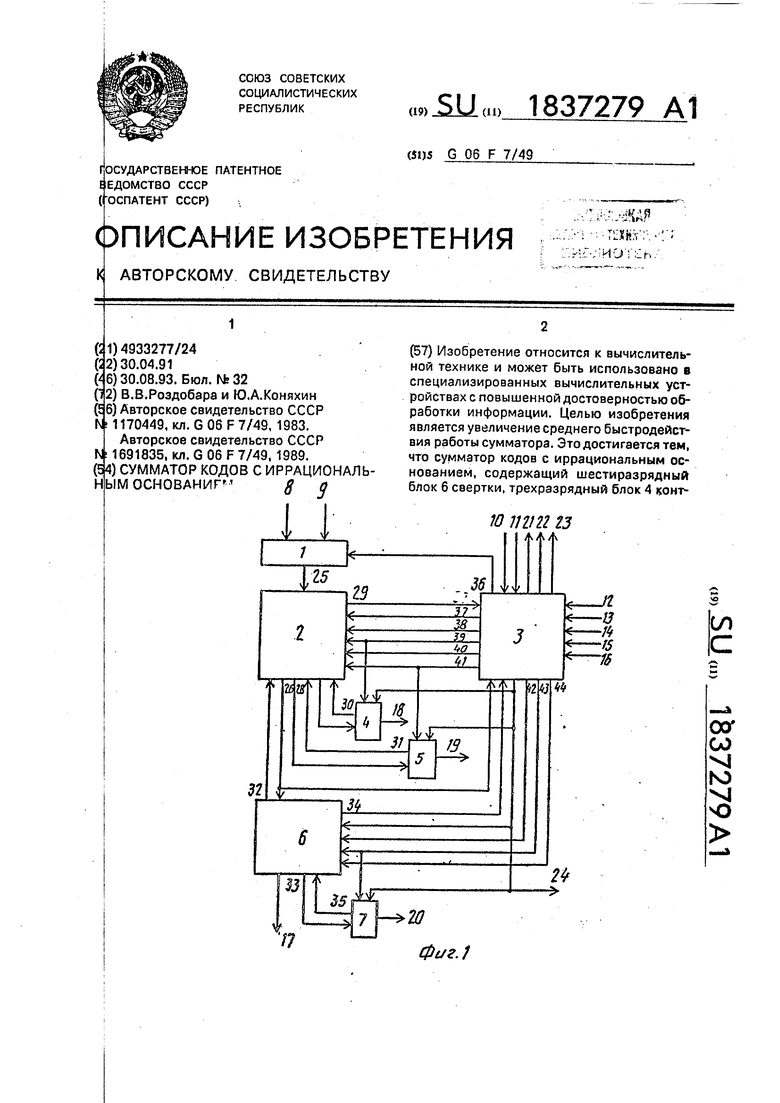

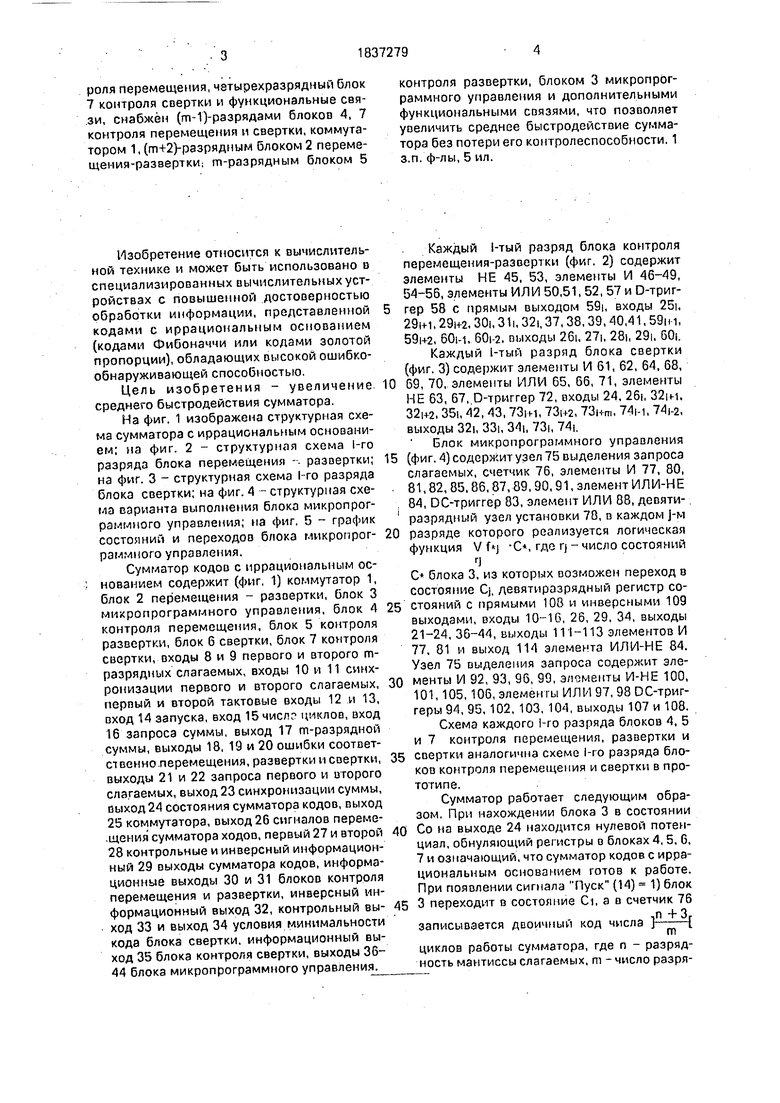

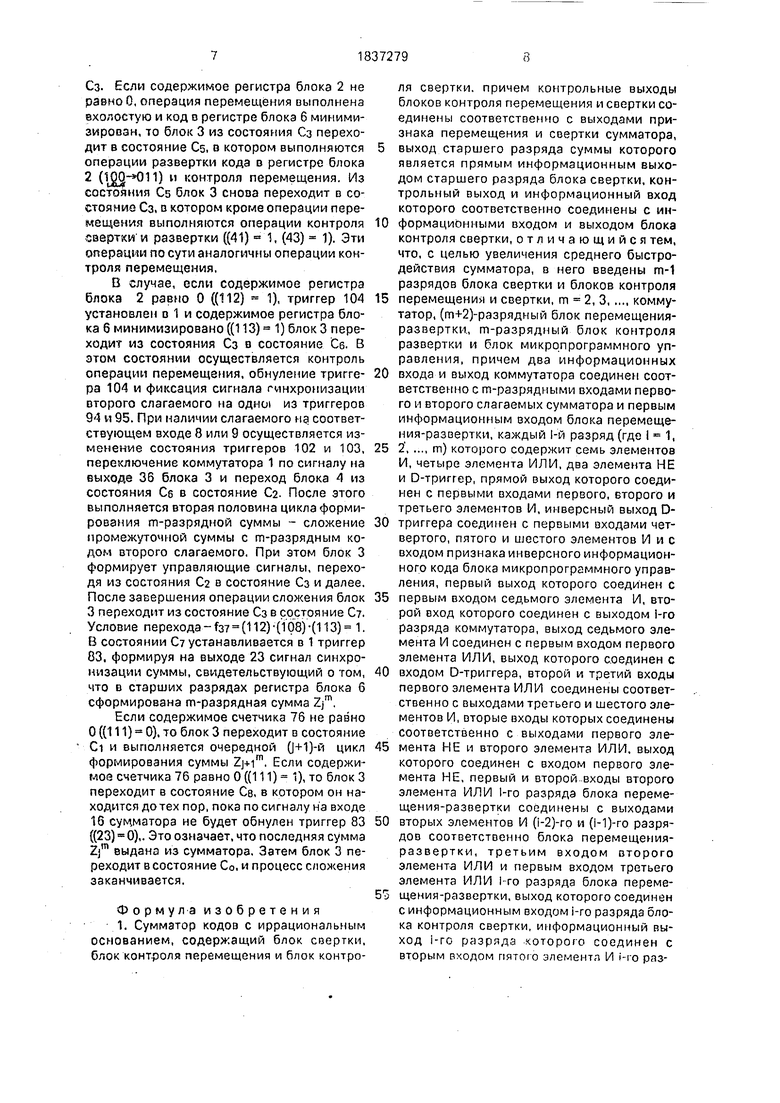

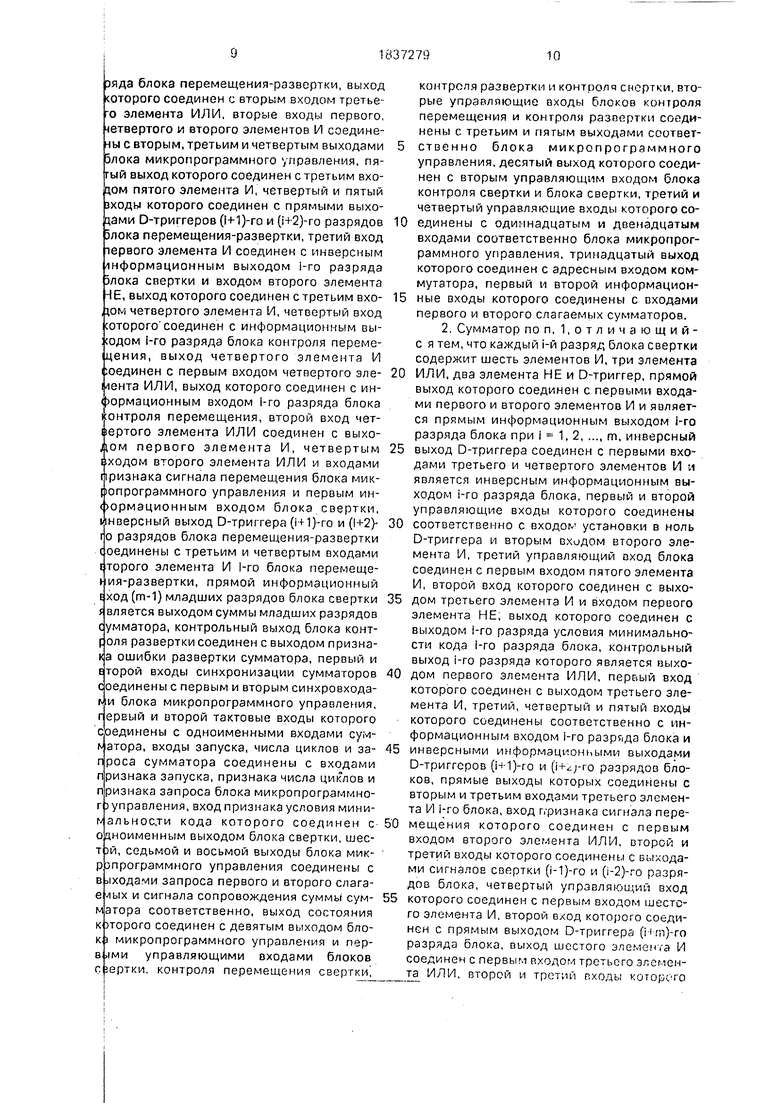

На фиг. 1 изображена структурная схема сумматора с иррациональным основанием; на фиг. 2 - структурная схема 1-го разряда блока перемещения -. развертки; на фиг. 3 - структурная схема 1-го разряда блока свертки; на фиг. 4 - структурная схема варианта выполнения блока микропрограммного управления; на фиг, 5 - график состояний и переходов блока микропрограммного управления.

Сумматор кодов с иррациональным основанием содержит (фиг. 1) коммутатор 1, блок 2 перемещения - развертки, блок 3 микропрограммного управления, блок 4 контроля перемещения, блок 5 контроля развертки, блок б свертки, блок 7 контроля свертки, входы 8 и 9 первого и второго т- разрядных слагаемых, входы 10 и 11 синхронизации первого и второго слагаемых, первый и второй тактовые входы 12 и 13, вход 14 запуска, вход 15 числ циклов, вход 16 запроса суммы, выход 17 т-разрлдной суммы, выходы 18, 19 и 20 ошибки соответственно .перемещения, развертки и свертки, выходы 21 и 22 запроса первого и второго слагаемых, выход 23 синхронизации суммы, выход 24 состояния сумматора кодов, выход 25 коммутатора, выход 26 сигналов переме- .щения сумматора ходов, первый 27 и второй 28 контрольные и инверсный информационный 29 выходы сумматора кодов, информационные выходы 30 и 31 блоков контроля перемещения и развертки, инверсный информационный выход 32, контрольный вы- ход 33 и выход 34 условия минимальности кода блока свертки, информационный выход 35 блока контроля свертки, выходы 36- 44 блока микропрограммного управления.

контроля развертки, блоком 3 микропрограммного управления и дополнительными функциональными связями, что позволяет увеличить среднее быстродействие сумматора без потери его контролеспособности. 1 з.п. ф-лы, 5 ил.

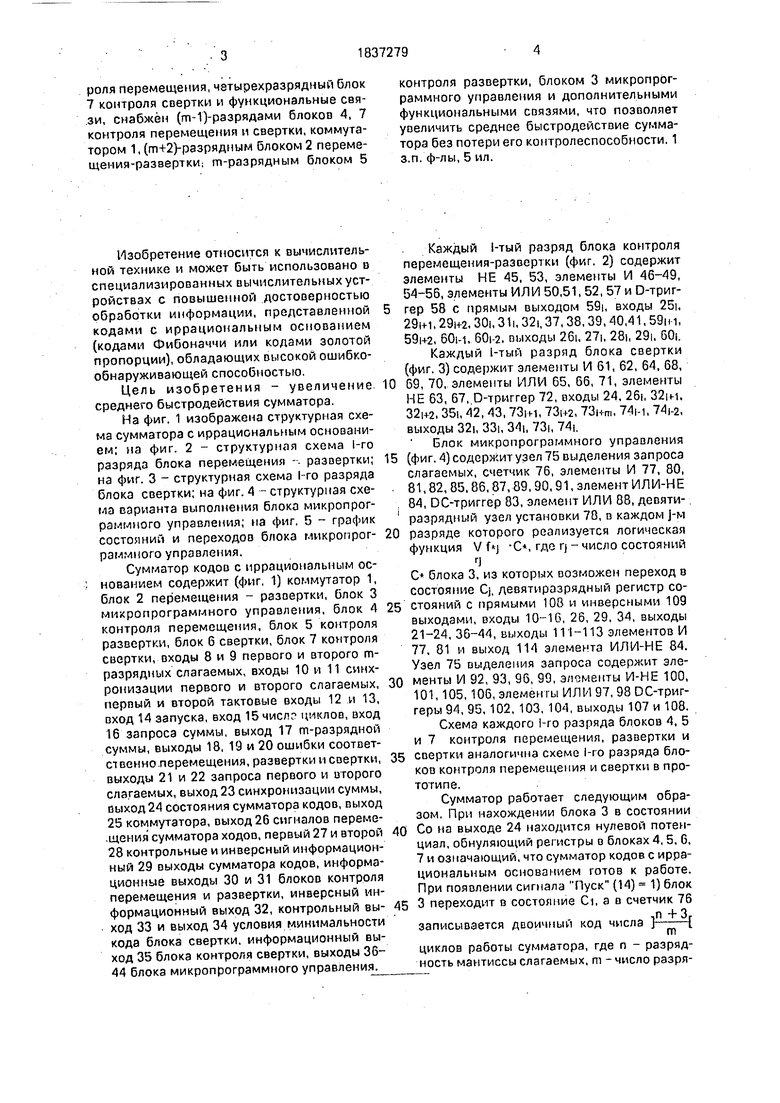

Каждый i-тый разряд блока контроля перемещения-развертки (фиг. 2) содержит элементы НЕ 45, 53, элементы И 46-49, 54-56, элементы ИЛИ 50,51, 52, 57 и D-тригrep 58 с прямым выходом 59i, входы 25i,

29н-1,29н-2, 30i, 31i, 32|. 37, 38,39,40,41,59н 1,

59н-2, 60и, 60i-2, выходы 26i, 27i, 28i, 29i, 60i.

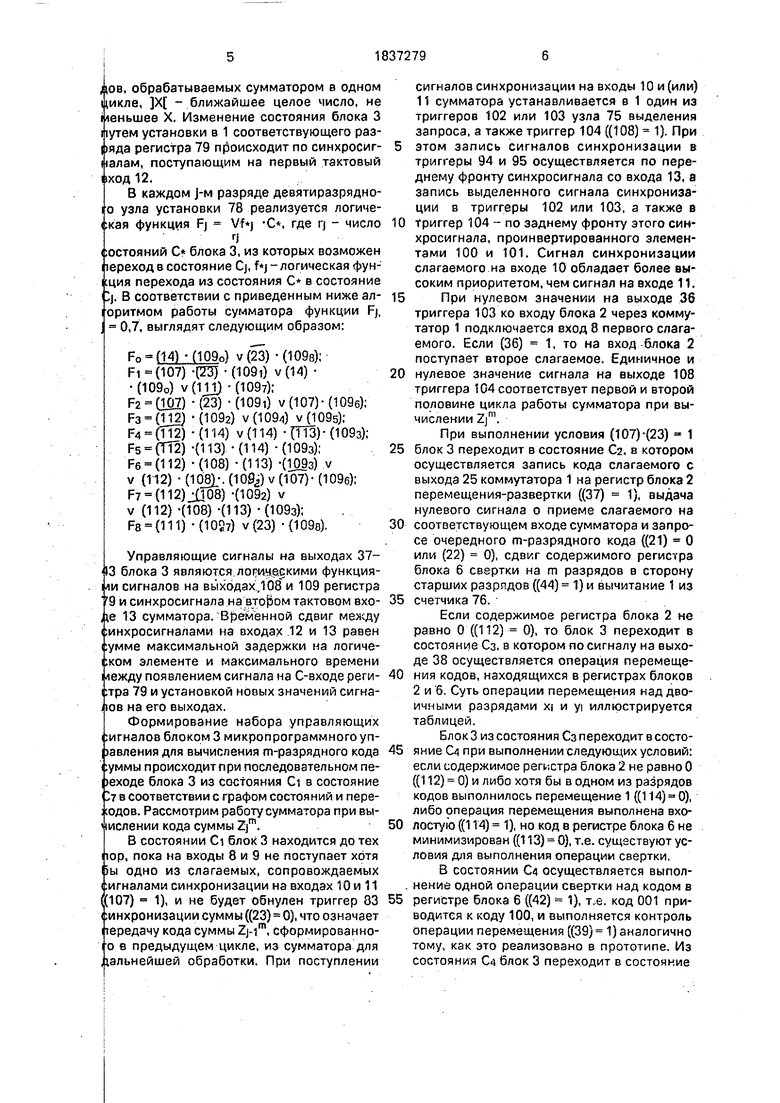

Каждый l-тый разряд блока свертки

(фиг. 3) содержит элементы 14 61, 62, 64, 68,

69, 70, элементы ИЛИ 65, 66, 71, элементы НЕ 63, 67, D-трмггер 72, входы 24, 26i, 32|-м. 32н«, 35i, 42, 43, 73м, 73м, 73i+m, 74м, 74|-2, выходы 32i, 33i, 34i, 73i, 74i.

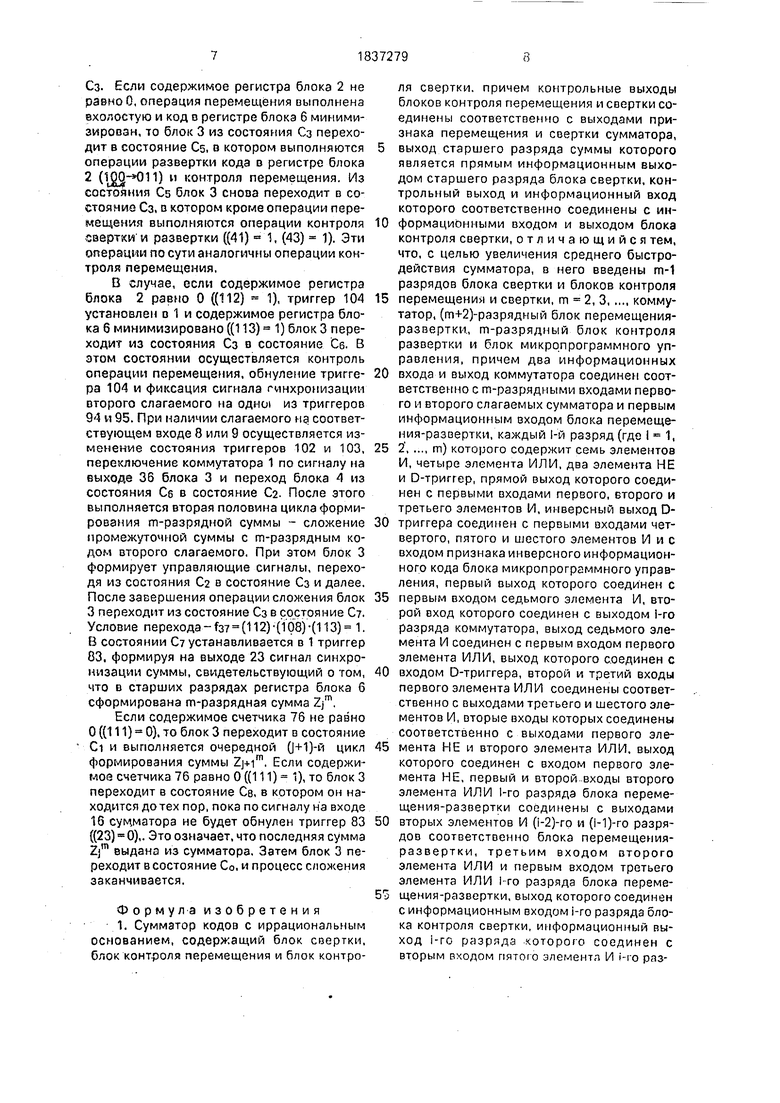

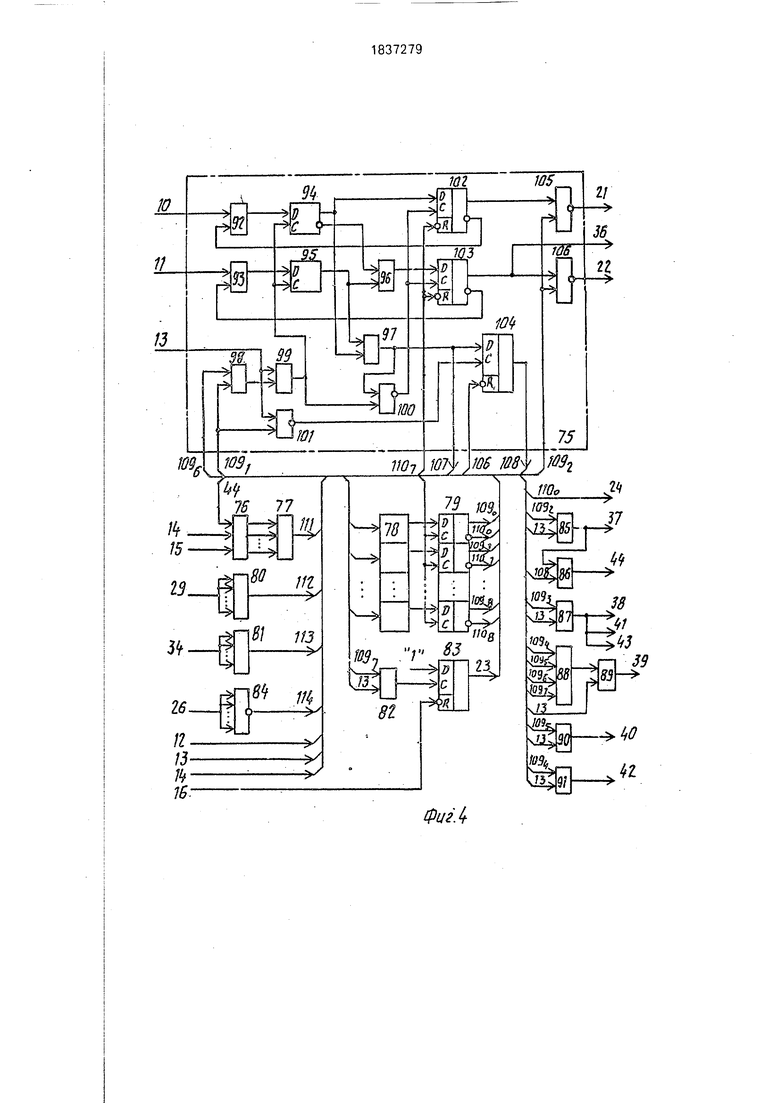

Блок микропрограммного управления

(фиг. 4) содержит узел 75 выделения запроса слагаемых, счетчик 76, элементы И 77, 80, 81,82,85.86,87,89,90,91, элемент ИЛИ-НЕ 84, DC-триггер 83, элемент ИЛИ 88, девятиразрядный узел установки 78, в каждом J-м

разряде которого реализуется логическая функция V -С, где rj - число состояний

П

С блока 3, из которых возможен переход в состояние Cj, девятиразрядный регистр состояний с прямыми 108 и инверсными 109 выходами, входы 10-16, 26, 29. 34, выходы 21-24, 36-44, выходы 111-113 элементов И 77. 81 и выход 114 элемента ИЛИ-НЕ 84. Узел 75 выделения запроса содержит элементы И 92, 93, 96, 99, элементы И-НЕ 100, 101,105,106, элементы ИЛИ 97, 98 DC-триггеры 94, 95, 102, 103, 104, выходы 107 и 108. Схема каждого 1-го разряда блоков 4, 5 и 7 контроля перемещения, развертки и

свертки аналогична схеме 1-го разряда блоков контроля перемещения и свертки в прототипе.

Сумматор работает следующим образом. При нахождении блока 3 в состоянии

Со на выходе 24 находится нулевой потенциал, обнуляющий регистры в блоках 4,5, 6. 7 и означающий, что сумматор кодов с иррациональным основанием готов к работе. При появлении сигнала Пуск (14) 1) блок

3 переходит в состояние Ci, а в счетчик 76

записывается двоичный код числа

m

циклов работы сумматора, где г - разрядность мантиссы слагаемых, m - число разрядов, обрабатываемых сумматором в одном цикле, Х - ближайшее целое число, не меньшее X, Изменение состояния блока 3 путем установки в 1 соответствующего разряда регистра 79 происходит по синхросиг- алам, поступающим на первый тактовый пход12.

В каждом j-м разряде девятиразрядно- о узла установки 78 реализуется логиче- кая функция Fj -С, где п - число

«1

остояний С блока 3, из которых возможен 1ереход в состояние Cj, -логическая фун- ция перехода из состояния С в состояние Oj. В соответствии с приведенным ниже ал- оритмом работы сумматора функции FJ, 0,7, выглядят следующим образом:

FO (14) (109б) v (23) (1098); ) -(2B7 -(109i) v(14) (109о) v{111) -(1097); Fa (Ш) (23) -(109i) v(107)-(1096); F3 (112) -(1092) v(1094) v(1095); F4 (Ш) (114) v (114) (T13)- (109з); Fs (TT2) -(113) (114) (109з): Fe - (112) (108) (113) -(Шз) v v (112) (10JI-. (10%) v (107)- (109e); F7-(112)JU08) -(1092) v v (112) -(108) -(113) -(109з); Fa (111)-(102) v (23)-{109s).

Управляющие сигналы на выходах 37- 13 блока 3 являются.логическими функциями сигналов на выходах.,108 и 109 регистра

9 и синхросигнала на втором тактовом входе 13 сумматора. Временной сдвиг между ;инхросигналами на входах 12 и 13 равен ;умме максимальной задержки на логиче- :ком элементе и максимального времени лежду появлением сигнала на С-входе регитра 79 и установкой новых значений сигнаов на его выходах.

Формирование набора управляющих :игналов блоком 3 микропрограммного уп- )авления для вычисления m-разрядного кода ;уммы происходитпри последовательном переходе блока 3 из состояния Ci в состояние

,7 в соответствии с графом состоя ний и переодов. Рассмотрим работу сумматора при выислении кода суммы Zjm,

В состоянии Ci блок 3 находится до тех

i юр, пока на входы 8 и 9 не поступает хотя

5ы одно из слагаемых, сопровождаемых

игналами синхронизации на входах 10 и 11

107) 1), и не будет обнулен триггер 83

инхронизации суммы ((23)0), что означает i тередачу кода суммы 2j-im, сформированноо е предыдущем цикле, из сумматора для дальнейшей обработки. При поступлении

сигналов синхронизации на входы 10 и (или) 11 сумматора устанавливается в 1 один из триггеров 102 или 103 узла 75 выделения запроса, а также триггер 104 ((108) 1). При 5 этом запись сигналов синхронизации в триггеры 94 и 95 осуществляется по переднему фронту синхросигнала со входа 13, а запись выделенного сигнала синхронизации в триггеры 102 или 103, а также в

0 Триггер 104 - по заднему фронту этого синхросигнала, проинвертированного элементами 100 и 101. Сигнал синхронизации слагаемого на входе 10 обладает более высоким приоритетом, чем сигнал на входе 11.

5 При нулевом значении на выходе 36 триггера 103 ко входу блока 2 через коммутатор 1 подключается вход 8 первого слагаемого. Если (36) 1, то на вход блока 2 поступает второе слагаемое. Единичное и

0 нулевое значение сигнала на выходе 108 триггера 104 соответствует первой и второй половине цикла работы сумматора при вычислении Zjm.

При выполнении условия (107)-(23) 1

5 блок 3 переходит в состояние С2, в котором осуществляется запись кода слагаемого с выхода 25 коммутатора 1 на регистр блока 2 перемещения-развертки ((37) 1), выдача нулевого сигнала о приеме слагаемого на

0 соответствующем входе сумматора и запросе очередного m-разрядного кода ((21) О или (22) 0), сдвиг содержимого регистра блока 6 свертки на m разрядов в сторону старших разрядов ((44) 1) и вычитание 1 из

5 счетчика 76.

Если содержимое регистра блока 2 не равно 0 ((112) 0), то блок 3 переходит в состояние Сз. в котором по сигналу на выходе 38 осуществляется операция перемеще0 ния кодов, находящихся в регистрах блоков 2 и б. Суть операции перемещения над двоичными разрядами xi и yi иллюстрируется таблицей.

Блок 3 из состояния Сз переходит в состо5 яние С4 при выполнении следующих условий: если содержимое регистра блока 2 не равно О ((112) 0) и либо хотя бы в одном из разрядов кодов выполнилось перемещение 1 ((114) 0), либо операция перемещения выполнена вхо0 лостую ((114) 1), но код в регистре блока 6 не минимизирован ((113) 0), т.е. существуют условия для выполнения операции свертки.

В состоянии С4 осуществляется выпол- . нение одной операции свертки над кодом в

5 регистре блока 6 ((42) - 1), т..е. код 001 приводится к коду 100, и выполняется контроль операции перемещения ((39) 1) аналогично тому, как это реализовано в прототипе. Из состояния С4 блок 3 переходит в состояние

Сз. Если содержимое регистра блока 2 не равно 0, операция перемещения выполнена вхолостую и код о регистре блока 6 минимизирован, то блок 3 из состояния Сз переходит в состояние Сз, в котором выполняются операции развертки кода в регистре блока 2 (у)) V1 контроля перемещения. Из состояния Сз блок 3 снова переходит в состояние Сз, в котором кроме операции перемещения выполняются операции контроля свертки и развертки ((41) ° 1, (43) - 1). Эти операции по сути аналогичны операции контроля перемещения,

В случае, если содержимое регистра блока 2 равно 0 ((112) 1), триггер 104 установлен в 1 и содержимое регистра блока 6 минимизировано ((113) - 1) блок 3 переходит из состояния Сз в состояние Се. В этом состоянии осуществляется контроль операции перемещения, обнуление триггера 104 и фиксация сигнала синхронизации второго слагаемого на одно из триггеров 94 и 95. При наличии слагаемого ид соответствующем входе 8 или 9 осуществляется изменение состояния триггеров 102 и 103, переключение коммутатора 1 по сигналу на выходе 36 блока 3 и переход блока 4 из состояния Се в состояние С2. После этого выполняется вторая половина цикла формирования m-разрядной суммы - сложение промежуточной суммы с m-разрядным кодом второго слагаемого. При этом блок 3 формирует управляющие сигналы, переходя из состояния С2 в состояние Сз и далее. После завершения операции сложения блок 3 переходит из состояние Сз в состояние С. Условие перехода-f37 (112) OpS)-(113) 1. В состоянии С устанавливается в 1 триггер 83. формируя на выходе 23 сигнал синхронизации суммы, свидетельствующий о том, что в старших разрядах регистра блока б сформирована m-разрядная сумма Zjm.

Если содержимое счетчика 76 не равно О ((111) 0). то блок 3 переходит в состояние d и выполняется очередной С+1)й Иикл формирования суммы . Если содержимое счетчика 76 равно 0 ((111) 1), то блок 3 переходит в состояние Св, в котором он находится до тех пор, пока по сигналу на входе 16 сумматора не будет обнулен триггер 83 {(23) 0),. Это означает, что последняя сумма Zjm выдана из сумматора. Затем блок 3 переходит в состояние Со, и процесс сложения заканчивается.

Формула изобретения 1, Сумматор кодов с иррациональным основанием, содержащий блок свертки, блок контроля перемещения и блок контроля свертки, причем контрольные выходы блоков контроля перемещения и свертки соединены соответственно с выходами признака перемещения и свертки сумматора,

выход старшего разряда суммы которого является прямым информационным выходом старшего разряда блока свертки, контрольный выход и информационный вход которого соответственно соединены с ин0 формационными входом и выходом блока контроля свертки, отличающийся тем, что, с целью увеличения среднего быстродействия сумматора, в него введены т-1 разрядов блока свертки и блоков контроля

5 перемещения и свертки, m 2, 3,.... коммутатор, (т+2)-разрядный блок перемещения- развертки., m-разрядный блок контроля развертки и блок микропрограммного управления, причем два информационных

0 входа и выход коммутатора соединен соответственно с m-разрядными входами первого и второго слагаемых сумматора и первым информационным входом блока перемещения-развертки, каждый 1-й разряд (где ,

5 2 т) которого содержит семь элементов

И, четыре элемента ИЛИ, два элемента НЕ и D-триггер, прямой выход которого соединен с первыми входами первого, второго и третьего элементов И, инверсный выход D0 триггера соединен с первыми входами четвертого, пятого и шестого элементов И и с входом признака инверсного информационного кода блока микропрограммного управления, первый выход которого соединен с

5 первым входом седьмого элемента И, второй вход которого соединен с выходом 1-го разряда коммутатора, выход седьмого элемента И соединен с первым входом первого элемента ИЛИ, выход которого соединен с

0 входом D-триггера, второй и третий входы первого элемента ИЛИ соединены соответственно с выходами третьего и шестого элементов И, вторые входы которых соединены соответственно с выходами первого эле5 мента НЕ и второго элемента ИЛИ, выход которого соединен с входом первого элемента НЕ, первый и второй входы второго элемента ИЛИ 1-го разряда блока перемещения-развертки соединены с выходами

0 вторых элементов И (i-2)-ro и (И)-го разрядов соответственно блока перемещения- развертки, третьим входом второго элемента ИЛИ и первым входом третьего элемента ИЛИ 1-го разряда блока переме5 щения-развертки, выход которого соединен с информационным входом i-ro разряда блока контроля свертки, информационный выход 1-го разряда которого соединен с вторым входом пятого элемента И i-ro разэяда блока перемещения-развертки, выход оторого соединен с вторым входом третьего элемента ИЛИ, вторые входы первого, четвертого и второго элементов И соединены с вторым, третьим и четвертым выходами элока микропрограммного управления, пятый выход которого соединен с третьим входом пятого элемента И, четвертый и пятый зходы которого соединен с прямыми выхо- цами D-триггеров (i+1)-ro и (i+2)-ro разрядов элока перемещения-развертки, третий вход тервого элемента И соединен с инверсным информационным выходом 1-го разряда элока свертки и входом второго элемента НЕ, выход которого соединен с третьим вхо- IOM четвертого элемента И, четвертый вход оторого соединен с информационным вы- одом 1-го разряда блока контроля перемещения, выход четвертого элемента И оединен с первым входом четвертого эле- лента ИЛИ, выход которого соединен с ин- юрмационным входом 1-го разряда блока онтроля перемещения, второй вход чет- ертого элемента ИЛИ соединен с выходом первого элемента И, четвертым нходом второго элемента ИЛИ и входами признака сигнала перемещения блока микропрограммного управления и первым ин- оормэционным входом блока свертки, инверсный выход D-тригтера (М)-го и (1+2)- го разрядов блока перемещения-развертки соединены с третьим и четвертым входами iToporo элемента И 1-го блока перемеще- h ия-развертки, прямой информационный Е ход (т-1) младших разрядов блока свертки я вляется выходом суммы младших разрядов сумматора, контрольный выход блока контроля развертки соединен с выходом признака ошибки развертки сумматора, первый и второй входы синхронизации сумматоров соединены с первым и вторым синхровхода- г. и блока микропрограммного управления, первый и второй тактовые входы которого соединены с одноименными входами сум- NaTopa, входы запуска, числа циклов и за- проса сумматора соединены с входами признака запуска, признака числа циклов и признака запроса блока микропрограммно- г эуправления, вход признака условия мини- Г Эльноати кода которого соединен с- одноименным выходом блока свертки, шестой, седьмой и восьмой выходы блока мик- рэлрограммного управления соединены с выходами запроса первого и второго слагаемых и сигнала сопровождения суммы сум- магора соответственно, выход состояния которого соединен с девятым выходом бло- K.J микропрограммного управления и первыми управляющими входами блоков г.иертки, контроля перемещения свертки

контроля развертки и контроля снертки, вторые управляющие входы блоков контроля перемещения и контроля развертки соединены с третьим и пятым выходами соответ- ственно блока микропрограммного управления, десятый выход которого соединен с вторым управляющим входом блока контроля свертки и блока свертки, третий и четвертый управляющие входы которого соединены с одиннадцатым и двенадцатым входами соответственно блока микропрограммного управления, тринадцатый выход которого соединен с адресным входом коммутатора, первый и второй информационные входы которого соединены с входами первого и второго слагаемых сумматоров.

2, Сумматор по п. 1,отличающий- с я тем, что каждый i-й разряд блока свертки содержит шесть элементов И, три элемента ИЛИ, два элемента НЕ и D-триггер, прямой выход которого соединен с первыми входами первого и второго элементов И и является прямым информационным выходом 1-го

разряда блока при 1 1.2т, инверсный

выход D-триггера соединен с первыми входами третьего и четвертого элементов И и является инверсным информационным выходом i-ro разряда блока, первый и второй управляющие входы которого соединены соответственно с входом установки в ноль D-триггера и вторым входом второго элемента И, третий управляющий сход блока соединен с первым входом пятого элемента И, второй вход которого соединен с выходом третьего элемента И и входом первого элемента НЕ, выход которого соединен с выходом i-ro разряда условия минимальности кода 1-го разряда блока, контрольный выход 1-го разряда которого является выходом первого элемента ИЛИ, первый вход которого соединен с выходом третьего элемента И, третий, четвертый и пятый входы которого соединены соответственно с информационным входом 1-го разряда блока и инверсными информационными выходами D-триггеров (i+1)-ro и (i+kj-ro разрядов блоков, прямые выходы которых соединены с вторым и третьим входами третьего элемента И i-ro блока, вход признака сигнала перемещения которого соединен с первым входом второго элемента ИЛИ, второй и третий входы которого соединены с выходами сигналов свертки (Н)-го и (i-2)-ro разрядов блока, четвертый управляющий вход которого соединен с первым входом шестого элемента И, второй вход которого соединен с прямым выходом D-триггера (Н-т)-го разряда блока, выход шестого элемента И соединен с первым входом третьего элемента ИЛИ, второй и третий входы которого

соединены с выходами первого и четвертого элементов И, выход третьего элемента ИЛИ соединен с информационным входом D- триггера, выход второго элемента ИЛИ соекоторого соединен с вторым входом первого элемента И, четвертый вход третьего элемента ИЛИ соединен с выходом пятого элемента И, вторым входом первого элемента

динен с вторым входом четвертого элемента 5 ИЛ И и выходом 1-го разряда сигнала сверт- Й и входом второго элемента НЕ, выход ки блока.

I9f.tЛ/, Я,, ftt;j

.. Фиг. г

которого соединен с вторым входом первого элемента И, четвертый вход третьего элемента ИЛИ соединен с выходом пятого элемента И, вторым входом первого элемента

42 73мЯЦ+г 35с«ЗЗЦ„зг1+г

X J,

Wi

pt/s 3

фиё.5

Авторы

Даты

1993-08-30—Публикация

1991-04-30—Подача