Г

з у

Изобретение относится к автоматике и вычислительной технике и может быть использовано в специализированных вычислительных машинах повьшен- иой надежности и живучести.

Целью изобретения является расширение функциональных возможностей за счет нормализации кодов переменной разрядности.

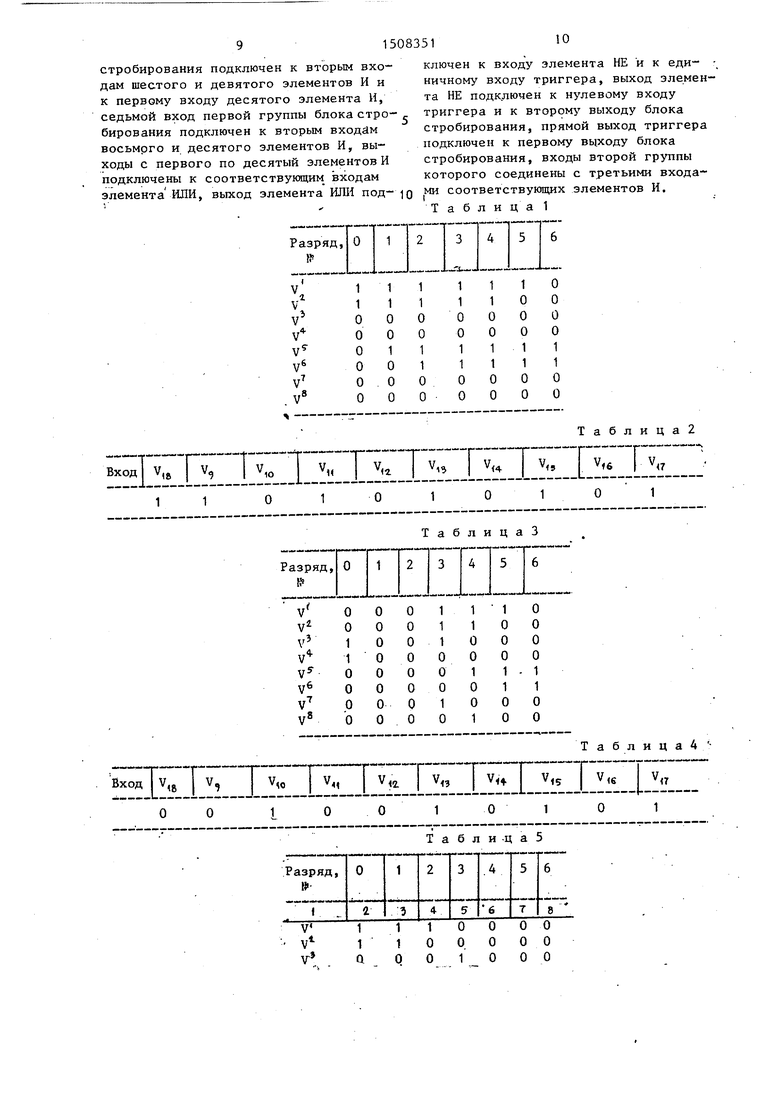

На фиг. 1 представлена схема устройства для приведения 1-кодов Фибо- наччи к нормальной форме (для ); на фиг. 2 - схема блока свертки.

Устройство (фиг, 1) содержит групНа фиг. 1 и 2 использо щие обозначения:

пу .входов 1 числаустройства, блок 2

Vg- запрет первого выхода (l+l3-ro блока свертки;

запрет первого выхода (1+2)-го блока свертки;

Vg - запрет первогс выхода (1+3)-го блока свертки;

запрет первого выхода (1+4)-го блока свертки;

V|- запрет второго выхода (1-1)-го блока свертки;

V|- запрет второго выхода (1-2)-го блока свертки;

v|- запрет второго выхода (1-3)-го блока свертки;

запрет второго выхода (1-4)-го блока свертки.

стробирования, группу элементов И З-,- 3,, с первого по седьмой блоки свертки соответственно, с первого по

десятый элементы И 5,-5,о блока 2

стробирования,соответственно, элемент И 6 блока 2 стробирования, элемент НЕ 7 блока 2 стробирования, триггер 8 блока 2 стробирования.

Блок 4 свертки (фиг. 2) содержит первый 9 и второй 9 элементы ИЛИ, с первого по пятый элементы И 105, первого по четвертый элементы И-НЕ 11;,-11, с первого по. четвертый

элементы НЕ . и триггер 13.

На фиг. 1 и 2 использованы следующие обозначения:

| название | год | авторы | номер документа |

|---|---|---|---|

| Сумматор кодов Фибоначчи | 1987 |

|

SU1532915A1 |

| Накапливающий сумматор | 1989 |

|

SU1702375A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1988 |

|

SU1583967A1 |

| Устройство для вывода информации | 1983 |

|

SU1137475A1 |

| Устройство для сопряжения двух электронно-вычислительных машин с внешними абонентами | 1985 |

|

SU1264192A1 |

| Оперативное запоминающее устройство с блокировкой неисправных ячеек памяти | 1981 |

|

SU1014033A1 |

| Устройство для приведения р-кодовфибОНАччи K МиНиМАльНОй фОРМЕ | 1979 |

|

SU842782A1 |

| Устройство для обнаружения и исправления ошибок | 1985 |

|

SU1368995A1 |

| Арифметическое устройство | 1976 |

|

SU664171A1 |

| Устройство для приведения р-кодов Фибоначчи к минимальной форме | 1988 |

|

SU1547074A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в специализированных вычислительных машинах повышенной надежности и живучести. Целью изобретения является расширение функциональных возможностей за счет нормализации кодов переменной разрядности. Поставленная цель достигается за счет новой организации связей в устройстве, содержащем блок 2 стробирования, состоящий из элементов И 51-510, элемента ИЛИ 6, элемента НЕ 7 и триггера 8, группу элементов И 31-37 и блоки 41-47 свертки. 2 з.п. ф-лы, 2 ил.

Указанные входы образуют п групп входов задания режима устройства.

V -Vg, Vg - являются соответствен-; На выходе элемента И 5д образуется но с первого по десятый входами (п+ лог. 1, которая хАпадает через эле- + 1)-й группы задания режима устрой- мент ИЛИ 6 на единичный вход триггера 8, на прямом выходе которого образуется единичный сигнал, поступающий на управляющие входы всех блоков свертки, Так как к выходу элемента

ства.

Рассмотрим работу устройства в различных режимах. Рассмотрим случаи а - все блоки свертки исправны; б - 1 и 2 разряды неисправны; в - 4 и 5 разряды 35 ИЛИ 6 подключен вход элемента НЕ 7,

неисправны.

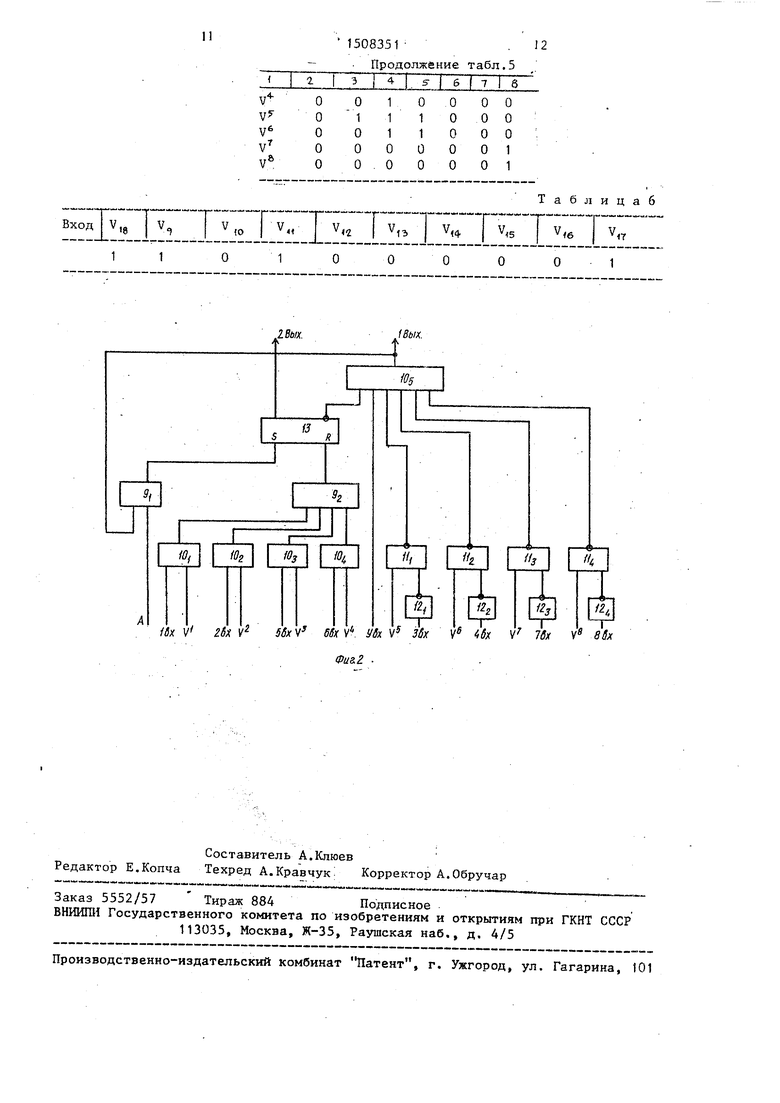

В случае а, когда все блоки свертки исправны, на V-входы подаются сиг- налы лог. О и Лог, 1 рогласио таол.1. На входы с Vg по подаются сиг- налы лог. О и лог. 1 согласно табл. 2.

На информационные входы подается число A AgA5-A4A3A2A A о рассмотрим код А 0000110. Лог. 1 постз пает на

го на вьщоде этого элемента образуется лог. О, запрещающий прохождение информации с первых выходов блоков

свертки через элементы И с 3( ПО 37.

Сигнал лог. 1, образующийся на единичном выходе триггера 8 блока 2 стробирования, попадает на второй вход элемента И 10 блока 4 свертки, так как триггер 13 находится в нулевторой вход элемента ШШ 9;,, триггер . вом состоянии. На инверсном выходе 13 встает в единичное состояние, код

А поступает в импульсном режиме, в

результате на первом выходе блока 4

свертки образуется лог. 1. На блок 4g

свертки на информационный вход посту-50 гласно табл. 1. На выходах элементов

пает импульсный сигнал лог. 1, кото- И-НЕ 1Ц и образуется лог. 1, порый, проходя через элемент ИЛИ 9,

устанавливает в единичное состояние

триггера 13. На первом выходе блока

свертки образуется сигнал лог. 1, на 5 ки поступают лог. 1 с вторых выходов

первых выходах всех других блоков ос- блоков 4,j и 4 свертки соответствен-

тается уровень лог. 0. Лог. 1 первых

выходов блоков 4 5 и 4g свертки поступает на первый и второй входы э лемёнтриггера образуется лог. 1, поступающая на первый вход элемента И . На пятнадцатый и шестнадцатый установочные входь поступает лог.О соступающая на пятый и шестой входы элемента И 10 j. На третий и четвертый установочные входы блока 4д свертно, попадающие на входы элементов НЕ 12;, и 12,21, на выходах которых образуется лог. О, так как,на первые вхо-,

та И 5,. На третий вход элемента И 5 поступает лог. 1, согласно табл. 2.

ИЛИ 6 подключен вход элемента НЕ 7,

го на вьщоде этого элемента образуется лог. О, запрещающий прохождение информации с первых выходов блоков

свертки через элементы И с 3( ПО 37.

триггера образуется лог. 1, поступающая на первый вход элемента И . На пятнадцатый и шестнадцатый установочные входь поступает лог.О соки поступают лог. 1 с вторых выходов

ступающая на пятый и шестой входы элемента И 10 j. На третий и четвертый установочные входы блока 4д свертно, попадающие на входы элементов НЕ 12;, и 12,21, на выходах которых образуется лог. О, так как,на первые вхо-,

5

ды элементов И-НЕ 11, и 11 иоступа- ет лог. 1 согласно табл. 1, а на вторых .входах лог. О, то на ёыходах элементов И-НЕ 11, и 11 образуются сигналы лог. 1, поступающие на третий и четвертый входы элемента И 10,, поэтому на выходе элемента И W блока 4 свертки образуется лог. 1. Этот сигнал, проходя через элемент ИЛИ 9 , устанавливает триггер 13 в единичное состояние, а также устанавливает триггер 13 блоков 4 и 4 свертки в нулевое состояние. Так как вторые выходы блоков 4 и 4g свертки встали в нулевое состояние, на выходе элемента И 5q блока 2 .стробирования образовался лог. 0. На выходе элемента ИЛИ 6 образовался лог. О, ,а на выходе элемента НЕ 7 - Лог. 1, которая сбро- сила триггер 8 в нулевое состояние. На единичном выходе триггера 8 образовался лог. О, т.е. сигнал стробиро- вания запретился, и на первые входы элементов И с 3 по 3 поступила лог. 1, поэтому на выходах-элементов И с 3, по ЗУ образовался выходной преобразованный код А 0001000. Преобразование кода А 0000110 в А 0001000 соответствует функции свертки кода, что соответствует функции предлагаемого устройства.

Рассмотрим функционирование устройства для случая б - неисправны 1 и 2 разряды кода свертки. На входы V по1

даются сигналы лог. О и лог. 1 согласно табл. 3.

На.входы -подаются сигналы лог. О и лог. 1 согласно табл. 4.

На информационные входы блоков свертки подается код .,A состояние и А, неопределенно и в работе не рассматривается. Для примера подадим .,1 , На вто- рых выходах блоков 4л и 47

2бр зуются сигналь1,лог. 1,

свертки поступающие на элемент Ц 5 блока 2 стробирования, на третий вход которого поступает лог. 1 согласно табл. 4,

В результате на единичном выходе триггера 8- лока 2 стробиров ания образуется лог. 1 - сигнал стробирования, по которому происходит функция свертки. 1ак как на входах элемента И lOg блока 4з свертки лог. 1, то, на выходе этого элемента образуется сигнал лог. 1, который перебрасывает в единичное состояние триггер 13 блока

1508331

5 0

.4 свертки, а триггер 13 блоков 4 и 4 свертки в нулевое состояние. Сигнал стробирования запрещается, так как на.первом и втором входах элемента И 5g блока 2 стробирования появляется лог.О. На первые входы элементов И с 3, по 3-j поступает лог. 1, на выходах которых образуется выходной преобразованный код А 0010А2 А,0. Произошло преобразование входного кода A 0001AjAJ в А 0010А2А,0, что соответствует функции свертки.

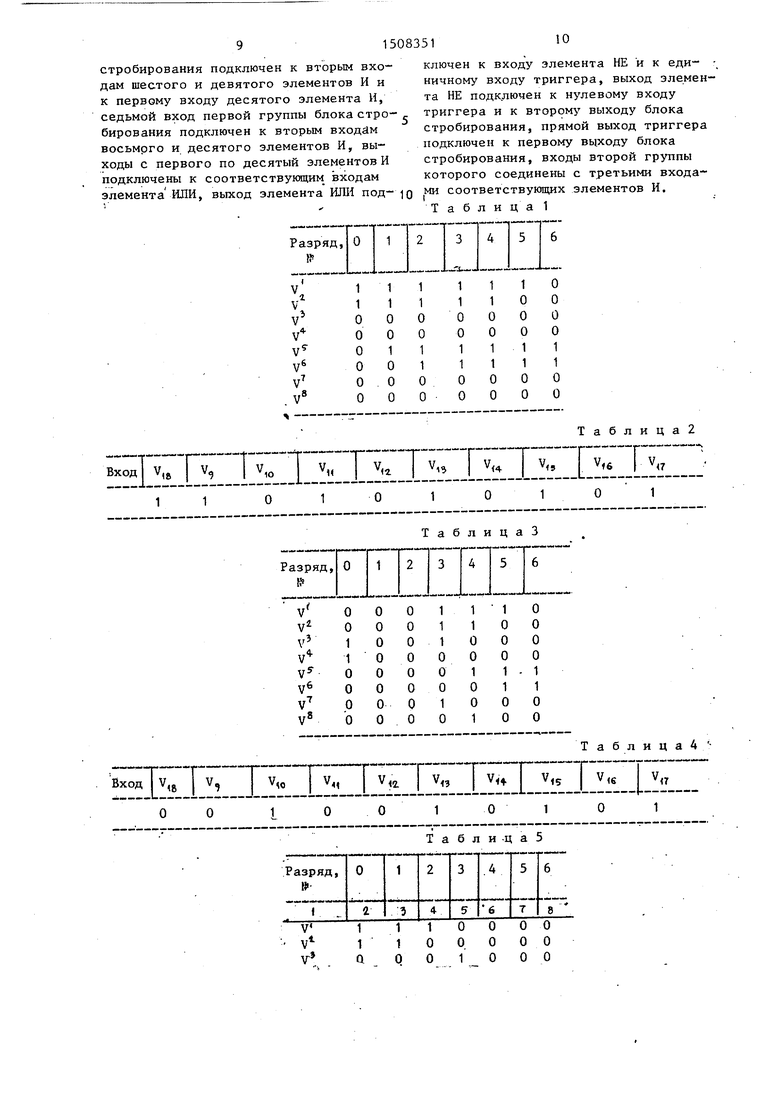

Рассмотрим случай в - неисправны 4 и 5 разряды. На входы V поступают сигналы лог. О и лог. 1 согласно табл. 5.

На входы V,-V,a подаются сигналы лог. О и лог. 1 согласно табл.6.

На информационные входы устройства поступает код ,,

5

состояние А J и

А. не определено и

в работе не рассматривается. Рас- 5 смотрим входной код А ОА5А4.1 100. На вторых выходах блоков 4ц. и 40 свертки образуется лог. 1, поступающая на первый и второй входы . элемента И -З блока 2 стробирова- Q ния, на третий вход которого подается лог. 1 согласно табл. 6. В результате образуется сигнал строби- рования на единичном выходе триг- г€ра 8 блока 2 стробирования. На всех входах элемента И lOg- блока И свертки образовалась лог. 1, на выходе элемента И 10 у- также лог. 1, по которой триггер 13 блока 4 свертки переходит в единичное состояние.

а триггер 13 блоков 4,. и 4 свертки переходит в нулевое состояние. Сигнал стробирования запрещается, так как на первом и втором входах элемента И 5 лог. 0. На выходе элементов И с 3, по 3-у образуется выходной код . Произошло преобразование входного кода в А 1А5А40000, что соответствует функции свертки.

Таким образом, предлагаемое устройство сохраняет работоспособность при выходе из строя соседних разрядов. При выходе из строя двух соседних блоков свертки на входы задания режима этих блоков подается лог. О, что соответствует их отключению , а также выходные сигналы с неисправных блоков свертки запрещаются на входах других блоков свертки.

Формула и.зобретения

25

первый и второй выходы блока стробиро- о вого элемента 1Щ1 подключен к единич- вания соединены соответственно с управляющими входами всех блоков сверт ки и с первыми входами элементов И группы, выходы которых являются груп пой выходов устройства, второй выход 1-го блока свертки соединен с (п-1+ +1)-м входом первой группы блока стро- бирования и с вторым входом соответствующего элемента И группы, о т л и- чающееся тем, что, с целью ЗО расширения функциональных возможностей за счет нормализации кодов переменной разрядности, первый выход блока свертки соединен с пятым установочным входом (1-3)-гоис шестым установочным входом (1-4)-го блоков свертки, второй выход 1-го блока свертки соединен с седьмым установочным входом (1+3)-го и с восьмым установочным входом (1+4)-го. блоков свертки, с девятого по шестнадцатый установочные входы 1-го.блока свертки соединены соответственно с входами с первого по восьмой задания режима 1-и группы устройства, входы задания режима (п+1)-й группы устройства соединены с соответствуюш 1ми входами второй группы блока стробирования.

40

45

50

55

ному входу триггера, инверсный выход триггера подключен к первому входу пятого элемента И, второй вход которого соединен с управляющим входом блока свертки, и с третьего по шестой входам пятого элемента И подключены выходы с первого по четвертый элементов И-НЕ, выход пятого элемен- т а И подключен к первому входу первого элемента ИЛИ и первому выходу блока свертки, прямой выход триггера подключен к второму выходу блока свертки, информационный вход которого соединен с вторым входом первого элемента ИЛИ.

одиннадцатому и двенадцатому установочным входам блока свертки, входы с первого по четвертый элементов НЕ подключены к третьему, четвертому, седьмому и восьмому установочным входам блока свертки, первые -входы с пер- Boi;o по четвертый элементов И-НЕ под- |Ключены к тринадцатом -, четырнадцатому, пятнадцатому и шестнадцатому установочным входам блока свертки, к вторым входам с первого по четвертый элементов И-НЕ подключены выходы с первого по четвертый элементов НЕ, к входам с первого по четвертый второго элемента ИЛИ подключены выходы с первого по четвертый элементов И, выход второго элемента ИЛИ подключен к нулевому входу триггера, выход пер25

о вого элемента 1Щ1 подключен к единич- ЗО 0

5

0

5

ному входу триггера, инверсный выход триггера подключен к первому входу пятого элемента И, второй вход которого соединен с управляющим входом блока свертки, и с третьего по шестой входам пятого элемента И подключены выходы с первого по четвертый элементов И-НЕ, выход пятого элемен- т а И подключен к первому входу первого элемента ИЛИ и первому выходу блока свертки, прямой выход триггера подключен к второму выходу блока свертки, информационный вход которого соединен с вторым входом первого элемента ИЛИ.

стробирования подключен к вторым входам шестого и девятого элементов И и к первому входу десятого элемента И, седьмой вход первой группы блока стробирования подключен к вторым входам восьмого и десятого элементов И, выходы с первого по десятый элементов И подключены к соответствующим входам элемента ИЛИ, выход элемента ИЛИ под-

Вход V,, PV, V,, 2 м .1-.

Разряд, №

V V

75-.

,а V, У V,o ,, V,,, V V V,5 j.e J V,,

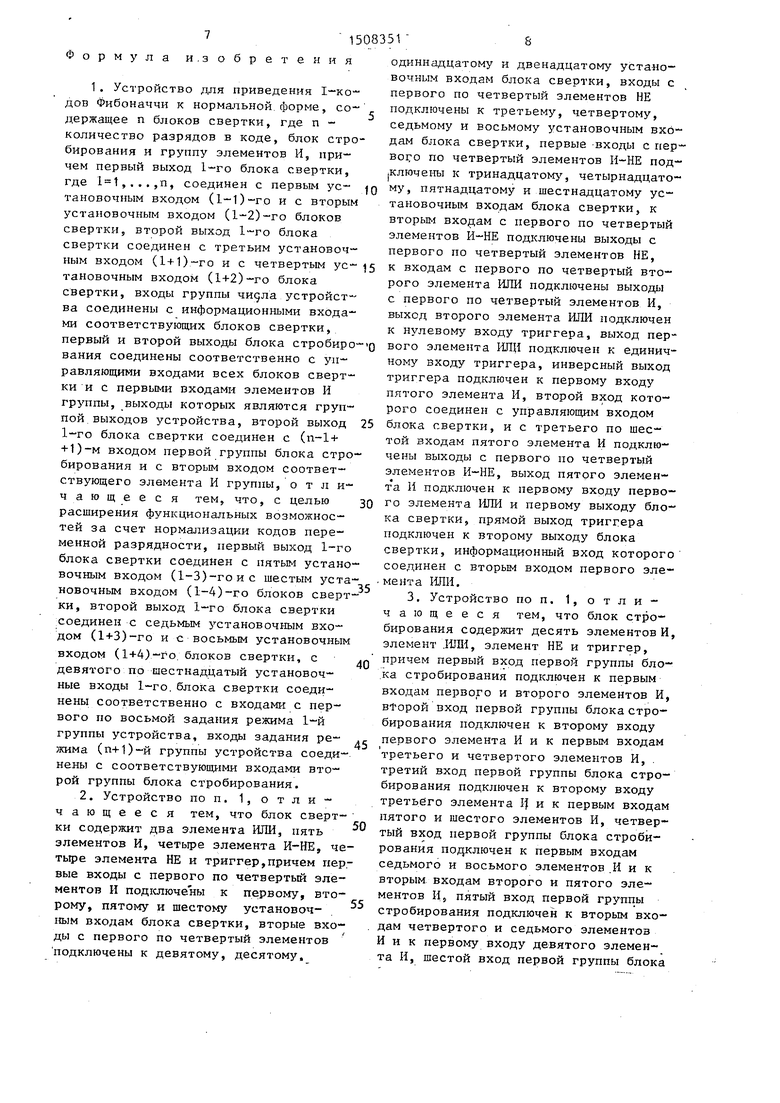

ключей к входу элемента НЕ и к единичному входу триггера, выход элемента НЕ подключен к нулевому входу триггера и к второму выходу блока стробирования, прямой выход триггера подключен к первому вцходу блока стробирования, входы второй группы которого соединены с третьими входами соответствующих элементов И. Т а б л и ц а 1

1 1

о о 1 о о о

1 1

о о 1 1

о о

1 1

о о 1 1

о о

1 1

о о 1 1 о о

1 о о о 1 1

о о

о о о о 1 1

о о

Таблица2

ТаблицаЗ

о о о о о о о о

о о о о о о о о

1

1 1

о о о 1 о

1 1

о о 1 о о 1

1 о о о 1 1 о о

о о о о 1 1

о о

ТаблицаА

11

150835 г.12

Продолжение табл.5

Вход

Jv,8 V, Jv, I I

/()Af v гЬк 1/

ЛгУ Ш V Л V 35х у (5х V ISx V 5Лг iPz/af .

| Устройство для приведения @ -кодов Фибоначчи к минимальной форме | 1982 |

|

SU1092489A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-09-15—Публикация

1988-02-22—Подача